Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| 2 0 0 0 0 0                |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1716-e-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 6.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (ECH, ECM, ECL mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (EXTRC) mode circuits.

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators and a dedicated Phase-Lock Loop (HFPLL) that are used to generate three internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC), 500 kHz (MFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 6.3 "Clock Switching"** for additional information.

#### 6.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Secondary oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See **Section 6.3 "Clock Switching**" for more information.

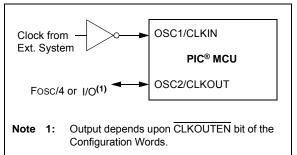

#### 6.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 6-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Words:

- ECH High power, 4-32 MHz

- ECM Medium power, 0.5-4 MHz

- ECL Low power, 0-0.5 MHz

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### EXTERNAL CLOCK (EC) MODE OPERATION

#### 6.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 6-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 6-3 and Figure 6-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

| U-0            | R/W-0/0       | R/W-0/0                            | R/W-0/0         | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|----------------|---------------|------------------------------------|-----------------|----------------|------------------|------------------|--------------|

| _              | NCOIE         | COGIE                              | ZCDIE           | CLC4IE         | CLC3IE           | CLC2IE           | CLC1IE       |

| oit 7          |               | 1                                  |                 | 1              |                  |                  | bit          |

|                |               |                                    |                 |                |                  |                  |              |

| Legend:        |               |                                    |                 |                |                  |                  |              |

| R = Readat     | ole bit       | W = Writable                       | bit             | U = Unimpler   | mented bit, read | l as '0'         |              |

| u = Bit is ur  | -             | x = Bit is unk                     |                 | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is s | et            | '0' = Bit is cle                   | ared            |                |                  |                  |              |

| bit 7          | Unimplemen    | ited: Read as '0'                  |                 |                |                  |                  |              |

| bit 6          | NCOIE: NCO    | O Interrupt Enat                   | ole bit         |                |                  |                  |              |

|                |               | errupt enabled                     |                 |                |                  |                  |              |

|                |               | errupt disabled                    |                 |                |                  |                  |              |

| bit 5          |               | G Auto-Shutdov                     | vn Interrupt Er | hable bit      |                  |                  |              |

|                |               | terrupt enabled terrupt disabled   |                 |                |                  |                  |              |

| bit 4          |               | -Cross Detection                   | on Interrupt Er | able bit       |                  |                  |              |

|                |               | errupt enabled                     |                 |                |                  |                  |              |

|                | 0 = ZCD inte  | errupt disabled                    |                 |                |                  |                  |              |

| bit 3          |               | C4 Interrupt En                    |                 |                |                  |                  |              |

|                |               | terrupt enabled                    |                 |                |                  |                  |              |

| bit 2          |               | terrupt disabled                   |                 |                |                  |                  |              |

| DILZ           |               | C3 Interrupt En<br>terrupt enabled |                 |                |                  |                  |              |

|                |               | terrupt disabled                   |                 |                |                  |                  |              |

| bit 1          |               | C2 Interrupt En                    |                 |                |                  |                  |              |

|                |               | iterrupt enabled                   |                 |                |                  |                  |              |

|                |               | terrupt disabled                   |                 |                |                  |                  |              |

| bit 0          |               | C1 Interrupt En                    |                 |                |                  |                  |              |

|                |               | terrupt enabled                    |                 |                |                  |                  |              |

|                | 0 = C C C I n |                                    |                 |                |                  |                  |              |

#### REGISTER 7-4: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

set to enable any peripheral interrupt.

## 8.0 POWER-DOWN MODE (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3.  $\overline{\text{TO}}$  bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Timer1 and peripherals that operate from Timer1 continue operation in Sleep when the Timer1 clock source selected is:

- LFINTOSC

- T1CKI

- Secondary oscillator

- 7. ADC is unaffected, if the dedicated FRC oscillator is selected.

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or high-impedance).

- 9. Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- · Internal circuitry sourcing current from I/O pins

- · Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

- · Modules using secondary oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 22.0 "Operational Amplifier (OPA) Modules" and Section 14.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

#### 8.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 5.12 "Determining the Cause of a Reset"**.

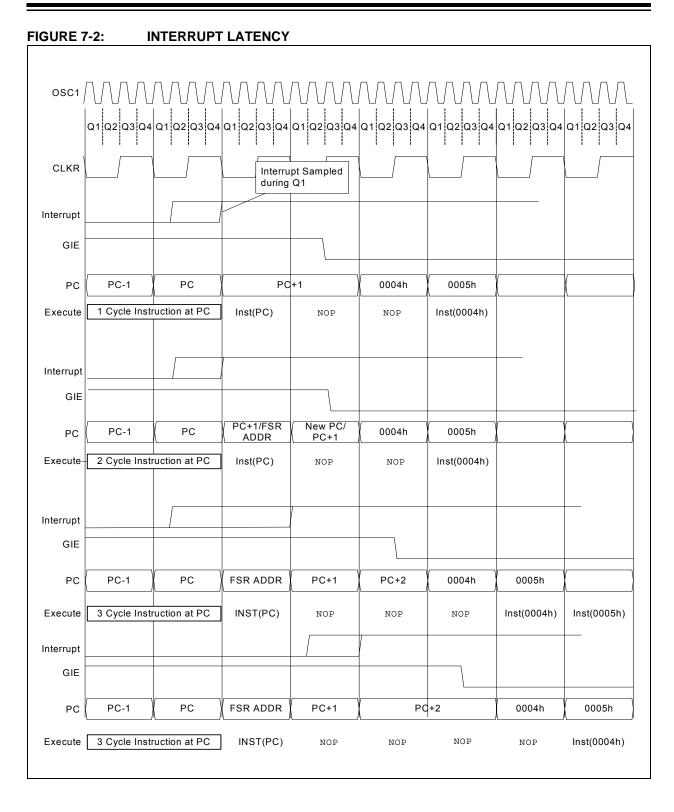

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

#### 10.6 Register Definitions: Flash Program Memory Control

#### REGISTER 10-1: PMDATL: PROGRAM MEMORY DATA LOW BYTE REGISTER

| R/W-x/u            | R/W-x/u | R/W-x/u                                                               | R/W-x/u | R/W-x/u                            | R/W-x/u | R/W-x/u | R/W-x/u |

|--------------------|---------|-----------------------------------------------------------------------|---------|------------------------------------|---------|---------|---------|

|                    |         |                                                                       | PMDA    | T<7:0>                             |         |         |         |

| bit 7              |         |                                                                       |         |                                    |         |         | bit 0   |

|                    |         |                                                                       |         |                                    |         |         |         |

| Legend:            |         |                                                                       |         |                                    |         |         |         |

| R = Readable bit   |         | W = Writable bit                                                      |         | U = Unimplemented bit, read as '0' |         |         |         |

| u = Bit is unchang | jed     | x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Res |         |                                    |         | ets     |         |

| '1' = Bit is set   |         | '0' = Bit is cleared                                                  |         |                                    |         |         |         |

bit 7-0 PMDAT<7:0>: Read/write value for Least Significant bits of program memory

#### REGISTER 10-2: PMDATH: PROGRAM MEMORY DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|-------------|---------|---------|---------|---------|

| —     | —   |         | PMDAT<13:8> |         |         |         |         |

| bit 7 |     |         |             |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 PMDAT<13:8>: Read/write value for Most Significant bits of program memory

#### REGISTER 10-3: PMADRL: PROGRAM MEMORY ADDRESS LOW BYTE REGISTER

| R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|------------|---------|---------|---------|---------|---------|---------|---------|

| PMADR<7:0> |         |         |         |         |         |         |         |

| bit 7      |         |         |         |         |         |         | bit 0   |

|            |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 PMADR<7:0>: Specifies the Least Significant bits for program memory address

#### REGISTER 10-4: PMADRH: PROGRAM MEMORY ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-------------|---------|---------|---------|

| _(1)  |         |         |         | PMADR<14:8> |         |         |         |

| bit 7 |         |         |         |             |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '1'

bit 6-0 PMADR<14:8>: Specifies the Most Significant bits for program memory address

Note 1: Unimplemented, read as '1'.

| R/W-1/1                               | R/W-1/1                                 | R/W-1/1 | R/W-1/1                                               | R/W-1/1                            | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |

|---------------------------------------|-----------------------------------------|---------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|

| WPUA7                                 | WPUA6                                   | WPUA5   | WPUA4                                                 | WPUA3                              | WPUA2   | WPUA1   | WPUA0   |  |

| bit 7                                 |                                         |         |                                                       |                                    |         |         | bit 0   |  |

|                                       |                                         |         |                                                       |                                    |         |         |         |  |

| Legend:                               |                                         |         |                                                       |                                    |         |         |         |  |

| R = Readable                          | R = Readable bit W = Writable bit       |         | bit                                                   | U = Unimplemented bit, read as '0' |         |         |         |  |

| u = Bit is unch                       | u = Bit is unchanged x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |

| '1' = Bit is set '0' = Bit is cleared |                                         |         |                                                       |                                    |         |         |         |  |

#### REGISTER 11-5: WPUA: WEAK PULL-UP PORTA REGISTER

bit 7-0 WPUA<7:0>: Weak Pull-up Register bits

1 = Pull-up enabled

0 = Pull-up disabled

Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is configured as an output.

#### **REGISTER 11-6: ODCONA: PORTA OPEN-DRAIN CONTROL REGISTER**

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ODA7    | ODA6    | ODA5    | ODA4    | ODA3    | ODA2    | ODA1    | ODA0    |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ODA<7:0>: PORTA Open-Drain Enable bits

For RA<7:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

### 11.3 PORTB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 11-10). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 11-9) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

#### 11.3.1 DIRECTION CONTROL

The TRISB register (Register 11-10) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 11.3.2 OPEN-DRAIN CONTROL

The ODCONB register (Register 11-14) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONB bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONB bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

#### 11.3.3 SLEW RATE CONTROL

The SLRCONB register (Register 11-15) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONB bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONB bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 11.3.4 INPUT THRESHOLD CONTROL

The INLVLB register (Register 11-16) controls the input voltage threshold for each of the available PORTB input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTB register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 34-4: I/O Ports for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

### 11.3.5 ANALOG CONTROL

The ANSELB register (Register 11-12) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSELB set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELB bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

#### 11.3.6 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after reset. Other functions are selected with the peripheral pin select logic. See **Section 12.0** "**Peripheral Pin Select** (**PPS**) **Module**" for more information. Analog input functions, such as ADC and Op Amp inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELB register. Digital output functions continue to may continue to control the pin when it is in Analog mode.

### 11.5 PORTC Registers

#### 11.5.1 DATA REGISTER

PORTC is an 8-bit wide bidirectional port. The corresponding data direction register is TRISC (Register 11-18). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTC register (Register 11-17) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

#### 11.5.2 DIRECTION CONTROL

The TRISC register (Register 11-18) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 11.5.3 INPUT THRESHOLD CONTROL

The INLVLC register (Register 11-24) controls the input voltage threshold for each of the available PORTC input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTC register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 34-4: I/O Ports for more information on threshold levels.

| Note: | Changing the input threshold selection should be performed while all peripheral |

|-------|---------------------------------------------------------------------------------|

|       | modules are disabled. Changing the                                              |

|       | threshold level during the time a module is                                     |

|       | active may inadvertently generate a                                             |

|       | transition associated with an input pin,                                        |

|       | regardless of the actual voltage level on                                       |

|       | that pin.                                                                       |

#### 11.5.4 OPEN-DRAIN CONTROL

The ODCONC register (Register 11-22) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONC bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONC bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

#### 11.5.5 SLEW RATE CONTROL

The SLRCONC register (Register 11-23) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONC bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONC bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 11.5.6 ANALOG CONTROL

The ANSELC register (Register 11-20) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELC bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELC bits has no effect on digital output functions. A pin with TRIS clear and ANSELC set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELC bits default to the Analog        |  |  |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|--|--|

|       | mode after Reset. To use any pins as         |  |  |  |  |  |  |  |  |

|       | digital general purpose or peripheral        |  |  |  |  |  |  |  |  |

|       | inputs, the corresponding ANSEL bits         |  |  |  |  |  |  |  |  |

|       | must be initialized to '0' by user software. |  |  |  |  |  |  |  |  |

#### 11.5.7 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each pin defaults to the PORT latch data after reset. Other functions are selected with the peripheral pin select logic. See **Section 12.0** "**Peripheral Pin Select (PPS) Module**" for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELC register. Digital output functions may continue to control the pin when it is in Analog mode.

#### REGISTER 12-3: PPSLOCK: PPS LOCK REGISTER

| U-0                                   | U-0    | U-0             | U-0  | U-0                                                   | U-0             | U-0      | R/W-0/0   |  |

|---------------------------------------|--------|-----------------|------|-------------------------------------------------------|-----------------|----------|-----------|--|

| —                                     | -      | —               | —    | —                                                     | —               | —        | PPSLOCKED |  |

| bit 7                                 |        |                 |      |                                                       |                 |          | bit 0     |  |

|                                       |        |                 |      |                                                       |                 |          |           |  |

| Legend:                               |        |                 |      |                                                       |                 |          |           |  |

| R = Readable                          | e bit  | W = Writable I  | oit  | U = Unimplem                                          | nented bit, rea | d as '0' |           |  |

| u = Bit is unc                        | hanged | x = Bit is unkn | own  | -n/n = Value at POR and BOR/Value at all other Resets |                 |          |           |  |

| '1' = Bit is set '0' = Bit is cleared |        |                 | ared |                                                       |                 |          |           |  |

bit 7-1 Unimplemented: Read as '0'

bit 0 PPSLOCKED: PPS Locked bit

1= PPS is locked. PPS selections can not be changed.

0= PPS is not locked. PPS selections can be changed.

When one device is transmitting a logical one, or letting the line float, and a second device is transmitting a logical zero, or holding the line low, the first device can detect that the line is not a logical one. This detection, when used on the SCL line, is called clock stretching. Clock stretching gives slave devices a mechanism to control the flow of data. When this detection is used on the SDA line, it is called arbitration. Arbitration ensures that there is only one master device communicating at any single time.

### 30.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of clock stretching. An addressed slave device may hold the SCL clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCL line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCL connection is open-drain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

#### 30.3.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDA data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels do not match, loses arbitration, and must stop transmitting on the SDA line.

For example, if one transmitter holds the SDA line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDA line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDA line. If this transmitter is also a master device, it also must stop driving the SCL line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDA line continues with its original transmission. It can do so without any complications, because so far, the transmission appears exactly as expected with no other transmitter disturbing the message.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

If two master devices are sending a message to two different slave devices at the address stage, the master sending the lower slave address always wins arbitration. When two master devices send messages to the same slave address, and addresses can sometimes refer to multiple slaves, the arbitration process must continue into the data stage.

Arbitration usually occurs very rarely, but it is a necessary process for proper multi-master support.

| R/W-0/0          | R/W-0/0                                                                                                                                    | R/W-0/0                                                                                                                                      | R/W-0/0         | R/W-0/0        | R-0/0             | R-0/0            | R-0/0       |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|-------------------|------------------|-------------|--|--|--|--|

| SPEN             | RX9                                                                                                                                        | SREN                                                                                                                                         | CREN            | ADDEN          | FERR              | OERR             | RX9D        |  |  |  |  |

| bit 7            |                                                                                                                                            |                                                                                                                                              |                 |                | ·                 |                  | bit C       |  |  |  |  |

|                  |                                                                                                                                            |                                                                                                                                              |                 |                |                   |                  |             |  |  |  |  |

| Legend:          |                                                                                                                                            |                                                                                                                                              |                 |                |                   |                  |             |  |  |  |  |

| R = Readable     |                                                                                                                                            | W = Writable                                                                                                                                 | bit             |                | emented bit, read |                  |             |  |  |  |  |

| u = Bit is unc   | •                                                                                                                                          | x = Bit is unk                                                                                                                               |                 | -n/n = Value   | e at POR and BC   | R/Value at all o | ther Resets |  |  |  |  |

| '1' = Bit is set |                                                                                                                                            | '0' = Bit is cle                                                                                                                             | ared            |                |                   |                  |             |  |  |  |  |

| bit 7            | SPEN: Seria                                                                                                                                | l Port Enable b                                                                                                                              | it              |                |                   |                  |             |  |  |  |  |

|                  | 1 = Serial po                                                                                                                              |                                                                                                                                              |                 |                |                   |                  |             |  |  |  |  |

|                  |                                                                                                                                            | ort disabled (he                                                                                                                             | ld in Reset)    |                |                   |                  |             |  |  |  |  |

| bit 6            | <b>RX9:</b> 9-Bit R                                                                                                                        | eceive Enable                                                                                                                                | bit             |                |                   |                  |             |  |  |  |  |

|                  |                                                                                                                                            | 9-bit reception<br>8-bit reception                                                                                                           |                 |                |                   |                  |             |  |  |  |  |

| bit 5            | SREN: Singl                                                                                                                                | e Receive Ena                                                                                                                                | ble bit         |                |                   |                  |             |  |  |  |  |

|                  | <u>Asynchronou</u>                                                                                                                         | <u>us mode</u> :                                                                                                                             |                 |                |                   |                  |             |  |  |  |  |

|                  | Don't care                                                                                                                                 |                                                                                                                                              |                 |                |                   |                  |             |  |  |  |  |

|                  |                                                                                                                                            | Synchronous mode – Master:                                                                                                                   |                 |                |                   |                  |             |  |  |  |  |

|                  |                                                                                                                                            | <ul><li>1 = Enables single receive</li><li>0 = Disables single receive</li></ul>                                                             |                 |                |                   |                  |             |  |  |  |  |

|                  |                                                                                                                                            | This bit is cleared after reception is complete.                                                                                             |                 |                |                   |                  |             |  |  |  |  |

|                  | -                                                                                                                                          | Synchronous mode – Slave                                                                                                                     |                 |                |                   |                  |             |  |  |  |  |

|                  | Don't care                                                                                                                                 |                                                                                                                                              |                 |                |                   |                  |             |  |  |  |  |

| bit 4            |                                                                                                                                            | CREN: Continuous Receive Enable bit                                                                                                          |                 |                |                   |                  |             |  |  |  |  |

|                  | -                                                                                                                                          | Asynchronous mode:                                                                                                                           |                 |                |                   |                  |             |  |  |  |  |

|                  |                                                                                                                                            | 1 = Enables receiver<br>0 = Disables receiver                                                                                                |                 |                |                   |                  |             |  |  |  |  |

|                  | Synchronous mode:                                                                                                                          |                                                                                                                                              |                 |                |                   |                  |             |  |  |  |  |

|                  | 1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)                                                      |                                                                                                                                              |                 |                |                   |                  |             |  |  |  |  |

|                  | 0 = Disables                                                                                                                               | s continuous re                                                                                                                              | ceive           |                |                   |                  |             |  |  |  |  |

| bit 3            |                                                                                                                                            | dress Detect Er                                                                                                                              |                 |                |                   |                  |             |  |  |  |  |

|                  | •                                                                                                                                          | Asynchronous mode 9-bit (RX9 = 1):                                                                                                           |                 |                |                   |                  |             |  |  |  |  |

|                  |                                                                                                                                            | 1 = Enables address detection, enable interrupt and load the receive buffer when RSR<8> is set                                               |                 |                |                   |                  |             |  |  |  |  |

|                  |                                                                                                                                            | 0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit<br><u>Asynchronous mode 8-bit (RX9 = 0)</u> : |                 |                |                   |                  |             |  |  |  |  |

|                  | Don't care                                                                                                                                 |                                                                                                                                              | ,               |                |                   |                  |             |  |  |  |  |

| bit 2            | FERR: Fram                                                                                                                                 | ing Error bit                                                                                                                                |                 |                |                   |                  |             |  |  |  |  |

|                  | <ul> <li>1 = Framing error (can be updated by reading RCREG register and receive next valid byte)</li> <li>0 = No framing error</li> </ul> |                                                                                                                                              |                 |                |                   |                  |             |  |  |  |  |

| bit 1            | OERR: Over                                                                                                                                 | run Error bit                                                                                                                                |                 |                |                   |                  |             |  |  |  |  |

|                  | 1 = Overrun<br>0 = No over                                                                                                                 | error (can be o<br>run error                                                                                                                 | cleared by clea | aring bit CREI | N)                |                  |             |  |  |  |  |

| hit 0            |                                                                                                                                            |                                                                                                                                              |                 |                |                   |                  |             |  |  |  |  |

| bit 0            | RX9D: Ninth                                                                                                                                | bit of Received                                                                                                                              | d Data          |                |                   |                  |             |  |  |  |  |

### REGISTER 31-2: RC1STA: RECEIVE STATUS AND CONTROL REGISTER

#### TABLE 31-3: BAUD RATE FORMULAS

| (    | Configuration Bi | ts   |                     | Baud Rate Formula |  |  |

|------|------------------|------|---------------------|-------------------|--|--|

| SYNC | BRG16            | BRGH | BRG/EUSART Mode     |                   |  |  |

| 0    | 0                | 0    | 8-bit/Asynchronous  | Fosc/[64 (n+1)]   |  |  |

| 0    | 0                | 1    | 8-bit/Asynchronous  |                   |  |  |

| 0    | 1                | 0    | 16-bit/Asynchronous | Fosc/[16 (n+1)]   |  |  |

| 0    | 1                | 1    | 16-bit/Asynchronous |                   |  |  |

| 1    | 0                | x    | 8-bit/Synchronous   | Fosc/[4 (n+1)]    |  |  |

| 1    | 1                | x    | 16-bit/Synchronous  |                   |  |  |

**Legend:** x = Don't care, n = value of SPBRGH, SPBRGL register pair.

#### TABLE 31-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR

| Name     | Bit 7        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|----------|--------------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| BAUD1CON | ABDOVF       | RCIDL | _     | SCKP  | BRG16 | _     | WUE   | ABDEN | 349                 |

| RC1STA   | SPEN         | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 348                 |

| SP1BRGL  | SP1BRG<7:0>  |       |       |       |       |       |       |       | 350                 |

| SP1BRGH  | SP1BRG<15:8> |       |       |       |       |       |       |       | 350                 |

| TX1STA   | CSRC         | TX9   | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 347                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for the Baud Rate Generator.

\* Page provides register information.

# 31.5.2.3 EUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 31.5.1.5 "Synchronous Master Reception"), with the following exceptions:

- · Sleep

- CREN bit is always set, therefore the receiver is never idle

- SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 31.5.2.4 Synchronous Slave Reception Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for both the CK and DT pins (if applicable).

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Set the CREN bit to enable reception.

- The RCIF bit will be set when reception is complete. An interrupt will be generated if the RCIE bit was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

| Name     | Bit 7                        | Bit 6  | Bit 5  | Bit 4      | Bit 3  | Bit 2      | Bit 1  | Bit 0  | Register<br>on Page |

|----------|------------------------------|--------|--------|------------|--------|------------|--------|--------|---------------------|

| ANSELB   | —                            | _      | ANSB5  | ANSB4      | ANSB3  | ANSB2      | ANSB1  | ANSB0  | 126                 |

| ANSELC   | ANSC7                        | ANSC6  | ANSC5  | ANSC4      | ANSC3  | ANSC2      | _      | —      | 131                 |

| BAUD1CON | ABDOVF                       | RCIDL  | _      | SCKP       | BRG16  | —          | WUE    | ABDEN  | 349                 |

| CKPPS    | —                            | -      | —      |            |        | CKPPS<4:0> |        |        | 136                 |

| INTCON   | GIE                          | PEIE   | TMR0IE | INTE       | IOCIE  | TMR0IF     | INTF   | IOCIF  | 83                  |

| PIE1     | TMR1GIE                      | ADIE   | RCIE   | TXIE       | SSP1IE | CCP1IE     | TMR2IE | TMR1IE | 84                  |

| PIR1     | TMR1GIF                      | ADIF   | RCIF   | TXIF       | SSP1IF | CCP1IF     | TMR2IF | TMR1IF | 87                  |

| RC1REG   | EUSART Receive Data Register |        |        |            |        |            |        | 342*   |                     |

| RC1STA   | SPEN                         | RX9    | SREN   | CREN       | ADDEN  | FERR       | OERR   | RX9D   | 348                 |

| RXPPS    | —                            | _      | —      | RXPPS<4:0> |        |            |        |        | 136                 |

| TRISB    | TRISB7                       | TRISB6 | TRISB5 | TRISB4     | TRISB3 | TRISB2     | TRISB1 | TRISB0 | 125                 |

| TRISC    | TRISC7                       | TRISC6 | TRISC5 | TRISC4     | TRISC3 | TRISC2     | TRISC1 | TRISA0 | 130                 |

| TX1STA   | CSRC                         | TX9    | TXEN   | SYNC       | SENDB  | BRGH       | TRMT   | TX9D   | 347                 |

## TABLE 31-10: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for synchronous slave reception. \* Page provides register information.

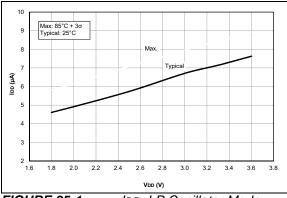

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

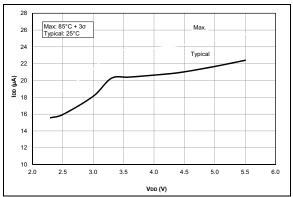

FIGURE 35-1: IDD, LP Oscillator Mode, Fosc = 32 kHz, PIC16LF1713/6 Only.

**FIGURE 35-2:** IDD, LP Oscillator Mode, Fosc = 32 kHz, PIC16F1713/6 Only.

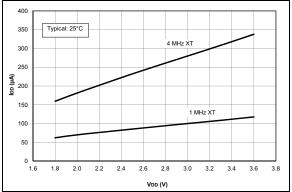

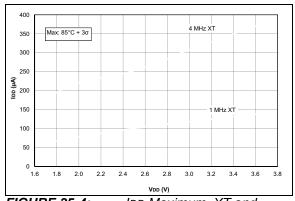

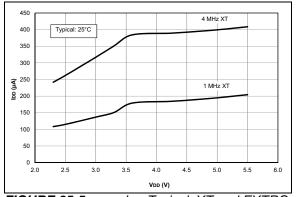

FIGURE 35-3: IDD Typical, XT and EXTRC Oscillator, PIC16LF1713/6 Only.

FIGURE 35-5: IDD Typical, XT and EXTRC Oscillator, PIC16F1713/6 Only.

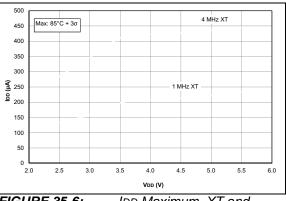

FIGURE 35-6: IDD Maximum, XT and EXTRC Oscillator, PIC16F1713/6 Only.

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, flexPWR, JukeBlox, KEELoQ, KEELoQ logo, Kleer, LANCheck, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC<sup>32</sup> logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

The Embedded Control Solutions Company and mTouch are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, ECAN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, RightTouch logo, REAL ICE, SQI, Serial Quad I/O, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2013-2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0172-8

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.