#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1716-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 6.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (ECH, ECM, ECL mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (EXTRC) mode circuits.

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators and a dedicated Phase-Lock Loop (HFPLL) that are used to generate three internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC), 500 kHz (MFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 6.3 "Clock Switching"** for additional information.

#### 6.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Secondary oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See **Section 6.3 "Clock Switching**" for more information.

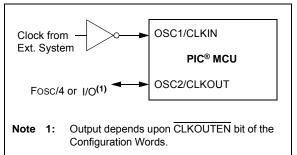

#### 6.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 6-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through Configuration Words:

- ECH High power, 4-32 MHz

- ECM Medium power, 0.5-4 MHz

- ECL Low power, 0-0.5 MHz

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### EXTERNAL CLOCK (EC) MODE OPERATION

#### 6.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 6-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 6-3 and Figure 6-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

#### 8.3 Register Definitions: Voltage Regulator Control

#### REGISTER 8-1: VREGCON: VOLTAGE REGULATOR CONTROL REGISTER<sup>(1)</sup>

| U-0                               | U-0 | U-0 | U-0 | U-0           | U-0                | R/W-0/0 | R/W-1/1  |

|-----------------------------------|-----|-----|-----|---------------|--------------------|---------|----------|

| —                                 | _   | —   | —   | —             |                    | VREGPM  | Reserved |

| bit 7                             |     |     |     |               |                    |         | bit 0    |

|                                   |     |     |     |               |                    |         |          |

| Legend:                           |     |     |     |               |                    |         |          |

| R = Readable bit W = Writable bit |     |     | t   | U = Unimpleme | ented bit, read as | 0'      |          |

-n/n = Value at POR and BOR/Value at all other Resets

| bit 7-2 | Unimplemented: Read as '0'                               |

|---------|----------------------------------------------------------|

| bit 1   | VREGPM: Voltage Regulator Power Mode Selection bit       |

|         | 1 = Low-Power Sleep mode enabled in Sleep <sup>(2)</sup> |

|         | Draws lowest current in Sleep, slower wake-up            |

|         | 0 = Normal-Power mode enabled in Sleep <sup>(2)</sup>    |

|         | Draws higher current in Sleep, faster wake-up            |

|         |                                                          |

x = Bit is unknown

'0' = Bit is cleared

bit 0 Reserved: Read as '1'. Maintain this bit set.

Note 1: PIC16F1713/6 only.

u = Bit is unchanged

'1' = Bit is set

2: See Section 34.0 "Electrical Specifications".

#### TABLE 8-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

| Name                   | Bit 7 | Bit 6 | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0    | Register on<br>Page |

|------------------------|-------|-------|------------|-------|-------|-------|--------|----------|---------------------|

| STATUS                 | —     | —     | _          | TO    | PD    | Z     | DC     | С        | 19                  |

| VREGCON <sup>(1)</sup> | —     | —     | —          | _     | —     | _     | VREGPM | Reserved | 94                  |

| WDTCON                 | _     | _     | WDTPS<4:0> |       |       |       | SWDTEN | 98       |                     |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used in Power-Down mode.

Note 1: PIC16F1713/6 only.

#### EXAMPLE 10-2: ERASING ONE ROW OF PROGRAM MEMORY

- ; This row erase routine assumes the following:

- ; 1. A valid address within the erase row is loaded in ADDRH:ADDRL

- ; 2. ADDRH and ADDRL are located in shared data memory  $0\,\mathrm{x}70$   $0\,\mathrm{x}7F$  (common RAM)

|                      | BCF<br>BANKSEL<br>MOVF<br>MOVWF<br>MOVF<br>MOVWF | INTCON,GIE<br>PMADRL<br>ADDRL,W<br>PMADRL<br>ADDRH,W<br>PMADRH | ; Disable ints so required sequences will execute properly<br>; Load lower 8 bits of erase address boundary<br>; Load upper 6 bits of erase address boundary                                                                                                                                                                                             |

|----------------------|--------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | BCF<br>BSF<br>BSF                                | PMADKH<br>PMCON1,CFGS<br>PMCON1,FREE<br>PMCON1,WREN            | ; Not configuration space<br>; Specify an erase operation<br>; Enable writes                                                                                                                                                                                                                                                                             |

| Required<br>Sequence | MOVLW<br>MOVWF<br>MOVWF<br>BSF<br>NOP<br>NOP     | 55h<br>PMCON2<br>0AAh<br>PMCON2<br>PMCON1,WR                   | <pre>; Start of required sequence to initiate erase<br/>; Write 55h<br/>;<br/>; Write AAh<br/>; Set WR bit to begin erase<br/>; NOP instructions are forced as processor starts<br/>; row erase of program memory.<br/>;<br/>; The processor stalls until the erase process is complete<br/>; after erase processor continues with 3rd instruction</pre> |

|                      | BCF<br>BSF                                       | PMCON1,WREN<br>INTCON,GIE                                      | ; Disable writes<br>; Enable interrupts                                                                                                                                                                                                                                                                                                                  |

| ODB7<br>bit 7 | ODB6 | ODB5 | ODB4 | ODB3 | ODB2 | ODB1 | ODB0<br>bit 0 |

|---------------|------|------|------|------|------|------|---------------|

| bit 7         |      |      |      |      |      |      | bit (         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

ODB<7:0>: PORTB Open-Drain Enable bits

For RB<7:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

#### REGISTER 11-15: SLRCONB: PORTB SLEW RATE CONTROL REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRB7   | SLRB6   | SLRB5   | SLRB4   | SLRB3   | SLRB2   | SLRB1   | SLRB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |  |

|----------------------|----------------------|-------------------------------------------------------|--|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |  |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |  |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |  |

bit 7-0 SLRB<7:0>: PORTB Slew Rate Enable bits

For RB<7:0> pins, respectively

1 = Port pin slew rate is limited

0 = Port pin slews at maximum rate

#### REGISTER 11-16: INLVLB: PORTB INPUT LEVEL CONTROL REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4 | INLVLB3 | INLVLB2 | INLVLB1 | INLVLB0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INLVLB<7:0>: PORTB Input Level Select bits

For RB<7:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

© 2013-2016 Microchip Technology Inc.

#### 17.1.9 SETUP FOR PWM OPERATION USING PWMx PINS

The following steps should be taken when configuring the module for PWM operation using the PWMx pins:

- 1. Disable the PWMx pin output driver(s) by setting the associated TRIS bit(s).

- 2. Clear the PWMxCON register.

- 3. Load the PR2 register with the PWM period value.

- Load the PWMxDCH register and bits <7:6> of the PWMxDCL register with the PWM duty cycle value.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register. See Note below.

- Configure the T2CKPS bits of the T2CON register with the Timer2 prescale value.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- Enable PWM output pin and wait until Timer2 overflows, TMR2IF bit of the PIR1 register is set. See Note below.

- 7. Enable the PWMx pin output driver(s) by clearing the associated TRIS bit(s) and setting the desired pin PPS control bits.

- 8. Configure the PWM module by loading the PWMxCON register with the appropriate values.

- Note 1: In order to send a complete duty cycle and period on the first PWM output, the above steps must be followed in the order given. If it is not critical to start with a complete PWM signal, then move Step 8 to replace Step 4.

- **2:** For operation with other peripherals only, disable PWMx pin outputs.

#### 17.1.10 SETUP FOR PWM OPERATION TO OTHER DEVICE PERIPHERALS

The following steps should be taken when configuring the module for PWM operation to be used by other device peripherals:

- 1. Disable the PWMx pin output driver(s) by setting the associated TRIS bit(s).

- 2. Clear the PWMxCON register.

- 3. Load the PR2 register with the PWM period value.

- 4. Load the PWMxDCH register and bits <7:6> of the PWMxDCL register with the PWM duty cycle value.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1

register. See Note below.

- Configure the T2CKPS bits of the T2CON register with the Timer2 prescale value.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output pin:

- Wait until Timer2 overflows, TMR2IF bit of the PIR1 register is set. See Note below.

- 7. Configure the PWM module by loading the PWMxCON register with the appropriate values.

- **Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

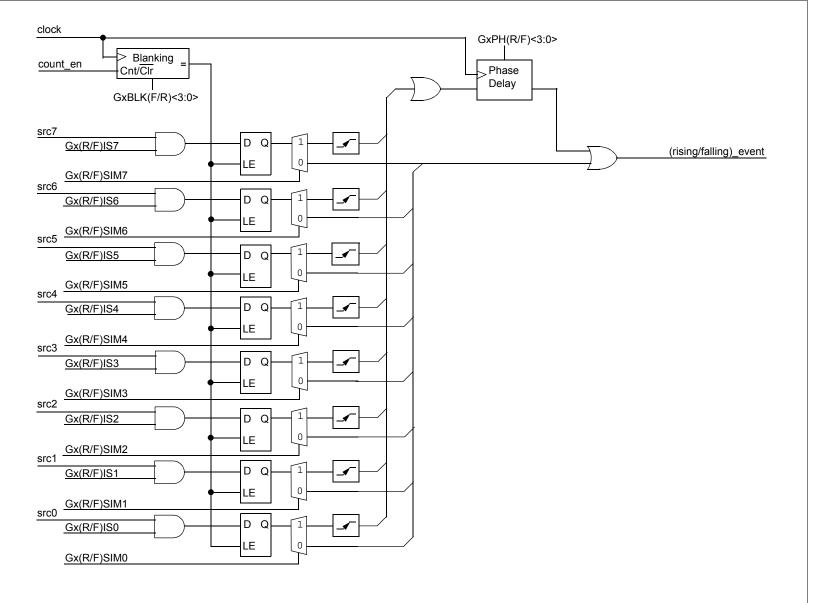

#### FIGURE 18-7: COG (RISING/FALLING) INPUT BLOCK

© 2013-2016 Microchip Technology Inc.

PIC16(L)F1713/6

#### 18.5.4 RISING EVENT DEAD-BAND

Rising event dead band delays the turn-on of the primary outputs from when complementary outputs are turned off. The rising event dead-band time starts when the rising\_ event output goes true.

See Section 18.5.1, Asynchronous Delay Chain Dead-band Delay and Section 18.5.2, Synchronous Counter Dead-band Delay for more information on setting the rising edge dead-band time.

#### 18.5.5 FALLING EVENT DEAD-BAND

Falling event dead band delays the turn-on of complementary outputs from when the primary outputs are turned off. The falling event dead-band time starts when the falling event output goes true.

See Section 18.5.1, Asynchronous Delay Chain Dead-band Delay and Section 18.5.2, Synchronous Counter Dead-band Delay for more information on setting the rising edge dead-band time.

#### 18.5.6 DEAD-BAND OVERLAP

There are two cases of dead-band overlap:

- Rising-to-falling

- Falling-to-rising

#### 18.5.6.1 Rising-to-Falling Overlap

In this case, the falling event occurs while the rising event dead-band counter is still counting. When this happens, the primary drives are suppressed and the dead-band extends by the falling event dead-band time. At the termination of the extended dead-band time, the complementary drive goes true.

#### 18.5.6.2 Falling-to-Rising Overlap

In this case, the rising event occurs while the falling event dead-band counter is still counting. When this happens, the complementary drive is suppressed and the dead-band extends by the rising event dead-band time. At the termination of the extended dead-band time, the primary drive goes true.

#### 18.6 Blanking Control

Input blanking is a function, whereby, the event inputs can be masked or blanked for a short period of time. This is to prevent electrical transients caused by the turn-on/off of power components from generating a false input event.

The COG contains two blanking counters: one triggered by the rising event and the other triggered by the falling event. The counters are cross coupled with the events they are blanking. The falling event blanking counter is used to blank rising input events and the rising event blanking counter is used to blank falling input events. Once started, blanking extends for the time specified by the corresponding blanking counter. Blanking is timed by counting COG\_clock periods from zero up to the value in the blanking count register. Use Equation 18-1 to calculate blanking times.

#### 18.6.1 FALLING EVENT BLANKING OF RISING EVENT INPUTS

The falling event blanking counter inhibits rising event inputs from triggering a rising event. The falling event blanking time starts when the rising event output drive goes false.

The falling event blanking time is set by the value contained in the COGxBLKF register (Register 18-13). Blanking times are calculated using the formula shown in Equation 18-1.

When the COGxBLKF value is zero, falling event blanking is disabled and the blanking counter output is true, thereby, allowing the event signal to pass straight through to the event trigger circuit.

#### 18.6.2 RISING EVENT BLANKING OF FALLING EVENT INPUTS

The rising event blanking counter inhibits falling event inputs from triggering a falling event. The rising event blanking time starts when the falling event output drive goes false.

The rising event blanking time is set by the value contained in the COGxBLKR register (Register 18-12).

When the COGxBLKR value is zero, rising event blanking is disabled and the blanking counter output is true, thereby, allowing the event signal to pass straight through to the event trigger circuit.

#### 18.6.3 BLANKING TIME UNCERTAINTY

When the rising and falling sources that trigger the blanking counters are asynchronous to the COG\_clock, it creates uncertainty in the blanking time. The maximum uncertainty is equal to one COG\_clock period. Refer to Equation 18-1 and Example 18-1 for more detail.

#### 18.7 Phase Delay

It is possible to delay the assertion of either or both the rising event and falling events. This is accomplished by placing a non-zero value in COGxPHR or COGxPHF phase-delay count register, respectively (Register 18-14 and Register 18-15). Refer to Figure 18-10 for COG operation with CCP1 and phase delay. The delay from the input rising event signal switching to the actual assertion of the events is calculated the same as the dead-band and blanking delays. Refer to Equation 18-1.

When the phase-delay count value is zero, phase delay is disabled and the phase-delay counter output is true, thereby, allowing the event signal to pass straight through to the complementary output driver flop.

<sup>© 2013-2016</sup> Microchip Technology Inc.

#### **REGISTER 20-3:** NCOxACCL: NCOx ACCUMULATOR REGISTER – LOW BYTE

| Logondi |         |         |         |         |         |         |         |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         |         |         |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         | NCOxA   | CC<7:0> |         |         |         |

| R/W-0/0 |

|         |         |         |         |         |         |         |         |

| Legena:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 NCOxACC<7:0>: NCOx Accumulator, Low Byte

#### REGISTER 20-4: NCOxACCH: NCOx ACCUMULATOR REGISTER – HIGH BYTE

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | NCOxAC  | C<15:8> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

| Legena.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 NCOxACC<15:8>: NCOx Accumulator, High Byte

#### REGISTER 20-5: NCOxACCU: NCOx ACCUMULATOR REGISTER – UPPER BYTE

| U-0   | U-0 | U-0 | U-0 | R/W-0/0        | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-------|-----|-----|-----|----------------|---------|---------|---------|--|

| —     | —   | —   | —   | NCOxACC<19:16> |         |         |         |  |

| bit 7 |     |     |     |                |         |         | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 NCOxACC<19:16>: NCOx Accumulator, Upper Byte

#### 22.3 Register Definitions: Op Amp Control

#### REGISTER 22-1: OPAxCON: OPERATIONAL AMPLIFIERS (OPAx) CONTROL REGISTERS

| R/W-0/0         R/W-0/0         U-0         R/W-0/0         U-0         R/W-0/0           OPAxEN         OPAxSP         —         OPAxUG         —         —         OPAxCH           bit 7 | R/W-0/0<br>I<1:0><br>bit 0 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| bit 7                                                                                                                                                                                       | -                          |

|                                                                                                                                                                                             | bit (                      |

| Legend:                                                                                                                                                                                     | DILL                       |

| Legend:                                                                                                                                                                                     |                            |

|                                                                                                                                                                                             |                            |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                                                                                                                        |                            |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all oth                                                                                                        | her Resets                 |

| '1' = Bit is set '0' = Bit is cleared q = Value depends on condition                                                                                                                        |                            |

|                                                                                                                                                                                             |                            |

| bit 7 OPAxEN: Op Amp Enable bit                                                                                                                                                             |                            |

| 1 = Op amp is enabled                                                                                                                                                                       |                            |

| 0 = Op amp is disabled and consumes no active power                                                                                                                                         |                            |

| bit 6 <b>OPAxSP:</b> Op Amp Speed/Power Select bit                                                                                                                                          |                            |

| 1 = Op amp operates in high GBWP mode                                                                                                                                                       |                            |

| 0 = Reserved. D not use.                                                                                                                                                                    |                            |

| bit 5 Unimplemented: Read as '0'                                                                                                                                                            |                            |

| bit 4 OPAxUG: Op Amp Unity Gain Select bit                                                                                                                                                  |                            |

| <ul> <li>1 = OPA output is connected to inverting input. OPAxIN- pin is available for general purp</li> <li>0 = Inverting input is connected to the OPAxIN- pin</li> </ul>                  | ose I/O.                   |

| bit 3-2 Unimplemented: Read as '0'                                                                                                                                                          |                            |

| bit 1-0 OPAxCH<1:0>: Non-inverting Channel Selection bits                                                                                                                                   |                            |

| 11 = Non-inverting input connects to FVR Buffer 2 output                                                                                                                                    |                            |

| 10 = Non-inverting input connects to DAC1_output                                                                                                                                            |                            |

| 01 = Non-inverting input connects to DAC2_output                                                                                                                                            |                            |

| 00 = Non-inverting input connects to OPAxIN+ pin                                                                                                                                            |                            |

#### TABLE 22-1: SUMMARY OF REGISTERS ASSOCIATED WITH OP AMPS

| Name     | Bit 7        | Bit 6  | Bit 5   | Bit 4   | Bit 3  | Bit 2            | Bit 1                       | Bit 0   | Register<br>on Page |  |

|----------|--------------|--------|---------|---------|--------|------------------|-----------------------------|---------|---------------------|--|

| ANSELA   | —            | —      | ANSA    | ANSA4   | ANSA3  | ANSA2            | ANSA1                       | ANSA0   | 120                 |  |

| ANSELB   | _            | _      | ANSB5   | ANSB4   | ANSB3  | ANSB2            | ANSB1                       | ANSB0   | 126                 |  |

| DAC1CON0 | DAC1EN       | -      | DAC10E1 | DAC10E2 | DAC1PS | SS<1:0>          | <ul> <li>DAC1NSS</li> </ul> |         | 249                 |  |

| DAC1CON1 | 1 DAC1R<7:0> |        |         |         |        |                  |                             |         |                     |  |

| FVRCON   | FVREN        | FVRRDY | TSEN    | TSRNG   | CDAFV  | 'R<1:0>          | ADFV                        | R<1:0>  | 151                 |  |

| OPA1CON  | OPA1EN       | OPA1SP | _       | OPA1UG  | _      | _                | OPA1P0                      | CH<1:0> | 245                 |  |

| OPA2CON  | OPA2EN       | OPA2SP | —       | OPA2UG  | _      | — — OPA2PCH<1:0> |                             |         |                     |  |

| TRISA    | TRISB7       | TRISB6 | TRISB5  | TRISB4  | TRISB3 | TRISB2           | TRISB1                      | TRISB0  | 119                 |  |

| TRISB    | TRISC7       | TRISC6 | TRISC5  | TRISC4  | TRISC3 | TRISC2           | TRISC1                      | TRISC0  | 125                 |  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by op amps.

### 23.6 Register Definitions: DAC Control

| REGISTER         | 23-1: DAC10                                                             | CONU: VOLT                                                 | AGE REFER                            | ENCE CON        | ROL REGIS          | IERU             |          |

|------------------|-------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------|-----------------|--------------------|------------------|----------|

| R/W-0/0          | U-0                                                                     | R/W-0/0                                                    | R/W-0/0                              | R/W-0/0         | R/W-0/0            | U-0              | R/W-0/0  |

| DAC1EN           | _                                                                       | DAC10E1                                                    | DAC10E2                              | DAC1P           | 2SS<1:0>           | —                | DAC1NSS  |

| bit 7            |                                                                         | •                                                          |                                      |                 |                    |                  | bit (    |

| Legend:          |                                                                         |                                                            |                                      |                 |                    |                  |          |

| R = Readable b   | oit                                                                     | W = Writable b                                             | it                                   | U = Unimpleme   | ented bit, read as | '0'              |          |

| u = Bit is uncha | anged                                                                   | x = Bit is unkno                                           | own                                  | -n/n = Value at | POR and BOR/V      | alue at all othe | r Resets |

| '1' = Bit is set |                                                                         | '0' = Bit is clear                                         | red                                  |                 |                    |                  |          |

| bit 6<br>bit 5   | 1 = DAC volta                                                           | sabled                                                     | an output on the                     | •               |                    |                  |          |

| bit 4            | <b>DAC10E2:</b> DA<br>1 = DAC volta                                     | C1 Voltage Outp<br>ge level is also a<br>ge level is disco | out 2 Enable bit<br>an output on the | DAC1OUT2 pin    |                    |                  |          |

| bit 3-2          | DAC1PSS<1:0<br>11 = Reserve<br>10 = FVR Buf<br>01 = VREF+ p<br>00 = VDD | fer2 output                                                | e Source Select                      | bits            |                    |                  |          |

| bit 1            | Unimplemente                                                            | ed: Read as '0'                                            |                                      |                 |                    |                  |          |

| bit 0            | <b>DAC1NSS:</b> DA<br>1 = VREF- pin<br>0 = VSS                          | C1 Negative So                                             | urce Select bits                     |                 |                    |                  |          |

#### REGISTER 23-1: DAC1CON0: VOLTAGE REFERENCE CONTROL REGISTER 0

#### REGISTER 23-2: DAC1CON1: VOLTAGE REFERENCE CONTROL REGISTER 1

| R/W-0/0 |  |  |

|---------|---------|---------|---------|---------|---------|---------|---------|--|--|

|         |         |         | DAC1    | R<7:0>  |         |         |         |  |  |

| bit 7   |         |         |         |         |         |         |         |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 DAC1R<7:0>: DAC1 Voltage Output Select bits

#### TABLE 23-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC1 MODULE

| Name     | Bit 7      | Bit 6 | Bit 5   | Bit 4   | Bit 3  | Bit 2   | Bit 1 | Bit 0   | Register<br>on page |  |

|----------|------------|-------|---------|---------|--------|---------|-------|---------|---------------------|--|

| DAC1CON0 | DAC1EN     | _     | DAC10E1 | DAC10E2 | DAC1PS | SS<1:0> |       | DAC1NSS | 249                 |  |

| DAC1CON1 | DAC1R<7:0> |       |         |         |        |         |       |         |                     |  |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used with the DAC module.

#### 26.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

#### 26.4 Timer1 (Secondary) Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins SOSCI (input) and SOSCO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OS-CEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to using Timer1. A suitable delay similar to the OST delay can be implemented in software by clearing the TMR1IF bit then presetting the TMR1H:TMR1L register pair to FC00h. The TMR1IF flag will be set when 1024 clock cycles have elapsed, thereby indicating that the oscillator is running and reasonably stable.

#### 26.5 Timer1 Operation in Asynchronous Counter Mode

If the control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 26.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

#### 26.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

#### 26.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

#### 26.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 26-3 for timing details.

TABLE 26-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| $\uparrow$ | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| 1          | 1      | 1   | Counts           |

#### 28.9 Register Definitions: ZCD Control

#### REGISTER 28-1: ZCDxCON: ZERO-CROSS DETECTION CONTROL REGISTER

| R/W-0/0                                                                                                                            | U-0                                                               | R-x/x                           | R/W-0/0        | U-0              | U-0             | R/W-0/0                             | R/W-0/0     |  |

|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------|----------------|------------------|-----------------|-------------------------------------|-------------|--|

| ZCDxEN                                                                                                                             | _                                                                 | ZCDxOUT                         | ZCDxPOL        | _                | _               | ZCDxINTP                            | ZCDxINTN    |  |

| bit 7                                                                                                                              |                                                                   |                                 |                |                  |                 |                                     | bit 0       |  |

|                                                                                                                                    |                                                                   |                                 |                |                  |                 |                                     |             |  |

| Legend:                                                                                                                            |                                                                   |                                 |                |                  |                 |                                     |             |  |

| R = Readable                                                                                                                       | bit                                                               | W = Writable                    | bit            | U = Unimpler     | mented bit, rea | d as '0'                            |             |  |

| u = Bit is uncha                                                                                                                   | anged                                                             | x = Bit is unkr                 | nown           | -n/n = Value     | at POR and BO   | OR/Value at all o                   | ther Resets |  |

| '1' = Bit is set                                                                                                                   |                                                                   | '0' = Bit is clea               | ared           | q = value dep    | pends on config | guration bits                       |             |  |

|                                                                                                                                    |                                                                   |                                 |                |                  |                 |                                     |             |  |

| bit 7                                                                                                                              | ZCDxEN: Zer                                                       | o-Cross Detec                   | tion Enable bi | t(1)             |                 |                                     |             |  |

|                                                                                                                                    |                                                                   |                                 |                |                  |                 | e and sink currer<br>and TRIS contr |             |  |

| bit 6                                                                                                                              | Unimplemen                                                        | ted: Read as '                  | כ'             |                  |                 |                                     |             |  |

| bit 5                                                                                                                              | ZCDxOUT: Ze                                                       | ero-Cross Dete                  | ction Logic Le | evel bit         |                 |                                     |             |  |

|                                                                                                                                    | ZCDxPOL bit                                                       | <u>= 0</u> :                    |                |                  |                 |                                     |             |  |

|                                                                                                                                    |                                                                   | is sinking curre                |                |                  |                 |                                     |             |  |

|                                                                                                                                    | 0 = ZCD pin<br>ZCDxPOL bit                                        | is sourcing cur                 | rent           |                  |                 |                                     |             |  |

|                                                                                                                                    |                                                                   | <u>−</u> ⊥.<br>is sourcing curi | rent           |                  |                 |                                     |             |  |

|                                                                                                                                    |                                                                   | is sinking curre                |                |                  |                 |                                     |             |  |

| bit 4                                                                                                                              | ZCDxPOL: Ze                                                       | ero-Cross Dete                  | ection Logic O | utput Polarity I | oit             |                                     |             |  |

|                                                                                                                                    | 0                                                                 | c output is inve                |                |                  |                 |                                     |             |  |

|                                                                                                                                    | •                                                                 | c output is not i               |                |                  |                 |                                     |             |  |

| bit 3-2                                                                                                                            | -                                                                 | ted: Read as '                  |                |                  |                 |                                     |             |  |

| bit 1                                                                                                                              |                                                                   | ero-Cross Pos                   | •              | •                |                 |                                     |             |  |

| 1 = ZCDIF bit is set on low-to-high ZCDx_output transition                                                                         |                                                                   |                                 |                |                  |                 |                                     |             |  |

| hit 0                                                                                                                              | 0 = ZCDIF bit is unaffected by low-to-high ZCDx_output transition |                                 |                |                  |                 |                                     |             |  |

| bit 0 <b>ZCDxINTN:</b> Zero-Cross Negative Edge Interrupt Enable bit<br>1 = ZCDIF bit is set on high-to-low ZCDx output transition |                                                                   |                                 |                |                  |                 |                                     |             |  |

|                                                                                                                                    |                                                                   | t is unaffected                 |                |                  |                 |                                     |             |  |

| Note 1: The                                                                                                                        | ZCDxEN bit ha                                                     |                                 |                |                  |                 | d.                                  |             |  |

|                                                                                                                                    |                                                                   |                                 |                | <u> </u>         |                 |                                     |             |  |

| Name    | Bit 7  | Bit 6 | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1    | Bit 0    | Register<br>on page |

|---------|--------|-------|---------|---------|-------|-------|----------|----------|---------------------|

| PIE3    | —      | _     | COGIE   | ZCDIE   | _     | —     | —        | —        | 86                  |

| PIR3    | _      | _     | CWGIF   | ZCDIF   | _     | _     | —        | _        | 89                  |

| ZCD1CON | ZCD1EN |       | ZCD10UT | ZCD1POL | _     |       | ZCD1INTP | ZCD1INTN | 276                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the ZCD module.

#### TABLE 28-2: SUMMARY OF CONFIGURATION WORD WITH THE ZCD MODULE

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

| CONFIG2 | 13:8 |         |         | LVP      | DEBUG    | LPBOR    | BORV     | STVREN  | PLLEN   | 49                  |

|         | 7:0  | ZCDDIS  |         | _        | _        | -        | _        | WRT     | <1:0>   |                     |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the ZCD module.

#### 34.3 DC Characteristics

#### TABLE 34-1:SUPPLY VOLTAGE

| PIC16LF       | 1713/6 |                                                | Standard Operating Conditions (unless otherwise stated) |      |                      |        |                                                              |  |  |  |  |  |

|---------------|--------|------------------------------------------------|---------------------------------------------------------|------|----------------------|--------|--------------------------------------------------------------|--|--|--|--|--|

| PIC16F1       | 713/6  |                                                |                                                         |      |                      |        |                                                              |  |  |  |  |  |

| Param.<br>No. | Sym.   | Characteristic                                 | Min.                                                    | Тур† | Max.                 | Units  | Conditions                                                   |  |  |  |  |  |

| D001          | Vdd    | Supply Voltage                                 |                                                         |      |                      |        |                                                              |  |  |  |  |  |

|               |        |                                                | VDDMIN<br>1.8<br>2.5                                    | _    | VDDMAX<br>3.6<br>3.6 | V<br>V | Fosc ≤ 16 MHz<br>Fosc > 16 MHz ( <b>Note 2</b> )             |  |  |  |  |  |

| D001          |        |                                                | 2.3<br>2.5                                              | _    | 5.5<br>5.5           | V<br>V | Fosc ≤ 16 MHz:<br>Fosc > 16 MHz ( <b>Note 2</b> )            |  |  |  |  |  |

| D002*         | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>      |                                                         |      |                      |        | 1                                                            |  |  |  |  |  |

|               |        |                                                | 1.5                                                     | —    | —                    | V      | Device in Sleep mode                                         |  |  |  |  |  |

| D002*         |        |                                                | 1.7                                                     | _    |                      | V      | Device in Sleep mode                                         |  |  |  |  |  |

| D002A*        | VPOR   | Power-on Reset Release Voltage <sup>(3)</sup>  |                                                         |      |                      |        |                                                              |  |  |  |  |  |

|               |        |                                                | —                                                       | 1.6  | _                    | V      |                                                              |  |  |  |  |  |

| D002A*        |        |                                                | —                                                       | 1.6  |                      | V      |                                                              |  |  |  |  |  |

| D002B*        | VPORR* | Power-on Reset Rearm Voltage <sup>(3)</sup>    |                                                         |      |                      |        |                                                              |  |  |  |  |  |

|               |        |                                                | —                                                       | 0.8  | _                    | V      |                                                              |  |  |  |  |  |

| D002B*        |        |                                                | —                                                       | 1.5  |                      | V      |                                                              |  |  |  |  |  |

|               |        |                                                | -4                                                      | _    | +4                   | %      | 1x Gain, 1.024, VDD ≥ 2.5V, -40°C to 85°C                    |  |  |  |  |  |

| D003          | Vfvr   | Fixed Voltage Reference Voltage <sup>(4)</sup> | -4                                                      | _    | +4                   | %      | 2x Gain, 2.048, VDD ≥ 2.5V, -40°C to 85°C                    |  |  |  |  |  |

|               |        |                                                | -5                                                      | _    | +5                   | %      | 4x Gain, 4.096, VDD $\geq$ 4.75V, -40°C to 85°C              |  |  |  |  |  |

| D004*         | SVDD   | VDD Rise Rate                                  | 0.05                                                    | _    | —                    | V/ms   | Ensures that the Power-on Reset signal is released properly. |  |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

2: PLL required for 32 MHz operation.

3: See Figure 34-3: POR and POR Rearm with Slow Rising VDD.

4: Industrial temperature range only.

### TABLE 34-15: ANALOG-TO-DIGITAL CONVERTER (ADC) CHARACTERISTICS<sup>(1,2,3,4)</sup>:

| <b>Operating Conditions (unless otherwise stated)</b><br>VDD = 3.0V, TA = 25°C, Single-ended, 2 μs TAD, VREF+ = 3V, VREF- = Vss |      |                                                   |      |      |      |       |                                                                           |  |  |

|---------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------|------|------|------|-------|---------------------------------------------------------------------------|--|--|

| Param<br>No.                                                                                                                    | Sym. | Characteristic                                    | Min. | Тур† | Max. | Units | Conditions                                                                |  |  |

| AD01                                                                                                                            | NR   | Resolution                                        | -    |      | 10   | bit   |                                                                           |  |  |

| AD02                                                                                                                            | EIL  | Integral Error                                    | —    | —    | ±1.7 | LSb   | VREF = 3.0V                                                               |  |  |

| AD03                                                                                                                            | Edl  | Differential Error                                | —    | _    | ±1   | LSb   | No missing codes, VREF = 3.0V                                             |  |  |

| AD04                                                                                                                            | EOFF | Offset Error                                      | —    | _    | ±2.5 | LSb   | VREF = 3.0V                                                               |  |  |

| AD05                                                                                                                            | Egn  | Gain Error                                        | —    | _    | ±2.0 | LSb   | VREF = 3.0V                                                               |  |  |

| AD06                                                                                                                            | VREF | Reference Voltage                                 | 1.8  | _    | Vdd  | V     | VREF = (VREF+ minus VREF-)                                                |  |  |

| AD07                                                                                                                            | VAIN | Full-Scale Range                                  | Vss  |      | VREF | V     |                                                                           |  |  |

| AD08                                                                                                                            | Zain | Recommended Impedance of<br>Analog Voltage Source | —    | —    | 10   | kΩ    | Can go higher if external 0.01 $\mu$ F capacitor is present on input pin. |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Total Absolute Error includes integral, differential, offset and gain errors.

2: The ADC conversion result never decreases with an increase in the input voltage and has no missing codes.

- 3: ADC VREF is from external VREF+ pin, VDD pin or FVR, whichever is selected as reference input.

- 4: See Section 35.0 "DC and AC Characteristics Graphs and Charts" for operating characterization.

#### TABLE 34-16: ADC CONVERSION REQUIREMENTS

| Standar      | Standard Operating Conditions (unless otherwise stated) |                                                                 |      |                |      |       |                                        |  |  |  |  |

|--------------|---------------------------------------------------------|-----------------------------------------------------------------|------|----------------|------|-------|----------------------------------------|--|--|--|--|

| Param<br>No. | Sym.                                                    | Characteristic                                                  | Min. | Тур†           | Max. | Units | Conditions                             |  |  |  |  |

| AD130*       | TAD                                                     | ADC Clock Period (TADC)                                         | 1.0  | —              | 9.0  | μS    | Fosc-based                             |  |  |  |  |

|              |                                                         | ADC Internal FRC Oscillator Period<br>(TFRC)                    | 1.0  | 2              | 6.0  | μS    | ADCS<1:0> = 11 (ADC FRC mode)          |  |  |  |  |

| AD131        | TCNV                                                    | Conversion Time (not including Acquisition Time) <sup>(1)</sup> | —    | 11             | —    | Tad   | Set GO/DONE bit to conversion complete |  |  |  |  |

| AD132*       | TACQ                                                    | Acquisition Time                                                | _    | 5.0            |      | μS    |                                        |  |  |  |  |

| AD133*       | THCD                                                    | Holding Capacitor Disconnect Time                               | —    | 1/2 TAD        | _    |       | ADCS<2:0> ≠ x11 (Fosc based)           |  |  |  |  |

|              |                                                         |                                                                 | —    | 1/2 TAD + 1TCY |      |       | ADCS<2:0> = x11 (FRC based)            |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The ADRES register may be read on the following TCY cycle.

Note: Unless otherwise noted, VIN = 5V, Fosc = 300 kHz, CIN = 0.1  $\mu$ F, TA = 25°C.

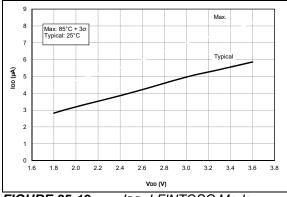

FIGURE 35-19: IDD, LFINTOSC Mode, Fosc = 31 kHz, PIC16LF1713/6 Only.

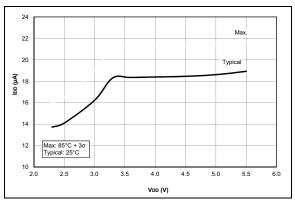

FIGURE 35-20: IDD, LFINTOSC Mode, Fosc = 31 kHz, PIC16F1713/6 Only.

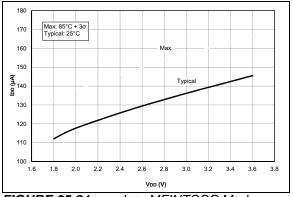

FIGURE 35-21: IDD, MFINTOSC Mode, Fosc = 500 kHz, PIC16LF1713/6 Only.

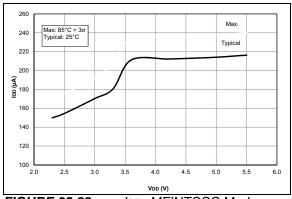

FIGURE 35-22: IDD, MFINTOSC Mode, Fosc = 500 kHz, PIC16F1713/6 Only.

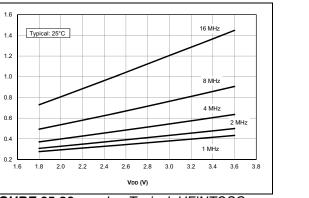

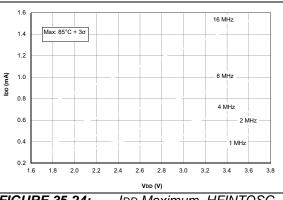

FIGURE 35-23: IDD Typical, HFINTOSC Mode, PIC16LF1713/6 Only.

FIGURE 35-24: IDD Maximum, HFINTOSC Mode, PIC16LF1713/6 Only.

(MM) aal

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, flexPWR, JukeBlox, KEELoQ, KEELoQ logo, Kleer, LANCheck, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC<sup>32</sup> logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

The Embedded Control Solutions Company and mTouch are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, ECAN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, RightTouch logo, REAL ICE, SQI, Serial Quad I/O, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2013-2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0172-8

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.