#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

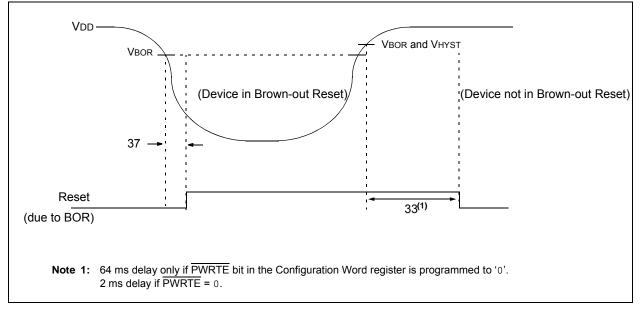

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 14KB (8K x 14)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 17x10b; D/A 1x5b, 1x8b                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1716t-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                    |    |    |      |       | Comparator |  |     | Timers |       | 900  | 3    |         | DIMM    |         |       | 900    |       |                    | MSSP                   |     | FIISART |                  |         | ر<br>د  |         |     |   |             |

|--------------------|----|----|------|-------|------------|--|-----|--------|-------|------|------|---------|---------|---------|-------|--------|-------|--------------------|------------------------|-----|---------|------------------|---------|---------|---------|-----|---|-------------|

| RC4                | 15 | 12 | AN16 |       |            |  |     |        |       |      |      |         |         |         |       |        |       |                    | SDI<br>SDA             |     |         |                  |         |         |         | IOC | Υ |             |

| RC5                | 16 | 13 | AN17 |       |            |  |     |        |       |      |      |         |         |         |       |        |       |                    |                        |     |         |                  |         |         |         | IOC | Υ |             |

| RC6                | 17 | 14 | AN18 |       |            |  |     |        |       |      |      |         |         |         |       |        |       |                    |                        |     | Ck      |                  |         |         |         | IOC | Υ |             |

| RC7                | 18 | 15 | AN19 |       |            |  |     |        |       |      |      |         |         |         |       |        |       |                    |                        |     | R۷      | < <sup>(3)</sup> |         |         |         | IOC | Υ |             |

| RE3                | 1  | 26 |      |       |            |  |     |        |       |      |      |         |         |         |       |        |       |                    |                        |     |         |                  |         |         |         | IOC | Y | MCLR<br>Vpp |

| Vdd                | 20 | 17 |      |       |            |  |     |        |       |      |      |         |         |         |       |        |       |                    |                        |     |         |                  |         |         |         |     |   | Vdd         |

| Vss                | 8  | 5  |      |       |            |  |     |        |       |      |      |         |         |         |       |        |       |                    |                        |     |         |                  |         |         |         |     |   | Vss         |

| 100                | 19 | 16 |      |       |            |  |     |        |       |      |      |         |         |         |       |        |       |                    |                        |     |         |                  |         |         |         |     |   |             |

| OUT <sup>(4)</sup> |    |    |      | C10UT | C20UT      |  |     |        |       | CCP1 | CCP2 | NCO10UT | PWM30UT | PWM40UT | COG1A | COG1B  | COG1D | SDA <sup>(3)</sup> | SCK/SCL <sup>(3)</sup> | SDO | TX/CK   | DT(3)            | CLC40UT | CLC30UT | CLC2OUT |     |   |             |

| IN <sup>(5)</sup>  |    |    |      |       |            |  | 116 | T1CKI  | TOCKI | CCP1 | CCP2 |         |         |         |       | COG1IN |       | SDI                | SCK/SCL <sup>(3)</sup> | SS  | RX(3)   | СК               | CLCINO  | CLCIN1  | CLCIN2  | INT |   |             |

Note 1: Default peripheral input. Alternate pins can be selected as the peripheral input with the PPS input selection registers.

2: All pin digital outputs default to PORT latch data. Alternate outputs can be selected as the peripheral digital output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: Alternate outputs are excluded from solid shaded areas.

5: Alternate inputs are excluded from dot shaded areas.

#### 1.0 DEVICE OVERVIEW

The PIC16(L)F1713/6 are described within this data sheet. They are available in 28-pin SPDIP, SSOP, SOIC, QFN, and UQFN packages. Figure 1-1 shows a block diagram of the PIC16(L)F1713/6 devices. Table 1-2 shows the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

#### TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| Peripheral                                               |                                       | PIC16(L)F1713 | PIC16(L)F1716 |

|----------------------------------------------------------|---------------------------------------|---------------|---------------|

| Analog-to-Digital Converter                              | (ADC)                                 | ٠             | •             |

| Complementary Output Gene                                | erator (COG)                          | •             | •             |

| Fixed Voltage Reference (FV                              | /R)                                   | •             | •             |

| Zero-Cross Detection (ZCD)                               |                                       | •             | •             |

| Temperature Indicator                                    |                                       | •             | •             |

| Numerically Controlled Osci                              | llator (NCO)                          | •             | •             |

| Digital-to-Analog Converter                              | (DAC)                                 |               |               |

|                                                          | DAC1                                  | •             | •             |

|                                                          | DAC2                                  | •             | •             |

| Capture/Compare/PWM (CC                                  | P/ECCP) Mod                           | ules          |               |

|                                                          | CCP1                                  | ٠             | •             |

|                                                          | CCP2                                  | •             | •             |

| Comparators                                              |                                       |               |               |

|                                                          | C1                                    | ٠             | •             |

|                                                          | C2                                    | ٠             | •             |

| Configurable Logic Cell (CL                              | C)                                    | 0             |               |

|                                                          | CLC1                                  | •             | •             |

|                                                          | CLC2                                  | •             | •             |

|                                                          | CLC3                                  | •             | •             |

|                                                          | CLC4                                  | •             | •             |

| Enhanced Universal Synchro<br>Receiver/Transmitter (EUSA |                                       | nous          |               |

|                                                          | EUSART                                | ٠             | •             |

| Master Synchronous Serial                                | Ports                                 |               |               |

|                                                          | MSSP                                  | ٠             | •             |

| Op Amp                                                   |                                       |               |               |

|                                                          | Op Amp 1                              | •             | •             |

|                                                          | Op Amp 2                              | •             | •             |

| Pulse Width Modulator (PW                                | -                                     |               |               |

|                                                          | PWM3                                  | •             | •             |

|                                                          | PWM4                                  | •             | •             |

| Timers                                                   | · · · · · · · · · · · · · · · · · · · |               |               |

|                                                          | Timer0                                | •             | •             |

|                                                          | Timer1                                | ٠             | ٠             |

|                                                          | Timer2                                | •             | •             |

#### 6.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

| Note: | Executing a SLEEP instruction will abort    |

|-------|---------------------------------------------|

|       | the oscillator start-up time and will cause |

|       | the OSTS bit of the OSCSTAT register to     |

|       | remain clear.                               |

#### 6.4.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Words) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 00.

- FOSC<2:0> bits in the Configuration Words configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- Wake-up from Sleep.

| TABLE 6-1: | OSCILLATOR SWITCHING DELAYS |

|------------|-----------------------------|

|------------|-----------------------------|

| Switch From      | Switch To                                                                     | Frequency                                       | Oscillator Delay                                                                                          |

|------------------|-------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Sleep            | LFINTOSC <sup>(1)</sup><br>MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup> | 31 kHz<br>31.25 kHz-500 kHz<br>31.25 kHz-16 MHz | Oscillator Warm-up Delay (TLFOSC ST) <sup>(2)</sup><br>Oscillator Warm-up Delay (Tlosc ST) <sup>(2)</sup> |

| Sleep/POR        | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 2 cycles                                                                                                  |

| LFINTOSC         | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 1 cycle of each                                                                                           |

| Sleep/POR        | Secondary Oscillator<br>LP, XT, HS <sup>(1)</sup>                             | 32 kHz-20 MHz                                   | 1024 Clock Cycles (OST)                                                                                   |

| Any clock source | MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup>                            | 31.25 kHz-500 kHz<br>31.25 kHz-16 MHz           | 2 μs (approx.)                                                                                            |

| Any clock source | LFINTOSC <sup>(1)</sup>                                                       | 31 kHz                                          | 1 cycle of each                                                                                           |

| Any clock source | Secondary Oscillator                                                          | 32 kHz                                          | 1024 Clock Cycles (OST)                                                                                   |

| PLL inactive     | PLL active                                                                    | 16-32 MHz                                       | 2 ms (approx.)                                                                                            |

Note 1: PLL inactive.

2: See Section 34.0 "Electrical Specifications".

#### TABLE 9-2: WDT CLEARING CONDITIONS

| Conditions                                               | WDT                          |  |  |

|----------------------------------------------------------|------------------------------|--|--|

| WDTE<1:0> = 00                                           |                              |  |  |

| WDTE<1:0> = 01 and SWDTEN = 0                            |                              |  |  |

| WDTE<1:0> = 10 and enter Sleep                           | Cleared                      |  |  |

| CLRWDT Command                                           | Cleared                      |  |  |

| Oscillator Fail Detected                                 |                              |  |  |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |  |  |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |  |  |

| Change INTOSC divider (IRCF bits)                        | Unaffected                   |  |  |

#### 10.3 Modifying Flash Program Memory

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- 1. Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- 4. Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- 6. Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

### MEMORY MODIFY FLOWCHART Start Modify Operation **Read Operation** Figure 10-1 An image of the entire row read must be stored in RAM Modify Image The words to be modified are changed in the RAM image Erase Operation Figure 10-4 Write Operation use RAM image Figure 10-6 End Modify Operation

**FLASH PROGRAM**

**FIGURE 10-7:**

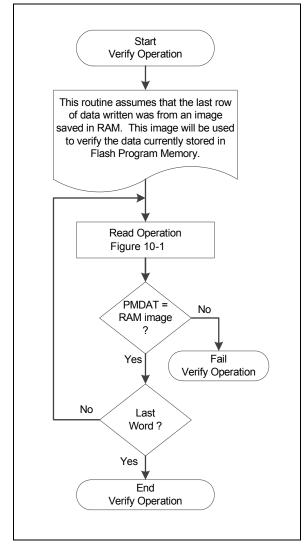

#### 10.5 Write Verify

It is considered good programming practice to verify that program memory writes agree with the intended value. Since program memory is stored as a full page then the stored program memory contents are compared with the intended data stored in RAM after the last write is complete.

FIGURE 10-8: FLASH PROGRAM MEMORY VERIFY FLOWCHART

'1' = Bit is set

| R/W-1/1                                                                          | R/W-1/1                           | R/W-1/1 | R/W-1/1 | R/W-1/1                            | R/W-1/1 | R/W-1/1      | R/W-1/1 |  |  |  |

|----------------------------------------------------------------------------------|-----------------------------------|---------|---------|------------------------------------|---------|--------------|---------|--|--|--|

| SLRA7                                                                            | SLRA6                             | SLRA5   | SLRA4   | SLRA3                              | SLRA2   | SLRA1        | SLRA0   |  |  |  |

| bit 7 bit 0                                                                      |                                   |         |         |                                    |         |              |         |  |  |  |

| Logondy                                                                          |                                   |         |         |                                    |         |              |         |  |  |  |

| Legend:                                                                          |                                   |         |         |                                    |         |              |         |  |  |  |

| R = Readable                                                                     | R = Readable bit W = Writable bit |         |         | U = Unimplemented bit, read as '0' |         |              |         |  |  |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all |                                   |         |         |                                    |         | other Resets |         |  |  |  |

#### REGISTER 11-7: SLRCONA: PORTA SLEW RATE CONTROL REGISTER

bit 7-0 SLRA<7:0>: PORTA Slew Rate Enable bits For RA<7:0> pins, respectively 1 = Port pin slew rate is limited 0 = Port pin slews at maximum rate

#### REGISTER 11-8: INLVLA: PORTA INPUT LEVEL CONTROL REGISTER

'0' = Bit is cleared

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 75-0 INLVLA<7:0>: PORTA Input Level Select bits For RA<7:0> pins, respectively 1 = ST input used for PORT reads and interrupt-on-change

0 = TTL input used for PORT reads and interrupt-on-change

#### 11.6 Register Definitions: PORTC

#### REGISTER 11-17: PORTC: PORTC REGISTER

| R/W-x/u           | R/W-x/u | R/W-x/u            | R/W-x/u | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |  |  |  |  |

|-------------------|---------|--------------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|--|--|

| RC7               | RC6     | RC5                | RC4     | RC3                                                   | RC2     | RC1     | RC0     |  |  |  |  |

| bit 7             |         |                    |         |                                                       |         |         | bit 0   |  |  |  |  |

|                   |         |                    |         |                                                       |         |         |         |  |  |  |  |

| Legend:           |         |                    |         |                                                       |         |         |         |  |  |  |  |

| R = Readable bi   | it      | W = Writable bi    | it      | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |  |  |

| u = Bit is unchar | nged    | x = Bit is unkno   | wn      | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |  |  |

| '1' = Bit is set  |         | '0' = Bit is clear | red     |                                                       |         |         |         |  |  |  |  |

bit 7-0

RC<7:0>: PORTC General Purpose I/O Pin bits<sup>(1)</sup>

1 = Port pin is

VIH

0 = Port pin is

VIL

#### REGISTER 11-18: TRISC: PORTC TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

TRISC<7:0>: PORTC Tri-State Control bits

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

#### REGISTER 11-19: LATC: PORTC DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATC7   | LATC6   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATC<7:0>: PORTC Output Latch Value bits

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

© 2013-2016 Microchip Technology Inc.

#### 17.1.5 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is 10 bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 17-4.

#### EQUATION 17-4: PWM RESOLUTION

Resolution =  $\frac{\log[4(PR2 + 1)]}{\log(2)}$  bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

| TABLE 17-1: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 M |

|------------------------------------------------------------------|

|------------------------------------------------------------------|

| <b>PWM Frequency</b>      | 0.31 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 17-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 0.31 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 17.1.6 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the PWMx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 17.1.7 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency (Fosc). Any changes in the system clock frequency will result in changes to the PWM frequency. Refer to Section 6.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

#### 17.1.8 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the PWM registers to their Reset states.

| R/W-0/0         | R/W-0/0   | R/W-0/0                                | R/W-0/0         | R/W-0/0                               | R/W-0/0                | R/W-0/0           | R/W-0/0    |

|-----------------|-----------|----------------------------------------|-----------------|---------------------------------------|------------------------|-------------------|------------|

| GxDATD          | GxDATC    | GxDATB                                 | GxDATA          | GxSTRD                                | GxSTRC                 | GxSTRB            | GxSTRA     |

| bit 7           | -<br>-    |                                        |                 | •<br>                                 | •                      |                   | bit (      |

| Legend:         |           |                                        |                 |                                       |                        |                   |            |

| R = Readabl     | e bit     | W = Writable                           | bit             | U = Unimplem                          | ented bit, read        | as '0'            |            |

| u = Bit is und  | changed   | x = Bit is unkr                        | nown            | -n/n = Value at                       | POR and BOF            | R/Value at all ot | her Resets |

| '1' = Bit is se | et        | '0' = Bit is clea                      | ared            | q = Value depe                        | ends on conditi        | on                |            |

|                 |           |                                        |                 |                                       |                        |                   |            |

| bit 7           |           | COGxD Static C                         | •               |                                       |                        |                   |            |

|                 |           | static data is hi<br>static data is lo | 0               |                                       |                        |                   |            |

| bit 6           |           | COGxC Static C                         |                 |                                       |                        |                   |            |

|                 |           | static data is hi                      |                 |                                       |                        |                   |            |

|                 |           | static data is lo                      |                 |                                       |                        |                   |            |

| bit 5           | GxSDATB:  | COGxB Static C                         | Output Data bit |                                       |                        |                   |            |

|                 |           | static data is hi                      | •               |                                       |                        |                   |            |

|                 |           | static data is lo                      |                 |                                       |                        |                   |            |

| bit 4           |           | COGxA Static C                         | •               |                                       |                        |                   |            |

|                 |           | static data is hi<br>static data is lo |                 |                                       |                        |                   |            |

| bit 3           |           | OGxD Steering                          |                 |                                       |                        |                   |            |

|                 |           | -                                      |                 | orm with polarity                     | control from C         | SxPOLD bit        |            |

|                 |           |                                        |                 | letermined by th                      |                        |                   |            |

| bit 2           | GxSTRC: C | OGxC Steering                          | Control bit     |                                       |                        |                   |            |

|                 |           |                                        |                 | orm with polarity                     |                        |                   |            |

|                 |           | •                                      |                 | letermined by th                      | ie GxSDATC b           | it                |            |

| bit 1           |           | OGxB Steering                          |                 |                                       | , a a ratural frame. C |                   |            |

|                 |           |                                        |                 | orm with polarity<br>letermined by th |                        |                   |            |

| bit 0           |           | OGxA Steering                          |                 |                                       |                        | -                 |            |

|                 |           |                                        |                 | orm with polarity                     | control from G         | xPOLA bit         |            |

|                 | 0 = COGxA |                                        |                 |                                       |                        |                   |            |

#### REGISTER 18-9: COGxSTR: COG STEERING CONTROL REGISTER 1

#### **REGISTER 20-3:** NCOxACCL: NCOx ACCUMULATOR REGISTER – LOW BYTE

| Logondi      |         |         |         |         |         |         |         |  |  |

|--------------|---------|---------|---------|---------|---------|---------|---------|--|--|

|              |         |         |         |         |         |         |         |  |  |

| bit 7        |         |         |         |         |         |         | bit 0   |  |  |

| NCOxACC<7:0> |         |         |         |         |         |         |         |  |  |

| R/W-0/0      | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|              |         |         |         |         |         |         |         |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 NCOxACC<7:0>: NCOx Accumulator, Low Byte

#### REGISTER 20-4: NCOxACCH: NCOx ACCUMULATOR REGISTER – HIGH BYTE

| R/W-0/0       | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|---------------|---------|---------|---------|---------|---------|---------|---------|--|

| NCOxACC<15:8> |         |         |         |         |         |         |         |  |

| bit 7         |         |         |         |         |         |         | bit 0   |  |

|               |         |         |         |         |         |         |         |  |

| Legend:       |         |         |         |         |         |         |         |  |

| Legena.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 NCOxACC<15:8>: NCOx Accumulator, High Byte

#### REGISTER 20-5: NCOxACCU: NCOx ACCUMULATOR REGISTER – UPPER BYTE

| U-0   | U-0 | U-0 | U-0 | R/W-0/0        | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-------|-----|-----|-----|----------------|---------|---------|---------|--|

| —     | —   | —   | —   | NCOxACC<19:16> |         |         |         |  |

| bit 7 |     |     |     |                |         |         | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 NCOxACC<19:16>: NCOx Accumulator, Upper Byte

#### 23.6 Register Definitions: DAC Control

| REGISTER         | 23-1: DAC10                                                             | CONU: VOLT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | AGE REFER        | ENCE CON        | ROL REGIS          | IERU             |          |  |  |

|------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|--------------------|------------------|----------|--|--|

| R/W-0/0          | U-0                                                                     | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0/0          | R/W-0/0         | R/W-0/0            | U-0              | R/W-0/0  |  |  |

| DAC1EN           | —                                                                       | DAC10E1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DAC10E2          | DAC1P           | 2SS<1:0>           | —                | DAC1NSS  |  |  |

| bit 7            |                                                                         | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |                 |                    |                  | bit (    |  |  |

| Legend:          |                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |                 |                    |                  |          |  |  |

| R = Readable I   | bit                                                                     | W = Writable b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | it               | U = Unimpleme   | ented bit, read as | '0'              |          |  |  |

| u = Bit is uncha | anged                                                                   | x = Bit is unkno                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | own              | -n/n = Value at | POR and BOR/V      | alue at all othe | r Resets |  |  |

| '1' = Bit is set |                                                                         | '0' = Bit is clear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | red              |                 |                    |                  |          |  |  |

| bit 6<br>bit 5   | 1 = DAC volta                                                           | sabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | an output on the | •               |                    |                  |          |  |  |

| bit 4            | 1 = DAC volta                                                           | C1 Voltage Outp<br>ge level is also a<br>ge level is disco                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | an output on the |                 |                    |                  |          |  |  |

| bit 3-2          | DAC1PSS<1:0<br>11 = Reserve<br>10 = FVR Buf<br>01 = VREF+ p<br>00 = VDD | fer2 output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | e Source Select  | bits            |                    |                  |          |  |  |

| bit 1            | Unimplemente                                                            | ed: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |                 |                    |                  |          |  |  |

| bit 0            | <b>DAC1NSS:</b> DA<br>1 = VREF- pin<br>0 = VSS                          | F Contraction of the second |                  |                 |                    |                  |          |  |  |

#### REGISTER 23-1: DAC1CON0: VOLTAGE REFERENCE CONTROL REGISTER 0

#### REGISTER 23-2: DAC1CON1: VOLTAGE REFERENCE CONTROL REGISTER 1

| R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|------------|---------|---------|---------|---------|---------|---------|---------|

| DAC1R<7:0> |         |         |         |         |         |         |         |

| bit 7 bit  |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 DAC1R<7:0>: DAC1 Voltage Output Select bits

#### TABLE 23-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC1 MODULE

| Name     | Bit 7      | Bit 6 | Bit 5   | Bit 4   | Bit 3  | Bit 2   | Bit 1 | Bit 0   | Register<br>on page |

|----------|------------|-------|---------|---------|--------|---------|-------|---------|---------------------|

| DAC1CON0 | DAC1EN     | _     | DAC10E1 | DAC10E2 | DAC1PS | SS<1:0> |       | DAC1NSS | 249                 |

| DAC1CON1 | DAC1R<7:0> |       |         |         |        |         |       | 249     |                     |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used with the DAC module.

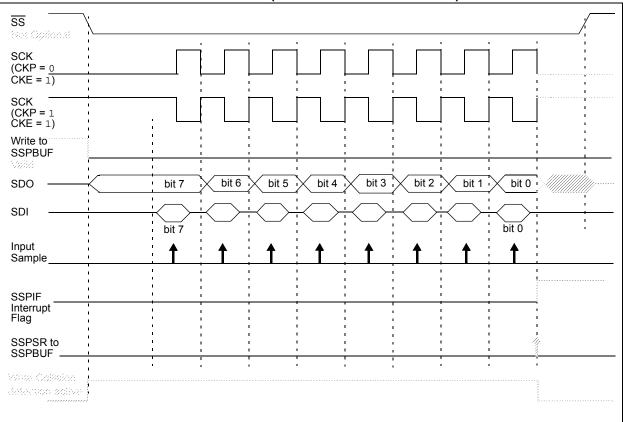

| FIGURE 30-9:                         | SPI N                                 | IODE W    | AVEFO            | RM (SL           | AVE MC           | DE WIT        | HCKE                         | = 0)                                      |                       |                                        |                                                |

|--------------------------------------|---------------------------------------|-----------|------------------|------------------|------------------|---------------|------------------------------|-------------------------------------------|-----------------------|----------------------------------------|------------------------------------------------|

|                                      | ×                                     |           |                  |                  |                  |               |                              |                                           |                       |                                        | , jaanna<br>Je                                 |

|                                      | ·<br>·<br>·                           |           |                  |                  |                  |               |                              |                                           |                       |                                        | :<br>:<br>:<br>:                               |

|                                      |                                       |           |                  | ·<br>·           | ,<br>,           |               | 4<br>4<br>                   |                                           | ><br>><br>            |                                        | :<br>                                          |

|                                      | :<br>-<br>-<br>-<br>-                 |           | )<br>)<br>;<br>} | 5<br>5<br>5<br>5 | :<br>:<br>:<br>: | ;<br>;<br>;   | 9<br>9<br>9<br>8             | «<br>«<br>«                               | e<br>e<br>o<br>o<br>o | :<br>:<br>:<br>:<br>:                  | ·<br>·<br>·                                    |

| -3920                                |                                       | V 32.7    | K 68.6           | X 88 8<br>,      | X 338 4          | X 88.3        | X 338.2<br>,                 | X.<br>v                                   |                       |                                        | ···t.<br>• • • • • • • • • • • • • • • • • • • |

| - 5574                               | ·<br>·<br>·<br>·                      |           |                  | ;<br>,,          |                  | ,             | ;<br>naa /////////<br>;<br>; | ,<br>,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                       | ////////////////////////////////////// | :                                              |

| itapati<br>Secregies                 | · · · · · · · · · · · · · · · · · · · | . 40.<br> |                  |                  | 40.<br>          | . <i>14</i> , | , 19.<br>                    |                                           | s<br>, 2<br>2         | %.                                     |                                                |

| SSPP<br>Interrupt<br>Plag            | :<br>:<br>:                           |           | •<br>6<br>9<br>9 | -<br>            | •<br>•<br>•<br>• |               | -<br>-<br>                   | -<br>-<br>-<br>                           | e<br>2<br>2<br>2<br>4 |                                        |                                                |

|                                      | · .<br>                               |           | 2<br>6           | ,<br>;<br>;<br>, | ,<br>5<br>5<br>  |               | ,<br>2<br>2<br>2,            | 5<br>7<br>7                               | ·<br>• :<br>• :       |                                        |                                                |

| Virite Codisson<br>Generation ective |                                       |           |                  |                  | *******          |               |                              |                                           |                       |                                        |                                                |

#### FIGURE 30-10: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

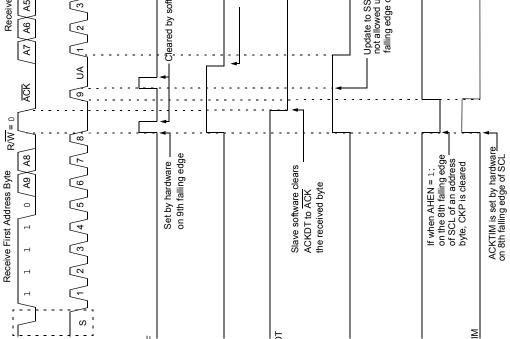

I<sup>2</sup>C SLAVE, 10-BIT ADDRESS, RECEPTION (SEN = 0, AHEN = 1, DHEN = 0) **FIGURE 30-21:** Received data is read from SSPBUF 9 UA 11 2 3 4 5 6 7 8 6 7 8 clears UA and releases SCL Update of SSPADD, Set CKP with software releases SCL Cleared by software ACK A7 A6 A5 A4 A3 A2 A1 A0 9 UA 11 2 3 4 5 6 7 8 SSPBUF can be read anytime before the next received byte Receive Second Address Byte - Update to SSPADD is not allowed until 9th falling edge of SCL Cleared by software ACK R/W = 0

ACKDT

A

ВΓ

SSPIF

SCL

Ч

SDA

ACKTIM

CКР

| Name      | Bit 7       | Bit 6           | Bit 5         | Bit 4         | Bit 3   | Bit 2     | Bit 1  | Bit 0  | Reset<br>Values on<br>Page: |

|-----------|-------------|-----------------|---------------|---------------|---------|-----------|--------|--------|-----------------------------|

| ANSELB    | -           |                 | ANSB5         | ANSB4         | ANSB3   | ANSB2     | ANSB1  | ANSB0  | 126                         |

| ANSELC    | ANSC7       | ANSC6           | ANSC5         | ANSC4         | ANSC3   | ANSC2     | _      | —      | 131                         |

| INTCON    | GIE         | PEIE            | TMR0IE        | INTE          | IOCIE   | TMR0IF    | INTF   | IOCIF  | 83                          |

| PIE1      | TMR1GIE     | ADIE            | RCIE          | TXIE          | SSP1IE  | CCP1IE    | TMR2IE | TMR1IE | 84                          |

| PIE2      | OSFIE       | C2IE            | C1IE          | _             | BCL1IE  | TMR6IE    | TMR4IE | CCP2IE | 85                          |

| PIR1      | TMR1GIF     | ADIF            | RCIF          | TXIF          | SSP1IF  | CCP1IF    | TMR2IF | TMR1IF | 87                          |

| PIR2      | OSFIF       | C2IF            | C1IF          | _             | BCL1IF  | TMR6IF    | TMR4IF | CCP2IF | 88                          |

| RxyPPS    | _           | _               | _             | RxyPPS<4:0>   |         |           |        |        |                             |

| SSPCLKPPS | _           | _               | _             |               | SS      | PCLKPPS<4 | :0>    |        | 136                         |

| SSPDATPPS | _           | _               | _             |               | SS      | PDATPPS<4 | :0>    |        | 136                         |

| SSP1ADD   |             |                 |               | ADD           | <7:0>   |           |        |        | 336                         |

| SSP1BUF   | Synchronous | s Serial Port F | Receive Buffe | r/Transmit Re | egister |           |        |        | 289*                        |

| SSP1CON1  | WCOL        | SSPOV           | SSPEN         | CKP           |         | SSPM      | <3:0>  |        | 333                         |

| SSP1CON2  | GCEN        | ACKSTAT         | ACKDT         | ACKEN         | RCEN    | PEN       | RSEN   | SEN    | 334                         |

| SSP1CON3  | ACKTIM      | PCIE            | SCIE          | BOEN          | SDAHT   | SBCDE     | AHEN   | DHEN   | 335                         |

| SSP1MSK   | MSK<7:0>    |                 |               |               |         |           |        |        | 336                         |

| SSP1STAT  | SMP         | CKE             | D/A           | Р             | S       | R/W       | UA     | BF     | 332                         |

| TRISB     | TRISB7      | TRISB6          | TRISB5        | TRISB4        | TRISB3  | TRISB2    | TRISB1 | TRISB0 | 125                         |

| TRISC     | TRISC7      | TRISC6          | TRISC5        | TRISC4        | TRISC3  | TRISC2    | TRISC1 | TRISC0 | 130                         |

### TABLE 30-3: SUMMARY OF REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the MSSP module in  $I^2C$  mode.

\* Page provides register information.

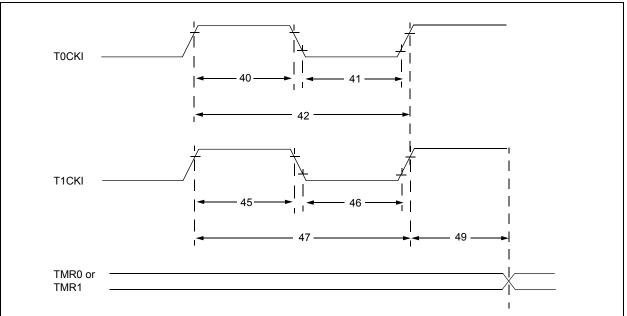

#### 34.4 AC Characteristics

Timing Parameter Symbology has been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| 2. Tpp5                                    |                                 | 1   |                |  |  |  |  |  |

|--------------------------------------------|---------------------------------|-----|----------------|--|--|--|--|--|

| Т                                          |                                 |     |                |  |  |  |  |  |

| F                                          | Frequency                       | Т   | Time           |  |  |  |  |  |

| Lowercase letters (pp) and their meanings: |                                 |     |                |  |  |  |  |  |

| рр                                         |                                 |     |                |  |  |  |  |  |

| сс                                         | CCP1                            | OSC | OSC1           |  |  |  |  |  |

| ck                                         | CLKOUT                          | rd  | RD             |  |  |  |  |  |

| cs                                         | CS                              | rw  | RD or WR       |  |  |  |  |  |

| di                                         | SDI                             | sc  | SCK            |  |  |  |  |  |

| do                                         | SDO                             | SS  | SS             |  |  |  |  |  |

| dt                                         | Data in                         | tO  | TOCKI          |  |  |  |  |  |

| io                                         | I/O PORT                        | t1  | T1CKI          |  |  |  |  |  |

| mc                                         | MCLR                            | wr  | WR             |  |  |  |  |  |

| Upperc                                     | ase letters and their meanings: |     |                |  |  |  |  |  |

| S                                          |                                 |     |                |  |  |  |  |  |

| F                                          | Fall                            | Р   | Period         |  |  |  |  |  |

| Н                                          | High                            | R   | Rise           |  |  |  |  |  |

| I                                          | Invalid (High-impedance)        | V   | Valid          |  |  |  |  |  |

| L                                          | Low                             | Z   | High-impedance |  |  |  |  |  |

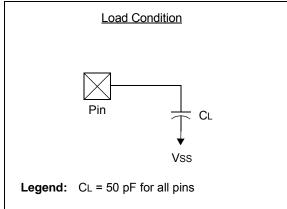

#### FIGURE 34-4: LOAD CONDITIONS

#### 36.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 36.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 36.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 36.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility