#### Welcome to **E-XFL.COM**

## **Understanding Embedded - CPLDs (Complex Programmable Logic Devices)**

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixed-function ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

| Details                         |                                                                            |

|---------------------------------|----------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                   |

| Programmable Type               | In System Programmable                                                     |

| Delay Time tpd(1) Max           | 10 ns                                                                      |

| Voltage Supply - Internal       | 3V ~ 3.6V                                                                  |

| Number of Logic Elements/Blocks | 4                                                                          |

| Number of Macrocells            | 64                                                                         |

| Number of Gates                 | -                                                                          |

| Number of I/O                   | 64                                                                         |

| Operating Temperature           | -40°C ~ 105°C (TJ)                                                         |

| Mounting Type                   | Surface Mount                                                              |

| Package / Case                  | 100-LQFP                                                                   |

| Supplier Device Package         | 100-TQFP (14x14)                                                           |

| Purchase URL                    | https://www.e-xfl.com/product-detail/lattice-semiconductor/lc4064v-10t100i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

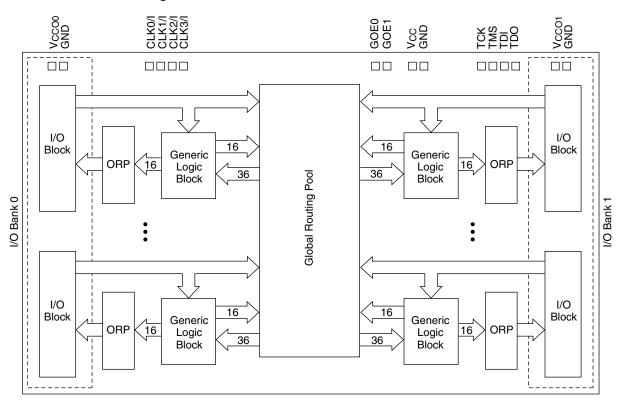

Figure 1. Functional Block Diagram

The I/Os in the ispMACH 4000 are split into two banks. Each bank has a separate I/O power supply. Inputs can support a variety of standards independent of the chip or bank power supply. Outputs support the standards compatible with the power supply provided to the bank. Support for a variety of standards helps designers implement designs in mixed voltage environments. In addition, 5V tolerant inputs are specified within an I/O bank that is connected to  $V_{CCO}$  of 3.0V to 3.6V for LVCMOS 3.3, LVTTL and PCI interfaces.

## ispMACH 4000 Architecture

There are a total of two GLBs in the ispMACH 4032, increasing to 32 GLBs in the ispMACH 4512. Each GLB has 36 inputs. All GLB inputs come from the GRP and all outputs from the GLB are brought back into the GRP to be connected to the inputs of any other GLB on the device. Even if feedback signals return to the same GLB, they still must go through the GRP. This mechanism ensures that GLBs communicate with each other with consistent and predictable delays. The outputs from the GLB are also sent to the ORP. The ORP then sends them to the associated I/O cells in the I/O block.

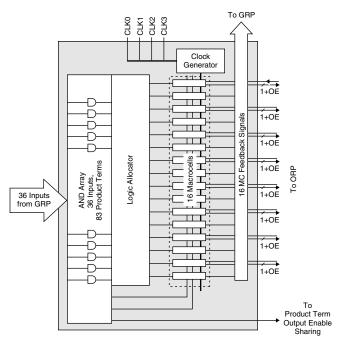

## Generic Logic Block

The ispMACH 4000 GLB consists of a programmable AND array, logic allocator, 16 macrocells and a GLB clock generator. Macrocells are decoupled from the product terms through the logic allocator and the I/O pins are decoupled from macrocells through the ORP. Figure 2 illustrates the GLB.

Figure 2. Generic Logic Block

#### **AND Array**

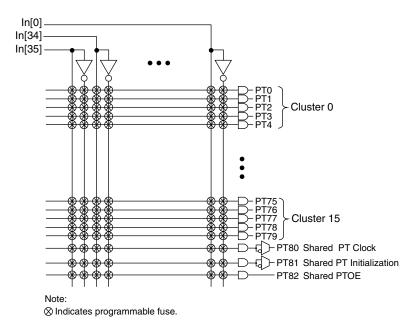

The programmable AND Array consists of 36 inputs and 83 output product terms. The 36 inputs from the GRP are used to form 72 lines in the AND Array (true and complement of the inputs). Each line in the array can be connected to any of the 83 output product terms via a wired-AND. Each of the 80 logic product terms feed the logic allocator with the remaining three control product terms feeding the Shared PT Clock, Shared PT Initialization and Shared PT OE. The Shared PT Clock and Shared PT Initialization signals can optionally be inverted before being fed to the macrocells.

Every set of five product terms from the 80 logic product terms forms a product term cluster starting with PT0. There is one product term cluster for every macrocell in the GLB. Figure 3 is a graphical representation of the AND Array.

Figure 3. AND Array

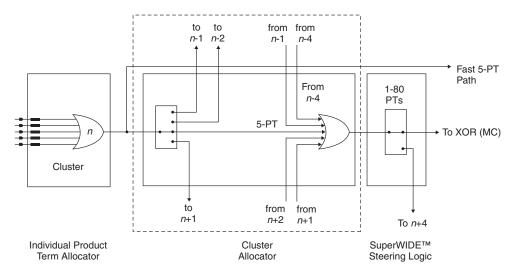

#### **Enhanced Logic Allocator**

Within the logic allocator, product terms are allocated to macrocells in product term clusters. Each product term cluster is associated with a macrocell. The cluster size for the ispMACH 4000 family is 4+1 (total 5) product terms. The software automatically considers the availability and distribution of product term clusters as it fits the functions within a GLB. The logic allocator is designed to provide three speed paths: 5-PT fast bypass path, 20-PT Speed Locking path and an up to 80-PT path. The availability of these three paths lets designers trade timing variability for increased performance.

The enhanced Logic Allocator of the ispMACH 4000 family consists of the following blocks:

- Product Term Allocator

- Cluster Allocator

- Wide Steering Logic

Figure 4 shows a macrocell slice of the Logic Allocator. There are 16 such slices in the GLB.

Figure 4. Macrocell Slice

#### **Product Term Allocator**

The product term allocator assigns product terms from a cluster to either logic or control applications as required by the design being implemented. Product terms that are used as logic are steered into a 5-input OR gate associated with the cluster. Product terms that used for control are steered either to the macrocell or I/O cell associated with the cluster. Table 3 shows the available functions for each of the five product terms in the cluster. The OR gate output connects to the associated I/O cell, providing a fast path for narrow combinatorial functions, and to the logic allocator.

Table 3. Individual PT Steering

| Product Term   | Logic    | Control                                                                     |

|----------------|----------|-----------------------------------------------------------------------------|

| PT <i>n</i>    | Logic PT | Single PT for XOR/OR                                                        |

| PT <i>n</i> +1 | Logic PT | Individual Clock (PT Clock)                                                 |

| PT <i>n</i> +2 | Logic PT | Individual Initialization or Individual Clock Enable (PT Initialization/CE) |

| PT <i>n</i> +3 | Logic PT | Individual Initialization (PT Initialization)                               |

| PT <i>n</i> +4 | Logic PT | Individual OE (PTOE)                                                        |

#### **Cluster Allocator**

The cluster allocator allows clusters to be steered to neighboring macrocells, thus allowing the creation of functions with more product terms. Table 4 shows which clusters can be steered to which macrocells. Used in this manner, the cluster allocator can be used to form functions of up to 20 product terms. Additionally, the cluster allocator accepts inputs from the wide steering logic. Using these inputs, functions up to 80 product terms can be created.

Table 4. Available Clusters for Each Macrocell

| Macrocell |     | Available | Clusters |     |

|-----------|-----|-----------|----------|-----|

| M0        | _   | C0        | C1       | C2  |

| M1        | C0  | C1        | C2       | C3  |

| M2        | C1  | C2        | C3       | C4  |

| M3        | C2  | C3        | C4       | C5  |

| M4        | C3  | C4        | C5       | C6  |

| M5        | C4  | C5        | C6       | C7  |

| M6        | C5  | C6        | C7       | C8  |

| M7        | C6  | C7        | C8       | C9  |

| M8        | C7  | C8        | C9       | C10 |

| M9        | C8  | C9        | C10      | C11 |

| M10       | C9  | C10       | C11      | C12 |

| M11       | C10 | C11       | C12      | C13 |

| M12       | C11 | C12       | C13      | C14 |

| M13       | C12 | C13       | C14      | C15 |

| M14       | C13 | C14       | C15      | _   |

| M15       | C14 | C15       | _        | _   |

#### Wide Steering Logic

The wide steering logic allows the output of the cluster allocator n to be connected to the input of the cluster allocator n+4. Thus, cluster chains can be formed with up to 80 product terms, supporting wide product term functions and allowing performance to be increased through a single GLB implementation. Table 5 shows the product term chains.

Table 5. Product Term Expansion Capability

| Expansion<br>Chains | Macrocells Associated with Expansion Chain (with Wrap Around) | Max PT/<br>Macrocell |

|---------------------|---------------------------------------------------------------|----------------------|

| Chain-0             | M0 M4 M8 M12 M0                                               | 75                   |

| Chain-1             | M1 M5 M9 M13 M1                                               | 80                   |

| Chain-2             | M2 M6 M10 M14 M2                                              | 75                   |

| Chain-3             | M3 M7 M11 M15 M3                                              | 70                   |

Every time the super cluster allocator is used, there is an incremental delay of t<sub>EXP</sub>. When the super cluster allocator is used, all destinations other than the one being steered to, are given the value of ground (i.e., if the super cluster is steered to M (n+4), then M (n) is ground).

#### Macrocell

The 16 macrocells in the GLB are driven by the 16 outputs from the logic allocator. Each macrocell contains a programmable XOR gate, a programmable register/latch, along with routing for the logic and control functions. Figure 5 shows a graphical representation of the macrocell. The macrocells feed the ORP and GRP. A direct input from the I/O cell allows designers to use the macrocell to construct high-speed input registers. A programmable delay in this path allows designers to choose between the fastest possible set-up time and zero hold time.

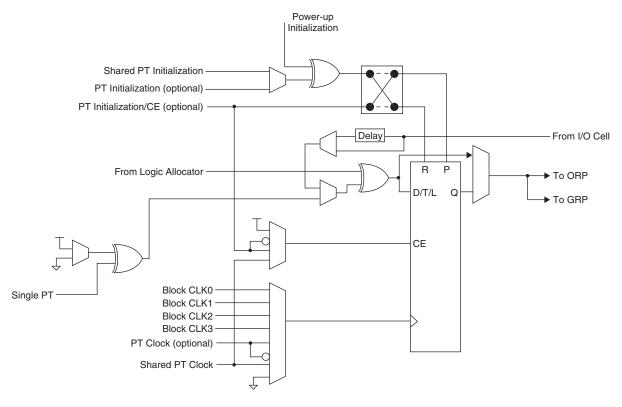

Figure 5. Macrocell

## **Enhanced Clock Multiplexer**

The clock input to the flip-flop can select any of the four block clocks along with the shared PT clock, and true and complement forms of the optional individual term clock. An 8:1 multiplexer structure is used to select the clock. The eight sources for the clock multiplexer are as follows:

- Block CLK0

- Block CLK1

### **Output Routing Pool (ORP)**

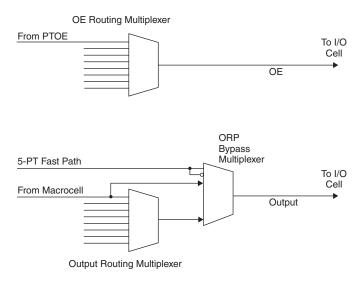

The Output Routing Pool allows macrocell outputs to be connected to any of several I/O cells within an I/O block. This provides greater flexibility in determining the pinout and allows design changes to occur without affecting the pinout. The output routing pool also provides a parallel capability for routing macrocell-level OE product terms. This allows the OE product term to follow the macrocell output as it is switched between I/O cells. Additionally, the output routing pool allows the macrocell output or true and complement forms of the 5-PT bypass signal to bypass the output routing multiplexers and feed the I/O cell directly. The enhanced ORP of the ispMACH 4000 family consists of the following elements:

- · Output Routing Multiplexers

- OE Routing Multiplexers

- Output Routing Pool Bypass Multiplexers

Figure 7 shows the structure of the ORP from the I/O cell perspective. This is referred to as an ORP slice. Each ORP has as many ORP slices as there are I/O cells in the corresponding I/O block.

Figure 7. ORP Slice

#### **Output Routing Multiplexers**

The details of connections between the macrocells and the I/O cells vary across devices and within a device dependent on the maximum number of I/Os available. Tables 5-9 provide the connection details.

Table 6. ORP Combinations for I/O Blocks with 8 I/Os

| I/O Cell | Available Macrocells                 |

|----------|--------------------------------------|

| I/O 0    | M0, M1, M2, M3, M4, M5, M6, M7       |

| I/O 1    | M2, M3, M4, M5, M6, M7, M8, M9       |

| I/O 2    | M4, M5, M6, M7, M8, M9, M10, M11     |

| I/O 3    | M6, M7, M8, M9, M10, M11, M12, M13   |

| I/O 4    | M8, M9, M10, M11, M12, M13, M14, M15 |

| I/O 5    | M10, M11, M12, M13, M14, M15, M0, M1 |

| I/O 6    | M12, M13, M14, M15, M0, M1, M2, M3   |

| I/O 7    | M14, M15, M0, M1, M2, M3, M4, M5     |

Timing v.3.2

## ispMACH 4000V/B/C External Switching Characteristics

#### **Over Recommended Operating Conditions**

|                               |                                                                                  | -2   | 25   | -2   | -27  |      | 3    | -35  |      |       |

|-------------------------------|----------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|-------|

| Parameter                     | Description <sup>1, 2, 3</sup>                                                   | Min. | Max. | Min. | Max. | Min. | Max. | Min. | Max. | Units |

| t <sub>PD</sub>               | 5-PT bypass combinatorial propagation delay                                      | _    | 2.5  | _    | 2.7  | _    | 3.0  | _    | 3.5  | ns    |

| t <sub>PD_MC</sub>            | 20-PT combinatorial propagation delay through macrocell                          | _    | 3.2  | _    | 3.5  | _    | 3.8  | _    | 4.2  | ns    |

| t <sub>S</sub>                | GLB register setup time before clock                                             | 1.8  |      | 1.8  |      | 2.0  |      | 2.0  | _    | ns    |

| t <sub>ST</sub>               | GLB register setup time before clock with T-type register                        | 2.0  | _    | 2.0  | _    | 2.2  | _    | 2.2  | _    | ns    |

| t <sub>SIR</sub>              | GLB register setup time before clock, input register path                        | 0.7  | _    | 1.0  | _    | 1.0  | _    | 1.0  | _    | ns    |

| t <sub>SIRZ</sub>             | GLB register setup time before clock with zero hold                              | 1.7  | _    | 2.0  | _    | 2.0  | _    | 2.0  | _    | ns    |

| t <sub>H</sub>                | GLB register hold time after clock                                               | 0.0  | _    | 0.0  | _    | 0.0  | _    | 0.0  | _    | ns    |

| t <sub>HT</sub>               | GLB register hold time after clock with T-type register                          | 0.0  | _    | 0.0  | _    | 0.0  | _    | 0.0  | _    | ns    |

| t <sub>HIR</sub>              | GLB register hold time after clock, input register path                          | 0.9  | _    | 1.0  | _    | 1.0  | _    | 1.0  | _    | ns    |

| t <sub>HIRZ</sub>             | GLB register hold time after clock, input register path with zero hold           | 0.0  | _    | 0.0  | _    | 0.0  | _    | 0.0  | _    | ns    |

| t <sub>CO</sub>               | GLB register clock-to-output delay                                               |      | 2.2  | _    | 2.7  | _    | 2.7  | _    | 2.7  | ns    |

| t <sub>R</sub>                | External reset pin to output delay                                               | _    | 3.5  | _    | 4.0  | _    | 4.4  | _    | 4.5  | ns    |

| t <sub>RW</sub>               | External reset pulse duration                                                    | 1.5  |      | 1.5  | _    | 1.5  |      | 1.5  | -    | ns    |

| t <sub>PTOE/DIS</sub>         | Input to output local product term output enable/disable                         | _    | 4.0  | _    | 4.5  | _    | 5.0  | _    | 5.5  | ns    |

| t <sub>GPTOE/DIS</sub>        | Input to output global product term output enable/disable                        | -    | 5.0  | _    | 6.5  | _    | 8.0  | _    | 8.0  | ns    |

| t <sub>GOE/DIS</sub>          | Global OE input to output enable/disable                                         | _    | 3.0  | _    | 3.5  | _    | 4.0  | _    | 4.5  | ns    |

| t <sub>CW</sub>               | Global clock width, high or low                                                  | 1.1  |      | 1.3  | _    | 1.3  | _    | 1.3  | _    | ns    |

| t <sub>GW</sub>               | Global gate width low (for low transparent) or high (for high transparent)       | 1.1  | _    | 1.3  | _    | 1.3  | _    | 1.3  | _    | ns    |

| t <sub>WIR</sub>              | Input register clock width, high or low                                          | 1.1  | _    | 1.3  | _    | 1.3  | _    | 1.3  | _    | ns    |

| f <sub>MAX</sub> <sup>4</sup> | Clock frequency with internal feedback                                           |      | 400  |      | 333  | _    | 322  | _    | 322  | MHz   |

| f <sub>MAX</sub> (Ext.)       | Clock frequency with external feedback, [1/ (t <sub>S</sub> + t <sub>CO</sub> )] | _    | 250  | _    | 222  | _    | 212  | _    | 212  | MHz   |

<sup>1.</sup> Timing numbers are based on default LVCMOS 1.8 I/O buffers. Use timing adjusters provided to calculate other standards.

<sup>2.</sup> Measured using standard switching circuit, assuming GRP loading of 1 and 1 output switching.

<sup>3.</sup> Pulse widths and clock widths less than minimum will cause unknown behavior.

<sup>4.</sup> Standard 16-bit counter using GRP feedback.

## ispMACH 4000Z External Switching Characteristics

#### **Over Recommended Operating Conditions**

|                               |                                                                            | -35  |      | -3   | 37   | -4   |      |       |

|-------------------------------|----------------------------------------------------------------------------|------|------|------|------|------|------|-------|

| Parameter                     | Description <sup>1, 2, 3</sup>                                             | Min. | Max. | Min. | Max. | Min. | Max. | Units |

| t <sub>PD</sub>               | 5-PT bypass combinatorial propagation delay                                |      | 3.5  |      | 3.7  | _    | 4.2  | ns    |

| t <sub>PD_MC</sub>            | 20-PT combinatorial propagation delay through macrocell                    | _    | 4.4  | _    | 4.7  | _    | 5.7  | ns    |

| t <sub>S</sub>                | GLB register setup time before clock                                       | 2.2  | _    | 2.5  | _    | 2.7  | _    | ns    |

| t <sub>ST</sub>               | GLB register setup time before clock with T-type register                  | 2.4  | _    | 2.7  | _    | 2.9  | _    | ns    |

| t <sub>SIR</sub>              | GLB register setup time before clock, input register path                  | 1.0  | _    | 1.1  | _    | 1.3  | _    | ns    |

| t <sub>SIRZ</sub>             | GLB register setup time before clock with zero hold                        | 2.0  | _    | 2.1  | _    | 2.6  | _    | ns    |

| t <sub>H</sub>                | GLB register hold time after clock                                         | 0.0  | _    | 0.0  | _    | 0.0  | _    | ns    |

| t <sub>HT</sub>               | GLB register hold time after clock with T-type register                    |      | _    | 0.0  | _    | 0.0  | _    | ns    |

| t <sub>HIR</sub>              | GLB register hold time after clock, input register path                    |      | _    | 1.0  | _    | 1.3  | _    | ns    |

| t <sub>HIRZ</sub>             | GLB register hold time after clock, input register path with zero hold     | 0.0  | _    | 0.0  | _    | 0.0  | _    | ns    |

| t <sub>CO</sub>               | GLB register clock-to-output delay                                         |      | 3.0  |      | 3.2  | _    | 3.5  | ns    |

| t <sub>R</sub>                | External reset pin to output delay                                         |      | 5.0  |      | 6.0  | _    | 7.3  | ns    |

| t <sub>RW</sub>               | External reset pulse duration                                              | 1.5  | _    | 1.7  | _    | 2.0  | _    | ns    |

| t <sub>PTOE/DIS</sub>         | Input to output local product term output enable/disable                   | _    | 7.0  | _    | 8.0  | _    | 8.0  | ns    |

| t <sub>GPTOE/DIS</sub>        | Input to output global product term output enable/disable                  | _    | 6.5  | _    | 7.0  | _    | 8.0  | ns    |

| t <sub>GOE/DIS</sub>          | Global OE input to output enable/disable                                   | _    | 4.5  | _    | 4.5  | _    | 4.8  | ns    |

| t <sub>CW</sub>               | Global clock width, high or low                                            | 1.0  | _    | 1.5  | _    | 1.8  | _    | ns    |

| t <sub>GW</sub>               | Global gate width low (for low transparent) or high (for high transparent) |      | _    | 1.5  | _    | 1.8  | _    | ns    |

| t <sub>WIR</sub>              | Input register clock width, high or low                                    | 1.0  | _    | 1.5  | _    | 1.8  | _    | ns    |

| f <sub>MAX</sub> <sup>4</sup> | Clock frequency with internal feedback                                     | _    | 267  | _    | 250  | _    | 220  | MHz   |

| f <sub>MAX</sub> (Ext.)       | clock frequency with external feedback, $[1 / (t_S + t_{CO})]$             | _    | 192  | _    | 175  | _    | 161  | MHz   |

<sup>1.</sup> Timing numbers are based on default LVCMOS 1.8 I/O buffers. Use timing adjusters provided to calculate other standards.

Timing v.2.2

<sup>2.</sup> Measured using standard switching GRP loading of 1 and 1 output switching.

<sup>3.</sup> Pulse widths and clock widths less than minimum will cause unknown behavior.

<sup>4.</sup> Standard 16-bit counter using GRP feedback.

## **Signal Descriptions**

| Signal Names                          | Desc                                                                                            | ription                                                                                                 |  |  |  |  |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| TMS                                   | Input – This pin is the IEEE 1149.1 Test Notes that the state machine.                          | Input – This pin is the IEEE 1149.1 Test Mode Select input, which is used to control the state machine. |  |  |  |  |  |

| TCK                                   | Input – This pin is the IEEE 1149.1 Test 0 state machine.                                       | Clock input pin, used to clock through the                                                              |  |  |  |  |  |

| TDI                                   | Input – This pin is the IEEE 1149.1 Test D                                                      | Data In pin, used to load data.                                                                         |  |  |  |  |  |

| TDO                                   | Output – This pin is the IEEE 1149.1 Test                                                       | Data Out pin used to shift data out.                                                                    |  |  |  |  |  |

| GOE0/IO, GOE1/IO                      | These pins are configured to be either Gl pins.                                                 | obal Output Enable Input or as general I/O                                                              |  |  |  |  |  |

| GND                                   | Ground                                                                                          | Ground                                                                                                  |  |  |  |  |  |

| NC                                    | Not Connected                                                                                   |                                                                                                         |  |  |  |  |  |

| V <sub>CC</sub>                       | The power supply pins for logic core and                                                        | JTAG port.                                                                                              |  |  |  |  |  |

| CLK0/I, CLK1/I, CLK2/I, CLK3/I        | These pins are configured to be either CL                                                       | ₋K input or as an input.                                                                                |  |  |  |  |  |

| V <sub>CCO0</sub> , V <sub>CCO1</sub> | The power supply pins for each I/O bank.                                                        |                                                                                                         |  |  |  |  |  |

|                                       | Input/Output <sup>1</sup> – These are the general pu reference (alpha) and z is macrocell refer | rpose I/O used by the logic array. y is GLB ence (numeric). z: 0-15.                                    |  |  |  |  |  |

|                                       | ispMACH 4032                                                                                    | y: A-B                                                                                                  |  |  |  |  |  |

|                                       | ispMACH 4064                                                                                    | y: A-D                                                                                                  |  |  |  |  |  |

| yzz                                   | ispMACH 4128                                                                                    | y: A-H                                                                                                  |  |  |  |  |  |

|                                       | ispMACH 4256                                                                                    | y: A-P                                                                                                  |  |  |  |  |  |

|                                       | ispMACH 4384                                                                                    | y: A-P, AX-HX                                                                                           |  |  |  |  |  |

|                                       | ispMACH 4512                                                                                    | y: A-P, AX-PX                                                                                           |  |  |  |  |  |

<sup>1.</sup> In some packages, certain I/Os are only available for use as inputs. See the signal connections table for details.

## ispMACH 4000V/B/C ORP Reference Table

|                         | 4032        | V/B/C      | 4               | 1064\ | //B/C            | 4128            | V/B/        | 0  |                 | 4256            | V/B/C           |                  | 4384\       | //B/C | 4512           | 2V/B/C                             |

|-------------------------|-------------|------------|-----------------|-------|------------------|-----------------|-------------|----|-----------------|-----------------|-----------------|------------------|-------------|-------|----------------|------------------------------------|

| Number of I/Os          | 30¹         | 32         | 30 <sup>2</sup> | 32    | 64               | 64              | 92³         | 96 | 64              | 96 <sup>4</sup> | 128             | 160              | 128         | 192   | 128            | 208                                |

| Number of GLBs          | 2           | 2          | 4               | 4     | 4                | 8               | 8           | 8  | 16              | 16              | 16              | 16               | 16          | 16    | 16             | 16                                 |

| Number of I/Os /<br>GLB | 16          | 16         | 8               | 8     | 16               | 8               | 12          | 12 | 4               | 8               | 8               | 10               | 8           | 8     | 8              | Mixture of 8 & 4 <sup>5</sup>      |

| Reference ORP<br>Table  | 16 l/<br>Gl | Os /<br>LB | 8 I/0<br>GI     |       | 16 I/Os /<br>GLB | 8 I/Os /<br>GLB | 12 l/<br>GI |    | 4 I/Os /<br>GLB | 8 I/Os /<br>GLB | 8 I/Os /<br>GLB | 10 I/Os /<br>GLB | 8 I/0<br>GL |       | 8 I/Os/<br>GLB | 8 I/Os /<br>GLB<br>4 I/Os /<br>GLB |

- 1. 32-macrocell device, 44 TQFP: 2 GLBs have 15 out of 16 I/Os bonded out.

- 2. 64-macrocells device, 44 TQFP: 2 GLBs have 7 out of 8 I/Os bonded out.

- 3. 128-macrocell device, 128 TQFP: 4 GLBs have 11 out of 12 I/Os

- 4. 256-macrocell device, 144 TQFP: 16 GLBs have 6 I/Os per

- 5. 512-macrocell device: 20 GLBs have 8 I/Os per, 12 GLBs have 4 I/Os per

## ispMACH 4000Z ORP Reference Table

|                      | 4032Z            | 406             | 64Z              | 412             | 28Z              | 4256Z           |                 |                 |

|----------------------|------------------|-----------------|------------------|-----------------|------------------|-----------------|-----------------|-----------------|

| Number of I/Os       | 32               | 32              | 64               | 64              | 96               | 64              | 96¹             | 128             |

| Number of GLBs       | 2                | 4               | 4                | 8               | 8                | 16              | 16              | 16              |

| Number of I/Os / GLB | 16               | 8               | 16               | 8               | 12               | 4               | 8               | 8               |

| Reference ORP Table  | 16 I/Os /<br>GLB | 8 I/Os /<br>GLB | 16 I/Os /<br>GLB | 8 I/Os /<br>GLB | 12 I/Os /<br>GLB | 4 I/Os /<br>GLB | 8 I/Os /<br>GLB | 8 I/Os /<br>GLB |

<sup>1. 256-</sup>macrocell device, 132 csBGA: 16 GLBs have 6 I/Os per

## ispMACH 4000V/B/C/Z Power Supply and NC Connections<sup>1</sup>

| Signal                 | 44-pin TQFP <sup>2</sup> | 48-pin TQFP <sup>2</sup> | 56-ball csBGA <sup>3</sup>                      | 100-pin TQFP <sup>2</sup> | 128-pin TQFP <sup>2</sup> |

|------------------------|--------------------------|--------------------------|-------------------------------------------------|---------------------------|---------------------------|

| VCC                    | 11, 33                   | 12, 36                   | K2, A9                                          | 25, 40, 75, 90            | 32, 51, 96, 115           |

| VCCO0<br>VCCO (Bank 0) | 6                        | 6                        | F3                                              | 13, 33, 95                | 3, 17, 30, 41, 122        |

| VCCO1<br>VCCO (Bank 1) | 28                       | 30                       | E8                                              | 45, 63, 83                | 58, 67, 81, 94, 105       |

| GND                    | 12, 34                   | 13, 37                   | H3, C8                                          | 1, 26, 51, 76             | 1, 33, 65, 97             |

| GND (Bank 0)           | 5                        | 5                        | D3                                              | 7, 18, 32, 96             | 10, 24, 40, 113, 123      |

| GND (Bank 1)           | 27                       | 29                       | G8                                              | 46, 57, 68, 82            | 49, 59, 74, 88, 104       |

| NC                     | _                        | _                        | <b>4032Z</b> : A8, B10, E1, E3, F8, F10, J1, K3 | _                         | _                         |

<sup>1.</sup> All grounds must be electrically connected at the board level. However, for the purposes of I/O current loading, grounds are associated with the bank shown.

<sup>2.</sup> Pin orientation follows the conventional order from pin 1 marking of the top side view and counter-clockwise.

<sup>3.</sup> Pin orientation A1 starts from the upper left corner of the top side view with alphabetical order ascending vertically and numerical order ascending horizontally.

# ispMACH 4256V/B/C/Z, 4384V/B/C, 4512V/B/C, Logic Signal Connections: 176-Pin TQFP (Cont.)

| Bank       |        | ispMACH 42    | 56V/B/C/Z | ispMACH 4     | 384V/B/C | ispMACH 4512V/B/C |     |  |

|------------|--------|---------------|-----------|---------------|----------|-------------------|-----|--|

| Pin Number | Number | GLB/MC/Pad    | ORP       | GLB/MC/Pad    | ORP      | GLB/MC/Pad        | ORP |  |

| 19         | 0      | D4            | D^2       | E4            | E^2      | G4                | G^2 |  |

| 20         | 0      | D2            | D^1       | E2            | E^1      | G2                | G^1 |  |

| 21         | 0      | D0            | D^0       | E0            | E^0      | G0                | G^0 |  |

| 22         | 0      | VCCO (Bank 0) | -         | VCCO (Bank 0) | -        | VCCO (Bank 0)     | -   |  |

| 23         | 0      | E0            | E^0       | H0            | H^0      | J0                | J^0 |  |

| 24         | 0      | E2            | E^1       | H2            | H^1      | J2                | J^1 |  |

| 25         | 0      | E4            | E^2       | H4            | H^2      | J4                | J^2 |  |

| 26         | 0      | E6            | E^3       | H6            | H^3      | J6                | J^3 |  |

| 27         | 0      | E8            | E^4       | H8            | H^4      | J8                | J^4 |  |

| 28         | 0      | E10           | E^5       | H10           | H^5      | J10               | J^5 |  |

| 29         | 0      | E12           | E^6       | H12           | H^6      | J12               | J^6 |  |

| 30         | 0      | E14           | E^7       | H14           | H^7      | J14               | J^7 |  |

| 31         | 0      | GND (Bank 0)  | -         | GND (Bank 0)  | -        | GND (Bank 0)      | -   |  |

| 32         | 0      | F0            | F^0       | J0            | J^0      | N0                | N^0 |  |

| 33         | 0      | F2            | F^1       | J2            | J^1      | N2                | N^1 |  |

| 34         | 0      | F4            | F^2       | J4            | J^2      | N4                | N^2 |  |

| 35         | 0      | F6            | F^3       | J6            | J^3      | N6                | N^3 |  |

| 36         | 0      | F8            | F^4       | J8            | J^4      | N8                | N^4 |  |

| 37         | 0      | F10           | F^5       | J10           | J^5      | N10               | N^5 |  |

| 38         | 0      | F12           | F^6       | J12           | J^6      | N12               | N^6 |  |

| 39         | 0      | F14           | F^7       | J14           | J^7      | N14               | N^7 |  |

| 40         | 0      | VCCO (Bank 0) | -         | VCCO (Bank 0) | -        | VCCO (Bank 0)     | -   |  |

| 41         | -      | TCK           | -         | TCK           | -        | TCK               | -   |  |

| 42         | -      | VCC           | -         | VCC           | -        | VCC               | -   |  |

| 43         | -      | NC            | -         | NC            | -        | NC                | -   |  |

| 44         | -      | NC            | -         | NC            | -        | NC                | -   |  |

| 45         | -      | NC            | -         | NC            | -        | NC                | -   |  |

| 46         | -      | GND           | -         | GND (Bank 0)  | -        | GND               | -   |  |

| 47         | 0      | G14           | G^7       | K14           | K^7      | O14               | O^7 |  |

| 48         | 0      | G12           | G^6       | K12           | K^6      | O12               | O^6 |  |

| 49         | 0      | G10           | G^5       | K10           | K^5      | O10               | O^5 |  |

| 50         | 0      | G8            | G^4       | K8            | K^4      | O8                | 0^4 |  |

| 51         | 0      | G6            | G^3       | K6            | K^3      | O6                | O^3 |  |

| 52         | 0      | G4            | G^2       | K4            | K^2      | O4                | O^2 |  |

| 53         | 0      | G2            | G^1       | K2            | K^1      | O2                | O^1 |  |

| 54         | 0      | G0            | G^0       | K0            | K^0      | 00                | O^0 |  |

| 55         | 0      | GND (Bank 0)  | -         | GND (Bank 0)  | -        | GND (Bank 0)      | -   |  |

| 56         | 0      | VCCO (Bank 0) | -         | VCCO (Bank 0) | -        | VCCO (Bank 0)     | -   |  |

| 57         | 0      | H14           | H^7       | L14           | L^7      | P14               | P^7 |  |

| 58         | 0      | H12           | H^6       | L12           | L^6      | P12               | P^6 |  |

| 59         | 0      | H10           | H^5       | L10           | L^5      | P10               | P^5 |  |

# ispMACH 4256V/B/C, 4384V/B/C, 4512V/B/C Logic Signal Connections: 256-Ball ftBGA/fpBGA (Cont.)

| Ball   | I/O  | ispMACH 4256<br>128-I/O | V/B/C | ispMACH 4256<br>160-I/O | V/B/C | ispMACH 4384  | V/B/C | ispMACH 4512  | V/B/C |

|--------|------|-------------------------|-------|-------------------------|-------|---------------|-------|---------------|-------|

| Number | Bank | GLB/MC/Pad              | ORP   | GLB/MC/Pad              | ORP   | GLB/MC/Pad    | ORP   | GLB/MC/Pad    | ORP   |

| J6     | 0    | E14                     | E^7   | E10                     | E^7   | H14           | H^7   | J14           | J^7   |

| K3     | 0    | NC                      | -     | E12                     | E^8   | G0            | G^0   | 10            | I^0   |

| K4     | 0    | NC                      | -     | E14                     | E^9   | G2            | G^1   | 14            | I^1   |

| L1     | 0    | NC                      | -     | NC                      | -     | l14           | I^7   | K0            | K^0   |

| L2     | 0    | NC                      | -     | NC                      | -     | l12           | I^6   | K2            | K^1   |

| M1     | 0    | NC                      | -     | NC                      | -     | NC            | -     | K4            | K^2   |

| -      | 0    | GND (Bank 0)            | -     | GND (Bank 0)            | -     | GND (Bank 0)  | -     | GND (Bank 0)  | -     |

| -      | 0    | -                       | -     | VCCO (Bank 0)           | -     | VCCO (Bank 0) | -     | VCCO (Bank 0) | -     |

| M2     | 0    | NC                      | -     | NC                      | -     | NC            | -     | K6            | K^3   |

| N1     | 0    | NC                      | -     | NC                      | -     | I10           | I^5   | K8            | K^4   |

| M3     | 0    | NC                      | -     | NC                      | -     | 18            | I^4   | K10           | K^5   |

| M4     | 0    | NC                      | -     | F0                      | F^0   | G4            | G^2   | 18            | I^2   |

| N2     | 0    | NC                      | -     | F1                      | F^1   | G6            | G^3   | l12           | I^3   |

| K5     | 0    | F0                      | F^0   | F2                      | F^2   | J0            | J^0   | N0            | N^0   |

| P1     | 0    | F2                      | F^1   | F4                      | F^3   | J2            | J^1   | N2            | N^1   |

| K6     | 0    | F4                      | F^2   | F6                      | F^4   | J4            | J^2   | N4            | N^2   |

| N3     | 0    | F6                      | F^3   | F8                      | F^5   | J6            | J^3   | N6            | N^3   |

| L5     | 0    | F8                      | F^4   | F9                      | F^6   | J8            | J^4   | N8            | N^4   |

| P2     | 0    | F10                     | F^5   | F10                     | F^7   | J10           | J^5   | N10           | N^5   |

| L6     | 0    | F12                     | F^6   | F12                     | F^8   | J12           | J^6   | N12           | N^6   |

| R1     | 0    | F14                     | F^7   | F14                     | F^9   | J14           | J^7   | N14           | N^7   |

| -      | 0    | VCCO (Bank 0)           | -     | VCCO (Bank 0)           | -     | VCCO (Bank 0) | -     | VCCO (Bank 0) | -     |

| P3     | -    | TCK                     | -     | TCK                     | -     | TCK           | -     | TCK           | -     |

| -      | -    | VCC                     | -     | VCC                     | -     | VCC           | -     | VCC           | -     |

| -      | -    | GND                     | -     | GND                     | -     | GND           | -     | GND           | -     |

| -      | 0    | -                       | -     | GND (Bank 0)            | -     | GND (Bank 0)  | -     | GND (Bank 0)  | -     |

| T2     | 0    | NC                      | -     | G14                     | G^9   | 16            | I^3   | K12           | K^6   |

| M5     | 0    | NC                      | -     | G12                     | G^8   | 14            | I^2   | K14           | K^7   |

| N4     | 0    | G14                     | G^7   | G10                     | G^7   | K14           | K^7   | O14           | O^7   |

| Т3     | 0    | G12                     | G^6   | G9                      | G^6   | K12           | K^6   | O12           | O^6   |

| R3     | 0    | G10                     | G^5   | G8                      | G^5   | K10           | K^5   | O10           | O^5   |

| M6     | 0    | G8                      | G^4   | G6                      | G^4   | K8            | K^4   | O8            | 0^4   |

| P4     | 0    | G6                      | G^3   | G4                      | G^3   | K6            | K^3   | O6            | O^3   |

| L7     | 0    | G4                      | G^2   | G2                      | G^2   | K4            | K^2   | O4            | 0^2   |

| N5     | 0    | G2                      | G^1   | G1                      | G^1   | K2            | K^1   | O2            | 0^1   |

| M7     | 0    | G0                      | G^0   | G0                      | G^0   | K0            | K^0   | 00            | O^0   |

| P5     | 0    | NC                      | -     | NC                      | -     | G8            | G^4   | MO            | M^0   |

| R4     | 0    | NC                      | -     | NC                      | -     | G10           | G^5   | M4            | M^1   |

| T4     | 0    | NC                      | -     | NC                      | -     | NC            | -     | L0            | L^0   |

| -      | 0    | GND (Bank 0)            | -     | GND (Bank 0)            | -     | GND (Bank 0)  | -     | GND (Bank 0)  | -     |

| -      | 0    | VCCO (Bank 0)           | -     | VCCO (Bank 0)           | -     | VCCO (Bank 0) | -     | VCCO (Bank 0) | -     |

# ispMACH 4256V/B/C, 4384V/B/C, 4512V/B/C Logic Signal Connections: 256-Ball ftBGA/fpBGA (Cont.)

| Ball   | I/O  | ispMACH 4256<br>128-I/O | V/B/C | ispMACH 4256<br>160-I/O | V/B/C | ispMACH 4384  | V/B/C | ispMACH 4512  | V/B/C |

|--------|------|-------------------------|-------|-------------------------|-------|---------------|-------|---------------|-------|

| Number | Bank | GLB/MC/Pad              | ORP   | GLB/MC/Pad              | ORP   | GLB/MC/Pad    | ORP   | GLB/MC/Pad    | ORP   |

| R14    | 1    | J10                     | J^5   | J10                     | J^7   | N10           | N^5   | BX10          | BX^5  |

| P13    | 1    | J12                     | J^6   | J12                     | J^8   | N12           | N^6   | BX12          | BX^6  |

| N13    | 1    | J14                     | J^7   | J14                     | J^9   | N14           | N^7   | BX14          | BX^7  |

| M12    | 1    | NC                      | -     | NC                      | -     | P4            | P^2   | FX0           | FX^0  |

| T15    | 1    | NC                      | -     | NC                      | -     | P6            | P^3   | FX2           | FX^1  |

| -      | -    | VCC                     | -     | VCC                     | -     | VCC           | -     | VCC           | -     |

| -      | -    | GND                     | -     | GND                     | -     | GND           | -     | GND           | -     |

| -      | 1    | -                       | -     | GND (Bank 1)            | -     | GND (Bank 1)  | -     | GND (Bank 1)  | -     |

| P14    | -    | TMS                     | -     | TMS                     | -     | TMS           | -     | TMS           | -     |

| -      | 1    | VCCO (Bank 1)           | -     | VCCO (Bank 1)           | -     | VCCO (Bank 1) | -     | VCCO (Bank 1) | -     |

| L12    | 1    | NC                      | -     | NC                      | -     | NC            | -     | FX4           | FX^2  |

| R16    | 1    | NC                      | -     | NC                      | -     | P8            | P^4   | FX6           | FX^3  |

| N14    | 1    | NC                      | -     | NC                      | -     | P10           | P^5   | FX8           | FX^4  |

| P15    | 1    | K14                     | K^7   | K14                     | K^9   | O14           | O^7   | CX14          | CX^7  |

| L11    | 1    | K12                     | K^6   | K12                     | K^8   | 012           | O^6   | CX12          | CX^6  |

| P16    | 1    | K10                     | K^5   | K10                     | K^7   | O10           | O^5   | CX10          | CX^5  |

| K11    | 1    | K8                      | K^4   | K9                      | K^6   | O8            | 0^4   | CX8           | CX^4  |

| M14    | 1    | K6                      | K^3   | K8                      | K^5   | O6            | O^3   | CX6           | CX^3  |

| K12    | 1    | K4                      | K^2   | K6                      | K^4   | O4            | O^2   | CX4           | CX^2  |

| N15    | 1    | K2                      | K^1   | K4                      | K^3   | O2            | O^1   | CX2           | CX^1  |

| N16    | 1    | K0                      | K^0   | K2                      | K^2   | 00            | O^0   | CX0           | CX^0  |

| M15    | 1    | NC                      | -     | K1                      | K^1   | BX6           | BX^3  | HX0           | HX^0  |

| M13    | 1    | NC                      | -     | K0                      | K^0   | BX4           | BX^2  | HX4           | HX^1  |

| -      | 1    | -                       | -     | VCCO (Bank 1)           | -     | VCCO (Bank 1) | -     | VCCO (Bank 1) | -     |

| -      | 1    | GND (Bank 1)            | -     | GND (Bank 1)            | -     | GND (Bank 1)  | -     | GND (Bank 1)  | -     |

| M16    | 1    | NC                      | -     | NC                      | -     | NC            | -     | FX10          | FX^5  |

| L15    | 1    | NC                      | -     | NC                      | -     | P12           | P^6   | FX12          | FX^6  |

| L16    | 1    | NC                      | -     | NC                      | -     | P14           | P^7   | FX14          | FX^7  |

| J11    | 1    | NC                      | -     | L14                     | L^9   | BX2           | BX^1  | HX8           | HX^2  |

| K15    | 1    | NC                      | -     | L12                     | L^8   | BX0           | BX^0  | HX12          | HX^3  |

| J12    | 1    | L14                     | L^7   | L10                     | L^7   | AX14          | AX^7  | GX14          | GX^7  |

| K13    | 1    | L12                     | L^6   | L9                      | L^6   | AX12          | AX^6  | GX12          | GX^6  |

| K14    | 1    | L10                     | L^5   | L8                      | L^5   | AX10          | AX^5  | GX10          | GX^5  |

| K16    | 1    | L8                      | L^4   | L6                      | L^4   | AX8           | AX^4  | GX8           | GX^4  |

| J16    | 1    | L6                      | L^3   | L4                      | L^3   | AX6           | AX^3  | GX6           | GX^3  |

| J15    | 1    | L4                      | L^2   | L2                      | L^2   | AX4           | AX^2  | GX4           | GX^2  |

| H16    | 1    | L2                      | L^1   | L1                      | L^1   | AX2           | AX^1  | GX2           | GX^1  |

| J13    | 1    | L0                      | L^0   | L0                      | L^0   | AX0           | AX^0  | GX0           | GX^0  |

| -      | 1    | VCCO (Bank 1)           | -     | VCCO (Bank 1)           | -     | VCCO (Bank 1) | -     | VCCO (Bank 1) | -     |

| -      | 1    | -                       | -     | GND (Bank 1)            | -     | GND (Bank 1)  | -     | GND (Bank 1)  | -     |

| J14    | 1    | MO                      | M^0   | MO                      | M^0   | DX0           | DX^0  | JX0           | JX^0  |

# ispMACH 4256V/B/C, 4384V/B/C, 4512V/B/C Logic Signal Connections: 256-Ball ftBGA/fpBGA (Cont.)

| Ball   | I/O  | ispMACH 4256<br>128-I/O | V/B/C | ispMACH 4256<br>160-I/O | V/B/C | ispMACH 4384V/B/C |     | ispMACH 4512 | V/B/C |

|--------|------|-------------------------|-------|-------------------------|-------|-------------------|-----|--------------|-------|

| Number | Bank | GLB/MC/Pad              | ORP   | GLB/MC/Pad              | ORP   | GLB/MC/Pad        | ORP | GLB/MC/Pad   | ORP   |

| E7     | 0    | NC                      | -     | B1                      | B^1   | F8                | F^4 | D12          | D^3   |

| A3     | 0    | B0                      | B^0   | B2                      | B^2   | B0                | B^0 | В0           | B^0   |

| F7     | 0    | B2                      | B^1   | B4                      | B^3   | B2                | B^1 | B2           | B^1   |

| B4     | 0    | B4                      | B^2   | B6                      | B^4   | B4                | B^2 | B4           | B^2   |

| C5     | 0    | B6                      | B^3   | B8                      | B^5   | B6                | B^3 | B6           | B^3   |

| A2     | 0    | B8                      | B^4   | B9                      | B^6   | B8                | B^4 | B8           | B^4   |

| E6     | 0    | B10                     | B^5   | B10                     | B^7   | B10               | B^5 | B10          | B^5   |

| В3     | 0    | B12                     | B^6   | B12                     | B^8   | B12               | B^6 | B12          | B^6   |

| C4     | 0    | B14                     | B^7   | B14                     | B^9   | B14               | B^7 | B14          | B^7   |

| D4     | 0    | NC                      | -     | NC                      | -     | D10               | D^5 | F0           | F^0   |

| E5     | 0    | NC                      | -     | NC                      | -     | D8                | D^4 | F2           | F^1   |

| -      | -    | VCC                     | -     | VCC                     | -     | VCC               | -   | VCC          | -     |

| -      | -    | -                       | -     | -                       | -     | GND               | -   | GND          | -     |

| -      | 0    | -                       | -     | -                       | -     | GND (Bank 0)      | -   | GND (Bank 0) | -     |

Note: VCC, VCCO and GND are tied together to their respective common signal on the package substrate. See Power Supply and NC Connections table for VCC/ VCCO/GND pin definitions.

## ispMACH 4000C (1.8V) Industrial Devices (Cont.)

| Family  | Part Number                  | Macrocells | Voltage | t <sub>PD</sub> | Package | Pin/Ball Count | 1/0 | Grade |

|---------|------------------------------|------------|---------|-----------------|---------|----------------|-----|-------|

|         | LC4384C-5FT256I              | 384        | 1.8     | 5               | ftBGA   | 256            | 192 | ı     |

|         | LC4384C-75FT256I             | 384        | 1.8     | 7.5             | ftBGA   | 256            | 192 | I     |

|         | LC4384C-10FT256I             | 384        | 1.8     | 10              | ftBGA   | 256            | 192 | I     |

|         | LC4384C-5F256I <sup>1</sup>  | 384        | 1.8     | 5               | fpBGA   | 256            | 192 | I     |

| LC4384C | LC4384C-75F256I <sup>1</sup> | 384        | 1.8     | 7.5             | fpBGA   | 256            | 192 | I     |

|         | LC4384C-10F256I <sup>1</sup> | 384        | 1.8     | 10              | fpBGA   | 256            | 192 | I     |

|         | LC4384C-5T176I               | 384        | 1.8     | 5               | TQFP    | 176            | 128 | I     |

|         | LC4384C-75T176I              | 384        | 1.8     | 7.5             | TQFP    | 176            | 128 | I     |

|         | LC4384C-10T176I              | 384        | 1.8     | 10              | TQFP    | 176            | 128 | I     |

|         | LC4512C-5FT256I              | 512        | 1.8     | 5               | ftBGA   | 256            | 208 | I     |

|         | LC4512C-75FT256I             | 512        | 1.8     | 7.5             | ftBGA   | 256            | 208 | I     |

|         | LC4512C-10FT256I             | 512        | 1.8     | 10              | ftBGA   | 256            | 208 | I     |

|         | LC4512C-5F256I <sup>1</sup>  | 512        | 1.8     | 5               | fpBGA   | 256            | 208 | I     |

| LC4512C | LC4512C-75F256I <sup>1</sup> | 512        | 1.8     | 7.5             | fpBGA   | 256            | 208 | I     |

|         | LC4512C-10F256I <sup>1</sup> | 512        | 1.8     | 10              | fpBGA   | 256            | 208 | I     |

|         | LC4512C-5T176I               | 512        | 1.8     | 5               | TQFP    | 176            | 128 | I     |

|         | LC4512C-75T176I              | 512        | 1.8     | 7.5             | TQFP    | 176            | 128 | I     |

|         | LC4512C-10T176I              | 512        | 1.8     | 10              | TQFP    | 176            | 128 | I     |

<sup>1.</sup> Use ftBGA package. fpBGA package devices have been discontinued via PCN#14A-07.

#### ispMACH 4000B (2.5V) Commercial Devices

| Device  | Part Number     | Macrocells | Voltage | t <sub>PD</sub> | Package | Pin/Ball Count | I/O | Grade |

|---------|-----------------|------------|---------|-----------------|---------|----------------|-----|-------|

|         | LC4032B-25T48C  | 32         | 2.5     | 2.5             | TQFP    | 48             | 32  | С     |

|         | LC4032B-5T48C   | 32         | 2.5     | 5               | TQFP    | 48             | 32  | С     |

| LC4032B | LC4032B-75T48C  | 32         | 2.5     | 7.5             | TQFP    | 48             | 32  | С     |

| LC4032D | LC4032B-25T44C  | 32         | 2.5     | 2.5             | TQFP    | 44             | 30  | С     |

|         | LC4032B-5T44C   | 32         | 2.5     | 5               | TQFP    | 44             | 30  | С     |

|         | LC4032B-75T44C  | 32         | 2.5     | 7.5             | TQFP    | 44             | 30  | С     |

|         | LC4064B-25T100C | 64         | 2.5     | 2.5             | TQFP    | 100            | 64  | С     |

|         | LC4064B-5T100C  | 64         | 2.5     | 5               | TQFP    | 100            | 64  | С     |

|         | LC4064B-75T100C | 64         | 2.5     | 7.5             | TQFP    | 100            | 64  | С     |

|         | LC4064B-25T48C  | 64         | 2.5     | 2.5             | TQFP    | 48             | 32  | С     |

| LC4064B | LC4064B-5T48C   | 64         | 2.5     | 5               | TQFP    | 48             | 32  | С     |

|         | LC4064B-75T48C  | 64         | 2.5     | 7.5             | TQFP    | 48             | 32  | С     |

|         | LC4064B-25T44C  | 64         | 2.5     | 2.5             | TQFP    | 44             | 30  | С     |

|         | LC4064B-5T44C   | 64         | 2.5     | 5               | TQFP    | 44             | 30  | С     |

|         | LC4064B-75T44C  | 64         | 2.5     | 7.5             | TQFP    | 44             | 30  | С     |

|         | LC4128B-27T128C | 128        | 2.5     | 2.7             | TQFP    | 128            | 92  | С     |

|         | LC4128B-5T128C  | 128        | 2.5     | 5               | TQFP    | 128            | 92  | С     |

| LC4128B | LC4128B-75T128C | 128        | 2.5     | 7.5             | TQFP    | 128            | 92  | С     |

| LU4120D | LC4128B-27T100C | 128        | 2.5     | 2.7             | TQFP    | 100            | 64  | С     |

|         | LC4128B-5T100C  | 128        | 2.5     | 5               | TQFP    | 100            | 64  | С     |

|         | LC4128B-75T100C | 128        | 2.5     | 7.5             | TQFP    | 100            | 64  | С     |

## ispMACH 4000V (3.3V) Commercial Devices (Cont.)

| Device  | Part Number                  | Macrocells | Voltage | t <sub>PD</sub> | Package | Pin/Ball Count | I/O | Grade |

|---------|------------------------------|------------|---------|-----------------|---------|----------------|-----|-------|

|         | LC4512V-35FT256C             | 512        | 3.3     | 3.5             | ftBGA   | 256            | 208 | С     |

|         | LC4512V-5FT256C              | 512        | 3.3     | 5               | ftBGA   | 256            | 208 | С     |

|         | LC4512V-75FT256C             | 512        | 3.3     | 7.5             | ftBGA   | 256            | 208 | С     |

|         | LC4512V-35F256C <sup>1</sup> | 512        | 3.3     | 3.5             | fpBGA   | 256            | 208 | С     |

| LC4512V | LC4512V-5F256C <sup>1</sup>  | 512        | 3.3     | 5               | fpBGA   | 256            | 208 | С     |

|         | LC4512V-75F256C1             | 512        | 3.3     | 7.5             | fpBGA   | 256            | 208 | С     |

|         | LC4512V-35T176C              | 512        | 3.3     | 3.5             | TQFP    | 176            | 128 | С     |

|         | LC4512V-5T176C               | 512        | 3.3     | 5               | TQFP    | 176            | 128 | С     |

|         | LC4512V-75T176C              | 512        | 3.3     | 7.5             | TQFP    | 176            | 128 | С     |

<sup>1.</sup> Use ftBGA package. fpBGA package devices have been discontinued via PCN#14A-07.

#### ispMACH 4000V (3.3V) Industrial Devices

| Family  | Part Number     | Macrocells | Voltage | t <sub>PD</sub> | Package | Pin/Ball Count | I/O | Grade |

|---------|-----------------|------------|---------|-----------------|---------|----------------|-----|-------|

|         | LC4032V-5T48I   | 32         | 3.3     | 5               | TQFP    | 48             | 32  | I     |

|         | LC4032V-75T48I  | 32         | 3.3     | 7.5             | TQFP    | 48             | 32  | I     |

| LC4032V | LC4032V-10T48I  | 32         | 3.3     | 10              | TQFP    | 48             | 32  | 1     |

| LC4032V | LC4032V-5T44I   | 32         | 3.3     | 5               | TQFP    | 44             | 30  | I     |

|         | LC4032V-75T44I  | 32         | 3.3     | 7.5             | TQFP    | 44             | 30  | 1     |

|         | LC4032V-10T44I  | 32         | 3.3     | 10              | TQFP    | 44             | 30  | I     |

|         | LC4064V-5T100I  | 64         | 3.3     | 5               | TQFP    | 100            | 64  | 1     |

|         | LC4064V-75T100I | 64         | 3.3     | 7.5             | TQFP    | 100            | 64  | 1     |

|         | LC4064V-10T100I | 64         | 3.3     | 10              | TQFP    | 100            | 64  | I     |

|         | LC4064V-5T48I   | 64         | 3.3     | 5               | TQFP    | 48             | 32  | 1     |

| LC4064V | LC4064V-75T48I  | 64         | 3.3     | 7.5             | TQFP    | 48             | 32  | I     |

|         | LC4064V-10T48I  | 64         | 3.3     | 10              | TQFP    | 48             | 32  | I     |

|         | LC4064V-5T44I   | 64         | 3.3     | 5               | TQFP    | 44             | 30  | 1     |

|         | LC4064V-75T44I  | 64         | 3.3     | 7.5             | TQFP    | 44             | 30  | I     |

|         | LC4064V-10T44I  | 64         | 3.3     | 10              | TQFP    | 44             | 30  | I     |

|         | LC4128V-5T144I  | 128        | 3.3     | 5               | TQFP    | 144            | 96  | I     |

|         | LC4128V-75T144I | 128        | 3.3     | 7.5             | TQFP    | 144            | 96  | I     |

|         | LC4128V-10T144I | 128        | 3.3     | 10              | TQFP    | 144            | 96  | I     |

|         | LC4128V-5T128I  | 128        | 3.3     | 5               | TQFP    | 128            | 92  | 1     |

| LC4128V | LC4128V-75T128I | 128        | 3.3     | 7.5             | TQFP    | 128            | 92  | I     |

|         | LC4128V-10T128I | 128        | 3.3     | 10              | TQFP    | 128            | 92  | I     |

|         | LC4128V-5T100I  | 128        | 3.3     | 5               | TQFP    | 100            | 64  | I     |

|         | LC4128V-75T100I | 128        | 3.3     | 7.5             | TQFP    | 100            | 64  | I     |

|         | LC4128V-10T100I | 128        | 3.3     | 10              | TQFP    | 100            | 64  | I     |

## **Lead-Free Packaging**

### ispMACH 4000Z (Zero Power, 1.8V) Lead-Free Commercial Devices

| Device   | Part Number       | Macrocells | Voltage | t <sub>PD</sub> | Package         | Pin/Ball<br>Count | I/O | Grade |

|----------|-------------------|------------|---------|-----------------|-----------------|-------------------|-----|-------|

|          | LC4032ZC-35MN56C  | 32         | 1.8     | 3.5             | Lead-free csBGA | 56                | 32  | С     |

|          | LC4032ZC-5MN56C   | 32         | 1.8     | 5               | Lead-free csBGA | 56                | 32  | С     |

| LC4032ZC | LC4032ZC-75MN56C  | 32         | 1.8     | 7.5             | Lead-free csBGA | 56                | 32  | С     |

| LU4032ZU | LC4032ZC-35TN48C  | 32         | 1.8     | 3.5             | Lead-free TQFP  | 48                | 32  | С     |

|          | LC4032ZC-5TN48C   | 32         | 1.8     | 5               | Lead-free TQFP  | 48                | 32  | С     |

|          | LC4032ZC-75TN48C  | 32         | 1.8     | 7.5             | Lead-free TQFP  | 48                | 32  | С     |

|          | LC4064ZC-37MN132C | 64         | 1.8     | 3.7             | Lead-free csBGA | 132               | 64  | С     |

|          | LC4064ZC-5MN132C  | 64         | 1.8     | 5               | Lead-free csBGA | 132               | 64  | С     |

|          | LC4064ZC-75MN132C | 64         | 1.8     | 7.5             | Lead-free csBGA | 132               | 64  | С     |

|          | LC4064ZC-37TN100C | 64         | 1.8     | 3.7             | Lead-free TQFP  | 100               | 64  | С     |

|          | LC4064ZC-5TN100C  | 64         | 1.8     | 5               | Lead-free TQFP  | 100               | 64  | С     |

| LC4064ZC | LC4064ZC-75TN100C | 64         | 1.8     | 7.5             | Lead-free TQFP  | 100               | 64  | С     |

| LO40042C | LC4064ZC-37MN56C  | 64         | 1.8     | 3.7             | Lead-free csBGA | 56                | 32  | С     |

|          | LC4064ZC-5MN56C   | 64         | 1.8     | 5               | Lead-free csBGA | 56                | 32  | С     |

|          | LC4064ZC-75MN56C  | 64         | 1.8     | 7.5             | Lead-free csBGA | 56                | 32  | С     |

|          | LC4064ZC-37TN48C  | 64         | 1.8     | 3.7             | Lead-free TQFP  | 48                | 32  | С     |

|          | LC4064ZC-5TN48C   | 64         | 1.8     | 5               | Lead-free TQFP  | 48                | 32  | С     |

|          | LC4064ZC-75TN48C  | 64         | 1.8     | 7.5             | Lead-free TQFP  | 48                | 32  | С     |

|          | LC4128ZC-42MN132C | 128        | 1.8     | 4.2             | Lead-free csBGA | 132               | 96  | С     |

| LC4128ZC | LC4128ZC-75MN132C | 128        | 1.8     | 7.5             | Lead-free csBGA | 132               | 96  | С     |

| LC41282C | LC4128ZC-42TN100C | 128        | 1.8     | 4.2             | Lead-free TQFP  | 100               | 64  | С     |

|          | LC4128ZC-75TN100C | 128        | 1.8     | 7.5             | Lead-free TQFP  | 100               | 64  | С     |

|          | LC4256ZC-45TN176C | 256        | 1.8     | 4.5             | Lead-free TQFP  | 176               | 128 | С     |

|          | LC4256ZC-75TN176C | 256        | 1.8     | 7.5             | Lead-free TQFP  | 176               | 128 | С     |

| LC4256ZC | LC4256ZC-45MN132C | 256        | 1.8     | 4.5             | Lead-free csBGA | 132               | 96  | С     |

| LU42302U | LC4256ZC-75MN132C | 256        | 1.8     | 7.5             | Lead-free csBGA | 132               | 96  | С     |

|          | LC4256ZC-45TN100C | 256        | 1.8     | 4.5             | Lead-free TQFP  | 100               | 64  | С     |

|          | LC4256ZC-75TN100C | 256        | 1.8     | 7.5             | Lead-free TQFP  | 100               | 64  | С     |

#### ispMACH 4000Z (Zero Power, 1.8V) Lead-Free Industrial Devices

| Device   | Part Number      | Macrocells | Voltage | t <sub>PD</sub> | Package         | Pin/Ball<br>Count | I/O | Grade |

|----------|------------------|------------|---------|-----------------|-----------------|-------------------|-----|-------|

|          | LC4032ZC-5MN56I  | 32         | 1.8     | 5               | Lead-free csBGA | 56                | 32  | I     |

| LC4032ZC | LC4032ZC-75MN56I | 32         | 1.8     | 7.5             | Lead-free csBGA | 56                | 32  | I     |

| LO403220 | LC4032ZC-5TN48I  | 32         | 1.8     | 5               | Lead-free TQFP  | 48                | 32  | I     |

|          | LC4032ZC-75TN48I | 32         | 1.8     | 7.5             | Lead-free TQFP  | 48                | 32  | I     |

## ispMACH 4000V (3.3V) Lead-Free Commercial Devices

| Device  | Part Number      | Macrocells | Voltage | t <sub>PD</sub> | Package        | Pin/Ball<br>Count | I/O | Grade |

|---------|------------------|------------|---------|-----------------|----------------|-------------------|-----|-------|

|         | LC4032V-25TN48C  | 32         | 3.3     | 2.5             | Lead-free TQFP | 48                | 32  | С     |

|         | LC4032V-5TN48C   | 32         | 3.3     | 5               | Lead-free TQFP | 48                | 32  | С     |

| LC4032V | LC4032V-75TN48C  | 32         | 3.3     | 7.5             | Lead-free TQFP | 48                | 32  | С     |

| LC4032V | LC4032V-25TN44C  | 32         | 3.3     | 2.5             | Lead-free TQFP | 44                | 30  | С     |

|         | LC4032V-5TN44C   | 32         | 3.3     | 5               | Lead-free TQFP | 44                | 30  | С     |

|         | LC4032V-75TN44C  | 32         | 3.3     | 7.5             | Lead-free TQFP | 44                | 30  | С     |

|         | LC4064V-25TN100C | 64         | 3.3     | 2.5             | Lead-free TQFP | 100               | 64  | С     |

|         | LC4064V-5TN100C  | 64         | 3.3     | 5               | Lead-free TQFP | 100               | 64  | С     |

|         | LC4064V-75TN100C | 64         | 3.3     | 7.5             | Lead-free TQFP | 100               | 64  | С     |

|         | LC4064V-25TN48C  | 64         | 3.3     | 2.5             | Lead-free TQFP | 48                | 32  | С     |

| LC4064V | LC4064V-5TN48C   | 64         | 3.3     | 5               | Lead-free TQFP | 48                | 32  | С     |

|         | LC4064V-75TN48C  | 64         | 3.3     | 7.5             | Lead-free TQFP | 48                | 32  | С     |

|         | LC4064V-25TN44C  | 64         | 3.3     | 2.5             | Lead-free TQFP | 44                | 30  | С     |

|         | LC4064V-5TN44C   | 64         | 3.3     | 5               | Lead-free TQFP | 44                | 30  | С     |

|         | LC4064V-75TN44C  | 64         | 3.3     | 7.5             | Lead-free TQFP | 44                | 30  | С     |

|         | LC4128V-27TN144C | 128        | 3.3     | 2.7             | Lead-free TQFP | 144               | 96  | С     |

|         | LC4128V-5TN144C  | 128        | 3.3     | 5               | Lead-free TQFP | 144               | 96  | С     |

|         | LC4128V-75TN144C | 128        | 3.3     | 7.5             | Lead-free TQFP | 144               | 96  | С     |

|         | LC4128V-27TN128C | 128        | 3.3     | 2.7             | Lead-free TQFP | 128               | 92  | С     |

| LC4128V | LC4128V-5TN128C  | 128        | 3.3     | 5               | Lead-free TQFP | 128               | 92  | С     |

|         | LC4128V-75TN128C | 128        | 3.3     | 7.5             | Lead-free TQFP | 128               | 92  | С     |

|         | LC4128V-27TN100C | 128        | 3.3     | 2.7             | Lead-free TQFP | 100               | 64  | С     |

|         | LC4128V-5TN100C  | 128        | 3.3     | 5               | Lead-free TQFP | 100               | 64  | С     |

|         | LC4128V-75TN100C | 128        | 3.3     | 7.5             | Lead-free TQFP | 100               | 64  | С     |

ispMACH 4000V (3.3V) Lead-Free Commercial Devices (Cont.)

| Device  | Part Number                    | Macrocells | Voltage | t <sub>PD</sub> | Package         | Pin/Ball<br>Count | I/O | Grade |

|---------|--------------------------------|------------|---------|-----------------|-----------------|-------------------|-----|-------|

|         | LC4256V-3FTN256AC              | 256        | 3.3     | 3               | Lead-free ftBGA | 256               | 128 | С     |

|         | LC4256V-5FTN256AC              | 256        | 3.3     | 5               | Lead-free ftBGA | 256               | 128 | С     |

|         | LC4256V-75FTN256AC             | 256        | 3.3     | 7.5             | Lead-free ftBGA | 256               | 128 | С     |

|         | LC4256V-3FTN256BC              | 256        | 3.3     | 3               | Lead-free ftBGA | 256               | 160 | С     |

|         | LC4256V-5FTN256BC              | 256        | 3.3     | 5               | Lead-free ftBGA | 256               | 160 | С     |

|         | LC4256V-75FTN256BC             | 256        | 3.3     | 7.5             | Lead-free ftBGA | 256               | 160 | С     |

|         | LC4256V-3FN256AC1              | 256        | 3.3     | 3               | Lead-free fpBGA | 256               | 128 | С     |

|         | LC4256V-5FN256AC1              | 256        | 3.3     | 5               | Lead-free fpBGA | 256               | 128 | С     |

|         | LC4256V-75FN256AC1             | 256        | 3.3     | 7.5             | Lead-free fpBGA | 256               | 128 | С     |

|         | LC4256V-3FN256BC1              | 256        | 3.3     | 3               | Lead-free fpBGA | 256               | 160 | С     |

| LC4256V | LC4256V-5FN256BC <sup>1</sup>  | 256        | 3.3     | 5               | Lead-free fpBGA | 256               | 160 | С     |

|         | LC4256V-75FN256BC <sup>1</sup> | 256        | 3.3     | 7.5             | Lead-free fpBGA | 256               | 160 | С     |

|         | LC4256V-3TN176C                | 256        | 3.3     | 3               | Lead-free TQFP  | 176               | 128 | С     |

|         | LC4256V-5TN176C                | 256        | 3.3     | 5               | Lead-free TQFP  | 176               | 128 | С     |

|         | LC4256V-75TN176C               | 256        | 3.3     | 7.5             | Lead-free TQFP  | 176               | 128 | С     |

|         | LC4256V-3TN144C                | 256        | 3.3     | 3               | Lead-free TQFP  | 144               | 96  | С     |

|         | LC4256V-5TN144C                | 256        | 3.3     | 5               | Lead-free TQFP  | 144               | 96  | С     |

|         | LC4256V-75TN144C               | 256        | 3.3     | 7.5             | Lead-free TQFP  | 144               | 96  | С     |

|         | LC4256V-3TN100C                | 256        | 3.3     | 3               | Lead-free TQFP  | 100               | 64  | С     |

|         | LC4256V-5TN100C                | 256        | 3.3     | 5               | Lead-free TQFP  | 100               | 64  | С     |

|         | LC4256V-75TN100C               | 256        | 3.3     | 7.5             | Lead-free TQFP  | 100               | 64  | С     |

|         | LC4384V-35FTN256C              | 384        | 3.3     | 3.5             | Lead-free ftBGA | 256               | 192 | С     |

|         | LC4384V-5FTN256C               | 384        | 3.3     | 5               | Lead-free ftBGA | 256               | 192 | С     |

|         | LC4384V-75FTN256C              | 384        | 3.3     | 7.5             | Lead-free ftBGA | 256               | 192 | С     |

|         | LC4384V-35FN256C1              | 384        | 3.3     | 3.5             | Lead-free fpBGA | 256               | 192 | С     |

| LC4384V | LC4384V-5FN256C <sup>1</sup>   | 384        | 3.3     | 5               | Lead-free fpBGA | 256               | 192 | С     |

|         | LC4384V-75FN256C1              | 384        | 3.3     | 7.5             | Lead-free fpBGA | 256               | 192 | С     |

|         | LC4384V-35TN176C               | 384        | 3.3     | 3.5             | Lead-free TQFP  | 176               | 128 | С     |

|         | LC4384V-5TN176C                | 384        | 3.3     | 5               | Lead-free TQFP  | 176               | 128 | С     |

|         | LC4384V-75TN176C               | 384        | 3.3     | 7.5             | Lead-free TQFP  | 176               | 128 | С     |

|         | LC4512V-35FTN256C              | 512        | 3.3     | 3.5             | Lead-free ftBGA | 256               | 208 | С     |

|         | LC4512V-5FTN256C               | 512        | 3.3     | 5               | Lead-free ftBGA | 256               | 208 | С     |

|         | LC4512V-75FTN256C              | 512        | 3.3     | 7.5             | Lead-free ftBGA | 256               | 208 | С     |

|         | LC4512V-35FN256C1              | 512        | 3.3     | 3.5             | Lead-free fpBGA | 256               | 208 | С     |

| LC4512V | LC4512V-5FN256C <sup>1</sup>   | 512        | 3.3     | 5               | Lead-free fpBGA | 256               | 208 | С     |

|         | LC4512V-75FN256C <sup>1</sup>  | 512        | 3.3     | 7.5             | Lead-free fpBGA | 256               | 208 | С     |

|         | LC4512V-35TN176C               | 512        | 3.3     | 3.5             | Lead-free TQFP  | 176               | 128 | С     |

|         | LC4512V-5TN176C                | 512        | 3.3     | 5               | Lead-free TQFP  | 176               | 128 | С     |

|         | LC4512V-75TN176C               | 512        | 3.3     | 7.5             | Lead-free TQFP  | 176               | 128 | С     |

<sup>1.</sup> Use ftBGA package. fpBGA package devices have been discontinued via PCN#14A-07.

## ispMACH 4000V (3.3V) Lead-Free Industrial Devices

| Device  | Part Number      | Macrocells | Voltage | t <sub>PD</sub> | Package        | Pin/Ball<br>Count | I/O | Grade |

|---------|------------------|------------|---------|-----------------|----------------|-------------------|-----|-------|

|         | LC4032V-5TN48I   | 32         | 3.3     | 5               | Lead-free TQFP | 48                | 32  | I     |

|         | LC4032V-75TN48I  | 32         | 3.3     | 7.5             | Lead-free TQFP | 48                | 32  | I     |

| LC4032V | LC4032V-10TN48I  | 32         | 3.3     | 10              | Lead-free TQFP | 48                | 32  | I     |

| LC4032V | LC4032V-5TN44I   | 32         | 3.3     | 5               | Lead-free TQFP | 44                | 30  | I     |

|         | LC4032V-75TN44I  | 32         | 3.3     | 7.5             | Lead-free TQFP | 44                | 30  | I     |

|         | LC4032V-10TN44I  | 32         | 3.3     | 10              | Lead-free TQFP | 44                | 30  | I     |