Welcome to **E-XFL.COM**

**Understanding Embedded - CPLDs (Complex Programmable Logic Devices)**

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixed-function ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

| Details                         |                                                                              |

|---------------------------------|------------------------------------------------------------------------------|

| Product Status                  | Active                                                                       |

| Programmable Type               | In System Programmable                                                       |

| Delay Time tpd(1) Max           | 5 ns                                                                         |

| Voltage Supply - Internal       | 3V ~ 3.6V                                                                    |

| Number of Logic Elements/Blocks | 16                                                                           |

| Number of Macrocells            | 256                                                                          |

| Number of Gates                 | -                                                                            |

| Number of I/O                   | 128                                                                          |

| Operating Temperature           | -40°C ~ 105°C (TJ)                                                           |

| Mounting Type                   | Surface Mount                                                                |

| Package / Case                  | 256-LBGA                                                                     |

| Supplier Device Package         | 256-FTBGA (17x17)                                                            |

| Purchase URL                    | https://www.e-xfl.com/product-detail/lattice-semiconductor/lc4256v-5ftn256ai |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Block CLK2

- Block CLK3

- PT Clock

- PT Clock Inverted

- Shared PT Clock

- Ground

### **Clock Enable Multiplexer**

Each macrocell has a 4:1 clock enable multiplexer. This allows the clock enable signal to be selected from the following four sources:

- PT Initialization/CE

- PT Initialization/CE Inverted

- Shared PT Clock

- Logic High

#### **Initialization Control**

The ispMACH 4000 family architecture accommodates both block-level and macrocell-level set and reset capability. There is one block-level initialization term that is distributed to all macrocell registers in a GLB. At the macrocell level, two product terms can be "stolen" from the cluster associated with a macrocell to be used for set/reset functionality. A reset/preset swapping feature in each macrocell allows for reset and preset to be exchanged, providing flexibility.

Note that the reset/preset swapping selection feature affects power-up reset as well. All flip-flops power up to a known state for predictable system initialization. If a macrocell is configured to SET on a signal from the block-level initialization, then that macrocell will be SET during device power-up. If a macrocell is configured to RESET on a signal from the block-level initialization or is not configured for set/reset, then that macrocell will RESET on power-up. To guarantee initialization values, the  $V_{CC}$  rise must be monotonic, and the clock must be inactive until the reset delay time has elapsed.

#### **GLB Clock Generator**

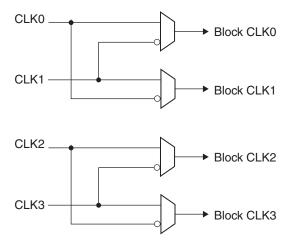

Each ispMACH 4000 device has up to four clock pins that are also routed to the GRP to be used as inputs. These pins drive a clock generator in each GLB, as shown in Figure 6. The clock generator provides four clock signals that can be used anywhere in the GLB. These four GLB clock signals can consist of a number of combinations of the true and complement edges of the global clock signals.

Figure 6. GLB Clock Generator

## **Output Routing Pool (ORP)**

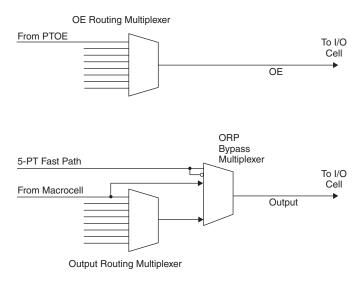

The Output Routing Pool allows macrocell outputs to be connected to any of several I/O cells within an I/O block. This provides greater flexibility in determining the pinout and allows design changes to occur without affecting the pinout. The output routing pool also provides a parallel capability for routing macrocell-level OE product terms. This allows the OE product term to follow the macrocell output as it is switched between I/O cells. Additionally, the output routing pool allows the macrocell output or true and complement forms of the 5-PT bypass signal to bypass the output routing multiplexers and feed the I/O cell directly. The enhanced ORP of the ispMACH 4000 family consists of the following elements:

- · Output Routing Multiplexers

- OE Routing Multiplexers

- Output Routing Pool Bypass Multiplexers

Figure 7 shows the structure of the ORP from the I/O cell perspective. This is referred to as an ORP slice. Each ORP has as many ORP slices as there are I/O cells in the corresponding I/O block.

Figure 7. ORP Slice

### **Output Routing Multiplexers**

The details of connections between the macrocells and the I/O cells vary across devices and within a device dependent on the maximum number of I/Os available. Tables 5-9 provide the connection details.

Table 6. ORP Combinations for I/O Blocks with 8 I/Os

| I/O Cell | Available Macrocells                 |

|----------|--------------------------------------|

| I/O 0    | M0, M1, M2, M3, M4, M5, M6, M7       |

| I/O 1    | M2, M3, M4, M5, M6, M7, M8, M9       |

| I/O 2    | M4, M5, M6, M7, M8, M9, M10, M11     |

| I/O 3    | M6, M7, M8, M9, M10, M11, M12, M13   |

| I/O 4    | M8, M9, M10, M11, M12, M13, M14, M15 |

| I/O 5    | M10, M11, M12, M13, M14, M15, M0, M1 |

| I/O 6    | M12, M13, M14, M15, M0, M1, M2, M3   |

| I/O 7    | M14, M15, M0, M1, M2, M3, M4, M5     |

Table 10. ORP Combinations for I/O Blocks with 12 I/Os

| I/O Cell | Available Macrocells                 |

|----------|--------------------------------------|

| I/O 0    | M0, M1, M2, M3, M4, M5, M6, M7       |

| I/O 1    | M1, M2, M3, M4, M5, M6, M7, M8       |

| I/O 2    | M2, M3, M4, M5, M6, M7, M8, M9       |

| I/O 3    | M4, M5, M6, M7, M8, M9, M10, M11     |

| I/O 4    | M5, M6, M7, M8, M9, M10, M11, M12    |

| I/O 5    | M6, M7, M8, M9, M10, M11, M12, M13   |

| I/O 6    | M8, M9, M10, M11, M12, M13, M14, M15 |

| I/O 7    | M9, M10, M11, M12, M13, M14, M15, M0 |

| I/O 8    | M10, M11, M12, M13, M14, M15, M0, M1 |

| I/O 9    | M12, M13, M14, M15, M0, M1, M2, M3   |

| I/O 10   | M13, M14, M15, M0, M1, M2, M3, M4    |

| I/O 11   | M14, M15, M0, M1, M2, M3, M4, M5     |

### **ORP Bypass and Fast Output Multiplexers**

The ORP bypass and fast-path output multiplexer is a 4:1 multiplexer and allows the 5-PT fast path to bypass the ORP and be connected directly to the pin with either the regular output or the inverted output. This multiplexer also allows the register output to bypass the ORP to achieve faster t<sub>CO</sub>.

## **Output Enable Routing Multiplexers**

The OE Routing Pool provides the corresponding local output enable (OE) product term to the I/O cell.

### I/O Cell

The I/O cell contains the following programmable elements: output buffer, input buffer, OE multiplexer and bus maintenance circuitry. Figure 8 details the I/O cell.

Figure 8. I/O Cell

Each output supports a variety of output standards dependent on the  $V_{CCO}$  supplied to its I/O bank. Outputs can also be configured for open drain operation. Each input can be programmed to support a variety of standards, independent of the  $V_{CCO}$  supplied to its I/O bank. The I/O standards supported are:

- LVTTL

- LVCMOS 1.8

- LVCMOS 3.3

- 3.3V PCI Compatible

- LVCMOS 2.5

All of the I/Os and dedicated inputs have the capability to provide a bus-keeper latch, Pull-up Resistor or Pull-down Resistor. A fourth option is to provide none of these. The selection is done on a global basis. The default in both hardware and software is such that when the device is erased or if the user does not specify, the input structure is configured to be a Pull-up Resistor.

Each ispMACH 4000 device I/O has an individually programmable output slew rate control bit. Each output can be individually configured for fast slew or slow slew. The typical edge rate difference between fast and slow slew setting is 20%. For high-speed designs with long, unterminated traces, the slow-slew rate will introduce fewer reflections, less noise and keep ground bounce to a minimum. For designs with short traces or well terminated lines, the fast slew rate can be used to achieve the highest speed.

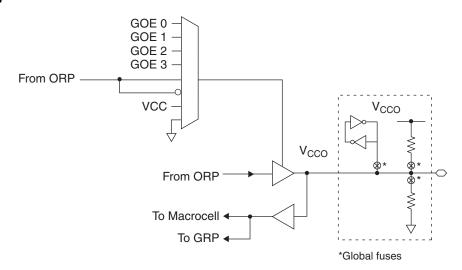

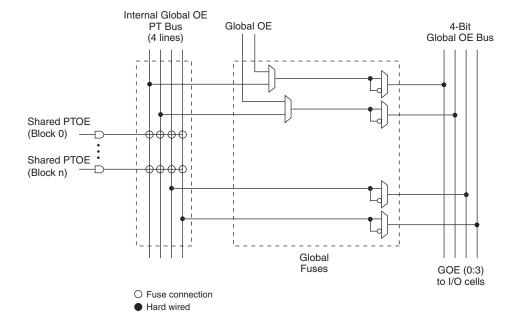

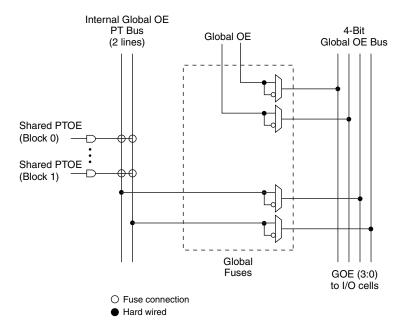

#### **Global OE Generation**

Most ispMACH 4000 family devices have a 4-bit wide Global OE Bus, except the ispMACH 4032 device that has a 2-bit wide Global OE Bus. This bus is derived from a 4-bit internal global OE PT bus and two dual purpose I/O or GOE pins. Each signal that drives the bus can optionally be inverted.

Each GLB has a block-level OE PT that connects to all bits of the Global OE PT bus with four fuses. Hence, for a 256-macrocell device (with 16 blocks), each line of the bus is driven from 16 OE product terms. Figures 9 and 10 show a graphical representation of the global OE generation.

Figure 9. Global OE Generation for All Devices Except ispMACH 4032

Figure 10. Global OE Generation for ispMACH 4032

## **Zero Power/Low Power and Power Management**

The ispMACH 4000 family is designed with high speed low power design techniques to offer both high speed and low power. With an advanced E² low power cell and non sense-amplifier design approach (full CMOS logic approach), the ispMACH 4000 family offers SuperFAST pin-to-pin speeds, while simultaneously delivering low standby power without needing any "turbo bits" or other power management schemes associated with a traditional sense-amplifier approach.

The zero power ispMACH 4000Z is based on the 1.8V ispMACH 4000C family. With innovative circuit design changes, the ispMACH 4000Z family is able to achieve the industry's "lowest static power".

## **IEEE 1149.1-Compliant Boundary Scan Testability**

All ispMACH 4000 devices have boundary scan cells and are compliant to the IEEE 1149.1 standard. This allows functional testing of the circuit board on which the device is mounted through a serial scan path that can access all critical logic notes. Internal registers are linked internally, allowing test data to be shifted in and loaded directly onto test nodes, or test node data to be captured and shifted out for verification. In addition, these devices can be linked into a board-level serial scan path for more board-level testing. The test access port operates with an LVCMOS interface that corresponds to the power supply voltage.

## I/O Quick Configuration

To facilitate the most efficient board test, the physical nature of the I/O cells must be set before running any continuity tests. As these tests are fast, by nature, the overhead and time that is required for configuration of the I/Os' physical nature should be minimal so that board test time is minimized. The ispMACH 4000 family of devices allows this by offering the user the ability to quickly configure the physical nature of the I/O cells. This quick configuration takes milliseconds to complete, whereas it takes seconds for the entire device to be programmed. Lattice's ispVM<sup>®</sup> System programming software can either perform the quick configuration through the PC parallel port, or can generate the ATE or test vectors necessary for a third-party test system.

## Supply Current, ispMACH 4000Z (Cont.)

### **Over Recommended Operating Conditions**

| Symbol                    | Parameter                      | Condition                          | Min. | Тур. | Max. | Units     |

|---------------------------|--------------------------------|------------------------------------|------|------|------|-----------|

| ispMACH 4                 | 1256ZC                         |                                    |      |      |      | <u>.I</u> |

|                           |                                | Vcc = 1.8V, T <sub>A</sub> = 25°C  | _    | 341  | _    | μΑ        |

| ICC <sup>1, 2, 3, 5</sup> | Operating Power Supply Current | $Vcc = 1.9V, T_A = 70^{\circ}C$    | _    | 361  | _    | μΑ        |

| ICC <sup>1, 2, 3, 3</sup> | Operating Power Supply Current | $Vcc = 1.9V, T_A = 85^{\circ}C$    | _    | 372  | _    | μΑ        |

|                           |                                | Vcc = 1.9V, T <sub>A</sub> = 125°C | _    | 468  | _    | μΑ        |

|                           |                                | Vcc = 1.8V, T <sub>A</sub> = 25°C  | _    | 13   | _    | μΑ        |

| ICC <sup>4, 5</sup>       | Standby Power Supply Current   | $Vcc = 1.9V, T_A = 70^{\circ}C$    | _    | 32   | 55   | μΑ        |

| 100                       | Standby Fower Supply Current   | $Vcc = 1.9V, T_A = 85^{\circ}C$    | _    | 43   | 90   | μΑ        |

|                           |                                | Vcc = 1.9V, T <sub>A</sub> = 125°C | _    | 135  | _    | μΑ        |

<sup>1.</sup>  $T_A = 25$ °C, frequency = 1.0 MHz.

Device configured with 16-bit counters.

I<sub>CC</sub> varies with specific device configuration and operating frequency.

<sup>4.</sup>  $V_{CCO}$  = 3.6V,  $V_{IN}$  = 0V or  $V_{CCO}$ , bus maintenance turned off.  $V_{IN}$  above  $V_{CCO}$  will add transient current above the specified standby  $I_{CC}$ .

<sup>5.</sup> Includes V<sub>CCO</sub> current without output loading.

## ispMACH 4000Z External Switching Characteristics (Cont.)

### **Over Recommended Operating Conditions**

|                               |                                                                                   | -4   | -45  |      | 5    | -75  |      |       |

|-------------------------------|-----------------------------------------------------------------------------------|------|------|------|------|------|------|-------|

| Parameter                     | Description <sup>1, 2, 3</sup>                                                    | Min. | Max. | Min. | Max. | Min. | Max. | Units |

| t <sub>PD</sub>               | 5-PT bypass combinatorial propagation delay                                       | _    | 4.5  | _    | 5.0  | _    | 7.5  | ns    |

| t <sub>PD_MC</sub>            | 20-PT combinatorial propagation delay through macrocell                           | _    | 5.8  | _    | 6.0  | _    | 8.0  | ns    |

| t <sub>S</sub>                | GLB register setup time before clock                                              | 2.9  | _    | 3.0  | _    | 4.5  | _    | ns    |

| t <sub>ST</sub>               | GLB register setup time before clock with T-type register                         | 3.1  | _    | 3.2  | _    | 4.7  | _    | ns    |

| t <sub>SIR</sub>              | GLB register setup time before clock, input register path                         | 1.3  | _    | 1.3  | _    | 1.4  | _    | ns    |

| t <sub>SIRZ</sub>             | GLB register setup time before clock with zero hold                               | 2.6  | _    | 2.6  | _    | 2.7  | _    | ns    |

| t <sub>H</sub>                | GLB register hold time after clock                                                | 0.0  | _    | 0.0  | _    | 0.0  | _    | ns    |

| t <sub>HT</sub>               | GLB register hold time after clock with T-type register                           |      | _    | 0.0  | _    | 0.0  | _    | ns    |

| t <sub>HIR</sub>              | GLB register hold time after clock, input register path                           | 1.3  | _    | 1.3  | _    | 1.3  | _    | ns    |

| t <sub>HIRZ</sub>             | GLB register hold time after clock, input register path with zero hold            | 0.0  | _    | 0.0  | _    | 0.0  | _    | ns    |

| t <sub>CO</sub>               | GLB register clock-to-output delay                                                | _    | 3.8  | _    | 4.2  | _    | 4.5  | ns    |

| t <sub>R</sub>                | External reset pin to output delay                                                | _    | 7.5  | _    | 7.5  | _    | 9.0  | ns    |

| t <sub>RW</sub>               | External reset pulse duration                                                     | 2.0  | _    | 2.0  | _    | 4.0  | _    | ns    |

| t <sub>PTOE/DIS</sub>         | Input to output local product term output enable/disable                          | _    | 8.2  | _    | 8.5  | _    | 9.0  | ns    |

| t <sub>GPTOE/DIS</sub>        | Input to output global product term output enable/disable                         | _    | 10.0 | _    | 10.0 | _    | 10.5 | ns    |

| t <sub>GOE/DIS</sub>          | Global OE input to output enable/disable                                          | _    | 5.5  | _    | 6.0  | _    | 7.0  | ns    |

| t <sub>CW</sub>               | Global clock width, high or low                                                   | 1.8  | _    | 2.0  | _    | 2.8  | _    | ns    |

| t <sub>GW</sub>               | Global gate width low (for low transparent) or high (for high transparent)        | 1.8  | _    | 2.0  | _    | 2.8  | _    | ns    |

| t <sub>WIR</sub>              | Input register clock width, high or low                                           | 1.8  | _    | 2.0  | _    | 2.8  | _    | ns    |

| f <sub>MAX</sub> <sup>4</sup> | Clock frequency with internal feedback                                            |      | 200  | _    | 200  | _    | 168  | MHz   |

| f <sub>MAX</sub> (Ext.)       | clock frequency with external feedback, [1 / (t <sub>S</sub> + t <sub>CO</sub> )] |      | 150  | _    | 139  |      | 111  | MHz   |

<sup>1.</sup> Timing numbers are based on default LVCMOS 1.8 I/O buffers. Use timing adjusters provided to calculate other standards.

Timing v.2.2

<sup>2.</sup> Measured using standard switching GRP loading of 1 and 1 output switching.

<sup>3.</sup> Pulse widths and clock widths less than minimum will cause unknown behavior.

<sup>4.</sup> Standard 16-bit counter using GRP feedback.

## ispMACH 4000Z Internal Timing Parameters (Cont.)

### **Over Recommended Operating Conditions**

|                    |                       |      | 35   | -3   | 37   | -4   | 2    |       |

|--------------------|-----------------------|------|------|------|------|------|------|-------|

| Parameter          | Description           | Min. | Max. | Min. | Max. | Min. | Max. | Units |

| t <sub>GPTOE</sub> | Global PT OE Delay    | _    | 1.9  | _    | 2.35 | _    | 2.60 | ns    |

| t <sub>PTOE</sub>  | Macrocell PT OE Delay | _    | 2.4  | _    | 3.35 | _    | 2.60 | ns    |

Note: Internal Timing Parameters are not tested and are for reference only. Refer to the timing model in this data sheet for further details.

Timing v.2.2

## ispMACH 4000Z Internal Timing Parameters (Cont.)

## **Over Recommended Operating Conditions**

|                   |                       | -4   | 15   | -:   | 5    | -7   | '5   |       |

|-------------------|-----------------------|------|------|------|------|------|------|-------|

| Parameter         | Description           | Min. | Max. | Min. | Max. | Min. | Max. | Units |

| t <sub>PTOE</sub> | Macrocell PT OE Delay | _    | 2.50 | _    | 2.70 | _    | 2.00 | ns    |

Note: Internal Timing Parameters are not tested and are for reference only. Refer to the timing model in this data sheet for further details.

Timing v.2.2

## **Boundary Scan Waveforms and Timing Specifications**

| Symbol              | Parameter                                                      | Min. | Max. | Units |

|---------------------|----------------------------------------------------------------|------|------|-------|

| t <sub>BTCP</sub>   | TCK [BSCAN test] clock cycle                                   | 40   | _    | ns    |

| t <sub>BTCH</sub>   | TCK [BSCAN test] pulse width high                              | 20   | _    | ns    |

| t <sub>BTCL</sub>   | TCK [BSCAN test] pulse width low                               | 20   | _    | ns    |

| t <sub>BTSU</sub>   | TCK [BSCAN test] setup time                                    | 8    | _    | ns    |

| t <sub>BTH</sub>    | TCK [BSCAN test] hold time                                     | 10   | _    | ns    |

| t <sub>BRF</sub>    | TCK [BSCAN test] rise and fall time                            | 50   | _    | mV/ns |

| t <sub>BTCO</sub>   | TAP controller falling edge of clock to valid output           | —    | 10   | ns    |

| t <sub>BTOZ</sub>   | TAP controller falling edge of clock to data output disable    | —    | 10   | ns    |

| t <sub>BTVO</sub>   | TAP controller falling edge of clock to data output enable     | _    | 10   | ns    |

| t <sub>BTCPSU</sub> | BSCAN test Capture register setup time                         | 8    | _    | ns    |

| t <sub>BTCPH</sub>  | BSCAN test Capture register hold time                          | 10   | _    | ns    |

| t <sub>BTUCO</sub>  | BSCAN test Update reg, falling edge of clock to valid output   | _    | 25   | ns    |

| t <sub>BTUOZ</sub>  | BSCAN test Update reg, falling edge of clock to output disable | _    | 25   | ns    |

| t <sub>BTUOV</sub>  | BSCAN test Update reg, falling edge of clock to output enable  | _    | 25   | ns    |

# ispMACH 4032V/B/C and 4064V/B/C Logic Signal Connections: 44-Pin TQFP

|            |             | ispMACH 40    | 032V/B/C | ispMACH 40    | 64V/B/C |

|------------|-------------|---------------|----------|---------------|---------|

| Pin Number | Bank Number | GLB/MC/Pad    | ORP      | GLB/MC/Pad    | ORP     |

| 1          | -           | TDI           | -        | TDI           | -       |

| 2          | 0           | A5            | A^5      | A10           | A^5     |

| 3          | 0           | A6            | A^6      | A12           | A^6     |

| 4          | 0           | A7            | A^7      | A14           | A^7     |

| 5          | 0           | GND (Bank 0)  | -        | GND (Bank 0)  | -       |

| 6          | 0           | VCCO (Bank 0) | -        | VCCO (Bank 0) | -       |

| 7          | 0           | A8            | A^8      | B0            | B^0     |

| 8          | 0           | A9            | A^9      | B2            | B^1     |

| 9          | 0           | A10           | A^10     | B4            | B^2     |

| 10         | -           | TCK           | -        | TCK           | -       |

| 11         | -           | VCC           | -        | VCC           | -       |

| 12         | -           | GND           | -        | GND           | -       |

| 13         | 0           | A12           | A^12     | B8            | B^4     |

| 14         | 0           | A13           | A^13     | B10           | B^5     |

| 15         | 0           | A14           | A^14     | B12           | B^6     |

| 16         | 0           | A15           | A^15     | B14           | B^7     |

| 17         | 1           | CLK2/I        | -        | CLK2/I        | -       |

| 18         | 1           | B0            | B^0      | C0            | C^0     |

| 19         | 1           | B1            | B^1      | C2            | C^1     |

| 20         | 1           | B2            | B^2      | C4            | C^2     |

| 21         | 1           | B3            | B^3      | C6            | C^3     |

| 22         | 1           | B4            | B^4      | C8            | C^4     |

| 23         | -           | TMS           | -        | TMS           | -       |

| 24         | 1           | B5            | B^5      | C10           | C^5     |

| 25         | 1           | B6            | B^6      | C12           | C^6     |

| 26         | 1           | B7            | B^7      | C14           | C^7     |

| 27         | 1           | GND (Bank 1)  | -        | GND (Bank 1)  | -       |

| 28         | 1           | VCCO (Bank 1) | -        | VCCO (Bank 1) | -       |

| 29         | 1           | B8            | B^8      | D0            | D^0     |

| 30         | 1           | B9            | B^9      | D2            | D^1     |

| 31         | 1           | B10           | B^10     | D4            | D^2     |

| 32         | -           | TDO           | -        | TDO           | -       |

| 33         | -           | VCC           | -        | VCC           | -       |

| 34         | -           | GND           | -        | GND           | -       |

| 35         | 1           | B12           | B^12     | D8            | D^4     |

| 36         | 1           | B13           | B^13     | D10           | D^5     |

| 37         | 1           | B14           | B^14     | D12           | D^6     |

| 38         | 1           | B15/GOE1      | B^15     | D14/GOE1      | D^7     |

| 39         | 0           | CLK0/I        | -        | CLK0/I        | -       |

| 40         | 0           | A0/GOE0       | A^0      | A0/GOE0       | A^0     |

| 41         | 0           | A1            | A^1      | A2            | A^1     |

# ispMACH 4064Z, 4128Z and 4256Z Logic Signal Connections: 132-Ball csBGA (Cont.)

|                    |             | ispMACH       | 1 4064Z | ispMACH       | 1 4128Z | ispMACH       | 1 4256Z |

|--------------------|-------------|---------------|---------|---------------|---------|---------------|---------|

| <b>Ball Number</b> | Bank Number | GLB/MC/Pad    | ORP     | GLB/MC/Pad    | ORP     | GLB/MC/Pad    | ORP     |

| E3                 | 0           | NC            | -       | B8            | B^6     | D12           | D^6     |

| F2                 | 0           | A12           | A^12    | B9            | B^7     | D10           | D^5     |

| F1                 | 0           | A13           | A^13    | B10           | B^8     | D8            | D^4     |

| F3                 | 0           | A14           | A^14    | B12           | B^9     | D6            | D^3     |

| G1                 | 0           | A15           | A^15    | B13           | B^10    | D4            | D^2     |

| G2                 | 0           | I             | -       | B14           | B^11    | D2            | D^1     |

| G3                 | 0           | VCCO (Bank 0) | -       | VCCO (Bank 0) | -       | VCCO (Bank 0) | -       |

| H2                 | 0           | NC            | -       | C14           | C^11    | E2            | E^1     |

| H1                 | 0           | B15           | B^15    | C13           | C^10    | E4            | E^2     |

| H3                 | 0           | B14           | B^14    | C12           | C^9     | E6            | E^3     |

| J1                 | 0           | B13           | B^13    | C10           | C^8     | E8            | E^4     |

| J2                 | 0           | B12           | B^12    | C9            | C^7     | E10           | E^5     |

| J3                 | 0           | NC            | -       | C8            | C^6     | E12           | E^6     |

| K2                 | 0           | GND (Bank 0)  | -       | GND (Bank 0)  | -       | GND (Bank 0)  | -       |

| K1                 | 0           | NC            | -       | C6            | C^5     | F2            | F^1     |

| K3                 | 0           | B11           | B^11    | C5            | C^4     | F4            | F^2     |

| L2                 | 0           | B10           | B^10    | C4            | C^3     | F6            | F^3     |

| L1                 | 0           | B9            | B^9     | C2            | C^2     | F8            | F^4     |

| L3                 | 0           | B8            | B^8     | C1            | C^1     | F10           | F^5     |

| M1                 | 0           | I             | -       | C0            | C^0     | F12           | F^6     |

| M2                 | 0           | NC            | -       | VCCO (Bank 0) | -       | VCCO (Bank 0) | -       |

| N1                 | -           | TCK           | -       | TCK           | -       | TCK           | -       |

| P1                 | -           | VCC           | -       | VCC           | -       | VCC           | -       |

| P2                 | -           | GND           | -       | GND           | -       | GND           | -       |

| N2                 | 0           | I             | -       | D14           | D^11    | G12           | G^6     |

| P3                 | 0           | B7            | B^7     | D13           | D^10    | G10           | G^5     |

| M3                 | 0           | B6            | B^6     | D12           | D^9     | G8            | G^4     |

| N3                 | 0           | B5            | B^5     | D10           | D^8     | G6            | G^3     |

| P4                 | 0           | B4            | B^4     | D9            | D^7     | G4            | G^2     |

| M4                 | 0           | NC            | -       | D8            | D^6     | G2            | G^1     |

| N4                 | 0           | GND (Bank 0)  | -       | GND (Bank 0)  | -       | GND (Bank 0)  | -       |

| P5                 | 0           | VCCO (Bank 0) | -       | VCCO (Bank 0) | -       | VCCO (Bank 0) | -       |

| N5                 | 0           | NC            | -       | D6            | D^5     | H12           | H^6     |

| M5                 | 0           | B3            | B^3     | D5            | D^4     | H10           | H^5     |

| N6                 | 0           | B2            | B^2     | D4            | D^3     | H8            | H^4     |

| P6                 | 0           | B1            | B^1     | D2            | D^2     | H6            | H^3     |

| M6                 | 0           | B0            | B^0     | D1            | D^1     | H4            | H^2     |

| P7                 | 0           | NC            | -       | D0            | D^0     | H2            | H^1     |

| N7                 | 0           | CLK1/I        | -       | CLK1/I        | -       | CLK1/I        |         |

| M7                 | 1           | CLK2/I        | _       | CLK2/I        |         | CLK2/I        |         |

| N8                 | -           | VCC           | -       | VCC           | -       | VCC           | -       |

# ispMACH 4256V/B/C/Z, 4384V/B/C, 4512V/B/C, Logic Signal Connections: 176-Pin TQFP (Cont.)

|            | Bank   | ispMACH 4256V/B/C/Z |     | ispMACH 4     | 384V/B/C | 4V/B/C ispMACH 4512 |      |  |

|------------|--------|---------------------|-----|---------------|----------|---------------------|------|--|

| Pin Number | Number | GLB/MC/Pad          | ORP | GLB/MC/Pad    | ORP      | GLB/MC/Pad          | ORP  |  |

| 60         | 0      | H8                  | H^4 | L8            | L^4      | P8                  | P^4  |  |

| 61         | 0      | H6                  | H^3 | L6            | L^3      | P6                  | P^3  |  |

| 62         | 0      | H4                  | H^2 | L4            | L^2      | P4                  | P^2  |  |

| 63         | 0      | H2                  | H^1 | L2            | L^1      | P2                  | P^1  |  |

| 64         | 0      | H0                  | H^0 | LO            | L^0      | P0                  | P^0  |  |

| 65         | -      | GND                 | -   | GND           | -        | GND                 | -    |  |

| 66         | 0      | CLK1/I              | -   | CLK1/I        | -        | CLK1/I              | -    |  |

| 67         | 1      | GND (Bank 1)        | -   | GND (Bank 1)  | -        | GND (Bank 1)        | -    |  |

| 68         | 1      | CLK2/I              | -   | CLK2/I        | -        | CLK2/I              | -    |  |

| 69         | -      | VCC                 | -   | VCC           | -        | VCC                 | -    |  |

| 70         | 1      | 10                  | I^0 | MO            | M^0      | AX0                 | AX^0 |  |

| 71         | 1      | I2                  | I^1 | M2            | M^1      | AX2                 | AX^1 |  |

| 72         | 1      | 14                  | I^2 | M4            | M^2      | AX4                 | AX^2 |  |

| 73         | 1      | 16                  | I^3 | M6            | M^3      | AX6                 | AX^3 |  |

| 74         | 1      | 18                  | I^4 | M8            | M^4      | AX8                 | AX^4 |  |

| 75         | 1      | I10                 | I^5 | M10           | M^5      | AX10                | AX^5 |  |

| 76         | 1      | l12                 | I^6 | M12           | M^6      | AX12                | AX^6 |  |

| 77         | 1      | l14                 | I^7 | M14           | M^7      | AX14                | AX^7 |  |

| 78         | 1      | VCCO (Bank 1)       | -   | VCCO (Bank 1) | -        | VCCO (Bank 1)       | -    |  |

| 79         | 1      | GND (Bank 1)        | -   | GND (Bank 1)  | -        | GND (Bank 1)        | -    |  |

| 80         | 1      | J0                  | J^0 | N0            | N^0      | BX0                 | BX^0 |  |

| 81         | 1      | J2                  | J^1 | N2            | N^1      | BX2                 | BX^1 |  |

| 82         | 1      | J4                  | J^2 | N4            | N^2      | BX4                 | BX^2 |  |

| 83         | 1      | J6                  | J^3 | N6            | N^3      | BX6                 | BX^3 |  |

| 84         | 1      | J8                  | J^4 | N8            | N^4      | BX8                 | BX^4 |  |

| 85         | 1      | J10                 | J^5 | N10           | N^5      | BX10                | BX^5 |  |

| 86         | 1      | J12                 | J^6 | N12           | N^6      | BX12                | BX^6 |  |

| 87         | 1      | J14                 | J^7 | N14           | N^7      | BX14                | BX^7 |  |

| 88         | -      | VCC                 | -   | VCC           | -        | VCC                 | -    |  |

| 89         | -      | NC                  | -   | NC            | -        | NC                  | -    |  |

| 90         | -      | GND                 | -   | GND           | -        | GND                 | -    |  |

| 91         | -      | TMS                 | -   | TMS           | -        | TMS                 | -    |  |

| 92         | 1      | VCCO (Bank 1)       | -   | VCCO (Bank 1) | -        | VCCO (Bank 1)       | -    |  |

| 93         | 1      | K14                 | K^7 | O14           | O^7      | CX14                | CX^7 |  |

| 94         | 1      | K12                 | K^6 | O12           | O^6      | CX12                | CX^6 |  |

| 95         | 1      | K10                 | K^5 | O10           | O^5      | CX10                | CX^5 |  |

| 96         | 1      | K8                  | K^4 | O8            | 0^4      | CX8                 | CX^4 |  |

| 97         | 1      | K6                  | K^3 | O6            | O^3      | CX6                 | CX^3 |  |

| 98         | 1      | K4                  | K^2 | 04            | O^2      | CX4                 | CX^2 |  |

| 99         | 1      | K2                  | K^1 | O2            | O^1      | CX2                 | CX^1 |  |

| 100        | 1      | K0                  | K^0 | 00            | O^0      | CX0                 | CX^0 |  |

# ispMACH 4256V/B/C/Z, 4384V/B/C, 4512V/B/C, Logic Signal Connections: 176-Pin TQFP (Cont.)

|            | Bank   | ispMACH 425   | 56V/B/C/Z | ispMACH 43    | 384V/B/C | ispMACH 4     | 512V/B/C |

|------------|--------|---------------|-----------|---------------|----------|---------------|----------|

| Pin Number | Number | GLB/MC/Pad    | ORP       | GLB/MC/Pad    | ORP      | GLB/MC/Pad    | ORP      |

| 142        | 1      | O0            | O^0       | GX0           | GX^0     | OX0           | OX^0     |

| 143        | 1      | GND (Bank 1)  | -         | GND (Bank 1)  | -        | GND (Bank 1)  | -        |

| 144        | 1      | VCCO (Bank 1) | -         | VCCO (Bank 1) | -        | VCCO (Bank 1) | -        |

| 145        | 1      | P14           | P^7       | HX14          | HX^7     | PX14          | PX^7     |

| 146        | 1      | P12           | P^6       | HX12          | HX^6     | PX12          | PX^6     |

| 147        | 1      | P10           | P^5       | HX10          | HX^5     | PX10          | PX^5     |

| 148        | 1      | P8            | P^4       | HX8           | HX^4     | PX8           | PX^4     |

| 149        | 1      | P6            | P^3       | HX6           | HX^3     | PX6           | PX^3     |

| 150        | 1      | P4            | P^2       | HX4           | HX^2     | PX4           | PX^2     |

| 151        | 1      | P2/GOE1       | P^1       | HX2/GOE1      | HX^1     | PX2/GOE1      | PX^1     |

| 152        | 1      | P0            | P^0       | HX0           | HX^0     | PX0           | PX^0     |

| 153        | -      | GND           | -         | GND           | -        | GND           | -        |

| 154        | 1      | CLK3/I        | -         | CLK3/I        | -        | CLK3/I        | -        |

| 155        | 0      | GND (Bank 0)  | -         | GND (Bank 0)  | -        | GND (Bank 0)  | -        |

| 156        | 0      | CLK0/I        | -         | CLK0/I        | -        | CLK0/I        | -        |

| 157        | -      | VCC           | -         | VCC           | -        | VCC           | -        |

| 158        | 0      | A0            | A^0       | A0            | A^0      | A0            | A^0      |

| 159        | 0      | A2/GOE0       | A^1       | A2/GOE0       | A^1      | A2//GOE0      | A^1      |

| 160        | 0      | A4            | A^2       | A4            | A^2      | A4            | A^2      |

| 161        | 0      | A6            | A^3       | A6            | A^3      | A6            | A^3      |

| 162        | 0      | A8            | A^4       | A8            | A^4      | A8            | A^4      |

| 163        | 0      | A10           | A^5       | A10           | A^5      | A10           | A^5      |

| 164        | 0      | A12           | A^6       | A12           | A^6      | A12           | A^6      |

| 165        | 0      | A14           | A^7       | A14           | A^7      | A14           | A^7      |

| 166        | 0      | VCCO (Bank 0) | -         | VCCO (Bank 0) | -        | VCCO (Bank 0) | -        |

| 167        | 0      | GND (Bank 0)  | -         | GND (Bank 0)  | -        | GND (Bank 0)  | -        |

| 168        | 0      | В0            | B^0       | В0            | B^0      | В0            | B^0      |

| 169        | 0      | B2            | B^1       | B2            | B^1      | B2            | B^1      |

| 170        | 0      | B4            | B^2       | B4            | B^2      | B4            | B^2      |

| 171        | 0      | B6            | B^3       | B6            | B^3      | B6            | B^3      |

| 172        | 0      | B8            | B^4       | B8            | B^4      | B8            | B^4      |

| 173        | 0      | B10           | B^5       | B10           | B^5      | B10           | B^5      |

| 174        | 0      | B12           | B^6       | B12           | B^6      | B12           | B^6      |

| 175        | 0      | B14           | B^7       | B14           | B^7      | B14           | B^7      |

| 176        | -      | VCC           | -         | VCC           | -        | VCC           | -        |

# ispMACH 4256V/B/C, 4384V/B/C, 4512V/B/C Logic Signal Connections: 256-Ball ftBGA/fpBGA

| Ball   | I/O  | ispMACH 4256V/B/C<br>128-I/O |     | ispMACH 4256<br>160-I/O | V/B/C | ispMACH 4384V/B/C |     | ispMACH 4512V/B/C |     |

|--------|------|------------------------------|-----|-------------------------|-------|-------------------|-----|-------------------|-----|

| Number | Bank | GLB/MC/Pad                   | ORP | GLB/MC/Pad              | ORP   | GLB/MC/Pad        | ORP | GLB/MC/Pad        | ORP |

| -      | -    | -                            | -   | -                       | -     | VCC               | -   | VCC               | -   |

| -      | -    | GND                          | -   | GND                     | -     | GND               | -   | GND               | -   |

| C3     | -    | TDI                          | -   | TDI                     | -     | TDI               | -   | TDI               | -   |

| -      | 0    | VCCO (Bank 0)                | -   | VCCO (Bank 0)           | -     | VCCO (Bank 0)     | -   | VCCO (Bank 0)     | -   |

| B1     | 0    | C14                          | C^7 | C14                     | C^9   | C14               | C^7 | C14               | C^7 |

| F5     | 0    | C12                          | C^6 | C12                     | C^8   | C12               | C^6 | C12               | C^6 |

| D3     | 0    | C10                          | C^5 | C10                     | C^7   | C10               | C^5 | C10               | C^5 |

| C1     | 0    | C8                           | C^4 | C9                      | C^6   | C8                | C^4 | C8                | C^4 |

| C2     | 0    | C6                           | C^3 | C8                      | C^5   | C6                | C^3 | C6                | C^3 |

| E3     | 0    | C4                           | C^2 | C6                      | C^4   | C4                | C^2 | C4                | C^2 |

| D2     | 0    | C2                           | C^1 | C4                      | C^3   | C2                | C^1 | C2                | C^1 |

| F6     | 0    | C0                           | C^0 | C2                      | C^2   | C0                | C^0 | C0                | C^0 |

| D1     | 0    | NC                           | -   | C1                      | C^1   | F6                | F^3 | H0                | H^0 |

| E2     | 0    | NC                           | -   | C0                      | C^0   | F4                | F^2 | H4                | H^1 |

| E4     | 0    | NC                           | -   | NC                      | -     | D6                | D^3 | F4                | F^2 |

| G5     | 0    | NC                           | -   | NC                      | -     | D4                | D^2 | F6                | F^3 |

| E1     | 0    | NC                           | -   | NC                      | -     | NC                | -   | F8                | F^4 |

| -      | 0    | -                            | -   | VCCO (Bank 0)           | -     | VCCO (Bank 0)     | -   | VCCO (Bank 0)     | -   |

| -      | 0    | GND (Bank 0)                 | -   | GND (Bank 0)            | -     | GND (Bank 0)      | -   | GND (Bank 0)      | -   |

| F2     | 0    | NC                           | -   | NC                      | -     | NC                | -   | F10               | F^5 |

| F1     | 0    | NC                           | -   | NC                      | -     | D2                | D^1 | F12               | F^6 |

| G1     | 0    | NC                           | -   | NC                      | -     | D0                | D^0 | F14               | F^7 |

| G6     | 0    | NC                           | -   | D14                     | D^9   | F2                | F^1 | H8                | H^2 |

| G4     | 0    | NC                           | -   | D12                     | D^8   | F0                | F^0 | H12               | H^3 |

| H6     | 0    | D14                          | D^7 | D10                     | D^7   | E14               | E^7 | G14               | G^7 |

| G3     | 0    | D12                          | D^6 | D9                      | D^6   | E12               | E^6 | G12               | G^6 |

| H5     | 0    | D10                          | D^5 | D8                      | D^5   | E10               | E^5 | G10               | G^5 |

| G2     | 0    | D8                           | D^4 | D6                      | D^4   | E8                | E^4 | G8                | G^4 |

| H1     | 0    | D6                           | D^3 | D4                      | D^3   | E6                | E^3 | G6                | G^3 |

| H2     | 0    | D4                           | D^2 | D2                      | D^2   | E4                | E^2 | G4                | G^2 |

| H3     | 0    | D2                           | D^1 | D1                      | D^1   | E2                | E^1 | G2                | G^1 |

| H4     | 0    | D0                           | D^0 | D0                      | D^0   | E0                | E^0 | G0                | G^0 |

| -      | 0    | VCCO (Bank 0)                | -   | VCCO (Bank 0)           | -     | VCCO (Bank 0)     | -   | VCCO (Bank 0)     | -   |

| -      | 0    | -                            | -   | GND (Bank 0)            | -     | GND (Bank 0)      | -   | GND (Bank 0)      | -   |

| J4     | 0    | E0                           | E^0 | E0                      | E^0   | H0                | H^0 | J0                | J^0 |

| J3     | 0    | E2                           | E^1 | E1                      | E^1   | H2                | H^1 | J2                | J^1 |

| J2     | 0    | E4                           | E^2 | E2                      | E^2   | H4                | H^2 | J4                | J^2 |

| J1     | 0    | E6                           | E^3 | E4                      | E^3   | H6                | H^3 | J6                | J^3 |

| K1     | 0    | E8                           | E^4 | E6                      | E^4   | H8                | H^4 | J8                | J^4 |

| J5     | 0    | E10                          | E^5 | E8                      | E^5   | H10               | H^5 | J10               | J^5 |

| K2     | 0    | E12                          | E^6 | E9                      | E^6   | H12               | H^6 | J12               | J^6 |

# ispMACH 4256V/B/C, 4384V/B/C, 4512V/B/C Logic Signal Connections: 256-Ball ftBGA/fpBGA (Cont.)

| Ball   | I/O  | ispMACH 4256V/B/C<br>128-I/O |     | ispMACH 4256<br>160-I/O | V/B/C | ispMACH 4384V/B/C |           | ispMACH 4512V/B/C |     |  |

|--------|------|------------------------------|-----|-------------------------|-------|-------------------|-----------|-------------------|-----|--|

| Number | Bank | GLB/MC/Pad                   | ORP | GLB/MC/Pad              | ORP   | GLB/MC/Pad        | ORP       | GLB/MC/Pad        | ORP |  |

| J6     | 0    | E14                          | E^7 | E10                     | E^7   | H14               | H^7       | J14               | J^7 |  |

| K3     | 0    | NC                           | -   | E12                     | E^8   | G0                | G^0       | 10                | I^0 |  |

| K4     | 0    | NC                           | -   | E14                     | E^9   | G2                | G^1       | 14                | I^1 |  |

| L1     | 0    | NC                           | -   | NC                      | -     | l14               | I^7       | K0                | K^0 |  |

| L2     | 0    | NC                           | -   | NC                      | -     | l12               | I^6       | K2                | K^1 |  |

| M1     | 0    | NC                           | -   | NC                      | -     | NC                | -         | K4                | K^2 |  |

| -      | 0    | GND (Bank 0)                 | -   | GND (Bank 0)            | -     | GND (Bank 0)      | -         | GND (Bank 0)      | -   |  |

| -      | 0    | -                            | -   | VCCO (Bank 0)           | -     | VCCO (Bank 0)     | -         | VCCO (Bank 0)     | -   |  |

| M2     | 0    | NC                           | -   | NC                      | -     | NC                | -         | K6                | K^3 |  |

| N1     | 0    | NC                           | -   | NC                      | -     | I10               | I^5       | K8                | K^4 |  |

| M3     | 0    | NC                           | -   | NC                      | -     | 18                | I^4       | K10               | K^5 |  |

| M4     | 0    | NC                           | -   | F0                      | F^0   | G4                | G^2       | 18                | I^2 |  |

| N2     | 0    | NC                           | -   | F1                      | F^1   | G6                | G^3       | l12               | I^3 |  |

| K5     | 0    | F0                           | F^0 | F2                      | F^2   | J0                | J^0       | N0                | N^0 |  |

| P1     | 0    | F2                           | F^1 | F4                      | F^3   | J2                | J^1       | N2                | N^1 |  |

| K6     | 0    | F4                           | F^2 | F6                      | F^4   | J4                | J^2       | N4                | N^2 |  |

| N3     | 0    | F6                           | F^3 | F8                      | F^5   | J6                | J6 J^3 N6 |                   | N^3 |  |

| L5     | 0    | F8                           | F^4 | F9                      | F^6   | J8                | J^4       | N8                | N^4 |  |

| P2     | 0    | F10                          | F^5 | F10                     | F^7   | J10               | J^5       | N10               | N^5 |  |

| L6     | 0    | F12                          | F^6 | F12                     | F^8   | J12               | J^6       | N12               | N^6 |  |

| R1     | 0    | F14                          | F^7 | F14                     | F^9   | J14               | J^7       | N14               | N^7 |  |

| -      | 0    | VCCO (Bank 0)                | -   | VCCO (Bank 0)           | -     | VCCO (Bank 0)     | -         | VCCO (Bank 0)     | -   |  |

| P3     | -    | TCK                          | -   | TCK                     | -     | TCK               | -         | TCK               | -   |  |

| -      | -    | VCC                          | -   | VCC                     | -     | VCC               | -         | VCC               | -   |  |

| -      | -    | GND                          | -   | GND                     | -     | GND               | -         | GND               | -   |  |

| -      | 0    | -                            | -   | GND (Bank 0)            | -     | GND (Bank 0)      | -         | GND (Bank 0)      | -   |  |

| T2     | 0    | NC                           | -   | G14                     | G^9   | 16                | I^3       | K12               | K^6 |  |

| M5     | 0    | NC                           | -   | G12                     | G^8   | 14                | I^2       | K14               | K^7 |  |

| N4     | 0    | G14                          | G^7 | G10                     | G^7   | K14               | K^7       | O14               | O^7 |  |

| T3     | 0    | G12                          | G^6 | G9                      | G^6   | K12               | K^6       | O12               | O^6 |  |

| R3     | 0    | G10                          | G^5 | G8                      | G^5   | K10               | K^5       | O10               | O^5 |  |

| M6     | 0    | G8                           | G^4 | G6                      | G^4   | K8                | K^4       | O8                | 0^4 |  |

| P4     | 0    | G6                           | G^3 | G4                      | G^3   | K6                | K^3       | O6                | O^3 |  |

| L7     | 0    | G4                           | G^2 | G2                      | G^2   | K4                | K^2       | O4                | O^2 |  |

| N5     | 0    | G2                           | G^1 | G1                      | G^1   | K2                | K^1       | O2                | 0^1 |  |

| M7     | 0    | G0                           | G^0 | G0                      | G^0   | K0                | K^0       | 00                | O^0 |  |

| P5     | 0    | NC                           | -   | NC                      | -     | G8                | G^4       | MO                | M^0 |  |

| R4     | 0    | NC                           | -   | NC                      | -     | G10               | G^5       | M4                | M^1 |  |

| T4     | 0    | NC                           | -   | NC                      | -     | NC                | -         | LO                | L^0 |  |

| -      | 0    | GND (Bank 0)                 | -   | GND (Bank 0)            | -     | GND (Bank 0)      | -         | GND (Bank 0)      | -   |  |

| -      | 0    | VCCO (Bank 0)                | -   | VCCO (Bank 0)           | -     | VCCO (Bank 0)     | -         | VCCO (Bank 0)     | -   |  |

# ispMACH 4256V/B/C, 4384V/B/C, 4512V/B/C Logic Signal Connections: 256-Ball ftBGA/fpBGA (Cont.)

| Ball   | I/O  | ispMACH 4256V/B/C<br>128-I/O |     | ispMACH 4256<br>160-I/O | V/B/C | ispMACH 4384  | V/B/C | ispMACH 4512V/B/C |      |  |

|--------|------|------------------------------|-----|-------------------------|-------|---------------|-------|-------------------|------|--|

| Number | Bank | GLB/MC/Pad                   | ORP | GLB/MC/Pad              | ORP   | GLB/MC/Pad    | ORP   | GLB/MC/Pad        | ORP  |  |

| R5     | 0    | NC                           | -   | NC                      | -     | NC            | -     | L4                | L^1  |  |

| T5     | 0    | NC                           | -   | NC                      | -     | 12            | I^1   | L8                | L^2  |  |

| R6     | 0    | NC                           | -   | NC                      | -     | 10            | I^0   | L12               | L^3  |  |

| T6     | 0    | NC                           | -   | H14                     | H^9   | G12           | G^6   | M8                | M^2  |  |

| N7     | 0    | NC                           | -   | H12                     | H^8   | G14           | G^7   | M12               | M^3  |  |

| P7     | 0    | H14                          | H^7 | H10                     | H^7   | L14           | L^7   | P14               | P^7  |  |

| R7     | 0    | H12                          | H^6 | H9                      | H^6   | L12           | L^6   | P12               | P^6  |  |

| L8     | 0    | H10                          | H^5 | H8                      | H^5   | L10           | L^5   | P10               | P^5  |  |

| T7     | 0    | H8                           | H^4 | H6                      | H^4   | L8            | L^4   | P8                | P^4  |  |

| M8     | 0    | H6                           | H^3 | H4                      | H^3   | L6            | L^3   | P6                | P^3  |  |

| N8     | 0    | H4                           | H^2 | H2                      | H^2   | L4            | L^2   | P4                | P^2  |  |

| R8     | 0    | H2                           | H^1 | H1                      | H^1   | L2            | L^1   | P2                | P^1  |  |

| P8     | 0    | H0                           | H^0 | H0                      | H^0   | L0            | L^0   | P0                | P^0  |  |

| -      | -    | GND                          | -   | GND                     | -     | GND           | -     | GND               | -    |  |

| Т8     | 0    | CLK1/I                       | -   | CLK1/I                  | -     | CLK1/I        | -     | CLK1/I            | -    |  |

| -      | 1    | GND (Bank 1)                 | -   | GND (Bank 1)            | -     | GND (Bank 1)  | -     | GND (Bank 1)      | -    |  |

| N9     | 1    | CLK2/I                       | -   | CLK2/I                  | -     | CLK2/I        | -     | CLK2/I            | -    |  |

| -      | -    | VCC                          | -   | VCC                     | -     | VCC           | -     | VCC               | -    |  |

| P9     | 1    | 10                           | I^0 | 10                      | I^0   | MO            | M^0   | AX0               | AX^0 |  |

| R9     | 1    | 12                           | I^1 | l1                      | I^1   | M2            | M^1   | AX2               | AX^1 |  |

| Т9     | 1    | 14                           | I^2 | 12                      | I^2   | M4            | M^2   | AX4               | AX^2 |  |

| T10    | 1    | 16                           | I^3 | 14                      | I^3   | M6            | M^3   | AX6               | AX^3 |  |

| R10    | 1    | 18                           | I^4 | 16                      | I^4   | M8            | M^4   | AX8               | AX^4 |  |

| M9     | 1    | I10                          | I^5 | 18                      | I^5   | M10           | M^5   | AX10              | AX^5 |  |

| P10    | 1    | l12                          | I^6 | 19                      | I^6   | M12           | M^6   | AX12              | AX^6 |  |

| L9     | 1    | l14                          | I^7 | I10                     | I^7   | M14           | M^7   | AX14              | AX^7 |  |

| N10    | 1    | NC                           | -   | l12                     | I^8   | BX14          | BX^7  | DX0               | DX^0 |  |

| T11    | 1    | NC                           | -   | l14                     | I^9   | BX12          | BX^6  | DX4               | DX^1 |  |

| R11    | 1    | NC                           | ı   | NC                      | •     | P0            | P^0   | EX0               | EX^0 |  |

| T12    | 1    | NC                           | -   | NC                      | -     | P2            | P^1   | EX4               | EX^1 |  |

| N12    | 1    | NC                           | -   | NC                      | -     | NC            | -     | EX8               | EX^2 |  |

| -      | 1    | VCCO (Bank 1)                | ı   | VCCO (Bank 1)           | •     | VCCO (Bank 1) | -     | VCCO (Bank 1)     | -    |  |

| -      | 1    | GND (Bank 1)                 | ı   | GND (Bank 1)            | ı     | GND (Bank 1)  | -     | GND (Bank 1)      | -    |  |

| R12    | 1    | NC                           | ı   | NC                      | -     | NC            | -     | EX12              | EX^3 |  |

| T13    | 1    | NC                           | Ī   | J0                      | J^0   | BX10          | BX^5  | DX8               | DX^2 |  |

| P12    | 1    | NC                           | -   | J1                      | J^1   | BX8           | BX^4  | DX12              | DX^3 |  |

| M10    | 1    | J0                           | J^0 | J2                      | J^2   | N0            | N^0   | BX0               | BX^0 |  |

| R13    | 1    | J2                           | J^1 | J4                      | J^3   | N2            | N^1   | BX2               | BX^1 |  |

| L10    | 1    | J4                           | J^2 | J6                      | J^4   | N4            | N^2   | BX4               | BX^2 |  |

| T14    | 1    | J6                           | J^3 | J8                      | J^5   | N6            | N^3   | BX6               | BX^3 |  |

| M11    | 1    | J8                           | J^4 | J9                      | J^6   | N8            | N^4   | BX8               | BX^4 |  |

## ispMACH 4000B (2.5V) Commercial Devices (Cont.)

| Device  | Part Number                  | Macrocells | Voltage | t <sub>PD</sub> | Package | Pin/Ball Count | I/O | Grade |

|---------|------------------------------|------------|---------|-----------------|---------|----------------|-----|-------|

|         | LC4256B-3FT256AC             | 256        | 2.5     | 3               | ftBGA   | 256            | 128 | С     |

|         | LC4256B-5FT256AC             | 256        | 2.5     | 5               | ftBGA   | 256            | 128 | С     |

|         | LC4256B-75FT256AC            | 256        | 2.5     | 7.5             | ftBGA   | 256            | 128 | С     |

|         | LC4256B-3FT256BC             | 256        | 2.5     | 3               | ftBGA   | 256            | 160 | С     |

|         | LC4256B-5FT256BC             | 256        | 2.5     | 5               | ftBGA   | 256            | 160 | С     |

|         | LC4256B-75FT256BC            | 256        | 2.5     | 7.5             | ftBGA   | 256            | 160 | С     |

|         | LC4256B-3F256AC1             | 256        | 2.5     | 3               | fpBGA   | 256            | 128 | С     |

|         | LC4256B-5F256AC <sup>1</sup> | 256        | 2.5     | 5               | fpBGA   | 256            | 128 | С     |

| LC4256B | LC4256B-75F256AC1            | 256        | 2.5     | 7.5             | fpBGA   | 256            | 128 | С     |

| LC4230B | LC4256B-3F256BC <sup>1</sup> | 256        | 2.5     | 3               | fpBGA   | 256            | 160 | С     |

|         | LC4256B-5F256BC <sup>1</sup> | 256        | 2.5     | 5               | fpBGA   | 256            | 160 | С     |

|         | LC4256B-75F256BC1            | 256        | 2.5     | 7.5             | fpBGA   | 256            | 160 | С     |

|         | LC4256B-3T176C               | 256        | 2.5     | 3               | TQFP    | 176            | 128 | С     |

|         | LC4256B-5T176C               | 256        | 2.5     | 5               | TQFP    | 176            | 128 | С     |

|         | LC4256B-75T176C              | 256        | 2.5     | 7.5             | TQFP    | 176            | 128 | С     |

|         | LC4256B-3T100C               | 256        | 2.5     | 3               | TQFP    | 100            | 64  | С     |

|         | LC4256B-5T100C               | 256        | 2.5     | 5               | TQFP    | 100            | 64  | С     |

|         | LC4256B-75T100C              | 256        | 2.5     | 7.5             | TQFP    | 100            | 64  | С     |

|         | LC4384B-35FT256C             | 384        | 2.5     | 3.5             | ftBGA   | 256            | 192 | С     |

|         | LC4384B-5FT256C              | 384        | 2.5     | 5               | ftBGA   | 256            | 192 | С     |

|         | LC4384B-75FT256C             | 384        | 2.5     | 7.5             | ftBGA   | 256            | 192 | С     |

|         | LC4384B-35F256C1             | 384        | 2.5     | 3.5             | fpBGA   | 256            | 192 | С     |

| LC4384B | LC4384B-5F256C1              | 384        | 2.5     | 5               | fpBGA   | 256            | 192 | С     |

|         | LC4384B-75F256C1             | 384        | 2.5     | 7.5             | fpBGA   | 256            | 192 | С     |

|         | LC4384B-35T176C              | 384        | 2.5     | 3.5             | TQFP    | 176            | 128 | С     |

|         | LC4384B-5T176C               | 384        | 2.5     | 5               | TQFP    | 176            | 128 | С     |

|         | LC4384B-75T176C              | 384        | 2.5     | 7.5             | TQFP    | 176            | 128 | С     |

|         | LC4512B-35FT256C             | 512        | 2.5     | 3.5             | ftBGA   | 256            | 208 | С     |

|         | LC4512B-5FT256C              | 512        | 2.5     | 5               | ftBGA   | 256            | 208 | С     |

|         | LC4512B-75FT256C             | 512        | 2.5     | 7.5             | ftBGA   | 256            | 208 | С     |

|         | LC4512B-35F256C1             | 512        | 2.5     | 3.5             | fpBGA   | 256            | 208 | С     |

| LC4512B | LC4512B-5F256C <sup>1</sup>  | 512        | 2.5     | 5               | fpBGA   | 256            | 208 | С     |

|         | LC4512B-75F256C1             | 512        | 2.5     | 7.5             | fpBGA   | 256            | 208 | С     |

|         | LC4512B-35T176C              | 512        | 2.5     | 3.5             | TQFP    | 176            | 128 | С     |

|         | LC4512B-5T176C               | 512        | 2.5     | 5               | TQFP    | 176            | 128 | С     |

|         | LC4512B-75T176C              | 512        | 2.5     | 7.5             | TQFP    | 176            | 128 | С     |

<sup>1.</sup> Use ftBGA package. fpBGA package devices have been discontinued via PCN#14A-07.

ispMACH 4000B (2.5V) Lead-Free Industrial Devices (Cont.)

|          | <b>-</b>                       |            |         |                 |                 | Pin/Ball |     |       |

|----------|--------------------------------|------------|---------|-----------------|-----------------|----------|-----|-------|

| Device   | Part Number                    | Macrocells | Voltage | t <sub>PD</sub> | Package         | Count    | I/O | Grade |

|          | LC4128B-5TN128I                | 128        | 2.5     | 5               | Lead-Free TQFP  | 128      | 92  | ı     |

|          | LC4128B-75TN128I               | 128        | 2.5     | 7.5             | Lead-Free TQFP  | 128      | 92  | I     |

| LC4128B  | LC4128B-10TN128I               | 128        | 2.5     | 10              | Lead-Free TQFP  | 128      | 92  | I     |

|          | LC4128B-5TN100I                | 128        | 2.5     | 5               | Lead-Free TQFP  | 100      | 64  | I     |

|          | LC4128B-75TN100I               | 128        | 2.5     | 7.5             | Lead-Free TQFP  | 100      | 64  | I     |

|          | LC4128B-10TN100I               | 128        | 2.5     | 10              | Lead-Free TQFP  | 100      | 64  | I     |

|          | LC4256B-5FTN256AI              | 256        | 2.5     | 5               | Lead-Free ftBGA | 256      | 128 | I     |

|          | LC4256B-75FTN256AI             | 256        | 2.5     | 7.5             | Lead-Free ftBGA | 256      | 128 | I     |

|          | LC4256B-10FTN256AI             | 256        | 2.5     | 10              | Lead-Free ftBGA | 256      | 128 | I     |

|          | LC4256B-5FTN256BI              | 256        | 2.5     | 5               | Lead-Free ftBGA | 256      | 160 | 1     |

|          | LC4256B-75FTN256BI             | 256        | 2.5     | 7.5             | Lead-Free ftBGA | 256      | 160 | I     |

|          | LC4256B-10FTN256BI             | 256        | 2.5     | 10              | Lead-Free ftBGA | 256      | 160 | I     |

|          | LC4256B-5FN256AI <sup>1</sup>  | 256        | 2.5     | 5               | Lead-Free fpBGA | 256      | 128 | I     |

|          | LC4256B-75FN256AI <sup>1</sup> | 256        | 2.5     | 7.5             | Lead-Free fpBGA | 256      | 128 | I     |

| L CAOSED | LC4256B-10FN256AI <sup>1</sup> | 256        | 2.5     | 10              | Lead-Free fpBGA | 256      | 128 | I     |

| LC4256B  | LC4256B-5FN256BI <sup>1</sup>  | 256        | 2.5     | 5               | Lead-Free fpBGA | 256      | 160 | I     |

|          | LC4256B-75FN256BI <sup>1</sup> | 256        | 2.5     | 7.5             | Lead-Free fpBGA | 256      | 160 | I     |

|          | LC4256B-10FN256BI <sup>1</sup> | 256        | 2.5     | 10              | Lead-Free fpBGA | 256      | 160 | I     |

|          | LC4256B-5TN176I                | 256        | 2.5     | 5               | Lead-Free TQFP  | 176      | 128 | I     |

|          | LC4256B-75TN176I               | 256        | 2.5     | 7.5             | Lead-Free TQFP  | 176      | 128 | I     |

|          | LC4256B-10TN176I               | 256        | 2.5     | 10              | Lead-Free TQFP  | 176      | 128 | I     |

|          | LC4256B-5TN100I                | 256        | 2.5     | 5               | Lead-Free TQFP  | 100      | 64  | I     |

|          | LC4256B-75TN100I               | 256        | 2.5     | 7.5             | Lead-Free TQFP  | 100      | 64  | I     |

|          | LC4256B-10TN100I               | 256        | 2.5     | 10              | Lead-Free TQFP  | 100      | 64  | I     |

|          | LC4384B-5FTN256I               | 384        | 2.5     | 5               | Lead-Free ftBGA | 256      | 192 | I     |

|          | LC4384B-75FTN256I              | 384        | 2.5     | 7.5             | Lead-Free ftBGA | 256      | 192 | I     |

|          | LC4384B-10FTN256I              | 384        | 2.5     | 10              | Lead-Free ftBGA | 256      | 192 | I     |

|          | LC4384B-5FN256I <sup>1</sup>   | 384        | 2.5     | 5               | Lead-Free fpBGA | 256      | 192 | I     |

| LC4384B  | LC4384B-75FN256I <sup>1</sup>  | 384        | 2.5     | 7.5             | Lead-Free fpBGA | 256      | 192 | I     |

|          | LC4384B-10FN256I <sup>1</sup>  | 384        | 2.5     | 10              | Lead-Free fpBGA | 256      | 192 | I     |

|          | LC4384B-5TN176I                | 384        | 2.5     | 5               | Lead-Free TQFP  | 176      | 128 | I     |

|          | LC4384B-75TN176I               | 384        | 2.5     | 7.5             | Lead-Free TQFP  | 176      | 128 | I     |

|          | LC4384B-10TN176I               | 384        | 2.5     | 10              | Lead-Free TQFP  | 176      | 128 | I     |

|          | LC4512B-5FTN256I               | 512        | 2.5     | 5               | Lead-Free ftBGA | 256      | 208 | I     |

|          | LC4512B-75FTN256I              | 512        | 2.5     | 7.5             | Lead-Free ftBGA | 256      | 208 | I     |

|          | LC4512B-10FTN256I              | 512        | 2.5     | 10              | Lead-Free ftBGA | 256      | 208 | I     |

|          | LC4512B-5FN256I <sup>1</sup>   | 512        | 2.5     | 5               | Lead-Free fpBGA | 256      | 208 | I     |

| LC4512B  | LC4512B-75FN256I <sup>1</sup>  | 512        | 2.5     | 7.5             | Lead-Free fpBGA | 256      | 208 | I     |

|          | LC4512B-10FN256I <sup>1</sup>  | 512        | 2.5     | 10              | Lead-Free fpBGA | 256      | 208 | I     |

|          | LC4512B-5TN176I                | 512        | 2.5     | 5               | Lead-Free TQFP  | 176      | 128 | I     |

|          | LC4512B-75TN176I               | 512        | 2.5     | 7.5             | Lead-Free TQFP  | 176      | 128 | I     |

|          | LC4512B-10TN176I               | 512        | 2.5     | 10              | Lead-Free TQFP  | 176      | 128 | ı     |

<sup>1.</sup> Use ftBGA package. fpBGA package devices have been discontinued via PCN#14A-07.

## ispMACH 4000V (3.3V) Lead-Free Industrial Devices

| Device  | Part Number      | Macrocells | Voltage | t <sub>PD</sub> | Package        | Pin/Ball<br>Count | I/O | Grade |

|---------|------------------|------------|---------|-----------------|----------------|-------------------|-----|-------|

|         | LC4032V-5TN48I   | 32         | 3.3     | 5               | Lead-free TQFP | 48                | 32  | I     |

|         | LC4032V-75TN48I  | 32         | 3.3     | 7.5             | Lead-free TQFP | 48                | 32  | I     |

| LC4032V | LC4032V-10TN48I  | 32         | 3.3     | 10              | Lead-free TQFP | 48                | 32  | I     |

| LC4032V | LC4032V-5TN44I   | 32         | 3.3     | 5               | Lead-free TQFP | 44                | 30  | I     |

|         | LC4032V-75TN44I  | 32         | 3.3     | 7.5             | Lead-free TQFP | 44                | 30  | I     |

|         | LC4032V-10TN44I  | 32         | 3.3     | 10              | Lead-free TQFP | 44                | 30  | I     |

|         | LC4064V-5TN100I  | 64         | 3.3     | 5               | Lead-free TQFP | 100               | 64  | I     |

|         | LC4064V-75TN100I | 64         | 3.3     | 7.5             | Lead-free TQFP | 100               | 64  | I     |

|         | LC4064V-10TN100I | 64         | 3.3     | 10              | Lead-free TQFP | 100               | 64  | I     |

|         | LC4064V-5TN48I   | 64         | 3.3     | 5               | Lead-free TQFP | 48                | 32  | I     |

| LC4064V | LC4064V-75TN48I  | 64         | 3.3     | 7.5             | Lead-free TQFP | 48                | 32  | I     |

|         | LC4064V-10TN48I  | 64         | 3.3     | 10              | Lead-free TQFP | 48                | 32  | I     |

|         | LC4064V-5TN44I   | 64         | 3.3     | 5               | Lead-free TQFP | 44                | 30  | I     |

|         | LC4064V-75TN44I  | 64         | 3.3     | 7.5             | Lead-free TQFP | 44                | 30  | I     |

|         | LC4064V-10TN44I  | 64         | 3.3     | 10              | Lead-free TQFP | 44                | 30  | I     |

|         | LC4128V-5TN144I  | 128        | 3.3     | 5               | Lead-free TQFP | 144               | 96  | I     |

|         | LC4128V-75TN144I | 128        | 3.3     | 7.5             | Lead-free TQFP | 144               | 96  | I     |

|         | LC4128V-10TN144I | 128        | 3.3     | 10              | Lead-free TQFP | 144               | 96  | I     |

|         | LC4128V-5TN128I  | 128        | 3.3     | 5               | Lead-free TQFP | 128               | 92  | I     |

| LC4128V | LC4128V-75TN128I | 128        | 3.3     | 7.5             | Lead-free TQFP | 128               | 92  | I     |

|         | LC4128V-10TN128I | 128        | 3.3     | 10              | Lead-free TQFP | 128               | 92  | I     |

|         | LC4128V-5TN100I  | 128        | 3.3     | 5               | Lead-free TQFP | 100               | 64  | I     |

|         | LC4128V-75TN100I | 128        | 3.3     | 7.5             | Lead-free TQFP | 100               | 64  | I     |

|         | LC4128V-10TN100I | 128        | 3.3     | 10              | Lead-free TQFP | 100               | 64  | I     |