Welcome to **E-XFL.COM**

**Understanding Embedded - CPLDs (Complex Programmable Logic Devices)**

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixed-function ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

| Details                         |                                                                             |

|---------------------------------|-----------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                                    |

| Programmable Type               | In System Programmable                                                      |

| Delay Time tpd(1) Max           | 7.5 ns                                                                      |

| Voltage Supply - Internal       | 1.7V ~ 1.9V                                                                 |

| Number of Logic Elements/Blocks | 16                                                                          |

| Number of Macrocells            | 256                                                                         |

| Number of Gates                 |                                                                             |

| Number of I/O                   | 128                                                                         |

| Operating Temperature           | 0°C ~ 90°C (TJ)                                                             |

| Mounting Type                   | Surface Mount                                                               |

| Package / Case                  | 176-LQFP                                                                    |

| Supplier Device Package         | 176-TQFP (24x24)                                                            |

| Purchase URL                    | https://www.e-xfl.com/product-detail/lattice-semiconductor/lc4256zc-75t176c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

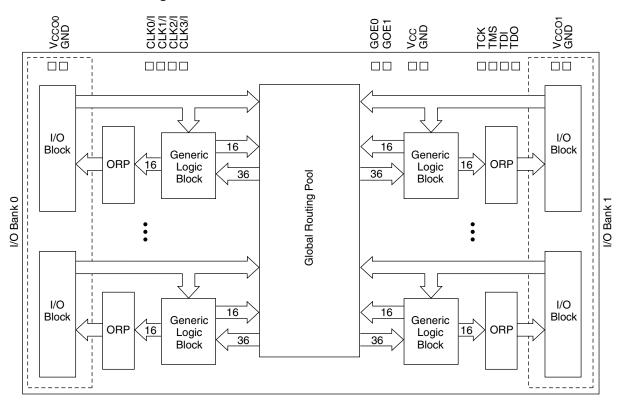

Figure 1. Functional Block Diagram

The I/Os in the ispMACH 4000 are split into two banks. Each bank has a separate I/O power supply. Inputs can support a variety of standards independent of the chip or bank power supply. Outputs support the standards compatible with the power supply provided to the bank. Support for a variety of standards helps designers implement designs in mixed voltage environments. In addition, 5V tolerant inputs are specified within an I/O bank that is connected to  $V_{CCO}$  of 3.0V to 3.6V for LVCMOS 3.3, LVTTL and PCI interfaces.

### ispMACH 4000 Architecture

There are a total of two GLBs in the ispMACH 4032, increasing to 32 GLBs in the ispMACH 4512. Each GLB has 36 inputs. All GLB inputs come from the GRP and all outputs from the GLB are brought back into the GRP to be connected to the inputs of any other GLB on the device. Even if feedback signals return to the same GLB, they still must go through the GRP. This mechanism ensures that GLBs communicate with each other with consistent and predictable delays. The outputs from the GLB are also sent to the ORP. The ORP then sends them to the associated I/O cells in the I/O block.

#### Generic Logic Block

The ispMACH 4000 GLB consists of a programmable AND array, logic allocator, 16 macrocells and a GLB clock generator. Macrocells are decoupled from the product terms through the logic allocator and the I/O pins are decoupled from macrocells through the ORP. Figure 2 illustrates the GLB.

Table 5. Product Term Expansion Capability

| Expansion<br>Chains | Macrocells Associated with Expansion Chain (with Wrap Around) | Max PT/<br>Macrocell |

|---------------------|---------------------------------------------------------------|----------------------|

| Chain-0             | M0 M4 M8 M12 M0                                               | 75                   |

| Chain-1             | M1 M5 M9 M13 M1                                               | 80                   |

| Chain-2             | M2 M6 M10 M14 M2                                              | 75                   |

| Chain-3             | M3 M7 M11 M15 M3                                              | 70                   |

Every time the super cluster allocator is used, there is an incremental delay of t<sub>EXP</sub>. When the super cluster allocator is used, all destinations other than the one being steered to, are given the value of ground (i.e., if the super cluster is steered to M (n+4), then M (n) is ground).

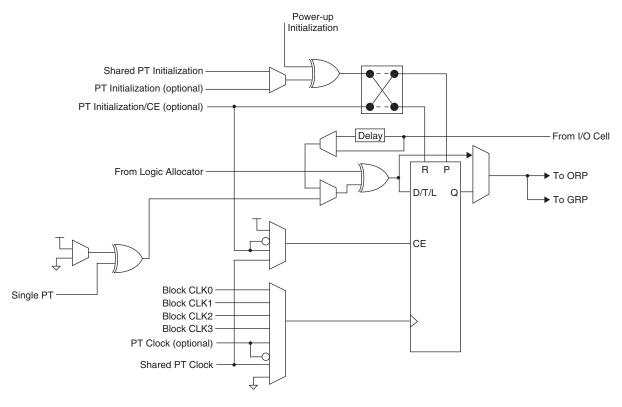

#### Macrocell

The 16 macrocells in the GLB are driven by the 16 outputs from the logic allocator. Each macrocell contains a programmable XOR gate, a programmable register/latch, along with routing for the logic and control functions. Figure 5 shows a graphical representation of the macrocell. The macrocells feed the ORP and GRP. A direct input from the I/O cell allows designers to use the macrocell to construct high-speed input registers. A programmable delay in this path allows designers to choose between the fastest possible set-up time and zero hold time.

Figure 5. Macrocell

#### **Enhanced Clock Multiplexer**

The clock input to the flip-flop can select any of the four block clocks along with the shared PT clock, and true and complement forms of the optional individual term clock. An 8:1 multiplexer structure is used to select the clock. The eight sources for the clock multiplexer are as follows:

- Block CLK0

- Block CLK1

- Block CLK2

- Block CLK3

- PT Clock

- PT Clock Inverted

- Shared PT Clock

- Ground

#### **Clock Enable Multiplexer**

Each macrocell has a 4:1 clock enable multiplexer. This allows the clock enable signal to be selected from the following four sources:

- PT Initialization/CE

- PT Initialization/CE Inverted

- Shared PT Clock

- Logic High

#### **Initialization Control**

The ispMACH 4000 family architecture accommodates both block-level and macrocell-level set and reset capability. There is one block-level initialization term that is distributed to all macrocell registers in a GLB. At the macrocell level, two product terms can be "stolen" from the cluster associated with a macrocell to be used for set/reset functionality. A reset/preset swapping feature in each macrocell allows for reset and preset to be exchanged, providing flexibility.

Note that the reset/preset swapping selection feature affects power-up reset as well. All flip-flops power up to a known state for predictable system initialization. If a macrocell is configured to SET on a signal from the block-level initialization, then that macrocell will be SET during device power-up. If a macrocell is configured to RESET on a signal from the block-level initialization or is not configured for set/reset, then that macrocell will RESET on power-up. To guarantee initialization values, the  $V_{CC}$  rise must be monotonic, and the clock must be inactive until the reset delay time has elapsed.

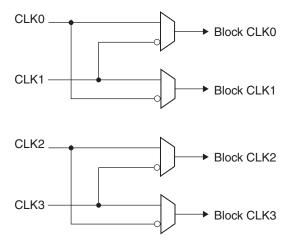

#### **GLB Clock Generator**

Each ispMACH 4000 device has up to four clock pins that are also routed to the GRP to be used as inputs. These pins drive a clock generator in each GLB, as shown in Figure 6. The clock generator provides four clock signals that can be used anywhere in the GLB. These four GLB clock signals can consist of a number of combinations of the true and complement edges of the global clock signals.

Figure 6. GLB Clock Generator

Table 10. ORP Combinations for I/O Blocks with 12 I/Os

| I/O Cell | Available Macrocells                 |

|----------|--------------------------------------|

| I/O 0    | M0, M1, M2, M3, M4, M5, M6, M7       |

| I/O 1    | M1, M2, M3, M4, M5, M6, M7, M8       |

| I/O 2    | M2, M3, M4, M5, M6, M7, M8, M9       |

| I/O 3    | M4, M5, M6, M7, M8, M9, M10, M11     |

| I/O 4    | M5, M6, M7, M8, M9, M10, M11, M12    |

| I/O 5    | M6, M7, M8, M9, M10, M11, M12, M13   |

| I/O 6    | M8, M9, M10, M11, M12, M13, M14, M15 |

| I/O 7    | M9, M10, M11, M12, M13, M14, M15, M0 |

| I/O 8    | M10, M11, M12, M13, M14, M15, M0, M1 |

| I/O 9    | M12, M13, M14, M15, M0, M1, M2, M3   |

| I/O 10   | M13, M14, M15, M0, M1, M2, M3, M4    |

| I/O 11   | M14, M15, M0, M1, M2, M3, M4, M5     |

#### **ORP Bypass and Fast Output Multiplexers**

The ORP bypass and fast-path output multiplexer is a 4:1 multiplexer and allows the 5-PT fast path to bypass the ORP and be connected directly to the pin with either the regular output or the inverted output. This multiplexer also allows the register output to bypass the ORP to achieve faster t<sub>CO</sub>.

#### **Output Enable Routing Multiplexers**

The OE Routing Pool provides the corresponding local output enable (OE) product term to the I/O cell.

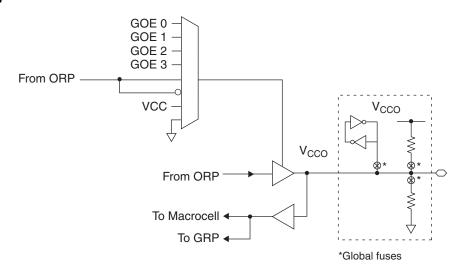

#### I/O Cell

The I/O cell contains the following programmable elements: output buffer, input buffer, OE multiplexer and bus maintenance circuitry. Figure 8 details the I/O cell.

Figure 8. I/O Cell

Each output supports a variety of output standards dependent on the  $V_{CCO}$  supplied to its I/O bank. Outputs can also be configured for open drain operation. Each input can be programmed to support a variety of standards, independent of the  $V_{CCO}$  supplied to its I/O bank. The I/O standards supported are:

#### **IEEE 1532-Compliant In-System Programming**

Programming devices in-system provides a number of significant benefits including: rapid prototyping, lower inventory levels, higher quality and the ability to make in-field modifications. All ispMACH 4000 devices provide In-System Programming (ISP™) capability through the Boundary Scan Test Access Port. This capability has been implemented in a manner that ensures that the port remains complaint to the IEEE 1149.1 standard. By using IEEE 1149.1 as the communication interface through which ISP is achieved, users get the benefit of a standard, well-defined interface. All ispMACH 4000 devices are also compliant with the IEEE 1532 standard.

The ispMACH 4000 devices can be programmed across the commercial temperature and voltage range. The PC-based Lattice software facilitates in-system programming of ispMACH 4000 devices. The software takes the JEDEC file output produced by the design implementation software, along with information about the scan chain, and creates a set of vectors used to drive the scan chain. The software can use these vectors to drive a scan chain via the parallel port of a PC. Alternatively, the software can output files in formats understood by common automated test equipment. This equipment can then be used to program ispMACH 4000 devices during the testing of a circuit board.

#### **User Electronic Signature**

The User Electronic Signature (UES) allows the designer to include identification bits or serial numbers inside the device, stored in E<sup>2</sup>CMOS memory. The ispMACH 4000 device contains 32 UES bits that can be configured by the user to store unique data such as ID codes, revision numbers or inventory control codes.

#### **Security Bit**

A programmable security bit is provided on the ispMACH 4000 devices as a deterrent to unauthorized copying of the array configuration patterns. Once programmed, this bit defeats readback of the programmed pattern by a device programmer, securing proprietary designs from competitors. Programming and verification are also defeated by the security bit. The bit can only be reset by erasing the entire device.

#### **Hot Socketing**

The ispMACH 4000 devices are well-suited for applications that require hot socketing capability. Hot socketing a device requires that the device, during power-up and down, can tolerate active signals on the I/Os and inputs without being damaged. Additionally, it requires that the effects of I/O pin loading be minimal on active signals. The isp-MACH 4000 devices provide this capability for input voltages in the range 0V to 3.0V.

### **Density Migration**

The ispMACH 4000 family has been designed to ensure that different density devices in the same package have the same pin-out. Furthermore, the architecture ensures a high success rate when performing design migration from lower density parts to higher density parts. In many cases, it is possible to shift a lower utilization design targeted for a high density device to a lower density device. However, the exact details of the final resource utilization will impact the likely success in each case.

#### I/O DC Electrical Characteristics

#### **Over Recommended Operating Conditions**

|                   |         | V <sub>IL</sub>                     | V <sub>IH</sub>                     |         | V <sub>OL</sub>      | V <sub>OH</sub>         | l <sub>OL</sub> <sup>1</sup> | I <sub>OH</sub> <sup>1</sup> |

|-------------------|---------|-------------------------------------|-------------------------------------|---------|----------------------|-------------------------|------------------------------|------------------------------|

| Standard          | Min (V) | Max (V)                             | Min (V)                             | Max (V) | Max (V)              | Min (V)                 | (mA)                         | (mA)                         |

| LVTTL             | -0.3    | 0.80                                | 2.0                                 | 5.5     | 0.40                 | V <sub>CCO</sub> - 0.40 | 8.0                          | -4.0                         |

| LVIIL             | -0.5    | 0.00                                | 2.0 0.0                             |         | 0.20                 | V <sub>CCO</sub> - 0.20 | 0.1                          | -0.1                         |

| LVCMOS 3.3        | -0.3    | 0.80                                | 2.0                                 | 2.0 5.5 |                      | V <sub>CCO</sub> - 0.40 | 8.0                          | -4.0                         |

| LV CIVICS 3.3     | -0.5    | 0.00                                | 2.0                                 |         |                      | V <sub>CCO</sub> - 0.20 | 0.1                          | -0.1                         |

| LVCMOS 2.5        | -0.3    | 0.70                                | 1.70 3.6                            | 3.6     | 0.40                 | V <sub>CCO</sub> - 0.40 | 8.0                          | -4.0                         |

| LVCIVIOS 2.5      | -0.3    | 0.70                                | 1.70                                | 3.0     | 0.20                 | V <sub>CCO</sub> - 0.20 | 0.1                          | -0.1                         |

| LVCMOS 1.8        | -0.3    | 0.63                                | 1.17                                | 3.6     | 0.40                 | V <sub>CCO</sub> - 0.45 | 2.0                          | -2.0                         |

| (4000V/B)         | -0.3    | 0.03                                | 1.17                                | 3.0     | 0.20                 | V <sub>CCO</sub> - 0.20 | 0.1                          | -0.1                         |

| LVCMOS 1.8        | -0.3    | 0.35 * V <sub>CC</sub>              | 0.65 * V <sub>CC</sub>              | 3.6     | 0.40                 | V <sub>CCO</sub> - 0.45 | 2.0                          | -2.0                         |

| (4000C/Z)         | -0.5    | 0.55 V <sub>CC</sub>                | 0.03 VCC                            | 5.0     | 0.20                 | V <sub>CCO</sub> - 0.20 | 0.1                          | -0.1                         |

| PCI 3.3 (4000V/B) | -0.3    | 1.08                                | 1.5                                 | 5.5     | 0.1 V <sub>CCO</sub> | 0.9 V <sub>CCO</sub>    | 1.5                          | -0.5                         |

| PCI 3.3 (4000C/Z) | -0.3    | 0.3 * 3.3 * (V <sub>CC</sub> / 1.8) | 0.5 * 3.3 * (V <sub>CC</sub> / 1.8) | 5.5     | 0.1 V <sub>CCO</sub> | 0.9 V <sub>CCO</sub>    | 1.5                          | -0.5                         |

<sup>1.</sup> The average DC current drawn by I/Os between adjacent bank GND connections, or between the last GND in an I/O bank and the end of the I/O bank, as shown in the logic signals connection table, shall not exceed *n*\*8mA. Where *n* is the number of I/Os between bank GND connections or between the last GND in a bank and the end of a bank.

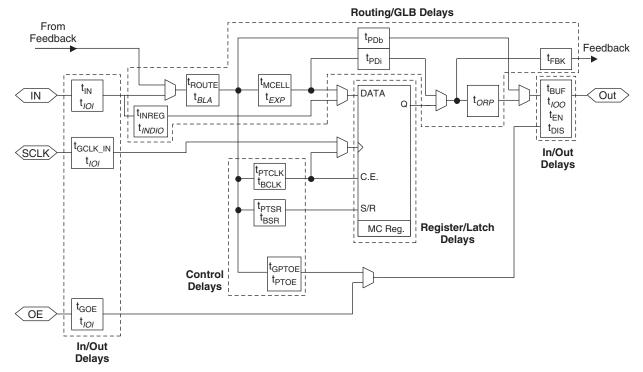

#### **Timing Model**

The task of determining the timing through the ispMACH 4000 family, like any CPLD, is relatively simple. The timing model provided in Figure 11 shows the specific delay paths. Once the implementation of a given function is determined either conceptually or from the software report file, the delay path of the function can easily be determined from the timing model. The Lattice design tools report the timing delays based on the same timing model for a particular design. Note that the internal timing parameters are given for reference only, and are not tested. The external timing parameters are tested and guaranteed for every device. For more information on the timing model and usage, refer to TN1004, ispMACH 4000 Timing Model Design and Usage Guidelines.

Figure 11. ispMACH 4000 Timing Model

Note: Italicized items are optional delay adders.

## ispMACH 4000V/B/C Internal Timing Parameters (Cont.)

#### **Over Recommended Operating Conditions**

| Parameter          | Description                                                               | -2   | 5    | -2   | 7    | -    | 3    | -3.5 |      | Units |

|--------------------|---------------------------------------------------------------------------|------|------|------|------|------|------|------|------|-------|

| t <sub>PDLi</sub>  | Propagation Delay through<br>Transparent Latch to Output/<br>Feedback MUX | _    | 0.25 | _    | 0.25 | _    | 0.25 | _    | 0.25 | ns    |

| t <sub>SRi</sub>   | Asynchronous Reset or Set to Output/Feedback MUX Delay                    | 0.28 | _    | 0.28 | _    | 0.28 | _    | 0.28 |      | ns    |

| t <sub>SRR</sub>   | Asynchronous Reset or Set<br>Recovery Time                                | 1.67 | _    | 1.67 | _    | 1.67 | _    | 1.67 | _    | ns    |

| Control Delay      | ys                                                                        |      |      |      |      |      |      |      |      |       |

| t <sub>BCLK</sub>  | GLB PT Clock Delay                                                        | _    | 1.12 |      | 1.12 |      | 1.12 |      | 1.12 | ns    |

| t <sub>PTCLK</sub> | Macrocell PT Clock Delay                                                  | _    | 0.87 | _    | 0.87 | _    | 0.87 | _    | 0.87 | ns    |

| t <sub>BSR</sub>   | Block PT Set/Reset Delay                                                  | _    | 1.83 | _    | 1.83 | _    | 1.83 | _    | 1.83 | ns    |

| t <sub>PTSR</sub>  | Macrocell PT Set/Reset Delay                                              | _    | 1.11 |      | 1.41 | —    | 1.51 | —    | 1.61 | ns    |

| t <sub>GPTOE</sub> | Global PT OE Delay                                                        | _    | 2.83 |      | 4.13 | —    | 5.33 | _    | 5.33 | ns    |

| t <sub>PTOE</sub>  | Macrocell PT OE Delay                                                     | _    | 1.83 | _    | 2.13 | _    | 2.33 | _    | 2.83 | ns    |

Timing v.3.2

Note: Internal Timing Parameters are not tested and are for reference only. Refer to the Timing Model in this data sheet for further details.

## ispMACH 4000Z Timing Adders (Cont.)<sup>1</sup>

| Adder                         | Base                                                      |                                            | -4   | <b>1</b> 5 | -    | 5    | -75  |      |       |

|-------------------------------|-----------------------------------------------------------|--------------------------------------------|------|------------|------|------|------|------|-------|

| Туре                          | Parameter                                                 | Description                                | Min. | Max.       | Min. | Max. | Min. | Max. | Units |

| Optional Delay A              | Adders                                                    |                                            |      |            | I.   |      |      | •    | I.    |

| t <sub>INDIO</sub>            | t <sub>INREG</sub>                                        | Input register delay                       | _    | 1.30       | _    | 1.30 | _    | 1.30 | ns    |

| t <sub>EXP</sub>              | t <sub>MCELL</sub>                                        | Product term expander delay                | _    | 0.45       | _    | 0.45 | _    | 0.50 | ns    |

| t <sub>ORP</sub>              | _                                                         | Output routing pool delay                  | _    | 0.40       | _    | 0.40 | _    | 0.40 | ns    |

| t <sub>BLA</sub>              | t <sub>ROUTE</sub>                                        | Additional block load-<br>ing adder        | _    | 0.05       | _    | 0.05 | _    | 0.05 | ns    |

| t <sub>IOI</sub> Input Adjust | ers                                                       |                                            |      |            | I.   |      |      | •    | I.    |

| LVTTL_in                      | t <sub>IN</sub> , t <sub>GCLK_IN</sub> , t <sub>GOE</sub> | Using LVTTL standard                       | _    | 0.60       | _    | 0.60 | _    | 0.60 | ns    |

| LVCMOS33_in                   | t <sub>IN,</sub> t <sub>GCLK_IN</sub> , t <sub>GOE</sub>  | Using LVCMOS 3.3 standard                  | _    | 0.60       | _    | 0.60 | _    | 0.60 | ns    |

| LVCMOS25_in                   | t <sub>IN,</sub> t <sub>GCLK_IN</sub> , t <sub>GOE</sub>  | Using LVCMOS 2.5 standard                  | _    | 0.60       | _    | 0.60 | _    | 0.60 | ns    |

| LVCMOS18_in                   | t <sub>IN,</sub> t <sub>GCLK_IN</sub> , t <sub>GOE</sub>  | Using LVCMOS 1.8 standard                  | _    | 0.00       | _    | 0.00 | _    | 0.00 | ns    |

| PCI_in                        | t <sub>IN,</sub> t <sub>GCLK_IN</sub> , t <sub>GOE</sub>  | Using PCI compatible input                 | _    | 0.60       | _    | 0.60 | _    | 0.60 | ns    |

| t <sub>IOO</sub> Output Adju  | ısters                                                    |                                            |      |            |      | •    |      | •    |       |

| LVTTL_out                     | t <sub>BUF,</sub> t <sub>EN,</sub> t <sub>DIS</sub>       | Output configured as TTL buffer            | _    | 0.20       | _    | 0.20 | _    | 0.20 | ns    |

| LVCMOS33_out                  | t <sub>BUF,</sub> t <sub>EN,</sub> t <sub>DIS</sub>       | Output configured as 3.3V buffer           | _    | 0.20       | _    | 0.20 | _    | 0.20 | ns    |

| LVCMOS25_out                  | t <sub>BUF,</sub> t <sub>EN,</sub> t <sub>DIS</sub>       | Output configured as 2.5V buffer           | _    | 0.10       | _    | 0.10 | _    | 0.10 | ns    |

| LVCMOS18_out                  | t <sub>BUF,</sub> t <sub>EN,</sub> t <sub>DIS</sub>       | Output configured as 1.8V buffer           | _    | 0.00       | _    | 0.00 | _    | 0.00 | ns    |

| PCI_out                       | t <sub>BUF,</sub> t <sub>EN,</sub> t <sub>DIS</sub>       | Output configured as PCI compatible buffer | _    | 0.20       | _    | 0.20 | _    | 0.20 | ns    |

| Slow Slew                     | t <sub>BUF,</sub> t <sub>EN</sub>                         | Output configured for slow slew rate       | _    | 1.00       | _    | 1.00 | _    | 1.00 | ns    |

Timing v.2.2

Note: Open drain timing is the same as corresponding LVCMOS timing.

1. Refer to TN1004, <u>ispMACH 4000 Timing Model Design and Usage Guidelines</u> for information regarding use of these adders.

### **Signal Descriptions**

| Signal Names                          | Desc                                                                                            | ription                                                                                   |  |  |  |  |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|--|--|--|--|

| TMS                                   | Input – This pin is the IEEE 1149.1 Test Notes that the state machine.                          | Mode Select input, which is used to control                                               |  |  |  |  |  |

| TCK                                   | Input – This pin is the IEEE 1149.1 Test 0 state machine.                                       | Clock input pin, used to clock through the                                                |  |  |  |  |  |

| TDI                                   | Input – This pin is the IEEE 1149.1 Test D                                                      | Data In pin, used to load data.                                                           |  |  |  |  |  |

| TDO                                   | Output – This pin is the IEEE 1149.1 Test                                                       | Data Out pin used to shift data out.                                                      |  |  |  |  |  |

| GOE0/IO, GOE1/IO                      | These pins are configured to be either Gl pins.                                                 | These pins are configured to be either Global Output Enable Input or as general I/O pins. |  |  |  |  |  |

| GND                                   | Ground                                                                                          | Ground                                                                                    |  |  |  |  |  |

| NC                                    | Not Connected                                                                                   | Not Connected                                                                             |  |  |  |  |  |

| V <sub>CC</sub>                       | The power supply pins for logic core and                                                        | The power supply pins for logic core and JTAG port.                                       |  |  |  |  |  |

| CLK0/I, CLK1/I, CLK2/I, CLK3/I        | These pins are configured to be either CL                                                       | ₋K input or as an input.                                                                  |  |  |  |  |  |

| V <sub>CCO0</sub> , V <sub>CCO1</sub> | The power supply pins for each I/O bank.                                                        |                                                                                           |  |  |  |  |  |

|                                       | Input/Output <sup>1</sup> – These are the general pu reference (alpha) and z is macrocell refer | rpose I/O used by the logic array. y is GLB ence (numeric). z: 0-15.                      |  |  |  |  |  |

|                                       | ispMACH 4032                                                                                    | y: A-B                                                                                    |  |  |  |  |  |

|                                       | ispMACH 4064                                                                                    | y: A-D                                                                                    |  |  |  |  |  |

| yzz                                   | ispMACH 4128                                                                                    | y: A-H                                                                                    |  |  |  |  |  |

|                                       | ispMACH 4256                                                                                    | y: A-P                                                                                    |  |  |  |  |  |

|                                       | ispMACH 4384                                                                                    | y: A-P, AX-HX                                                                             |  |  |  |  |  |

|                                       | ispMACH 4512                                                                                    | y: A-P, AX-PX                                                                             |  |  |  |  |  |

<sup>1.</sup> In some packages, certain I/Os are only available for use as inputs. See the signal connections table for details.

### ispMACH 4000V/B/C ORP Reference Table

|                         | 4032        | V/B/C      | 4               | 1064\ | //B/C            | 4128            | V/B/        | 0  |                 | 4256            | V/B/C           |                  | 4384\       | //B/C | 4512           | 2V/B/C                             |

|-------------------------|-------------|------------|-----------------|-------|------------------|-----------------|-------------|----|-----------------|-----------------|-----------------|------------------|-------------|-------|----------------|------------------------------------|

| Number of I/Os          | 30¹         | 32         | 30 <sup>2</sup> | 32    | 64               | 64              | 92³         | 96 | 64              | 96 <sup>4</sup> | 128             | 160              | 128         | 192   | 128            | 208                                |

| Number of GLBs          | 2           | 2          | 4               | 4     | 4                | 8               | 8           | 8  | 16              | 16              | 16              | 16               | 16          | 16    | 16             | 16                                 |

| Number of I/Os /<br>GLB | 16          | 16         | 8               | 8     | 16               | 8               | 12          | 12 | 4               | 8               | 8               | 10               | 8           | 8     | 8              | Mixture of 8 & 4 <sup>5</sup>      |

| Reference ORP<br>Table  | 16 l/<br>Gl | Os /<br>LB | 8 I/0<br>GI     |       | 16 I/Os /<br>GLB | 8 I/Os /<br>GLB | 12 l/<br>GI |    | 4 I/Os /<br>GLB | 8 I/Os /<br>GLB | 8 I/Os /<br>GLB | 10 I/Os /<br>GLB | 8 I/0<br>GL |       | 8 I/Os/<br>GLB | 8 I/Os /<br>GLB<br>4 I/Os /<br>GLB |

- 1. 32-macrocell device, 44 TQFP: 2 GLBs have 15 out of 16 I/Os bonded out.

- 2. 64-macrocells device, 44 TQFP: 2 GLBs have 7 out of 8 I/Os bonded out.

- 3. 128-macrocell device, 128 TQFP: 4 GLBs have 11 out of 12 I/Os

- 4. 256-macrocell device, 144 TQFP: 16 GLBs have 6 I/Os per

- 5. 512-macrocell device: 20 GLBs have 8 I/Os per, 12 GLBs have 4 I/Os per

## ispMACH 4000Z ORP Reference Table

|                      | 4032Z            | 406             | 64Z              | 412             | 28Z              | 4256Z           |                 |                 |

|----------------------|------------------|-----------------|------------------|-----------------|------------------|-----------------|-----------------|-----------------|

| Number of I/Os       | 32               | 32              | 64               | 64              | 96               | 64              | 96¹             | 128             |

| Number of GLBs       | 2                | 4               | 4                | 8               | 8                | 16              | 16              | 16              |

| Number of I/Os / GLB | 16               | 8               | 16               | 8               | 12               | 4               | 8               | 8               |

| Reference ORP Table  | 16 I/Os /<br>GLB | 8 I/Os /<br>GLB | 16 I/Os /<br>GLB | 8 I/Os /<br>GLB | 12 I/Os /<br>GLB | 4 I/Os /<br>GLB | 8 I/Os /<br>GLB | 8 I/Os /<br>GLB |

<sup>1. 256-</sup>macrocell device, 132 csBGA: 16 GLBs have 6 I/Os per

# ispMACH 4032V/B/C and 4064V/B/C Logic Signal Connections: 44-Pin TQFP

|            |             | ispMACH 40    | 032V/B/C | ispMACH 40    | 64V/B/C |

|------------|-------------|---------------|----------|---------------|---------|

| Pin Number | Bank Number | GLB/MC/Pad    | ORP      | GLB/MC/Pad    | ORP     |

| 1          | -           | TDI           | -        | TDI           | -       |

| 2          | 0           | A5            | A^5      | A10           | A^5     |

| 3          | 0           | A6            | A^6      | A12           | A^6     |

| 4          | 0           | A7            | A^7      | A14           | A^7     |

| 5          | 0           | GND (Bank 0)  | -        | GND (Bank 0)  | -       |

| 6          | 0           | VCCO (Bank 0) | -        | VCCO (Bank 0) | -       |

| 7          | 0           | A8            | A^8      | B0            | B^0     |

| 8          | 0           | A9            | A^9      | B2            | B^1     |

| 9          | 0           | A10           | A^10     | B4            | B^2     |

| 10         | -           | TCK           | -        | TCK           | -       |

| 11         | -           | VCC           | -        | VCC           | -       |

| 12         | -           | GND           | -        | GND           | -       |

| 13         | 0           | A12           | A^12     | B8            | B^4     |

| 14         | 0           | A13           | A^13     | B10           | B^5     |

| 15         | 0           | A14           | A^14     | B12           | B^6     |

| 16         | 0           | A15           | A^15     | B14           | B^7     |

| 17         | 1           | CLK2/I        | -        | CLK2/I        | -       |

| 18         | 1           | B0            | B^0      | C0            | C^0     |

| 19         | 1           | B1            | B^1      | C2            | C^1     |

| 20         | 1           | B2            | B^2      | C4            | C^2     |

| 21         | 1           | B3            | B^3      | C6            | C^3     |

| 22         | 1           | B4            | B^4      | C8            | C^4     |

| 23         | -           | TMS           | -        | TMS           | -       |

| 24         | 1           | B5            | B^5      | C10           | C^5     |

| 25         | 1           | B6            | B^6      | C12           | C^6     |

| 26         | 1           | B7            | B^7      | C14           | C^7     |

| 27         | 1           | GND (Bank 1)  | -        | GND (Bank 1)  | -       |

| 28         | 1           | VCCO (Bank 1) | -        | VCCO (Bank 1) | -       |

| 29         | 1           | B8            | B^8      | D0            | D^0     |

| 30         | 1           | B9            | B^9      | D2            | D^1     |

| 31         | 1           | B10           | B^10     | D4            | D^2     |

| 32         | -           | TDO           | -        | TDO           | -       |

| 33         | -           | VCC           | -        | VCC           | -       |

| 34         | -           | GND           | -        | GND           | -       |

| 35         | 1           | B12           | B^12     | D8            | D^4     |

| 36         | 1           | B13           | B^13     | D10           | D^5     |

| 37         | 1           | B14           | B^14     | D12           | D^6     |

| 38         | 1           | B15/GOE1      | B^15     | D14/GOE1      | D^7     |

| 39         | 0           | CLK0/I        | -        | CLK0/I        | -       |

| 40         | 0           | A0/GOE0       | A^0      | A0/GOE0       | A^0     |

| 41         | 0           | A1            | A^1      | A2            | A^1     |

## ispMACH 4032V/B/C and 4064V/B/C Logic Signal Connections: 44-Pin TQFP (Cont.)

|            |             | ispMACH    | 4032V/B/C | ispMACH    | 4064V/B/C |

|------------|-------------|------------|-----------|------------|-----------|

| Pin Number | Bank Number | GLB/MC/Pad | ORP       | GLB/MC/Pad | ORP       |

| 42         | 0           | A2         | A^2       | A4         | A^2       |

| 43         | 0           | A3         | A^3       | A6         | A^3       |

| 44         | 0           | A4         | A^4       | A8         | A^4       |

## ispMACH 4032V/B/C/Z and 4064V/B/C/Z Logic Signal Connections: 48-Pin TQFP

| Pin    | Bank   | ispMACH 4     | 032V/B/C/Z | ispMACH 4     | 4064V/B/C | ispMACH       | 1 4064Z |

|--------|--------|---------------|------------|---------------|-----------|---------------|---------|

| Number | Number | GLB/MC/Pad    | ORP        | GLB/MC/Pad    | ORP       | GLB/MC/Pad    | ORP     |

| 1      | -      | TDI           | -          | TDI           | -         | TDI           | -       |

| 2      | 0      | A5            | A^5        | A10           | A^5       | A8            | A^5     |

| 3      | 0      | A6            | A^6        | A12           | A^6       | A10           | A^6     |

| 4      | 0      | A7            | A^7        | A14           | A^7       | A11           | A^7     |

| 5      | 0      | GND (Bank 0)  | -          | GND (Bank 0)  | -         | GND (Bank 0)  | -       |

| 6      | 0      | VCCO (Bank 0) | -          | VCCO (Bank 0) | -         | VCCO (Bank 0) | -       |

| 7      | 0      | A8            | A^8        | В0            | B^0       | B15           | B^7     |

| 8      | 0      | A9            | A^9        | B2            | B^1       | B12           | B^6     |

| 9      | 0      | A10           | A^10       | B4            | B^2       | B10           | B^5     |

| 10     | 0      | A11           | A^11       | B6            | B^3       | B8            | B^4     |

| 11     | -      | TCK           | -          | TCK           | -         | TCK           | -       |

| 12     | -      | VCC           | -          | VCC           | -         | VCC           | -       |

| 13     | -      | GND           | -          | GND           | -         | GND           | -       |

| 14     | 0      | A12           | A^12       | B8            | B^4       | B6            | B^3     |

| 15     | 0      | A13           | A^13       | B10           | B^5       | B4            | B^2     |

| 16     | 0      | A14           | A^14       | B12           | B^6       | B2            | B^1     |

| 17     | 0      | A15           | A^15       | B14           | B^7       | B0            | B^0     |

| 18     | 0      | CLK1/I        | -          | CLK1/I        | -         | CLK1/I        | -       |

| 19     | 1      | CLK2/I        | -          | CLK2/I        | -         | CLK2/I        | -       |

| 20     | 1      | B0            | B^0        | C0            | C^0       | C0            | C^0     |

| 21     | 1      | B1            | B^1        | C2            | C^1       | C1            | C^1     |

| 22     | 1      | B2            | B^2        | C4            | C^2       | C2            | C^2     |

| 23     | 1      | B3            | B^3        | C6            | C^3       | C4            | C^3     |

| 24     | 1      | B4            | B^4        | C8            | C^4       | C6            | C^4     |

| 25     | -      | TMS           | -          | TMS           | -         | TMS           | -       |

| 26     | 1      | B5            | B^5        | C10           | C^5       | C8            | C^5     |

| 27     | 1      | B6            | B^6        | C12           | C^6       | C10           | C^6     |

| 28     | 1      | B7            | B^7        | C14           | C^7       | C11           | C^7     |

| 29     | 1      | GND (Bank 1)  | -          | GND (Bank 1)  | -         | GND (Bank 1)  | -       |

| 30     | 1      | VCCO (Bank 1) | -          | VCCO (Bank 1) | -         | VCCO (Bank 1) | -       |

| 31     | 1      | B8            | B^8        | D0            | D^0       | D15           | D^7     |

| 32     | 1      | B9            | B^9        | D2            | D^1       | D12           | D^6     |

## ispMACH 4032V/B/C/Z and 4064V/B/C/Z Logic Signal Connections: 48-Pin TQFP (Cont.)

| Pin    | Bank   | ispMACH 4  | 032V/B/C/Z | ispMACH 4  | 4064V/B/C | ispMACH    | 4064Z |

|--------|--------|------------|------------|------------|-----------|------------|-------|

| Number | Number | GLB/MC/Pad | ORP        | GLB/MC/Pad | ORP       | GLB/MC/Pad | ORP   |

| 33     | 1      | B10        | B^10       | D4         | D^2       | D10        | D^5   |

| 34     | 1      | B11        | B^11       | D6         | D^3       | D8         | D^4   |

| 35     | -      | TDO        | -          | TDO        | -         | TDO        | -     |

| 36     | -      | VCC        | -          | VCC        | -         | VCC        | -     |

| 37     | -      | GND        | -          | GND        | -         | GND        | -     |

| 38     | 1      | B12        | B^12       | D8         | D^4       | D6         | D^3   |

| 39     | 1      | B13        | B^13       | D10        | D^5       | D4         | D^2   |

| 40     | 1      | B14        | B^14       | D12        | D^6       | D2         | D^1   |

| 41     | 1      | B15/GOE1   | B^15       | D14/GOE1   | D^7       | D0/GOE1    | D^0   |

| 42     | 1      | CLK3/I     | -          | CLK3/I     | -         | CLK3/I     | -     |

| 43     | 0      | CLK0/I     | -          | CLK0/I     | -         | CLK0/I     | -     |

| 44     | 0      | A0/GOE0    | A^0        | A0/GOE0    | A^0       | A0/GOE0    | A^0   |

| 45     | 0      | A1         | A^1        | A2         | A^1       | A1         | A^1   |

| 46     | 0      | A2         | A^2        | A4         | A^2       | A2         | A^2   |

| 47     | 0      | A3         | A^3        | A6         | A^3       | A4         | A^3   |

| 48     | 0      | A4         | A^4        | A8         | A^4       | A6         | A^4   |

## ispMACH 4032Z and 4064Z Logic Signal Connections: 56-Ball csBGA

|             |             | ispMACH         | 4032Z | ispMACH        | 4064Z |

|-------------|-------------|-----------------|-------|----------------|-------|

| Ball Number | Bank Number | GLB/MC/Pad      | ORP   | GLB/MC/Pad     | ORP   |

| B1          | -           | TDI             | -     | TDI            | -     |

| C3          | 0           | A5              | A^5   | A8             | A^5   |

| C1          | 0           | A6              | A^6   | A10            | A^6   |

| D1          | 0           | A7              | A^7   | A11            | A^7   |

| D3          | 0           | GND (Bank 0)    | -     | GND (Bank 0)   | -     |

| E3          | 0           | NC <sup>1</sup> | -     | J <sup>1</sup> | -     |

| E1          | 0           | NC <sup>1</sup> | -     | I <sup>1</sup> | -     |

| F3          | 0           | VCCO (Bank 0)   | -     | VCCO (Bank 0)  | -     |

| F1          | 0           | A8              | A^8   | B15            | B^7   |

| G3          | 0           | A9              | A^9   | B12            | B^6   |

| G1          | 0           | A10             | A^10  | B10            | B^5   |

| H1          | 0           | A11             | A^11  | B8             | B^4   |

| J1          | 0           | NC              | -     | I              | -     |

| K1          | -           | TCK             | -     | TCK            | -     |

| K2          | -           | VCC             | -     | VCC            | -     |

| H3          | -           | GND             | -     | GND            | -     |

| K3          | -           | NC <sup>1</sup> | -     | J <sup>1</sup> | -     |

| K4          | 0           | A12             | A^12  | B6             | B^3   |

| H4          | 0           | A13             | A^13  | B4             | B^2   |

| H5          | 0           | A14             | A^14  | B2             | B^1   |

## ispMACH 4064V/B/C/Z, 4128V/B/C/Z, 4256V/B/C/Z Logic Signal Connections: 100-Pin TQFP (Cont.)

|            | Bank   | ispMACH 40    | 64V/B/C/Z | ispMACH 41    | 28V/B/C/Z | ispMACH 42    | 256V/B/C/Z |

|------------|--------|---------------|-----------|---------------|-----------|---------------|------------|

| Pin Number | Number | GLB/MC/Pad    | ORP       | GLB/MC/Pad    | ORP       | GLB/MC/Pad    | ORP        |

| 83         | 1      | VCCO (Bank 1) | -         | VCCO (Bank 1) | -         | VCCO (Bank 1) | -          |

| 84         | 1      | D3            | D^3       | H6            | H^3       | P12           | P^3        |

| 85         | 1      | D2            | D^2       | H4            | H^2       | P10           | P^2        |

| 86         | 1      | D1            | D^1       | H2            | H^1       | P6            | P^1        |

| 87         | 1      | D0/GOE1       | D^0       | H0/GOE1       | H^0       | P2/OE1        | P^0        |

| 88         | 1      | CLK3/I        | -         | CLK3/I        | -         | CLK3/I        | -          |

| 89         | 0      | CLK0/I        | -         | CLK0/I        | -         | CLK0/I        | -          |

| 90         | -      | VCC           | -         | VCC           | -         | VCC           | -          |

| 91         | 0      | A0/GOE0       | A^0       | A0/GOE0       | A^0       | A2/GOE0       | A^0        |

| 92         | 0      | A1            | A^1       | A2            | A^1       | A6            | A^1        |

| 93         | 0      | A2            | A^2       | A4            | A^2       | A10           | A^2        |

| 94         | 0      | A3            | A^3       | A6            | A^3       | A12           | A^3        |

| 95         | 0      | VCCO (Bank 0) | -         | VCCO (Bank 0) | -         | VCCO (Bank 0) | -          |

| 96         | 0      | GND (Bank 0)  | -         | GND (Bank 0)  | -         | GND (Bank 0)  | -          |

| 97         | 0      | A4            | A^4       | A8            | A^4       | B2            | B^0        |

| 98         | 0      | A5            | A^5       | A10           | A^5       | B6            | B^1        |

| 99         | 0      | A6            | A^6       | A12           | A^6       | B10           | B^2        |

| 100        | 0      | A7            | A^7       | A14           | A^7       | B12           | B^3        |

<sup>\*</sup>This pin is input only.

## ispMACH 4128V/B/C Logic Signal Connections: 128-Pin TQFP

|            |             | ispMACH 41    | 28V/B/C |

|------------|-------------|---------------|---------|

| Pin Number | Bank Number | GLB/MC/Pad    | ORP     |

| 1          | 0           | GND           | -       |

| 2          | 0           | TDI           | -       |

| 3          | 0           | VCCO (Bank 0) | -       |

| 4          | 0           | B0            | B^0     |

| 5          | 0           | B1            | B^1     |

| 6          | 0           | B2            | B^2     |

| 7          | 0           | B4            | B^3     |

| 8          | 0           | B5            | B^4     |

| 9          | 0           | B6            | B^5     |

| 10         | 0           | GND (Bank 0)  | -       |

| 11         | 0           | B8            | B^6     |

| 12         | 0           | B9            | B^7     |

| 13         | 0           | B10           | B^8     |

| 14         | 0           | B12           | B^9     |

| 15         | 0           | B13           | B^10    |

| 16         | 0           | B14           | B^11    |

| 17         | 0           | VCCO (Bank 0) | -       |

| 18         | 0           | C14           | C^11    |

## ispMACH 4064Z, 4128Z and 4256Z Logic Signal Connections: 132-Ball csBGA (Cont.)

|             |             | ispMAC          | H 4064Z | ispMAC        | H 4128Z | ispMAC         | H 4256Z |

|-------------|-------------|-----------------|---------|---------------|---------|----------------|---------|

| Ball Number | Bank Number | GLB/MC/Pad      | ORP     | GLB/MC/Pad    | ORP     | GLB/MC/Pad     | ORP     |

| D13         | 1           | D10             | D^10    | G4            | G^3     | N6             | N^3     |

| D14         | 1           | D9              | D^9     | G2            | G^2     | N8             | N^4     |

| D12         | 1           | D8              | D^8     | G1            | G^1     | N10            | N^5     |

| C14         | 1           | I               | -       | G0            | G^0     | N12            | N^6     |

| C13         | 1           | NC              | -       | VCCO (Bank 1) | -       | VCCO (Bank 1)  | -       |

| B14         | -           | TDO             | -       | TDO           | -       | TDO            | -       |

| A14         | -           | VCC             | -       | VCC           | -       | VCC            | -       |

| A13         | -           | GND             | -       | GND           | -       | GND            | -       |

| B13         | 1           | NC              | -       | H14           | H^11    | O12            | O^6     |

| A12         | 1           | Ţ               | -       | H13           | H^10    | O10            | O^5     |

| C12         | 1           | D7              | D^7     | H12           | H^9     | O8             | 0^4     |

| B12         | 1           | D6              | D^6     | H10           | H^8     | O6             | O^3     |

| A11         | 1           | D5              | D^5     | H9            | H^7     | O4             | 0^2     |

| C11         | 1           | D4              | D^4     | H8            | H^6     | O2             | O^1     |

| B11         | 1           | GND (Bank 1)    | -       | GND (Bank 1)  | -       | GND (Bank 1)   | -       |

| A10         | 1           | VCCO (Bank 1)   | -       | VCCO (Bank 1) | -       | VCCO (Bank 1)  | -       |

| B10         | 1           | NC              | -       | H6            | H^5     | P12            | P^6     |

| C10         | 1           | NC              | -       | H5            | H^4     | P10            | P^5     |

| B9          | 1           | D3              | D^3     | H4            | H^3     | P8             | P^4     |

| A9          | 1           | D2              | D^2     | H2            | H^2     | P6             | P^3     |

| C9          | 1           | D1              | D^1     | H1            | H^1     | P4             | P^2     |

| A8          | 1           | D0/GOE1         | D^0     | H0/GOE1       | H^0     | P2/GOE1        | P^1     |

| B8          | 1           | CLK3/I          | -       | CLK3/I        | -       | CLK3/I         | -       |

| C8          | 0           | CLK0/I          | -       | CLK0/I        | -       | CLK0/I         | -       |

| B7          | -           | VCC             | -       | VCC           | -       | VCC            | -       |

| A7          | 0           | NC <sup>1</sup> | -       | NC¹           | -       | I <sup>1</sup> | -       |

| C7          | 0           | A0/GOE0         | A^0     | A0/GOE0       | A^0     | A2/GOE0        | A^1     |

| A6          | 0           | A1              | A^1     | A1            | A^1     | A4             | A^2     |

| B6          | 0           | A2              | A^2     | A2            | A^2     | A6             | A^3     |

| C6          | 0           | A3              | A^3     | A4            | A^3     | A8             | A^4     |

| B5          | 0           | NC              | -       | A5            | A^4     | A10            | A^5     |

| A5          | 0           | NC              | -       | A6            | A^5     | A12            | A^6     |

| C5          | 0           | VCCO (Bank 0)   | -       | VCCO (Bank 0) | -       | VCCO (Bank 0)  | -       |

| B4          | 0           | GND (Bank 0)    | -       | GND (Bank 0)  | -       | GND (Bank 0)   | -       |

| A4          | 0           | NC              | -       | A8            | A^6     | B2             | B^1     |

| C4          | 0           | A4              | A^4     | A9            | A^7     | B4             | B^2     |

| A3          | 0           | A5              | A^5     | A10           | A^8     | В6             | B^3     |

| В3          | 0           | A6              | A^6     | A12           | A^9     | B8             | B^4     |

| A2          | 0           | A7              | A^7     | A13           | A^10    | B10            | B^5     |

| A1          | 0           | NC              | -       | A14           | A^11    | B12            | B^6     |

|             | 1           | 1               |         | 1             | l       | l .            |         |

<sup>1.</sup> For device migration considerations, these NC pins are input signal pins in ispMACH 4256Z device.

## ispMACH 4128V and 4256V Logic Signal Connections: 144-Pin TQFP

|            |             | ispMAC                    | H 4128V | ispMAC                | H 4256V |

|------------|-------------|---------------------------|---------|-----------------------|---------|

| Pin Number | Bank Number | GLB/MC/Pad                | ORP     | GLB/MC/Pad            | ORP     |

| 1          | -           | GND                       | -       | GND                   | -       |

| 2          | -           | TDI                       | -       | TDI                   | -       |

| 3          | 0           | VCCO (Bank 0)             | -       | VCCO (Bank 0)         | -       |

| 4          | 0           | B0                        | B^0     | C12                   | C^6     |

| 5          | 0           | B1                        | B^1     | C10                   | C^5     |

| 6          | 0           | B2                        | B^2     | C8                    | C^4     |

| 7          | 0           | B4                        | B^3     | C6                    | C^3     |

| 8          | 0           | B5                        | B^4     | C4                    | C^2     |

| 9          | 0           | B6                        | B^5     | C2                    | C^1     |

| 10         | 0           | GND (Bank 0)              | -       | GND (Bank 0)          | -       |

| 11         | 0           | B8                        | B^6     | D14                   | D^7     |

| 12         | 0           | B9                        | B^7     | D12                   | D^6     |

| 13         | 0           | B10                       | B^8     | D10                   | D^5     |

| 14         | 0           | B12                       | B^9     | D8                    | D^4     |

| 15         | 0           | B13                       | B^10    | D6                    | D^3     |

| 16         | 0           | B14                       | B^11    | D4                    | D^2     |

| 17         | -           | NC <sup>2</sup>           | -       | <b>l</b> <sup>2</sup> | -       |

| 18         | 0           | GND (Bank 0) <sup>1</sup> | -       | NC <sup>1</sup>       | -       |

| 19         | 0           | VCCO (Bank 0)             | -       | VCCO (Bank 0)         | -       |

| 20         | 0           | NC <sup>2</sup>           | -       | <b>I</b> <sup>2</sup> | -       |

| 21         | 0           | C14                       | C^11    | E2                    | E^1     |

| 22         | 0           | C13                       | C^10    | E4                    | E^2     |

| 23         | 0           | C12                       | C^9     | E6                    | E^3     |

| 24         | 0           | C10                       | C^8     | E8                    | E^4     |

| 25         | 0           | C9                        | C^7     | E10                   | E^5     |

| 26         | 0           | C8                        | C^6     | E12                   | E^6     |

| 27         | 0           | GND (Bank 0)              | -       | GND (Bank 0)          | -       |

| 28         | 0           | C6                        | C^5     | F2                    | F^1     |

| 29         | 0           | C5                        | C^4     | F4                    | F^2     |

| 30         | 0           | C4                        | C^3     | F6                    | F^3     |

| 31         | 0           | C2                        | C^2     | F8                    | F^4     |

| 32         | 0           | C1                        | C^1     | F10                   | F^5     |

| 33         | 0           | C0                        | C^0     | F12                   | F^6     |

| 34         | 0           | VCCO (Bank 0)             | -       | VCCO (Bank 0)         | -       |

| 35         | -           | TCK                       | -       | TCK                   | -       |

| 36         | -           | VCC                       | -       | VCC                   | -       |

| 37         | -           | GND                       | -       | GND                   | -       |

| 38         | 0           | NC <sup>2</sup>           | -       | l <sup>2</sup>        | -       |

| 39         | 0           | D14                       | D^11    | G12                   | G^6     |

| 40         | 0           | D13                       | D^10    | G10                   | G^5     |

| 41         | 0           | D12                       | D^9     | G8                    | G^4     |

| 42         | 0           | D10                       | D^8     | G6                    | G^3     |

# ispMACH 4256V/B/C, 4384V/B/C, 4512V/B/C Logic Signal Connections: 256-Ball ftBGA/fpBGA (Cont.)

| Ball   | I/O  | ispMACH 4256<br>128-I/O | V/B/C | ispMACH 4256<br>160-I/O | V/B/C | ispMACH 4384  | V/B/C | ispMACH 4512  | V/B/C |

|--------|------|-------------------------|-------|-------------------------|-------|---------------|-------|---------------|-------|

| Number | Bank | GLB/MC/Pad              | ORP   | GLB/MC/Pad              | ORP   | GLB/MC/Pad    | ORP   | GLB/MC/Pad    | ORP   |

| J6     | 0    | E14                     | E^7   | E10                     | E^7   | H14           | H^7   | J14           | J^7   |

| K3     | 0    | NC                      | -     | E12                     | E^8   | G0            | G^0   | 10            | I^0   |

| K4     | 0    | NC                      | -     | E14                     | E^9   | G2            | G^1   | 14            | I^1   |

| L1     | 0    | NC                      | -     | NC                      | -     | l14           | I^7   | K0            | K^0   |

| L2     | 0    | NC                      | -     | NC                      | -     | l12           | I^6   | K2            | K^1   |

| M1     | 0    | NC                      | -     | NC                      | -     | NC            | -     | K4            | K^2   |

| -      | 0    | GND (Bank 0)            | -     | GND (Bank 0)            | -     | GND (Bank 0)  | -     | GND (Bank 0)  | -     |

| -      | 0    | -                       | -     | VCCO (Bank 0)           | -     | VCCO (Bank 0) | -     | VCCO (Bank 0) | -     |

| M2     | 0    | NC                      | -     | NC                      | -     | NC            | -     | K6            | K^3   |

| N1     | 0    | NC                      | -     | NC                      | -     | I10           | I^5   | K8            | K^4   |

| М3     | 0    | NC                      | -     | NC                      | -     | 18            | I^4   | K10           | K^5   |

| M4     | 0    | NC                      | -     | F0                      | F^0   | G4            | G^2   | 18            | I^2   |

| N2     | 0    | NC                      | -     | F1                      | F^1   | G6            | G^3   | l12           | I^3   |

| K5     | 0    | F0                      | F^0   | F2                      | F^2   | J0            | J^0   | N0            | N^0   |

| P1     | 0    | F2                      | F^1   | F4                      | F^3   | J2            | J^1   | N2            | N^1   |

| K6     | 0    | F4                      | F^2   | F6                      | F^4   | J4            | J^2   | N4            | N^2   |

| N3     | 0    | F6                      | F^3   | F8                      | F^5   | J6            | J^3   | N6            | N^3   |

| L5     | 0    | F8                      | F^4   | F9                      | F^6   | J8            | J^4   | N8            | N^4   |

| P2     | 0    | F10                     | F^5   | F10                     | F^7   | J10           | J^5   | N10           | N^5   |

| L6     | 0    | F12                     | F^6   | F12                     | F^8   | J12           | J^6   | N12           | N^6   |

| R1     | 0    | F14                     | F^7   | F14                     | F^9   | J14           | J^7   | N14           | N^7   |

| -      | 0    | VCCO (Bank 0)           | -     | VCCO (Bank 0)           | -     | VCCO (Bank 0) | -     | VCCO (Bank 0) | -     |

| P3     | -    | TCK                     | -     | TCK                     | -     | TCK           | -     | TCK           | -     |

| -      | -    | VCC                     | -     | VCC                     | -     | VCC           | -     | VCC           | -     |

| -      | -    | GND                     | -     | GND                     | -     | GND           | -     | GND           | -     |

| -      | 0    | -                       | -     | GND (Bank 0)            | -     | GND (Bank 0)  | -     | GND (Bank 0)  | -     |

| T2     | 0    | NC                      | -     | G14                     | G^9   | 16            | I^3   | K12           | K^6   |

| M5     | 0    | NC                      | -     | G12                     | G^8   | 14            | I^2   | K14           | K^7   |

| N4     | 0    | G14                     | G^7   | G10                     | G^7   | K14           | K^7   | O14           | O^7   |

| Т3     | 0    | G12                     | G^6   | G9                      | G^6   | K12           | K^6   | O12           | O^6   |

| R3     | 0    | G10                     | G^5   | G8                      | G^5   | K10           | K^5   | O10           | O^5   |

| M6     | 0    | G8                      | G^4   | G6                      | G^4   | K8            | K^4   | O8            | 0^4   |

| P4     | 0    | G6                      | G^3   | G4                      | G^3   | K6            | K^3   | O6            | O^3   |

| L7     | 0    | G4                      | G^2   | G2                      | G^2   | K4            | K^2   | 04            | 0^2   |

| N5     | 0    | G2                      | G^1   | G1                      | G^1   | K2            | K^1   | O2            | 0^1   |

| M7     | 0    | G0                      | G^0   | G0                      | G^0   | K0            | K^0   | 00            | O^0   |

| P5     | 0    | NC                      | -     | NC                      | -     | G8            | G^4   | MO            | M^0   |

| R4     | 0    | NC                      | -     | NC                      | -     | G10           | G^5   | M4            | M^1   |

| T4     | 0    | NC                      | -     | NC                      | -     | NC            | -     | L0            | L^0   |

| -      | 0    | GND (Bank 0)            | -     | GND (Bank 0)            | -     | GND (Bank 0)  | -     | GND (Bank 0)  | -     |

| -      | 0    | VCCO (Bank 0)           | -     | VCCO (Bank 0)           | -     | VCCO (Bank 0) | -     | VCCO (Bank 0) | -     |

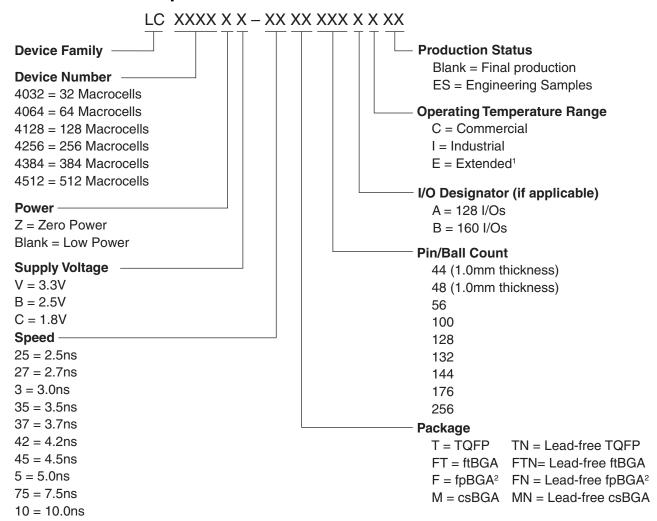

#### **Part Number Description**

- 1. For automotive AEC-Q100 compliant devices, refer to the LA-ispMACH 4000V/Z Automotive Family Data Sheet (DS1017).

- 2. Use ftBGA package. fpBGA package devices have been discontinued via PCN#14A-07.

## ispMACH 4000 Family Speed Grade Offering

|                   | -25 | -27 | -3  | -35 | -37 | -42 | -45 | -;  | 5   |     | -75 |     | -10 |

|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|                   | Com | Ind | Com | Ind | Ext | Ind |

| ispMACH 4032V/B/C |     |     |     |     |     |     |     |     |     |     |     | 1   |     |

| ispMACH 4064V/B/C |     |     |     |     |     |     |     |     |     |     |     | 1   |     |

| ispMACH 4128V/B/C |     |     |     |     |     |     |     |     |     |     |     | 1   |     |

| ispMACH 4256V/B/C |     |     |     |     |     |     |     |     |     |     |     |     |     |

| ispMACH 4384V/B/C |     |     |     |     |     |     |     |     |     |     |     |     |     |

| ispMACH 4512V/B/C |     |     |     |     |     |     |     |     |     |     |     |     |     |

| ispMACH 4032ZC    |     |     |     |     |     |     |     |     |     |     |     | 1   |     |

| ispMACH 4064ZC    |     |     |     |     |     |     |     |     |     |     |     | 1   |     |

| ispMACH 4128ZC    |     |     |     |     |     |     |     |     |     |     |     | 1   |     |

| ispMACH 4256ZC    |     |     |     |     |     |     |     |     |     |     |     |     |     |

1. 3.3V only.

#### ispMACH 4000C (1.8V) Industrial Devices (Cont.)

| Family  | Part Number                  | Macrocells | Voltage | t <sub>PD</sub> | Package | Pin/Ball Count | 1/0 | Grade |

|---------|------------------------------|------------|---------|-----------------|---------|----------------|-----|-------|

|         | LC4384C-5FT256I              | 384        | 1.8     | 5               | ftBGA   | 256            | 192 | ı     |

|         | LC4384C-75FT256I             | 384        | 1.8     | 7.5             | ftBGA   | 256            | 192 | I     |

|         | LC4384C-10FT256I             | 384        | 1.8     | 10              | ftBGA   | 256            | 192 | I     |

|         | LC4384C-5F256I <sup>1</sup>  | 384        | 1.8     | 5               | fpBGA   | 256            | 192 | I     |

| LC4384C | LC4384C-75F256I <sup>1</sup> | 384        | 1.8     | 7.5             | fpBGA   | 256            | 192 | I     |

|         | LC4384C-10F256I <sup>1</sup> | 384        | 1.8     | 10              | fpBGA   | 256            | 192 | I     |

|         | LC4384C-5T176I               | 384        | 1.8     | 5               | TQFP    | 176            | 128 | I     |

|         | LC4384C-75T176I              | 384        | 1.8     | 7.5             | TQFP    | 176            | 128 | I     |

|         | LC4384C-10T176I              | 384        | 1.8     | 10              | TQFP    | 176            | 128 | I     |

|         | LC4512C-5FT256I              | 512        | 1.8     | 5               | ftBGA   | 256            | 208 | I     |

|         | LC4512C-75FT256I             | 512        | 1.8     | 7.5             | ftBGA   | 256            | 208 | I     |

|         | LC4512C-10FT256I             | 512        | 1.8     | 10              | ftBGA   | 256            | 208 | I     |

|         | LC4512C-5F256I <sup>1</sup>  | 512        | 1.8     | 5               | fpBGA   | 256            | 208 | I     |

| LC4512C | LC4512C-75F256I <sup>1</sup> | 512        | 1.8     | 7.5             | fpBGA   | 256            | 208 | I     |

|         | LC4512C-10F256I <sup>1</sup> | 512        | 1.8     | 10              | fpBGA   | 256            | 208 | I     |

|         | LC4512C-5T176I               | 512        | 1.8     | 5               | TQFP    | 176            | 128 | I     |

|         | LC4512C-75T176I              | 512        | 1.8     | 7.5             | TQFP    | 176            | 128 | I     |

|         | LC4512C-10T176I              | 512        | 1.8     | 10              | TQFP    | 176            | 128 | I     |

<sup>1.</sup> Use ftBGA package. fpBGA package devices have been discontinued via PCN#14A-07.

#### ispMACH 4000B (2.5V) Commercial Devices

| Device   | Part Number     | Macrocells | Voltage | t <sub>PD</sub> | Package | Pin/Ball Count | I/O | Grade |

|----------|-----------------|------------|---------|-----------------|---------|----------------|-----|-------|

|          | LC4032B-25T48C  | 32         | 2.5     | 2.5             | TQFP    | 48             | 32  | С     |

|          | LC4032B-5T48C   | 32         | 2.5     | 5               | TQFP    | 48             | 32  | С     |

| LC4032B  | LC4032B-75T48C  | 32         | 2.5     | 7.5             | TQFP    | 48             | 32  | С     |

| LC4032B  | LC4032B-25T44C  | 32         | 2.5     | 2.5             | TQFP    | 44             | 30  | С     |

|          | LC4032B-5T44C   | 32         | 2.5     | 5               | TQFP    | 44             | 30  | С     |

|          | LC4032B-75T44C  | 32         | 2.5     | 7.5             | TQFP    | 44             | 30  | С     |

|          | LC4064B-25T100C | 64         | 2.5     | 2.5             | TQFP    | 100            | 64  | С     |

|          | LC4064B-5T100C  | 64         | 2.5     | 5               | TQFP    | 100            | 64  | С     |

|          | LC4064B-75T100C | 64         | 2.5     | 7.5             | TQFP    | 100            | 64  | С     |

|          | LC4064B-25T48C  | 64         | 2.5     | 2.5             | TQFP    | 48             | 32  | С     |

| LC4064B  | LC4064B-5T48C   | 64         | 2.5     | 5               | TQFP    | 48             | 32  | С     |

|          | LC4064B-75T48C  | 64         | 2.5     | 7.5             | TQFP    | 48             | 32  | С     |

|          | LC4064B-25T44C  | 64         | 2.5     | 2.5             | TQFP    | 44             | 30  | С     |

|          | LC4064B-5T44C   | 64         | 2.5     | 5               | TQFP    | 44             | 30  | С     |

|          | LC4064B-75T44C  | 64         | 2.5     | 7.5             | TQFP    | 44             | 30  | С     |

|          | LC4128B-27T128C | 128        | 2.5     | 2.7             | TQFP    | 128            | 92  | С     |

|          | LC4128B-5T128C  | 128        | 2.5     | 5               | TQFP    | 128            | 92  | С     |

| I C4120B | LC4128B-75T128C | 128        | 2.5     | 7.5             | TQFP    | 128            | 92  | С     |

| _C4128B  | LC4128B-27T100C | 128        | 2.5     | 2.7             | TQFP    | 100            | 64  | С     |

|          | LC4128B-5T100C  | 128        | 2.5     | 5               | TQFP    | 100            | 64  | С     |

|          | LC4128B-75T100C | 128        | 2.5     | 7.5             | TQFP    | 100            | 64  | С     |

#### ispMACH 4000B (2.5V) Lead-Free Commercial Devices (Cont.)

| Device  | Part Number                   | Macrocells | Voltage | t <sub>PD</sub> | Package         | Pin/Ball<br>Count | I/O | Grade |

|---------|-------------------------------|------------|---------|-----------------|-----------------|-------------------|-----|-------|

|         | LC4384B-35FTN256C             | 384        | 2.5     | 3.5             | Lead-Free ftBGA | 256               | 192 | С     |

|         | LC4384B-5FTN256C              | 384        | 2.5     | 5               | Lead-Free ftBGA | 256               | 192 | С     |

|         | LC4384B-75FTN256C             | 384        | 2.5     | 7.5             | Lead-Free ftBGA | 256               | 192 | С     |

|         | LC4384B-35FN256C1             | 384        | 2.5     | 3.5             | Lead-Free fpBGA | 256               | 192 | С     |

| LC4384B | LC4384B-5FN256C1              | 384        | 2.5     | 5               | Lead-Free fpBGA | 256               | 192 | С     |

|         | LC4384B-75FN256C <sup>1</sup> | 384        | 2.5     | 7.5             | Lead-Free fpBGA | 256               | 192 | С     |

|         | LC4384B-35TN176C              | 384        | 2.5     | 3.5             | Lead-Free TQFP  | 176               | 128 | С     |

|         | LC4384B-5TN176C               | 384        | 2.5     | 5               | Lead-Free TQFP  | 176               | 128 | С     |

|         | LC4384B-75TN176C              | 384        | 2.5     | 7.5             | Lead-Free TQFP  | 176               | 128 | С     |

|         | LC4512B-35FTN256C             | 512        | 2.5     | 3.5             | Lead-Free ftBGA | 256               | 208 | С     |

|         | LC4512B-5FTN256C              | 512        | 2.5     | 5               | Lead-Free ftBGA | 256               | 208 | С     |

|         | LC4512B-75FTN256C             | 512        | 2.5     | 7.5             | Lead-Free ftBGA | 256               | 208 | С     |

|         | LC4512B-35FN256C1             | 512        | 2.5     | 3.5             | Lead-Free fpBGA | 256               | 208 | С     |

| LC4512B | LC4512B-5FN256C1              | 512        | 2.5     | 5               | Lead-Free fpBGA | 256               | 208 | С     |

|         | LC4512B-75FN256C <sup>1</sup> | 512        | 2.5     | 7.5             | Lead-Free fpBGA | 256               | 208 | С     |

|         | LC4512B-35TN176C              | 512        | 2.5     | 3.5             | Lead-Free TQFP  | 176               | 128 | С     |

|         | LC4512B-5TN176C               | 512        | 2.5     | 5               | Lead-Free TQFP  | 176               | 128 | С     |

|         | LC4512B-75TN176C              | 512        | 2.5     | 7.5             | Lead-Free TQFP  | 176               | 128 | С     |

<sup>1.</sup> Use ftBGA package. fpBGA package devices have been discontinued via PCN#14A-07.

#### ispMACH 4000B (2.5V) Lead-Free Industrial Devices

| Device  | Part Number      | Macrocells | Voltage | t <sub>PD</sub> | Package        | Pin/Ball<br>Count | I/O | Grade |

|---------|------------------|------------|---------|-----------------|----------------|-------------------|-----|-------|

|         | LC4032B-5TN48I   | 32         | 2.5     | 5               | Lead-Free TQFP | 48                | 32  | I     |

|         | LC4032B-75TN48I  | 32         | 2.5     | 7.5             | Lead-Free TQFP | 48                | 32  | I     |

| LC4032B | LC4032B-10TN48I  | 32         | 2.5     | 10              | Lead-Free TQFP | 48                | 32  | I     |

| LC4032B | LC4032B-5TN44I   | 32         | 2.5     | 5               | Lead-Free TQFP | 44                | 30  | I     |

|         | LC4032B-75TN44I  | 32         | 2.5     | 7.5             | Lead-Free TQFP | 44                | 30  | I     |

|         | LC4032B-10TN44I  | 32         | 2.5     | 10              | Lead-Free TQFP | 44                | 30  | I     |

|         | LC4064B-5TN100I  | 64         | 2.5     | 5               | Lead-Free TQFP | 100               | 64  | I     |

|         | LC4064B-75TN100I | 64         | 2.5     | 7.5             | Lead-Free TQFP | 100               | 64  | I     |

|         | LC4064B-10TN100I | 64         | 2.5     | 10              | Lead-Free TQFP | 100               | 64  | I     |

|         | LC4064B-5TN48I   | 64         | 2.5     | 5               | Lead-Free TQFP | 48                | 32  | I     |

| LC4064B | LC4064B-75TN48I  | 64         | 2.5     | 7.5             | Lead-Free TQFP | 48                | 32  | I     |

|         | LC4064B-10TN48I  | 64         | 2.5     | 10              | Lead-Free TQFP | 48                | 32  | I     |

|         | LC4064B-5TN44I   | 64         | 2.5     | 5               | Lead-Free TQFP | 44                | 30  | I     |

|         | LC4064B-75TN44I  | 64         | 2.5     | 7.5             | Lead-Free TQFP | 44                | 30  | I     |

|         | LC4064B-10TN44I  | 64         | 2.5     | 10              | Lead-Free TQFP | 44                | 30  | I     |