# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                              |

|----------------------------|-----------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                                  |

| Speed                      | 80MHz                                                                                               |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                                          |

| Number of I/O              | 82                                                                                                  |

| Program Memory Size        | 1MB (1M × 8)                                                                                        |

| Program Memory Type        | FLASH                                                                                               |

| EEPROM Size                | -                                                                                                   |

| RAM Size                   | 128K x 8                                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                                        |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                               |

| Oscillator Type            | Internal                                                                                            |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                                  |

| Mounting Type              | Surface Mount                                                                                       |

| Package / Case             | 100-LQFP                                                                                            |

| Supplier Device Package    | 100-LQFP (14x14)                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l476vgt7                               |

|                            |                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

If in Range 1, then the following step can be applied:

5. Increase the system frequency if needed.

# 5.2 **Power supply supervisor**

# 5.2.1 Power-on reset (POR) / power-down reset (PDR) / brown-out reset (BOR)

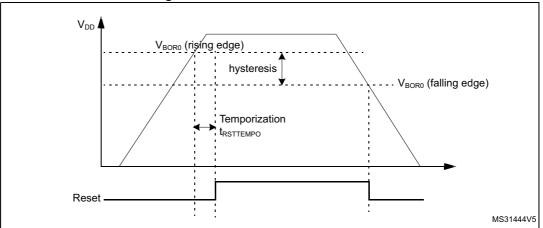

The device has an integrated power-on reset (POR) / power-down reset (PDR), coupled with a brown-out reset (BOR) circuitry. The BOR is active in all power modes except Shutdown mode, and cannot be disabled.

Five BOR thresholds can be selected through option bytes.

During power-on, the BOR keeps the device under reset until the supply voltage V<sub>DD</sub> reaches the specified V<sub>BORx</sub> threshold. When V<sub>DD</sub> drops below the selected threshold, a device reset is generated. When V<sub>DD</sub> is above the V<sub>BORx</sub> upper limit, the device reset is released and the system can start.

For more details on the brown-out reset thresholds, refer to the electrical characteristics section in the datasheet.

Figure 11. Brown-out reset waveform

1. The reset temporization  $t_{RSTTEMPO}$  is present only for the BOR lowest threshold (V<sub>BOR0</sub>).

# 5.2.2 Programmable voltage detector (PVD)

You can use the PVD to monitor the  $V_{DD}$  power supply by comparing it to a threshold selected by the PLS[2:0] bits in the *Power control register 2 (PWR\_CR2)*.

The PVD is enabled by setting the PVDE bit.

A PVDO flag is available, in the *Power status register 2 (PWR\_SR2)*, to indicate if  $V_{DD}$  is higher or lower than the PVD threshold. This event is internally connected to the EXTI line16 and can generate an interrupt if enabled through the EXTI registers. The PVD output interrupt can be generated when  $V_{DD}$  drops below the PVD threshold and/or when  $V_{DD}$  rises above the PVD threshold depending on EXTI line16 rising/falling edge configuration. As an example, the service routine could perform emergency shutdown tasks.

RM0351

This register only configures the clock gating, not the clock source itself. Most of the peripherals are clocked by a single clock (AHB or APB clock), which is always disabled in Stop mode. In this case setting the bit has no effect in Stop mode.

# 6.4.24 AHB3 peripheral clocks enable in Sleep and Stop modes register (RCC\_AHB3SMENR)

Address offset: 0x70

Reset value: 0x00000 0101

Access: no wait state, word, half-word and byte access

| 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24           | 23   | 22   | 21   | 20   | 19   | 18   | 17   | 16          |

|------|------|------|------|------|------|------|--------------|------|------|------|------|------|------|------|-------------|

| Res.         | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res.        |

|      |      |      |      |      |      |      |              |      |      |      |      |      |      |      |             |

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8            | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0           |

| Res. | QSPI<br>SMEN | Res. | FMC<br>SMEN |

|      |      |      |      |      |      |      | rw           |      |      |      |      |      |      |      | rw          |

Bits 31:9 Reserved, must be kept at reset value.

Bit 8 **QSPISMEN** Quad SPI memory interface clocks enable during Sleep and Stop modes

Set and cleared by software.

0: QUADSPI clocks disabled by the clock gating<sup>(1)</sup> during Sleep and Stop modes

1: QUADSPI clocks enabled by the clock gating<sup>(1)</sup> during Sleep and Stop modes

Bits 7:1 Reserved, must be kept at reset value.

Bit 0 **FMCSMEN**: Flexible memory controller clocks enable during Sleep and Stop modes

Set and cleared by software.

0: FMC clocks disabled by the clock gating<sup>(1)</sup> during Sleep and Stop modes

1: FMC clocks enabled by the clock gating<sup>(1)</sup> during Sleep and Stop modes

This register only configures the clock gating, not the clock source itself. Most of the peripherals are clocked by a single clock (AHB or APB clock), which is always disabled in Stop mode. In this case setting the bit has no effect in Stop mode.

# 6.4.25 APB1 peripheral clocks enable in Sleep and Stop modes register 1 (RCC\_APB1SMENR1)

Address: 0x78

Reset value: 0xF7FE CE3F (for STM32L496xx/4A6xx devices)

0xF2FE CA3F (for STM32L475xx/476xx/486xx devices)

Access: no wait state, word, half-word and byte access

| 31             | 30            | 29           | 28          | 27           | 26                 | 25           | 24          | 23           | 22           | 21           | 20            | 19            | 18             | 17             | 16           |

|----------------|---------------|--------------|-------------|--------------|--------------------|--------------|-------------|--------------|--------------|--------------|---------------|---------------|----------------|----------------|--------------|

| LPTIM1<br>SMEN | OPAMP<br>SMEN | DAC1<br>SMEN | PWR<br>SMEN | Res.         | CAN2<br>SMEN       | CAN1<br>SMEN | CRSS<br>MEN | I2C3<br>SMEN | I2C2<br>SMEN | I2C1<br>SMEN | UART5<br>SMEN | UART4<br>SMEN | USART3<br>SMEN | USART2<br>SMEN | Res.         |

| rw             | rw            | rw           | rw          |              | rw                 | rw           | rw          | rw           | rw           | rw           | rw            | rw            | rw             | rw             |              |

| 15             | 14            | 13           | 12          | 11           | 10                 | 9            | 8           | 7            | 6            | 5            | 4             | 3             | 2              | 1              | 0            |

| SPI3<br>SMEN   | SPI2<br>SMEN  | Res.         | Res.        | WWDG<br>SMEN | RTCA<br>PBSM<br>EN | LCD<br>SMEN  | Res.        | Res.         | Res.         | TIM7<br>SMEN | TIM6<br>SMEN  | TIM5<br>SMEN  | TIM4<br>SMEN   | TIM3<br>SMEN   | TIM2<br>SMEN |

| rw             | rw            |              |             | rw           | rw                 | rw           |             |              |              | rw           | rw            | rw            | rw             | rw             | rw           |

DocID024597 Rev 5

259/1830

| Position | Priority | Type of<br>priority | Acronym                | Description                                   | Address     |  |  |  |  |  |  |  |

|----------|----------|---------------------|------------------------|-----------------------------------------------|-------------|--|--|--|--|--|--|--|

| 12       | 19       | settable            | DMA1_CH2               | DMA1 channel 2 interrupt                      | 0x0000 0070 |  |  |  |  |  |  |  |

| 13       | 20       | settable            | DMA1_CH3               | DMA1 channel 3 interrupt                      | 0x0000 0074 |  |  |  |  |  |  |  |

| 14       | 21       | settable            | DMA1_CH4               | DMA1 channel 4 interrupt                      | 0x0000 0078 |  |  |  |  |  |  |  |

| 15       | 22       | settable            | DMA1_CH5               | DMA1 channel 5 interrupt                      | 0x0000 007C |  |  |  |  |  |  |  |

| 16       | 23       | settable            | DMA1_CH6               | DMA1 channel 6 interrupt                      | 0x0000 0080 |  |  |  |  |  |  |  |

| 17       | 24       | settable            | DMA1_CH7               | DMA1 channel 7 interrupt                      | 0x0000 0084 |  |  |  |  |  |  |  |

| 18       | 25       | settable            | ADC1_2                 | ADC1 and ADC2 global interrupt                | 0x0000 0088 |  |  |  |  |  |  |  |

| 19       | 26       | settable            | CAN1_TX                | CAN1_TX interrupts                            | 0x0000 008C |  |  |  |  |  |  |  |

| 20       | 27       | settable            | CAN1_RX0               | CAN1_RX0 interrupts                           | 0x0000 0090 |  |  |  |  |  |  |  |

| 21       | 28       | settable            | CAN1_RX1               | CAN1_RX1 interrupt                            | 0x0000 0094 |  |  |  |  |  |  |  |

| 22       | 29       | settable            | CAN1_SCE               | CAN1_SCE interrupt                            | 0x0000 0098 |  |  |  |  |  |  |  |

| 23       | 30       | settable            | EXTI9_5                | EXTI Line[9:5] interrupts                     | 0x0000 009C |  |  |  |  |  |  |  |

| 24       | 31       | settable            | TIM1_BRK/TIM15         | TIM1 Break/TIM15 global interrupts            | 0x0000 00A0 |  |  |  |  |  |  |  |

| 25       | 32       | settable            | TIM1_UP/TIM16          | TIM1 Update/TIM16 global interrupts           | 0x0000 00A4 |  |  |  |  |  |  |  |

| 26       | 33       | settable            | TIM1_TRG_COM<br>/TIM17 | TIM1 trigger and commutation/TIM17 interrupts | 0x0000 00A8 |  |  |  |  |  |  |  |

| 27       | 34       | settable            | TIM1_CC                | TIM1 capture compare interrupt                | 0x0000 00AC |  |  |  |  |  |  |  |

| 28       | 35       | settable            | TIM2                   | TIM2 global interrupt                         | 0x0000 00B0 |  |  |  |  |  |  |  |

| 29       | 36       | settable            | TIM3                   | TIM3 global interrupt                         | 0x0000 00B4 |  |  |  |  |  |  |  |

| 30       | 37       | settable            | TIM4                   | TIM4 global interrupt                         | 0x0000 00B8 |  |  |  |  |  |  |  |

| 31       | 38       | settable            | I2C1_EV                | I2C1 event interrupt                          | 0x0000 00BC |  |  |  |  |  |  |  |

| 32       | 39       | settable            | I2C1_ER                | I2C1 error interrupt                          | 0x0000 00C0 |  |  |  |  |  |  |  |

| 33       | 40       | settable            | I2C2_EV                | I2C2 event interrupt                          | 0x0000 00C4 |  |  |  |  |  |  |  |

| 34       | 41       | settable            | I2C2_ER                | I2C2 error interrupt                          | 0x0000 00C8 |  |  |  |  |  |  |  |

| 35       | 42       | settable            | SPI1                   | SPI1 global interrupt                         | 0x0000 00CC |  |  |  |  |  |  |  |

| 36       | 43       | settable            | SPI2                   | SPI2 global interrupt                         | 0x0000 00D0 |  |  |  |  |  |  |  |

| 37       | 44       | settable            | USART1                 | USART1 global interrupt                       | 0x0000 00D4 |  |  |  |  |  |  |  |

| 38       | 45       | settable            | USART2                 | USART2 global interrupt                       | 0x0000 00D8 |  |  |  |  |  |  |  |

| 39       | 46       | settable            | USART3                 | USART3 global interrupt                       | 0x0000 00DC |  |  |  |  |  |  |  |

| 40       | 47       | settable            | EXTI15_10              | EXTI Line[15:10] interrupts                   | 0x0000 00E0 |  |  |  |  |  |  |  |

| 41       | 48       | settable            | RTC_ALARM              | RTC alarms through EXTI line 18 interrupts    | 0x0000 00E4 |  |  |  |  |  |  |  |

| 42       | 49       | settable            | DFSDM1_FLT3            | DFSDM1_FLT3 global interrupt                  | 0x0000 00E8 |  |  |  |  |  |  |  |

| 43       | 50       | settable            | TIM8_BRK               | TIM8 Break interrupt                          | 0x0000 00EC |  |  |  |  |  |  |  |

|          |          |                     |                        |                                               |             |  |  |  |  |  |  |  |

| Table 57. STM32L4x5/STM32L4x6 vector table (contin |

|----------------------------------------------------|

|----------------------------------------------------|

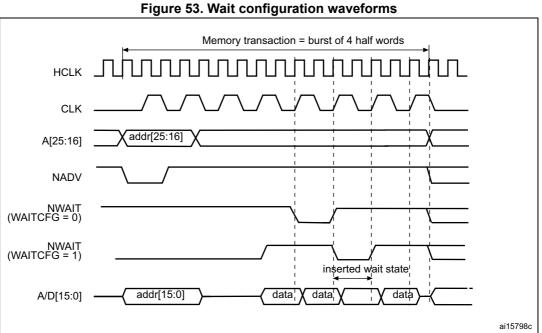

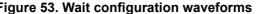

#### Figure 55. Synchronous multiplexed write mode waveforms - PSRAM (CRAM)

1. The memory must issue NWAIT signal one cycle in advance, accordingly WAITCFG must be programmed to 0.

2. Byte Lane (NBL) outputs are not shown, they are held low while NEx is active.

#### Table 90. FMC\_BCRx bit fields

| Bit number | Bit name  | Value to set                                                         |

|------------|-----------|----------------------------------------------------------------------|

| 31-22      | Reserved  | 0x000                                                                |

| 21         | WFDIS     | As needed (this bit is reserved for STM32L475xx/476xx/486xx devices) |

| 20         | CCLKEN    | As needed                                                            |

| 19         | CBURSTRW  | 0x1                                                                  |

| 18:16      | CPSIZE    | As needed (0x1 for CRAM 1.5)                                         |

| 15         | ASYNCWAIT | 0x0                                                                  |

| 14         | EXTMOD    | 0x0                                                                  |

# 16.7 FMC register map

|        |             |      |      |      |          |      |      |      |      |      |      |                      |        | 1        |     | T            |          |           |        |        |      |         |      |         |         | 1    |        |     |            |             |      |        |

|--------|-------------|------|------|------|----------|------|------|------|------|------|------|----------------------|--------|----------|-----|--------------|----------|-----------|--------|--------|------|---------|------|---------|---------|------|--------|-----|------------|-------------|------|--------|

| Offset | Register    | 31   | 30   | 29   | 28       | 27   | 26   | 25   | 24   | 23   | 22   | 21                   | 20     | 19       | 18  | 17           | 16       | 15        | 14     | 13     | 12   | 11      | 10   | 6       | 8       | 2    | 9      | 2   | 4          | 3           |      | - 0    |

| 0x00   | FMC_BCR1    | Res. | Res. | Res. | Res.     | Res. | Res. | Res. | Res. | Res. | Res. | WFDIS <sup>(1)</sup> | CCLKEN | CBURSTRW |     | 2951<br>[2:0 | ZE<br>)] | ASYNCWAIT | EXTMOD | WAITEN | WREN | WAITCFG | Res. | WAITPOL | BURSTEN | Res. | FACCEN |     | VID<br>:0] | MT\<br>[1:( |      | MBKEN  |

|        | Reset value |      |      |      |          |      |      |      |      |      |      | 0                    | 0      | 0        | 0   | 0            |          | 0         | 0      | 1      | 1    | 0       |      | 0       | 0       |      | 1      | 0   | 1          | 1           | 0    | 1 1    |

| 0x08   | FMC_BCR2    | Res. | Res. | Res. | Res.     | Res. | Res. | Res. | Res. | Res. | Res. | Res.                 | Res.   | CBURSTRW |     | 2PSI<br>[2:0 | ZE<br>)] | ASYNCWAIT | EXTMOD | WAITEN | WREN | WAITCFG | Res. | WAITPOL | BURSTEN | Res. | FACCEN |     | WID<br>:0] | MT\<br>[1:( |      | MBKEN  |

|        | Reset value |      |      |      |          |      |      |      |      |      |      |                      |        | 0        | 0   | 0            |          | 0         | 0      | 1      | 1    | 0       |      | 0       | 0       |      | 1      | 0   | 1          | 0           | 0    | 1 0    |

| 0x10   | FMC_BCR3    | Res. | Res. | Res. | Res.     | Res. | Res. | Res. | Res. | Res. | Res. | Res.                 | Res.   | CBURSTRW |     | 2PSI<br>[2:0 |          | ASYNCWAIT | EXTMOD | WAITEN | WREN | WAITCFG | Res. | WAITPOL | BURSTEN | Res. | FACCEN |     | VID<br>:0] | MT\<br>[1:( | )] 2 | MBKEN  |

|        | Reset value |      |      |      |          |      |      |      |      |      |      |                      |        | 0        | 0   | 0            | 0        | 0         | 0      | 1      | 1    | 0       |      | 0       | 0       |      | 1      | 0   | 1          | 0           | 0    | 1 0    |

| 0x18   | FMC_BCR4    | Res. | Res. | Res. | Res.     | Res. | Res. | Res. | Res. | Res. | Res. | Res.                 | Res.   | CBURSTRW |     | 2PSI<br>[2:0 | ZE<br>)] | ASYNCWAIT | EXTMOD | WAITEN | WREN | WAITCFG | Res. | WAITPOL | BURSTEN | Res. | FACCEN |     | VID<br>:0] | MT\<br>[1:( | (P)] | MBKEN  |

|        | Reset value |      |      |      |          |      |      |      |      |      |      |                      |        | 0        | 0   | 0            | 0        | 0         | 0      | 1      | 1    | 0       |      | 0       | 0       |      | 1      | 0   | 1          | 0           | 0    | 1 0    |

| 0x04   | FMC_BTR1    | Res. | Res. |      | <u> </u> |      | ATL/ | -    | -    |      |      | IV[3                 | -      |          | •   |              | [3:0]    |           |        |        | TAS  |         |      |         |         |      | DDH    | T   |            |             |      | T[3:0] |

|        | Reset value |      |      | 0    | 0        | 1    | 1    | 1    | 1    | 1    | 1    | 1                    | 1      | 1        | 1   | 1            | 1        | 1         | 1      | 1      | 1    | 1       | 1    | 1       | 1       | 1    | 1      | 1   | 1          | 1           | 1    | 1 1    |

| 0x0C   | FMC_BTR2    | Res. | Res. |      |          | DA   | ΑTL/ | AT[3 | 3:0] | CL   | .KD  | IV[3                 | 8:0]   | BU       | STL | JRN          | [3:0]    |           |        | DA     | TAS  | ST[7    | ':0] |         |         | AE   | DDH    | LD[ | 3:0]       | ADI         | DSE  | T[3:0] |

|        | Reset value |      |      | 0    | 0        | 1    | 1    | 1    | 1    | 1    | 1    | 1                    | 1      | 1        | 1   | 1            | 1        | 1         | 1      | 1      | 1    | 1       | 1    | 1       | 1       | 1    | 1      | 1   | 1          | 1           | 1    | 1 1    |

| 0x14   | FMC_BTR3    | Res. | Res. |      |          | DA   | ATL/ | AT[3 | 8:0] | CL   | .KD  | IV[3                 | 8:0]   | BU       | STL | JRN          | [3:0]    |           |        | DA     | TAS  | ST[7    | :0]  |         |         | AC   | DDH    | LD[ | 3:0]       | ADI         | DSE  | T[3:0] |

|        | Reset value |      |      | 0    | 0        | 1    | 1    | 1    | 1    | 1    | 1    | 1                    | 1      | 1        | 1   | 1            | 1        | 1         | 1      | 1      | 1    | 1       | 1    | 1       | 1       | 1    | 1      | 1   | 1          | 1           | 1    | 1 1    |

| 0x1C   | FMC_BTR4    | Res. | Res. |      |          | DA   | ATL/ | AT[3 | 8:0] | CL   | .KD  | IV[3                 | 8:0]   | BU       | STL | JRN          | [3:0]    |           |        | DA     | TAS  | ST[7    | ':0] |         |         | AD   | DDH    | LD[ | 3:0]       | ADI         | DSE  | T[3:0] |

|        | Reset value |      |      | 0    | 0        | 1    | 1    | 1    | 1    | 1    | 1    | 1                    | 1      | 1        | 1   | 1            | 1        | 1         | 1      | 1      | 1    | 1       | 1    | 1       | 1       | 1    | 1      | 1   | 1          | 1           | 1    | 1 1    |

| 0x104  | FMC_BWTR1   | Res. | Res. |      |          | Res. | Res. | Res. | Res. | Res. |      | Res.                 | Res.   | BU       | STL | JRN          | [3:0]    |           |        | DA     | TAS  | ST[7    | ':0] |         |         | AD   | DDH    | LD[ | 3:0]       | ADI         | DSE  | T[3:0] |

|        | Reset value |      |      | 0    | 0        |      |      |      |      |      |      |                      |        | 1        | 1   | 1            | 1        | 1         | 1      | 1      | 1    | 1       | 1    | 1       | 1       | 1    | 1      | 1   | 1          | 1           | 1    | 1 1    |

| 0x10C  | FMC_BWTR2   | Res. | Res. |      |          | Res.                 | Res.   | BU       | STL | JRN          | [3:0]    |           |        | DA     | TAS  | ST[7    | ':0] |         |         | AD   | DDH    | LD[ | 3:0]       | ADI         | DSE  | T[3:0] |

|        | Reset value |      |      | 0    | 0        |      |      |      |      |      |      |                      |        | 1        | 1   | 1            | 1        | 1         | 1      | 1      | 1    | 1       | 1    | 1       | 1       | 1    | 1      | 1   | 1          | 1           | 1    | 1 1    |

# Table 97. FMC register map

| RM0351 |

|--------|

|        |

|        |                 |      |      |      |      |      |      |      |      | • •  |      |      | - 9  |      |              |      | - F 1 |      |      |      |      | 7    |      |      |      |      |       |          |            |      |       |         |      |

|--------|-----------------|------|------|------|------|------|------|------|------|------|------|------|------|------|--------------|------|-------|------|------|------|------|------|------|------|------|------|-------|----------|------------|------|-------|---------|------|

| Offset | Register        | 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   | 23   | 22   | 21   | 20   | 19   | 18           | 17   | 16    | 15   | 14   | 13   | 12   | 11   | 10   | 6    | 8    | 7    | 9     | 5        | 4          | 3    | 2     | 1       | 0    |

| 0x114  | FMC_BWTR3       | Res. | Res. |      |      | Res. | BUS  | STU          | RN[  | [3:0] |      |      | DA   | TAS  | 6T[7 | ':0] |      |      | AD   | DH    | LD[:     | 3:0]       | A    | DDS   | ET[3    | :0]  |

|        | Reset value     |      |      | 0    | 0    |      |      |      |      |      |      |      |      | 1    | 1            | 1    | 1     | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1     | 1        | 1          | 1    | 1     | 1       | 1    |

| 0x11C  | FMC_BWTR4       | Res. | Res. |      |      | Res. | BUS  | STU          | RN[  | [3:0] |      |      | DA   | TAS  | ST[7 | ':0] |      |      | AD   | DH    | LD[3     | 3:0]       | AE   | DDS   | ET[3    | :0]  |

|        | Reset value     |      |      | 0    | 0    |      |      |      |      |      |      |      |      | 1    | 1            | 1    | 1     | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1     | 1        | 1          | 1    | 1     | 1       | 1    |

| 0x80   | FMC_PCR         | Res. |      | CCF<br>[2:0] |      | -     | TAR  | [3:0 | ]    | Т    | CLF  | २[3: | 0]   | Res. | Res. | ECCEN | PV<br>[1 | VID<br>:0] | РТҮР | PBKEN | PWAITEN | Res. |

|        | Reset value     |      |      |      |      |      |      |      |      |      |      |      |      | 0    | 0            | 0    | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |      | 0     | 0        | 1          | 1    | 0     | 0       |      |

| 0x84   | FMC_SR          | Res.         | Res. | Res.  | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | Res. | FEMPT | IFEN     | ILEN       | IREN | IFS   | ILS     | IRS  |

|        | Reset value     |      |      |      |      |      |      |      |      |      |      |      |      |      |              |      |       |      |      |      |      |      |      |      |      |      | 1     | 0        | 0          | 0    | 0     | 0       | 0    |

| 0x88   | FMC_PMEM        |      |      | ME   | MH   | Zx[  | 7:0] |      |      |      | I    | MEN  | но   | LDx  | [7:0         | ]    |       |      |      | MEN  | 1WA  | ١Tx  | [7:0 | ]    |      |      |       | ME       | MSE        | ΞTx  | [7:0] |         |      |

| 0,000  | Reset value     | 1    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1            | 0    | 0     | 1    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 1    | 1     | 1        | 1          | 1    | 1     | 0       | 0    |

| 0x8C   | FMC_PATT        |      | ı    | A    | ГТН  | Z[7  | :0]  |      |      |      |      | AT   | ГНО  | LD[  | 7:0]         |      |       |      |      | AT   | ΓWA  | NT[  | 7:0] |      | •    |      |       | AT       | TSE        | ET[7 | 7:0]  |         |      |

| UXOC   | Reset value     | 1    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1            | 0    | 0     | 1    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 1    | 1     | 1        | 1          | 1    | 1     | 0       | 0    |

| 0x94   | FMC_ECCR        |      | •    | •    |      | •    | •    |      |      |      |      |      |      |      |              | Е    | CC×   | (31  | [0]  |      |      |      | •    | •    |      |      | •     |          |            | •    |       |         |      |

| 0794   | Reset value     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0            | 0    | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     | 0        | 0          | 0    | 0     | 0       | 0    |

| 1 Thie | hit is reserved | for  | ет   | N124 | 01.4 | 75.  | ×/4  | 76   | ~//  | 06.  | vd   |      |      |      |              |      |       | -    |      |      |      |      | -    |      |      |      |       |          |            |      | •     |         |      |

### Table 97. FMC register map (continued)

1. This bit is reserved for STM32L475xx/476xx/486xx devices.

Refer to Section 2.2.2 on page 75 for the register boundary addresses.

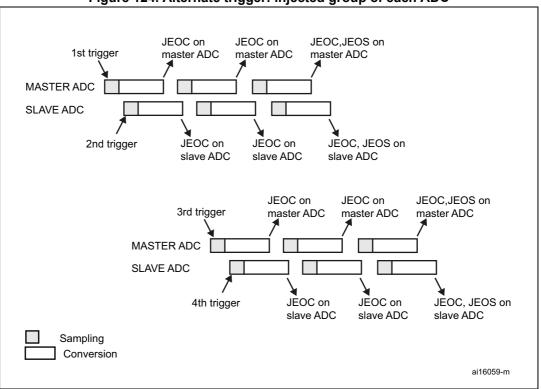

#### Figure 124. Alternate trigger: injected group of each ADC

Note:

Regular conversions can be enabled on one or all ADCs. In this case the regular conversions are independent of each other. A regular conversion is interrupted when the ADC has to perform an injected conversion. It is resumed when the injected conversion is finished.

The time interval between 2 trigger events must be greater than or equal to 1 ADC clock period. The minimum time interval between 2 trigger events that start conversions on the same ADC is the same as in the single ADC mode.

#### Injected discontinuous mode enabled (JDISCEN=1 for both ADC)

If the injected discontinuous mode is enabled for both master and slave ADCs:

- When the 1st trigger occurs, the first injected channel of the master ADC is converted.

- When the 2nd trigger occurs, the first injected channel of the slave ADC is converted.

- And so on.

A JEOS interrupt, if enabled, is generated after all injected channels of the master ADC in the group have been converted.

A JEOS interrupt, if enabled, is generated after all injected channels of the slave ADC in the group have been converted.

JEOC interrupts, if enabled, can also be generated after each injected conversions.

If another external trigger occurs after all injected channels in the group have been converted then the alternate trigger process restarts.

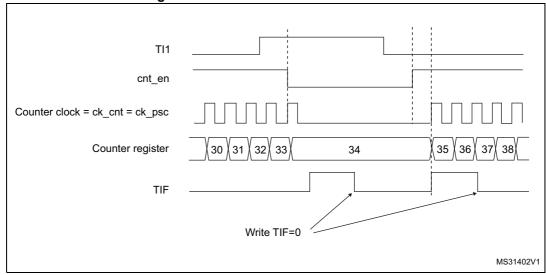

#### Slave mode: Gated mode

The counter can be enabled depending on the level of a selected input.

In the following example, the upcounter counts only when TI1 input is low:

- Configure the channel 1 to detect low levels on TI1. Configure the input filter duration (in this example, we don't need any filter, so we keep IC1F=0000). The capture prescaler is not used for triggering, so you don't need to configure it. The CC1S bits select the input capture source only, CC1S=01 in TIMx\_CCMR1 register. Write CC1P=1 and CC1NP='0' in TIMx\_CCER register to validate the polarity (and detect low level only).

- Configure the timer in gated mode by writing SMS=101 in TIMx\_SMCR register. Select TI1 as the input source by writing TS=101 in TIMx\_SMCR register.

- Enable the counter by writing CEN=1 in the TIMx\_CR1 register (in gated mode, the counter doesn't start if CEN=0, whatever is the trigger input level).

The counter starts counting on the internal clock as long as TI1 is low and stops as soon as TI1 becomes high. The TIF flag in the TIMx\_SR register is set both when the counter starts or stops.

The delay between the rising edge on TI1 and the actual stop of the counter is due to the resynchronization circuit on TI1 input.

Figure 269. Control circuit in Gated mode

# Slave mode: Trigger mode

The counter can start in response to an event on a selected input.

In the following example, the upcounter starts in response to a rising edge on TI2 input:

Configure the channel 2 to detect rising edges on TI2. Configure the input filter duration (in this example, we don't need any filter, so we keep IC2F=0000). The capture prescaler is not used for triggering, so you don't need to configure it. The CC2S bits are configured to select the input capture source only, CC2S=01 in TIMx\_CCMR1 register.

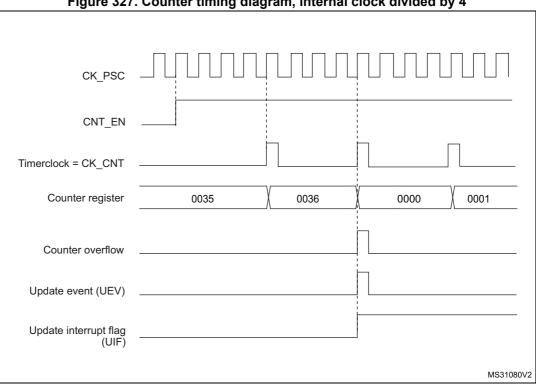

Figure 327. Counter timing diagram, internal clock divided by 4

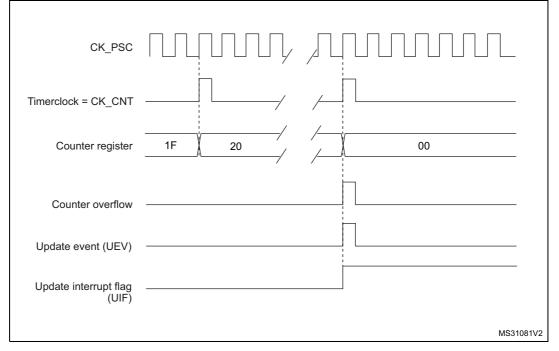

Figure 328. Counter timing diagram, internal clock divided by N

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| Res. | OR_1 | OR_0 |

|      |      |      |      |      |      |      |      |      |      |      |      |      |      | rw   | rw   |

Bits 31:2 Reserved, must be kept at reset value.

- Bit 1 **OR\_1**: Option register bit 1

- 0: LPTIM2 input 1 is connected to I/O

- 1: LPTIM2 input 1 is connected to COMP2\_OUT

- Bit 0 **OR\_0**: Option register bit 0

- 0: LPTIM2 input 1 is connected to I/O

- 1: LPTIM2 input 1 is connected to COMP1\_OUT

- *Note:* When both OR\_1 and OR\_0 are set, LPTIM2 input 1 is connected to (COMP1\_OUT OR COMP2\_OUT).

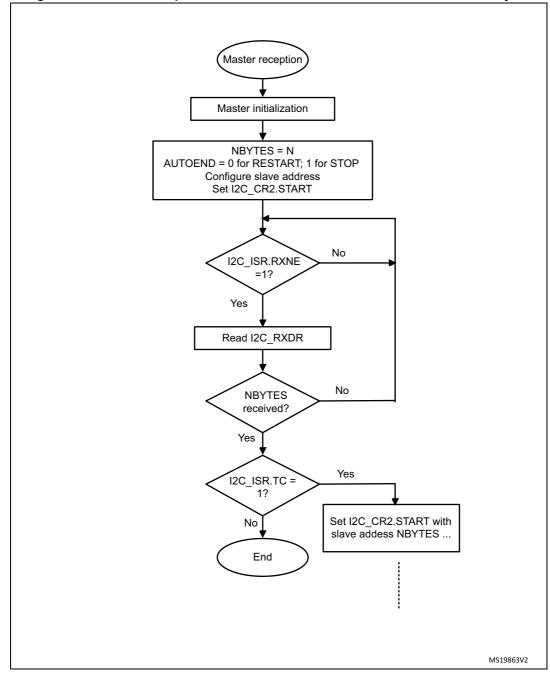

Figure 395. Transfer sequence flowchart for I2C master receiver for N≤255 bytes

#### Specific address (Slave mode)

The specific SMBus addresses should be enabled if needed. Refer to *Bus idle detection on page 1269* for more details.

- The SMBus Device Default address (0b1100 001) is enabled by setting the SMBDEN bit in the I2C\_CR1 register.

- The SMBus Host address (0b0001 000) is enabled by setting the SMBHEN bit in the I2C\_CR1 register.

- The Alert Response Address (0b0001100) is enabled by setting the ALERTEN bit in the I2C\_CR1 register.

#### Packet error checking

PEC calculation is enabled by setting the PECEN bit in the I2C\_CR1 register. Then the PEC transfer is managed with the help of a hardware byte counter: NBYTES[7:0] in the I2C\_CR2 register. The PECEN bit must be configured before enabling the I2C.

The PEC transfer is managed with the hardware byte counter, so the SBC bit must be set when interfacing the SMBus in slave mode. The PEC is transferred after NBYTES-1 data have been transferred when the PECBYTE bit is set and the RELOAD bit is cleared. If RELOAD is set, PECBYTE has no effect.

**Caution:** Changing the PECEN configuration is not allowed when the I2C is enabled.

|                                     |         | -          |             |             |

|-------------------------------------|---------|------------|-------------|-------------|

| Mode                                | SBC bit | RELOAD bit | AUTOEND bit | PECBYTE bit |

| Master Tx/Rx NBYTES + PEC+ STOP     | х       | 0          | 1           | 1           |

| Master Tx/Rx NBYTES + PEC + ReSTART | х       | 0          | 0           | 1           |

| Slave Tx/Rx with PEC                | 1       | 0          | х           | 1           |

Table 225. SMBUS with PEC configuration

#### Timeout detection

The timeout detection is enabled by setting the TIMOUTEN and TEXTEN bits in the I2C\_TIMEOUTR register. The timers must be programmed in such a way that they detect a timeout before the maximum time given in the SMBus specification version 2.0.

t<sub>TIMEOUT</sub> check

In order to enable the  $t_{TIMEOUT}$  check, the 12-bit TIMEOUTA[11:0] bits must be programmed with the timer reload value in order to check the  $t_{TIMEOUT}$  parameter. The TIDLE bit must be configured to '0' in order to detect the SCL low level timeout.

Then the timer is enabled by setting the TIMOUTEN in the I2C\_TIMEOUTR register. If SCL is tied low for a time greater than (TIMEOUTA+1) x 2048 x  $t_{I2CCLK}$ , the TIMEOUT flag is set in the I2C\_ISR register.

Refer to Table 226: Examples of TIMEOUTA settings for various I2CCLK frequencies (max tTIMEOUT = 25 ms).

- **Caution:** Changing the TIMEOUTA[11:0] bits and TIDLE bit configuration is not allowed when the TIMEOUTEN bit is set.

- t<sub>LOW:SEXT</sub> and t<sub>LOW:MEXT</sub> check

Depending on if the peripheral is configured as a master or as a slave, The 12-bit TIMEOUTB timer must be configured in order to check t<sub>LOW:SEXT</sub> for a slave and

# 41.7 LPUART registers

Refer to Section 1.1 on page 67 for a list of abbreviations used in register descriptions.

# 41.7.1 Control register 1 (LPUART\_CR1)

#### Address offset: 0x00

Reset value: 0x0000

| 31   | 30   | 29   | 28 | 27   | 26   | 25 | 24   | 23       | 22   | 21     | 20     | 19 | 18       | 17   | 16 |

|------|------|------|----|------|------|----|------|----------|------|--------|--------|----|----------|------|----|

| Res. | Res. | Res. | M1 | Res. | Res. |    |      | DEAT[4:0 | ]    |        |        | [  | DEDT[4:0 | ]    |    |

|      |      |      | rw |      |      | rw | rw   | rw       | rw   | rw     | rw     | rw | rw       | rw   | rw |

| 15   | 14   | 13   | 12 | 11   | 10   | 9  | 8    | 7        | 6    | 5      | 4      | 3  | 2        | 1    | 0  |

| Res. | CMIE | MME  | M0 | WAKE | PCE  | PS | PEIE | TXEIE    | TCIE | RXNEIE | IDLEIE | TE | RE       | UESM | UE |

|      | rw   | rw   | rw | rw   | rw   | rw | rw   | rw       | rw   | rw     | rw     | rw | rw       | rw   | rw |

Bits 31:29 Reserved, must be kept at reset value

Bit 28 M1: Word length

This bit, with bit 12 (M0) determines the word length. It is set or cleared by software.

M[1:0] = 00: 1 Start bit, 8 data bits, n stop bits

M[1:0] = 01: 1 Start bit, 9 data bits, n stop bits

M[1:0] = 10: 1 Start bit, 7 data bits, n stop bits

This bit can only be written when the LPUART is disabled (UE=0).

- Note: In 7-bit data length mode, the Smartcard mode, LIN master mode and Auto baud rate (0x7F and 0x55 frames detection) are not supported.

- Bit 27 Reserved, must be kept at reset value

- Bit 26 Reserved, must be kept at reset value

- Bits 25:21 DEAT[4:0]: Driver Enable assertion time

This 5-bit value defines the time between the activation of the DE (Driver Enable) signal and the beginning of the start bit. It is expressed in UCLK (USART clock) clock cycles. For more details, refer to RS485 Driver Enable paragraph.

This bit field can only be written when the LPUART is disabled (UE=0).

#### Bits 20:16 DEDT[4:0]: Driver Enable de-assertion time

This 5-bit value defines the time between the end of the last stop bit, in a transmitted message, and the de-activation of the DE (Driver Enable) signal. It is expressed in UCLK (USART clock) clock cycles. For more details, refer to RS485 Driver Enable paragraph. If the LPUART\_TDR register is written during the DEDT time, the new data is transmitted only when the DEDT and DEAT times have both elapsed.

This bit field can only be written when the LPUART is disabled (UE=0).

- Bit 15 Reserved, must be kept at reset value

- Bit 14 CMIE: Character match interrupt enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: A LPUART interrupt is generated when the CMF bit is set in the LPUART\_ISR register.

Bit 4 **TRIS**: Tristate management on data line.

This bit is set and cleared by software. It is meaningful only if the audio block is configured as a transmitter. This bit is not used when the audio block is configured in SPDIF mode. It should be configured when SAI is disabled.

Refer to Section : Output data line management on an inactive slot for more details.

0: SD output line is still driven by the SAI when a slot is inactive.

1: SD output line is released (HI-Z) at the end of the last data bit of the last active slot if the next one is inactive.

Bit 3 FFLUSH: FIFO flush.

This bit is set by software. It is always read as 0. This bit should be configured when the SAI is disabled.

0: No FIFO flush.

1: FIFO flush. Programming this bit to 1 triggers the FIFO Flush. All the internal FIFO pointers (read and write) are cleared. In this case data still present in the FIFO are lost (no more transmission or received data lost). Before flushing, SAI DMA stream/interruption must be disabled

Bits 2:0 FTH: FIFO threshold.

This bit is set and cleared by software. 000: FIFO empty 001: ¼ FIFO 010: ½ FIFO 011: ¾ FIFO 100: FIFO full 101: Reserved 110: Reserved 111: Reserved

### 43.5.4 Frame configuration register (SAI\_AFRCR / SAI\_BFRCR)

Address offset: Block A: 0x00C

Address offset: Block B: 0x02C

Reset value: 0x0000 0007

Note: This register has no meaning in AC'97 and SPDIF audio protocol

| 31   | 30         | 29   | 28   | 27   | 26   | 25       | 24   | 23   | 22   | 21   | 20   | 19   | 18    | 17    | 16    |

|------|------------|------|------|------|------|----------|------|------|------|------|------|------|-------|-------|-------|

| Res. | Res.       | Res. | Res. | Res. | Res. | Res.     | Res. | Res. | Res. | Res. | Res. | Res. | FSOFF | FSPOL | FSDEF |

|      |            |      |      |      |      |          |      |      |      |      |      |      | rw    | rw    | r     |

| 15   | 14         | 13   | 12   | 11   | 10   | 9        | 8    | 7    | 6    | 5    | 4    | 3    | 2     | 1     | 0     |

| Res. | FSALL[6:0] |      |      |      |      | FRL[7:0] |      |      |      |      |      |      |       |       |       |

|      | rw         | rw   | rw   | rw   | rw   | rw       | rw   | rw   | rw   | rw   | rw   | rw   | rw    | rw    | rw    |

#### RM0351

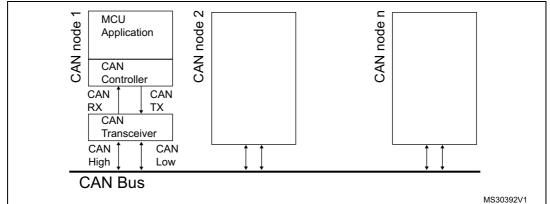

# 46.3 bxCAN general description

In today's CAN applications, the number of nodes in a network is increasing and often several networks are linked together via gateways. Typically the number of messages in the system (and thus to be handled by each node) has significantly increased. In addition to the application messages, Network Management and Diagnostic messages have been introduced.

• An enhanced filtering mechanism is required to handle each type of message.

Furthermore, application tasks require more CPU time, therefore real-time constraints caused by message reception have to be reduced.

A receive FIFO scheme allows the CPU to be dedicated to application tasks for a long time period without losing messages.

The standard HLP (Higher Layer Protocol) based on standard CAN drivers requires an efficient interface to the CAN controller.

Figure 501. CAN network topology

# 46.3.1 CAN 2.0B active core

The bxCAN module handles the transmission and the reception of CAN messages fully autonomously. Standard identifiers (11-bit) and extended identifiers (29-bit) are fully supported by hardware.

# 46.3.2 Control, status and configuration registers

The application uses these registers to:

- Configure CAN parameters, e.g. baud rate

- Request transmissions

- Handle receptions

- Manage interrupts

- Get diagnostic information

#### 46.3.3 Tx mailboxes

Three transmit mailboxes are provided to the software for setting up messages. The transmission Scheduler decides which mailbox has to be transmitted first.

DocID024597 Rev 5

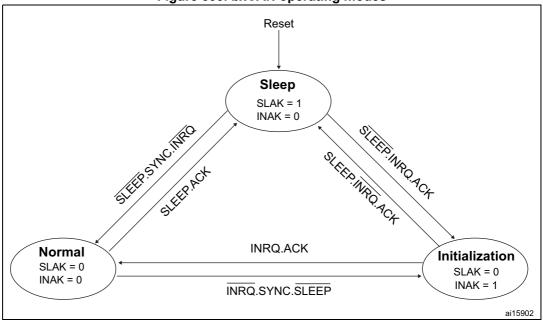

this mode, the bxCAN clock is stopped, however software can still access the bxCAN mailboxes.

If software requests entry to **initialization** mode by setting the INRQ bit while bxCAN is in **Sleep** mode, it must also clear the SLEEP bit.

bxCAN can be woken up (exit Sleep mode) either by software clearing the SLEEP bit or on detection of CAN bus activity.

On CAN bus activity detection, hardware automatically performs the wakeup sequence by clearing the SLEEP bit if the AWUM bit in the CAN\_MCR register is set. If the AWUM bit is cleared, software has to clear the SLEEP bit when a wakeup interrupt occurs, in order to exit from Sleep mode.

Note: If the wakeup interrupt is enabled (WKUIE bit set in CAN\_IER register) a wakeup interrupt will be generated on detection of CAN bus activity, even if the bxCAN automatically performs the wakeup sequence.

After the SLEEP bit has been cleared, Sleep mode is exited once bxCAN has synchronized with the CAN bus, refer to *Figure 503: bxCAN operating modes*. The Sleep mode is exited once the SLAK bit has been cleared by hardware.

Figure 503. bxCAN operating modes

1. ACK = The wait state during which hardware confirms a request by setting the INAK or SLAK bits in the CAN\_MSR register

2. SYNC = The state during which bxCAN waits until the CAN bus is idle, meaning 11 consecutive recessive bits have been monitored on CANRX

# 46.5 Test mode

Test mode can be selected by the SILM and LBKM bits in the CAN\_BTR register. These bits must be configured while bxCAN is in Initialization mode. Once test mode has been selected, the INRQ bit in the CAN\_MCR register must be reset to enter Normal mode.

DocID024597 Rev 5

# 47.16 OTG\_FS programming model

### 47.16.1 Core initialization

The application must perform the core initialization sequence. If the cable is connected during power-up, the current mode of operation bit in the OTG\_GINTSTS (CMOD bit in OTG\_GINTSTS) reflects the mode. The OTG\_FS controller enters host mode when an "A" plug is connected or device mode when a "B" plug is connected.

This section explains the initialization of the OTG\_FS controller after power-on. The application must follow the initialization sequence irrespective of host or device mode operation. All core global registers are initialized according to the core's configuration:

- 1. Program the following fields in the OTG\_GAHBCFG register:

- Global interrupt mask bit GINTMSK = 1

- Rx FIFO non-empty (RXFLVL bit in OTG\_GINTSTS)

- Periodic Tx FIFO empty level

- 2. Program the following fields in the OTG\_GUSBCFG register:

- HNP capable bit

- SRP capable bit

- OTG\_FS timeout calibration field

- USB turnaround time field

- 3. The software must unmask the following bits in the OTG\_GINTMSK register: OTG interrupt mask

Mode mismatch interrupt mask

4. The software can read the CMOD bit in OTG\_GINTSTS to determine whether the OTG\_FS controller is operating in host or device mode.

# 47.16.2 Host initialization

To initialize the core as host, the application must perform the following steps:

- 1. Program the HPRTINT in the OTG\_GINTMSK register to unmask

- 2. Program the OTG\_HCFG register to select full-speed host

- 3. Program the PPWR bit in OTG\_HPRT to 1. This drives V<sub>BUS</sub> on the USB.

- 4. Wait for the PCDET interrupt in OTG\_HPRT0. This indicates that a device is connecting to the port.

- 5. Program the PRST bit in OTG\_HPRT to 1. This starts the reset process.

- 6. Wait at least 10 ms for the reset process to complete.

- 7. Program the PRST bit in OTG\_HPRT to 0.

- 8. Wait for the PENCHNG interrupt in OTG\_HPRT.

- 9. Read the PSPD bit in OTG\_HPRT to get the enumerated speed.

- 10. Program the HFIR register with a value corresponding to the selected PHY clock 1

- 11. Program the FSLSPCS field in the OTG\_HCFG register following the speed of the device detected in step 9. If FSLSPCS has been changed a port reset must be performed.

- 12. Program the OTG\_GRXFSIZ register to select the size of the receive FIFO.

- 13. Program the OTG\_HNPTXFSIZ register to select the size and the start address of the Non-periodic transmit FIFO for non-periodic transactions.

- 14. Program the OTG\_HPTXFSIZ register to select the size and start address of the periodic transmit FIFO for periodic transactions.

To communicate with devices, the system software must initialize and enable at least one channel.

# 47.16.3 Device initialization

The application must perform the following steps to initialize the core as a device on powerup or after a mode change from host to device.

- 1. Program the following fields in the OTG\_DCFG register:

- Device speed

- Non-zero-length status OUT handshake

- 2. Program the OTG\_GINTMSK register to unmask the following interrupts:

- USB reset

- Enumeration done

- Early suspend

- USB suspend

- SOF

- 3. Wait for the USBRST interrupt in OTG\_GINTSTS. It indicates that a reset has been detected on the USB that lasts for about 10 ms on receiving this interrupt.

Wait for the ENUMDNE interrupt in OTG\_GINTSTS. This interrupt indicates the end of reset on the USB. On receiving this interrupt, the application must read the OTG\_DSTS register to determine the enumeration speed and perform the steps listed in *Endpoint initialization on enumeration completion on page 1747*.

IDCODE read or CTRL/STAT read or ABORT write which are accepted even if the write buffer is full.

• Because of the asynchronous clock domains SWCLK and HCLK, two extra SWCLK cycles are needed after a write transaction (after the parity bit) to make the write effective internally. These cycles should be applied while driving the line low (IDLE state)

This is particularly important when writing the CTRL/STAT for a power-up request. If the next transaction (requiring a power-up) occurs immediately, it will fail.

### 48.8.5 SW-DP registers

Access to these registers are initiated when APnDP=0

| A(3:2) | R/W          | CTRLSEL bit<br>of SELECT<br>register | Register         | Notes                                                                                                                                                                                                                                                                               |  |  |  |  |

|--------|--------------|--------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 00     | Read         | -                                    | IDCODE           | The manufacturer code is not set to ST code <b>0x2BA01477</b> (identifies the SW-DP)                                                                                                                                                                                                |  |  |  |  |

| 00     | Write        | -                                    | ABORT            | -                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 01     | Read/Write   | 0                                    | DP-<br>CTRL/STAT | <ul> <li>Purpose is to:</li> <li>request a system or debug power-up</li> <li>configure the transfer operation for AP accesses</li> <li>control the pushed compare and pushed verify operations.</li> <li>read some status flags (overrun, power-up acknowledges)</li> </ul>         |  |  |  |  |

| 01     | Read/Write   | 1                                    | WIRE<br>CONTROL  | Purpose is to configure the physical serial port protocol (like the duration of the turnaround time)                                                                                                                                                                                |  |  |  |  |

| 10     | Read         | -                                    | READ<br>RESEND   | Enables recovery of the read data from a corrupted debugger transfer, without repeating the original AP transfer.                                                                                                                                                                   |  |  |  |  |

| 10     | Write        | -                                    | SELECT           | The purpose is to select the current access port and the active 4-words register window                                                                                                                                                                                             |  |  |  |  |

| 11     | Read/Write - |                                      | READ<br>BUFFER   | This read buffer is useful because AP<br>accesses are posted (the result of a read AP<br>request is available on the next AP<br>transaction).<br>This read buffer captures data from the AP,<br>presented as the result of a previous read,<br>without initiating a new transaction |  |  |  |  |

Table 317. SW-DP registers