#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | Н8/300Н                                                                    |

| Core Size                  | 16-Bit                                                                     |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I²C, SCI                                                                   |

| Peripherals                | PWM, WDT                                                                   |

| Number of I/O              | 79                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 5K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | A/D 16x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-BQFP                                                                   |

| Supplier Device Package    | 100-QFP (14x20)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36109fv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure B.13 | Port 5 Block Diagram (P55, P54, P53, P52, P51, P50)           |  |

|-------------|---------------------------------------------------------------|--|

| Figure B.14 | Port 7 Block Diagram (P77)                                    |  |

| Figure B.15 | Port 7 Block Diagram (P76)                                    |  |

| Figure B.16 | Port 7 Block Diagram (P75)                                    |  |

| Figure B.17 | Port 7 Block Diagram (P74)                                    |  |

| Figure B.18 | Port 7 Block Diagram (P72)                                    |  |

| Figure B.19 | Port 7 Block Diagram (P71)                                    |  |

| Figure B.20 | Port 7 Block Diagram (P70)                                    |  |

| Figure B.21 | Port 8 Block Diagram (P87, P86, P85)                          |  |

| Figure B.22 | Port C Block Diagram (PC3, PC2, PC1, PC0)                     |  |

| Figure B.23 | Port D Block Diagram (PD7, PD6, PD5, PD4, PD3, PD2, PD1, PD0) |  |

| Figure B.24 | Port E Block Diagram (PE7, PE6, PE5, PE4, PE3, PE2, PE1, PE0) |  |

| Figure B.25 | Port F Block Diagram (PF7, PF6, PF5, PF4, PF3, PF2, PF1, PF0) |  |

| Figure B.26 | Port G Block Diagram (PG7, PG6, PG5)                          |  |

| Figure B.27 | Port G Block Diagram (PG4, PG3, PG2, PG1, PG0)                |  |

| Figure B.28 | Port H Block Diagram (PH7, PH6, PH5, PH4)                     |  |

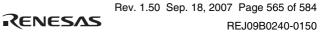

| Figure B.29 | Port H Block Diagram (PH3)                                    |  |

| Figure B.30 | Port H Block Diagram (PH2)                                    |  |

| Figure B.31 | Port H Block Diagram (PH1)                                    |  |

| Figure B.32 | Port H Block Diagram (PH0)                                    |  |

| Figure B.33 | Port J Block Diagram (PJ1)                                    |  |

| Figure B.34 | Port J Block Diagram (PJ0)                                    |  |

| Figure D.1  | FP-100A Package Dimensions                                    |  |

| Figure D.2  | FP-100U Package Dimensions                                    |  |

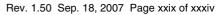

Figure 4.2 Address Break Interrupt Operation Example (2)

## 5.6 Subclock Generator

Figure 5.14 shows a block diagram of the subclock generator.

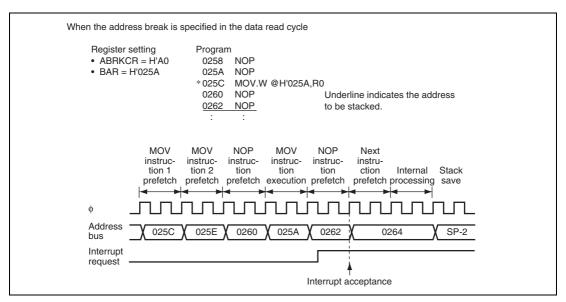

Figure 5.14 Block Diagram of Subclock Generator

### 5.6.1 Connecting 32.768-kHz Crystal Resonator

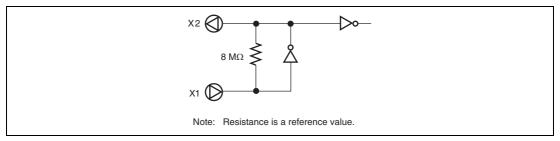

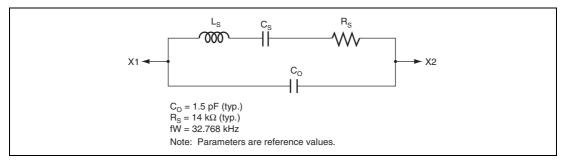

Clock pulses can be supplied to the subclock divider by connecting a 32.768-kHz crystal resonator, as shown in figure 5.15. Figure 5.16 shows the equivalent circuit of the 32.768-kHz crystal resonator.

Figure 5.15 Typical Connection to 32.768-kHz Crystal Resonator

Figure 5.16 Equivalent Circuit of 32.768-kHz Crystal Resonator

## Table 7.2 Boot Mode Operation

| Item                                                          | Host Operation                                                                                                                                                                                                                    |                                                                  | LSI Operation                                                                                                                                                                                                                     |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ite                                                           | Processing Contents                                                                                                                                                                                                               | Communication Contents                                           | Processing Contents                                                                                                                                                                                                               |

| Boot mode initiation                                          |                                                                                                                                                                                                                                   |                                                                  | Branches to boot program at reset-start.                                                                                                                                                                                          |

| Bit rate adjustment                                           | Continuously transmits data H'00<br>at specified bit rate.<br>Transmits data H'55 when data H'00<br>is received error-free                                                                                                        | H'00, H'00 ··· · H'00<br>H'00<br>H'55                            | <ul> <li>Measures low-level period of receive data<br/>H'00.</li> <li>Calculates bit rate and sets BRR in SCI3.</li> <li>Transmits data H'00 to host as adjustment<br/>end indication.</li> <li>H'55 reception</li> </ul>         |

| Flash memory erase                                            | Boot program -<br>erase error<br>H'AA reception                                                                                                                                                                                   | H'FF<br>H'AA                                                     | <ul> <li>Checks flash memory data, erases all flash memory blocks in case of written data existing, and transmits data H'AA to host. (If erasing could not be done, transmits data H'FF to host and aborts operation.)</li> </ul> |

| Transfer of number of bytes of<br>programming control program | Transmits number of bytes (N) of<br>programming control program to be<br>transferred as 2-byte data<br>(low-order byte following high-order<br>byte)<br>Transmits 1-byte of programming<br>control program (repeated for N times) | Upper bytes, lower bytes<br>Echoback<br>H'XX<br>Echoback<br>H'AA | <ul> <li>Echobacks the 2-byte data received to host.</li> <li>Echobacks received data to host and also transfers it to RAM. (repeated for N times)</li> <li>Transmits data H'AA to host.</li> </ul>                               |

|                                                               |                                                                                                                                                                                                                                   |                                                                  | Branches to programming control program transferred to on-chip RAM and starts execution.                                                                                                                                          |

#### 9.1.4 Port Pull-Up Control Register 1 (PUCR1)

Initial Bit **Bit Name** Value R/W Description 7 PUCR17 0 R/W Only bits for which PCR1 is cleared are valid. The pullup MOSs of P17 to P14 and P12 to P10 pins enter the PUCR16 R/W 6 0 on-state when these bits are set to 1, while they enter 5 PUCR15 0 R/W the off-state when these bits are cleared to 0. 4 PUCR14 0 R/W Bit 3 is a reserved bit. This bit is always read as 1. 3 1 2 PUCR12 0 R/W 1 PUCR11 0 R/W

PUCR1 controls the pull-up MOS in bit units of the pins set as the input ports.

R/W

#### 9.1.5 Pin Functions

PUCR10

0

0

The correspondence between the register specification and the port functions is shown below.

### • P17/IRQ3/TRGV pin

| Register      | PMR1 | PCR1  |                           |

|---------------|------|-------|---------------------------|

| Bit Name      | IRQ3 | PCR17 | Pin Function              |

| Setting value | 0    | 0     | P17 input pin             |

|               |      | 1     | P17 output pin            |

|               | 1    | Х     | IRQ3 input/TRGV input pin |

[Legend] X: Don't care.

• PE3/FTIOD2 pin

| Register         | TRDOER<br>1_23 | TRDFCR_23           |          | TRDPM<br>R_23 | TRDIOR<br>C_2   | PCRE      |                            |

|------------------|----------------|---------------------|----------|---------------|-----------------|-----------|----------------------------|

| Bit Name         | ED0            | CMD1<br>and<br>CMD0 | PWM<br>3 | PWMD0         | IOD3 to<br>IOD0 | PCRE<br>3 | Pin Function               |

| Setting<br>Value | 1              | XX                  | Х        | Х             | XXXX            | 0         | PE3 input/FTIOD2 input pin |

|                  |                |                     |          |               |                 | 1         | PE3 output pin             |

|                  | 0              | 00                  | 0        | Х             | XXXX            | 0         | PE3 input/FTIOD2 input pin |

|                  |                |                     |          |               |                 | 1         | PE3 output pin             |

|                  |                |                     | 1        | 1             | XXXX            | Х         | FTIOD2 output pin          |

|                  |                |                     |          | 0             | 0XXX            | 0         | PE3 input/FTIOD2 input pin |

|                  |                |                     |          |               |                 | 1         | PE3 output pin             |

|                  |                |                     |          |               | 101X or<br>1001 | Х         | FTIOD2 output pin          |

|                  |                |                     |          |               | 11XX or<br>1000 | 0         | PE3 input/FTIOD2 input pin |

|                  |                |                     |          |               |                 | 1         | PE3 output pin             |

|                  |                | Other than 00       | Х        | Х             | XXXX            | Х         | FTIOD2 output pin          |

| [Legend]         | X. Don't ca    |                     |          |               |                 |           |                            |

[Legend] X: Don't care.

Section 12 Timer V

|     |          | Initial |     |                                                                                              |

|-----|----------|---------|-----|----------------------------------------------------------------------------------------------|

| Bit | Bit Name | Value   | R/W | Description                                                                                  |

| 5   | OVF      | 0       | R/W | Timer Overflow Flag                                                                          |

|     |          |         |     | Setting condition:                                                                           |

|     |          |         |     | When TCNTV overflows from H'FF to H'00                                                       |

|     |          |         |     | Clearing condition:                                                                          |

| _   |          |         |     | After reading OVF = 1, cleared by writing 0 to OVF                                           |

| 4   | _        | 1       |     | Reserved                                                                                     |

|     |          |         |     | This bit is always read as 1.                                                                |

| 3   | OS3      | 0       | R/W | Output Select 3 and 2                                                                        |

| 2   | OS2      | 0       | R/W | These bits select an output method for the TOMV pin by the compare match of TCORB and TCNTV. |

|     |          |         |     | 00: No change                                                                                |

|     |          |         |     | 01: 0 output                                                                                 |

|     |          |         |     | 10: 1 output                                                                                 |

|     |          |         |     | 11: Output toggles                                                                           |

| 1   | OS1      | 0       | R/W | Output Select 1 and 0                                                                        |

| 0   | OS0      | 0       | R/W | These bits select an output method for the TOMV pin by the compare match of TCORA and TCNTV. |

|     |          |         |     | 00: No change                                                                                |

|     |          |         |     | 01: 0 output                                                                                 |

|     |          |         |     | 10: 1 output                                                                                 |

|     |          |         |     | 11: Output toggles                                                                           |

OS3 and OS2 select the output level for compare match B. OS1 and OS0 select the output level for compare match A. The two output levels can be controlled independently. After a reset, the timer output is 0 until the first compare match.

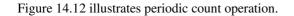

Figure 14.12 Periodic Counter Operation

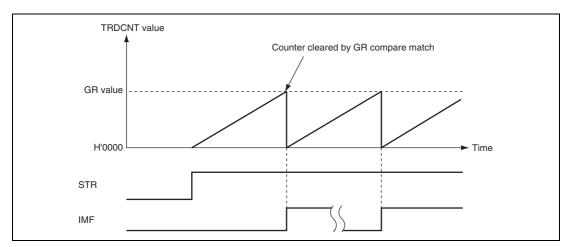

#### (2) TRDCNT Count Timing

• Internal clock operation

A system clock ( $\phi$ ), four types of clocks ( $\phi/2$ ,  $\phi/4$ ,  $\phi/8$ , or  $\phi/32$ ) that are generated by dividing the system clock, or on-chip oscillator clock ( $\phi40M$ ) can be selected by bits TPSC2 to TPSC0 in TRDCR.

Figure 14.13 illustrates this timing.

Figure 14.13 Count Timing at Internal Clock Operation

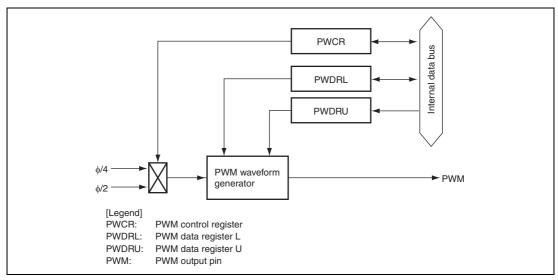

# Section 16 14-Bit PWM

The 14-bit PWM is a pulse division type PWM that can be used for electronic tuner control, etc. Figure 16.1 shows a block diagram of the 14-bit PWM.

## 16.1 Features

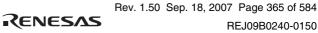

• Choice of two conversion periods

A conversion period of  $32768/\phi$  with a minimum modulation width of  $2/\phi$ , or a conversion period of  $16384/\phi$  with a minimum modulation width of  $1/\phi$ , can be selected.

• Pulse division method for less ripple

Figure 16.1 Block Diagram of 14-Bit PWM

## 16.2 Input/Output Pin

Table 16.1 shows the 14-bit PWM pin configuration.

#### Table 16.1 Pin Configuration

| Name                          | Abbreviation | I/O    | Function                          |  |  |  |  |

|-------------------------------|--------------|--------|-----------------------------------|--|--|--|--|

| 14-bit PWM square-wave output | PWM          | Output | 14-bit PWM square-wave output pin |  |  |  |  |

Figure 16.2 Waveform Output by 14-Bit PWM

|                     |   |     |              |   | Oper | ating i re   | quent | <i>γ</i> ψ (IVI | 112)         |   |     |              |

|---------------------|---|-----|--------------|---|------|--------------|-------|-----------------|--------------|---|-----|--------------|

|                     |   | 4   |              |   | 4.91 | 52           |       | 5               |              |   | 6   |              |

| Bit Rate<br>(bit/s) | n | N   | Error<br>(%) | n | N    | Error<br>(%) | n     | N               | Error<br>(%) | n | N   | Error<br>(%) |

| 110                 | 2 | 70  | 0.03         | 2 | 86   | 0.31         | 2     | 88              | -0.25        | 2 | 106 | -0.44        |

| 150                 | 1 | 207 | 0.16         | 1 | 255  | 0.00         | 2     | 64              | 0.16         | 2 | 77  | 0.16         |

| 300                 | 1 | 103 | 0.16         | 1 | 127  | 0.00         | 1     | 129             | 0.16         | 1 | 155 | 0.16         |

| 600                 | 0 | 207 | 0.16         | 0 | 255  | 0.00         | 1     | 64              | 0.16         | 1 | 77  | 0.16         |

| 1200                | 0 | 103 | 0.16         | 0 | 127  | 0.00         | 0     | 129             | 0.16         | 0 | 155 | 0.16         |

| 2400                | 0 | 51  | 0.16         | 0 | 63   | 0.00         | 0     | 64              | 0.16         | 0 | 77  | 0.16         |

| 4800                | 0 | 25  | 0.16         | 0 | 31   | 0.00         | 0     | 32              | -1.36        | 0 | 38  | 0.16         |

| 9600                | 0 | 12  | 0.16         | 0 | 15   | 0.00         | 0     | 15              | 1.73         | 0 | 19  | -2.34        |

| 19200               | 0 | 6   | -6.99        | 0 | 7    | 0.00         | 0     | 7               | 1.73         | 0 | 9   | -2.34        |

| 31250               | 0 | 3   | 0.00         | 0 | 4    | -1.70        | 0     | 4               | 0.00         | 0 | 5   | 0.00         |

| 38400               | 0 | 2   | 8.51         | 0 | 3    | 0.00         | 0     | 3               | 1.73         | 0 | 4   | -2.34        |

Table 17.3

Examples of BRR Settings for Various Bit Rates (Asynchronous Mode) (1)

Operating Frequency & (MHz)

#### Operating Frequency φ (MHz)

|                     |   |      |              |   |      | 5            |   |     | ,            |        |     |              |  |

|---------------------|---|------|--------------|---|------|--------------|---|-----|--------------|--------|-----|--------------|--|

|                     |   | 6.14 | 14           |   | 7.37 | 28           |   | 8   |              | 9.8304 |     |              |  |

| Bit Rate<br>(bit/s) | n | N    | Error<br>(%) | n | N    | Error<br>(%) | n | N   | Error<br>(%) | n      | N   | Error<br>(%) |  |

| 110                 | 2 | 108  | 0.08         | 2 | 130  | -0.07        | 2 | 141 | 0.03         | 2      | 174 | -0.26        |  |

| 150                 | 2 | 79   | 0.00         | 2 | 95   | 0.00         | 2 | 103 | 0.16         | 2      | 127 | 0.00         |  |

| 300                 | 1 | 159  | 0.00         | 1 | 191  | 0.00         | 1 | 207 | 0.16         | 1      | 255 | 0.00         |  |

| 600                 | 1 | 79   | 0.00         | 1 | 95   | 0.00         | 1 | 103 | 0.16         | 1      | 127 | 0.00         |  |

| 1200                | 0 | 159  | 0.00         | 0 | 191  | 0.00         | 0 | 207 | 0.16         | 0      | 255 | 0.00         |  |

| 2400                | 0 | 79   | 0.00         | 0 | 95   | 0.00         | 0 | 103 | 0.16         | 0      | 127 | 0.00         |  |

| 4800                | 0 | 39   | 0.00         | 0 | 47   | 0.00         | 0 | 51  | 0.16         | 0      | 63  | 0.00         |  |

| 9600                | 0 | 19   | 0.00         | 0 | 23   | 0.00         | 0 | 25  | 0.16         | 0      | 31  | 0.00         |  |

| 19200               | 0 | 9    | 0.00         | 0 | 11   | 0.00         | 0 | 12  | 0.16         | 0      | 15  | 0.00         |  |

| 31250               | 0 | 5    | 2.40         | 0 | 6    | 5.33         | 0 | 7   | 0.00         | 0      | 9   | -1.70        |  |

| 38400               | 0 | 4    | 0.00         | 0 | 5    | 0.00         | 0 | 6   | -6.99        | 0      | 7   | 0.00         |  |

| [Logond]            |   |      |              |   |      |              |   |     |              |        |     |              |  |

[Legend]

--: A setting is available but error occurs

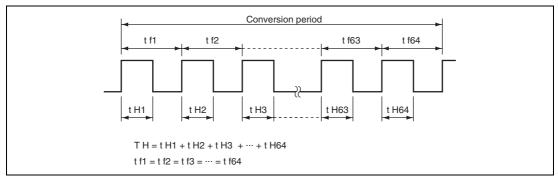

### 17.4.3 Data Transmission

Figure 17.5 shows an example of operation for transmission in asynchronous mode. In transmission, the SCI3 operates as described below.

- 1. The SCI3 monitors the TDRE flag in SSR. If the flag is cleared to 0, the SCI3 recognizes that data has been written to TDR, and transfers the data from TDR to TSR.

- 2. After transferring data from TDR to TSR, the SCI3 sets the TDRE flag to 1 and starts transmission. If the TIE bit is set to 1 at this time, a TXI interrupt request is generated. Continuous transmission is possible because the TXI interrupt routine writes next transmit data to TDR before transmission of the current transmit data has been completed.

- 3. The SCI3 checks the TDRE flag at the timing for sending the stop bit.

- 4. If the TDRE flag is 0, the data is transferred from TDR to TSR, the stop bit is sent, and then serial transmission of the next frame is started.

- 5. If the TDRE flag is 1, the TEND flag in SSR is set to 1, the stop bit is sent, and then the "mark state" is entered, in which 1 is output. If the TEIE bit in SCR3 is set to 1 at this time, a TEI interrupt request is generated.

- 6. Figure 17.6 shows a sample flowchart for transmission in asynchronous mode.

Figure 17.5 Example of SCI3 Transmission in Asynchronous Mode (8-Bit Data, Parity, One Stop Bit)

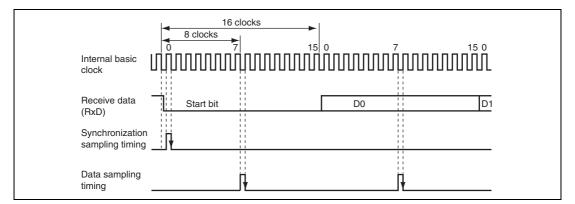

### 17.8.4 Receive Data Sampling Timing and Reception Margin in Asynchronous Mode

In asynchronous mode, the SCI3 operates on a basic clock with a frequency of 16 times the transfer rate. In reception, the SCI3 samples the falling edge of the start bit using the basic clock, and performs internal synchronization. Receive data is latched internally at the rising edge of the 8th pulse of the basic clock as shown in figure 17.19. Thus, the reception margin in asynchronous mode is given by formula (1) below.

$$M = \left\{ (0.5 - \frac{1}{2N}) - \frac{D - 0.5}{N} - (L - 0.5) F \right\} \times 100(\%)$$

... Formula (1)

[Legend]

N: Ratio of bit rate to clock (N = 16)

D: Clock duty (D = 0.5 to 1.0)

L: Frame length (L = 9 to 12)

F: Absolute value of clock rate deviation

Assuming values of F (absolute value of clock rate deviation) = 0 and D (clock duty) = 0.5 in formula (1), the reception margin can be given by the formula.

$M = \{0.5 - 1/(2 \times 16)\} \times 100 \ [\%] = 46.875\%$

However, this is only the computed value, and a margin of 20% to 30% should be allowed for in system design.

Figure 17.19 Receive Data Sampling Timing in Asynchronous Mode

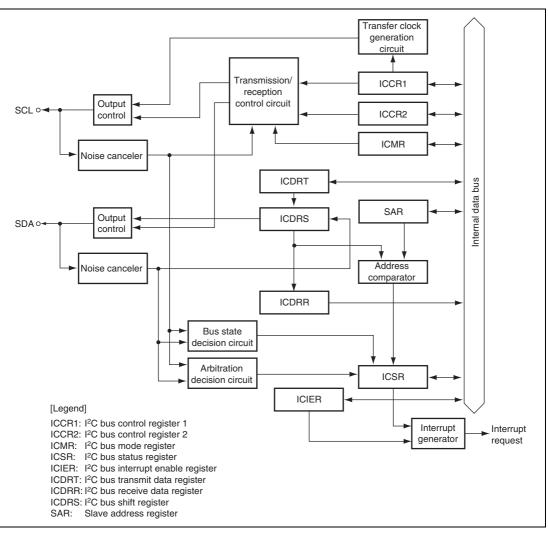

Figure 18.1 Block Diagram of I<sup>2</sup>C Bus Interface 2

## 18.3.3 I<sup>2</sup>C Bus Mode Register (ICMR)

ICMR selects whether the MSB or LSB is transferred first, performs master mode wait control, and selects the transfer bit count.

|     |          | Initial |     |                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|-----|----------|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Bit | Bit Name | Value   | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| 7   | MLS      | 0       | R/W | MSB-First/LSB-First Select                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|     |          |         |     | 0: MSB-first                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|     |          |         |     | 1: LSB-first                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|     |          |         |     | Set this bit to 0 when the $I^2C$ bus format is used.                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 6   | WAIT     | 0       | R/W | Wait Insertion Bit                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|     |          |         |     | In master mode with the I <sup>2</sup> C bus format, this bit selects<br>whether to insert a wait after data transfer except the<br>acknowledge bit. When WAIT is set to 1, after the fall of<br>the clock for the final data bit, low period is extended for<br>two transfer clocks. If WAIT is cleared to 0, data and<br>acknowledge bits are transferred consecutively with no<br>wait inserted. |  |  |  |  |  |  |

|     |          |         |     | The setting of this bit is invalid in slave mode with the<br>I <sup>2</sup> C bus format or with the clocked synchronous serial<br>format.                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 5   | _        | 1       |     | Reserved                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 4   | _        | 1       |     | These bits are always read as 1.                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 3   | BCWP     | 1       | R/W | BC Write Protect                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|     |          |         |     | This bit controls the BC2 to BC0 modifications. When modifying BC2 to BC0, this bit should be cleared to 0 and use the MOV instruction. In clock synchronous serial mode, BC should not be modified.                                                                                                                                                                                                |  |  |  |  |  |  |

|     |          |         |     | 0: When writing, values of BC2 to BC0 are set.                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|     |          |         |     | 1: When reading, 1 is always read.                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|     |          |         |     | When writing, settings of BC2 to BC0 are invalid.                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Register Name                     | Abbreviation | Bit No. | Address  | Module Name         | Data Bus<br>Width | Access<br>State |

|-----------------------------------|--------------|---------|----------|---------------------|-------------------|-----------------|

| Port mode register 3              | PMR3         | 8       | H'FFFFE2 | I/O Port            | 8                 | 2               |

| Port control register 1           | PCR1         | 8       | H'FFFFE4 | I/O Port            | 8                 | 2               |

| Port control register 2           | PCR2         | 8       | H'FFFFE5 | I/O Port            | 8                 | 2               |

| Port control register 3           | PCR3         | 8       | H'FFFFE6 | I/O Port            | 8                 | 2               |

| Port control register 5           | PCR5         | 8       | H'FFFFE8 | I/O Port            | 8                 | 2               |

| Port control register 7           | PCR7         | 8       | H'FFFFEA | I/O Port            | 8                 | 2               |

| Port control register 8           | PCR8         | 8       | H'FFFFEB | I/O Port            | 8                 | 2               |

| Port control register C           | PCRC         | 8       | H'FFFFEE | I/O Port            | 8                 | 2               |

| System control register 3         | SYSCR3       | 8       | H'FFFFEF | Power-down<br>modes | 8                 | 2               |

| System control register 1         | SYSCR1       | 8       | H'FFFFF0 | Power-down<br>modes | 8                 | 2               |

| System control register 2         | SYSCR2       | 8       | H'FFFFF1 | Power-down<br>modes | 8                 | 2               |

| Interrupt edge select register 1  | IEGR1        | 8       | H'FFFFF2 | Interrupt           | 8                 | 2               |

| Interrupt edge select register 2  | IEGR2        | 8       | H'FFFFF3 | Interrupt           | 8                 | 2               |

| Interrupt enable register 1       | IENR1        | 8       | H'FFFFF4 | Interrupt           | 8                 | 2               |

| Interrupt enable register 2       | IENR2        | 8       | H'FFFFF5 | Interrupt           | 8                 | 2               |

| Interrupt flag register 1         | IRR1         | 8       | H'FFFFF6 | Interrupt           | 8                 | 2               |

| Interrupt flag register 2         | IRR2         | 8       | H'FFFFF7 | Interrupt           | 8                 | 2               |

| Wakeup interrupt flag register    | IWPR         | 8       | H'FFFFF8 | Interrupt           | 8                 | 2               |

| Module standby control register 1 | MSTCR1       | 8       | H'FFFFF9 | Power-down<br>modes | 8                 | 2               |

| Module standby control register 2 | MSTCR2       | 8       | H'FFFFFA | Power-down<br>modes | 8                 | 2               |

Notes: 1. These registers can be accessed by word size only.

2. WDT: Watchdog timer

|          |            |              | Addressing Mode and<br>Instruction Length (bytes) |    |      |           |             |     |          |       | - |                                                  |   |     |       |     |     |   | No. of<br>States*1 |          |

|----------|------------|--------------|---------------------------------------------------|----|------|-----------|-------------|-----|----------|-------|---|--------------------------------------------------|---|-----|-------|-----|-----|---|--------------------|----------|

| Mnemonic |            | Operand Size |                                                   |    | @ERn | @(d, ERn) | @-ERn/@ERn+ | a   | @(d, PC) | @ @aa |   | Operation                                        |   | Con | ditio | n C | ode |   | Normal             | Advanced |

|          |            | d            | XX#                                               | Rn | 0    | 0         | 0           | @aa | 0        | 0     | Ι |                                                  |   | н   | Ν     | z   | v   | С | ٩                  | Ρq       |

| JMP      | JMP @ERn   | -            |                                                   |    | 2    |           |             |     |          |       |   | $PC \gets ERn$                                   | - | —   | —     | -   | —   | — | 4                  | 4        |

|          | JMP @aa:24 | -            |                                                   |    |      |           |             | 4   |          |       |   | PC ← aa:24                                       | - | -   | -     | -   | -   | - | 6                  | 6        |

|          | JMP @@aa:8 | -            |                                                   |    |      |           |             |     |          | 2     |   | PC ← @aa:8                                       | - | -   | -     | -   | -   | - | 8                  | 10       |

| BSR      | BSR d:8    | -            |                                                   |    |      |           |             |     | 2        |       |   | $PC \rightarrow @-SP$<br>$PC \leftarrow PC+d:8$  | - | -   | -     | _   | -   | - | 6                  | 8        |

|          | BSR d:16   | -            |                                                   |    |      |           |             |     | 4        |       |   | $PC \rightarrow @-SP$<br>$PC \leftarrow PC+d:16$ | - | -   | -     | -   | -   | - | 8                  | 10       |

| JSR      | JSR @ERn   | -            |                                                   |    | 2    |           |             |     |          |       |   | $PC \rightarrow @-SP$<br>$PC \leftarrow ERn$     | - | -   | -     | -   | -   | - | 6                  | 8        |

|          | JSR @aa:24 | -            |                                                   |    |      |           |             | 4   |          |       |   | $PC \rightarrow @-SP$<br>$PC \leftarrow aa:24$   | - | -   | -     | -   | -   | - | 8                  | 10       |

|          | JSR @@aa:8 | -            |                                                   |    |      |           |             |     |          | 2     |   | $PC \rightarrow @-SP$<br>$PC \leftarrow @aa:8$   | - | -   | -     | -   | -   | - | 8                  | 12       |

| RTS      | RTS        | -            |                                                   |    |      |           |             |     |          |       | 2 | $PC \leftarrow @SP+$                             | - | —   | _     | —   | _   | — | 8                  | 10       |

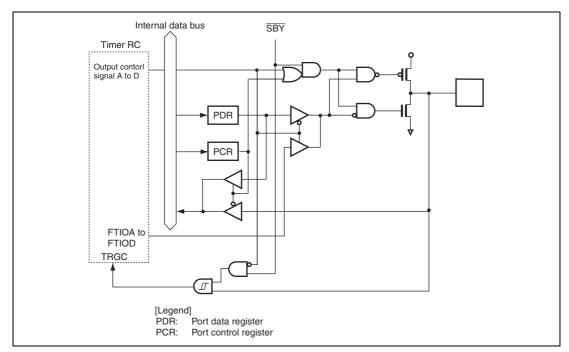

Figure B.28 Port H Block Diagram (PH7, PH6, PH5, PH4)

# Main Revisions and Additions in this Edition

| Item                                            | Page | Revisions (See Manual for Details)                                                                                               |                                                                                                                                           |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |                                |  |

|-------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------|--|

| Section 5 Clock Pulse Generators                | 76   | Amended                                                                                                                          |                                                                                                                                           |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |                                |  |

| 5.2.4 Clock Control/Status<br>Register (CKCSR)  |      | Bit                                                                                                                              | Bit Bit Name Description                                                                                                                  |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |                                |  |

|                                                 |      | 7                                                                                                                                | 7 PMRJ1 OSC Pin Function Select 1 and 0                                                                                                   |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |                                |  |

|                                                 |      | 6                                                                                                                                | PMRJ0                                                                                                                                     | PMRJ1                                                                                                                              | PMRJ0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | OSC2   | OSC1                           |  |

|                                                 |      |                                                                                                                                  |                                                                                                                                           | 0                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | I/O    | I/O                            |  |

|                                                 |      |                                                                                                                                  |                                                                                                                                           | 1                                                                                                                                  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CLKOUT | I/O                            |  |

|                                                 |      |                                                                                                                                  |                                                                                                                                           | 0                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Hi-Z   | OSC1<br>(external clock input) |  |

|                                                 |      |                                                                                                                                  |                                                                                                                                           | 1                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | OSC2   | OSC1                           |  |

|                                                 |      |                                                                                                                                  |                                                                                                                                           |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |                                |  |

| Section 14 Timer RD                             | 346  | Amended                                                                                                                          |                                                                                                                                           |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |                                |  |

| Figure 14.54 Block Diagram of<br>Digital Filter |      | FTIOA0 (TCLK)       \$\phi40M\$       \$\phi32\$       \$\phi4\$       \$\phi2\$       \$\phi4\$       \$\phi2\$       \$\phi4\$ |                                                                                                                                           |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |                                |  |

| Section 17 Serial Communication                 | 404  | Amended                                                                                                                          |                                                                                                                                           |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |                                |  |

| Interface 3 (SCI3)                              |      |                                                                                                                                  |                                                                                                                                           | or the TXD_3 bit in                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |                                |  |

| 17.8.2 Mark State and Break<br>Sending          |      | direc<br>PCF<br>marl<br>data<br>at m<br>to 1<br>becc<br>To s<br>PCF<br>to 1.<br>state                                            | ction (inpu<br>and PDR<br>k state (hig<br>transmiss<br>ark state to<br>and also s<br>omes an I/<br>send a brea<br>to 1 and<br>At this tin | t or outp<br>a. This c<br>gh level)<br>sion. To<br>until TE<br>set the T<br>O port,<br>ak durin<br>clear PI<br>ne, rega<br>pin bec | TXD pin is used as an I/O port whose<br>or output) and level are determined by<br>This can be used to set the TXD pin to<br>h level) or send a break during serial<br>ion. To maintain the communication line<br>ntil TE is set to 1, set both PCR and PDR<br>et the TXD bit to 1. Then, the TXD pin<br>D port, and 1 is output from the TXD pin.<br>k during serial transmission, first set<br>clear PDR to 0, and then set the TXD bit<br>e, regardless of the current transmission<br>pin becomes an I/O port, and 0 is output<br>bin. |        |                                |  |