Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | A/D 5x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c73a-04-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIC16C7X

NOTES:

## FIGURE 4-4: PIC16C72 REGISTER FILE MAP

| File<br>Address   | 3                     |                     | File<br>Address |

|-------------------|-----------------------|---------------------|-----------------|

| 00h               | INDF <sup>(1)</sup>   | INDF <sup>(1)</sup> | 80h             |

| 01h               | TMR0                  | OPTION              | 81h             |

| 02h               | PCL                   | PCL                 |                 |

| 03h               | STATUS                | STATUS              |                 |

| 04h               | FSR                   | FSR                 |                 |

| 05h               | PORTA                 | TRISA               | 85h             |

| 06h               | PORTB                 | TRISB               | 86h             |

| 07h               | PORTC                 | TRISC               |                 |

| 08h               |                       |                     |                 |

| 09h               |                       |                     | 89h             |

| 0Ah               | PCLATH                | PCLATH              | 8Ah             |

| 0Bh               | INTCON                | INTCON              | 8Bh             |

| 0Ch               | PIR1                  | PIE1                | 8Ch             |

| 0Dh               |                       |                     | 8Dh             |

| 0Eh               | TMR1L                 | PCON                | 8Eh             |

| 0Fh               | TMR1H                 |                     | 8Fh             |

| 10h               | T1CON                 |                     | 90h             |

| 11h               | TMR2                  |                     | 91h             |

| 12h               | T2CON                 | PR2                 | 92h             |

| 13h               | SSPBUF                | SSPADD              | 93h             |

| 14h               | SSPCON                | SSPSTAT             |                 |

| 15h               | CCPR1L                |                     | 95h             |

| 16h               | CCPR1H                |                     | 96h             |

| 17h               | CCP1CON               |                     | 97h             |

| 18h               |                       |                     | 98h             |

| 19h               |                       |                     | 99h             |

| 1Ah               |                       |                     | 9Ah             |

| 1Bh               |                       |                     | 9Bh             |

| 1Ch               |                       |                     | 9Ch             |

| 1Dh               |                       |                     | 9Dh             |

| 1Eh               | ADRES                 |                     | 9Eh             |

| 1Fh               | ADCON0                | ADCON1              | 9Fh             |

| 20h               |                       |                     | A0h             |

|                   | General<br>Purpose    | General<br>Purpose  |                 |

|                   | Register              | Register            |                 |

|                   | U U                   |                     | BFh             |

|                   |                       |                     | C0h             |

|                   |                       |                     |                 |

|                   |                       |                     |                 |

|                   |                       |                     |                 |

| 7Fh               |                       |                     | FFh             |

|                   | Bank 0                | Bank 1              |                 |

|                   |                       |                     |                 |

|                   | nimplemented data     | a memory locations  | s, read as      |

| '0'.<br>Note 1: 1 | Not a physical regis  | stor                |                 |

|                   | tot a priysical regit | лот.                |                 |

|                   |                       |                     |                 |

#### FIGURE 4-5: PIC16C73/73A/74/74A REGISTER FILE MAP

|                | REGIST                                                        | ER FILE MA                     | F               |

|----------------|---------------------------------------------------------------|--------------------------------|-----------------|

| File<br>Addres | SS                                                            |                                | File<br>Address |

| 00h            | INDF <sup>(1)</sup>                                           | INDF <sup>(1)</sup>            | 80h             |

| 01h            | TMR0                                                          | OPTION                         |                 |

| 02h            | PCL                                                           | PCL                            | 82h             |

| 03h            | STATUS                                                        | STATUS                         | 83h             |

| 04h            | FSR                                                           | FSR                            |                 |

| 05h            | PORTA                                                         | TRISA                          | 85h             |

| 06h            | PORTB                                                         | TRISB                          | 86h             |

| 07h            | PORTC                                                         | TRISC                          |                 |

| 08h            | PORTD <sup>(2)</sup>                                          | TRISD <sup>(2)</sup>           |                 |

| 09h            | PORTE <sup>(2)</sup>                                          | TRISE <sup>(2)</sup>           | 89h             |

| 0Ah            | PCLATH                                                        | PCLATH                         | 8Ah             |

| 0Bh            | INTCON                                                        | INTCON                         | 8Bh             |

| 0Ch            | PIR1                                                          | PIE1                           | 8Ch             |

| 0Dh            | PIR2                                                          | PIE2                           | 8Dh             |

| 0Eh            | TMR1L                                                         | PCON                           | 8Eh             |

| 0Fh            | TMR1H                                                         |                                | 8Fh             |

| 10h            | T1CON                                                         |                                | 90h             |

| 11h            | TMR2                                                          |                                | 91h             |

| 12h            | T2CON                                                         | PR2                            |                 |

| 13h            | SSPBUF                                                        | SSPADD                         | 93h             |

| 14h            | SSPCON                                                        | SSPSTAT                        | 94h             |

| 15h            | CCPR1L                                                        |                                | 95h             |

| 16h            | CCPR1H                                                        |                                | 96h             |

| 17h            | CCP1CON                                                       |                                | 97h             |

| 18h            | RCSTA                                                         | TXSTA                          |                 |

| 19h            | TXREG                                                         | SPBRG                          | 99h             |

| 1Ah            | RCREG                                                         |                                | 9Ah             |

| 1Bh            | CCPR2L                                                        |                                | 9Bh             |

| 1Ch            | CCPR2H                                                        |                                | 9Ch             |

| 1Dh            | CCP2CON                                                       |                                | 9Dh             |

| 1Eh            | ADRES                                                         |                                | 9Eh             |

| 1Fh            | ADCON0                                                        | ADCON1                         | 9Fh             |

| 20h            |                                                               |                                | A0h             |

|                | General<br>Purpose<br>Register                                | General<br>Purpose<br>Register |                 |

| 7Fh            |                                                               |                                | FFh             |

|                | Bank 0                                                        | Bank 1                         |                 |

|                | Unimplemented da                                              | -                              | ons, read as    |

| Note 1:<br>2:  | Not a physical reg<br>These registers ar<br>mented on the PIC | e not physically               |                 |

|                |                                                               |                                |                 |

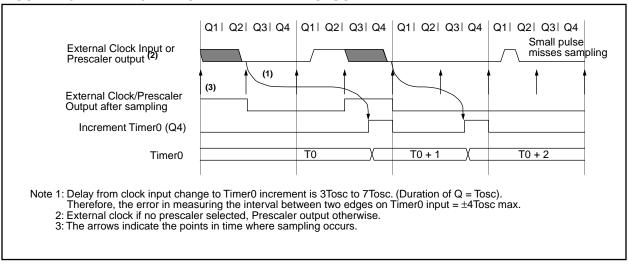

#### 7.2 Using Timer0 with an External Clock Applicable Devices 72 73 73A 74 74A 76 77

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 7.2.2 TMR0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

#### FIGURE 7-5: TIMER0 TIMING WITH EXTERNAL CLOCK

#### FIGURE 9-2: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

| U-0      | R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0                                                                                                     |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| <u> </u> | TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0 R = Readable bit                                                                 |  |

| bit7     | bit0<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset                                           |  |

| bit 7:   | Unimplemented: Read as '0'                                                                                                              |  |

| bit 6-3: | TOUTPS3:TOUTPS0: Timer2 Output Postscale Select bits<br>0000 = 1:1 Postscale<br>0001 = 1:2 Postscale<br>•<br>•<br>1111 = 1:16 Postscale |  |

| bit 2:   | TMR2ON: Timer2 On bit<br>1 = Timer2 is on<br>0 = Timer2 is off                                                                          |  |

| bit 1-0: | <b>T2CKPS1:T2CKPS0</b> : Timer2 Clock Prescale Select bits<br>00 = Prescaler is 1<br>01 = Prescaler is 4<br>1x = Prescaler is 16        |  |

#### **TABLE 9-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER**

| Address                        | Name   | Bit 7                  | Bit 6          | Bit 5               | Bit 4               | Bit 3   | Bit 2  | Bit 1   | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|--------------------------------|--------|------------------------|----------------|---------------------|---------------------|---------|--------|---------|-----------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh          | INTCON | GIE                    | PEIE           | TOIE                | INTE                | RBIE    | TOIF   | INTF    | RBIF      | 0000 000x                | 0000 000u                       |

| 0Ch                            | PIR1   | PSPIF <sup>(1,2)</sup> | ADIF           | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | SSPIF   | CCP1IF | TMR2IF  | TMR1IF    | 0000 0000                | 0000 0000                       |

| 8Ch                            | PIE1   | PSPIE <sup>(1,2)</sup> | ADIE           | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup> | SSPIE   | CCP1IE | TMR2IE  | TMR1IE    | 0000 0000                | 0000 0000                       |

| 11h                            | TMR2   | Timer2 mod             | lule's registe | r                   |                     |         |        |         |           | 0000 0000                | 0000 0000                       |

| 12h                            | T2CON  | _                      | TOUTPS3        | TOUTPS2             | TOUTPS1             | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0   | -000 0000                | -000 0000                       |

| 92h PR2 Timer2 Period Register |        |                        |                |                     |                     |         |        |         | 1111 1111 | 1111 1111                |                                 |

Legend:

x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

Note

1:

Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

2:

The PIC16C72 does not have a Parallel Slave Port or a USART, these bits are unimplemented, read as '0'.

#### 11.5.1.3 TRANSMISSION

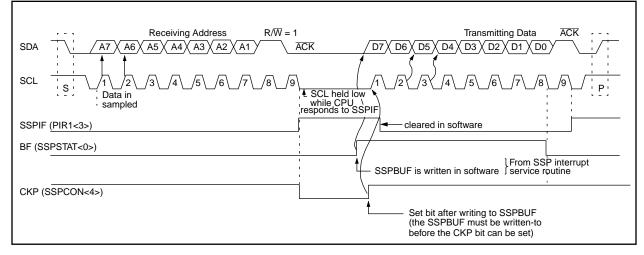

When the  $R\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The  $\overline{ACK}$  pulse will be sent on the ninth bit, and pin RC3/SCK/SCL is held low. The transmit data must be loaded into the SSP-BUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 11-26). An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software, and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP.

#### FIGURE 11-26: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

#### 12.1 USART Baud Rate Generator (BRG) Applicable Devices 72 73 73A 74 74A 76 77

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In asynchronous mode bit BRGH (TXSTA<2>) also controls the baud rate. In synchronous mode bit BRGH is ignored. Table 12-1 shows the formula for computation of the baud rate for different USART modes which only apply in master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 12-1. From this, the error in baud rate can be determined.

Example 12-1 shows the calculation of the baud rate error for the following conditions:

Fosc = 16 MHz Desired Baud Rate = 9600 BRGH = 0 SYNC = 0

#### EXAMPLE 12-1: CALCULATING BAUD RATE ERROR

Desired Baud rate = Fosc / (64 (X + 1))

$9600 = \frac{16000000}{(64 (X + 1))}$

$X = \lfloor 25.042 \rfloor = 25$

Calculated Baud Rate=16000000 / (64 (25 + 1))

= 9615

- Error = (Calculated Baud Rate Desired Baud Rate) Desired Baud Rate

- = (9615 9600) / 9600

= 0.16%

It may be advantageous to use the high baud rate (BRGH = 1) even for slower baud clocks. This is because the Fosc/(16(X + 1)) equation can reduce the baud rate error in some cases.

| Note: | For the PIC16C73/73A/74/74A, the asyn-<br>chronous high speed mode (BRGH = 1)<br>may experience a high rate of receive<br>errors. It is recommended that BRGH = 0.<br>If you desire a higher baud rate than<br>BRGH = 0 can support, refer to the device<br>errata for additional information, or use the<br>PIC16C76/77. |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Writing a new value to the SPBRG register, causes the BRG timer to be reset (or cleared), this ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### TABLE 12-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)     |

|------|-------------------------------------------|---------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate= Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X+1))   | NA                        |

X = value in SPBRG (0 to 255)

#### TABLE 12-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name                                   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|----------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 98h     | TXSTA                                  | CSRC  | TX9   | TXEN  | SYNC  | —     | BRGH  | TRMT  | TX9D  | 0000 -010                | 0000 -010                 |

| 18h     | RCSTA                                  | SPEN  | RX9   | SREN  | CREN  | _     | FERR  | OERR  | RX9D  | 0000 -00x                | 0000 -00x                 |

| 99h     | 99h SPBRG Baud Rate Generator Register |       |       |       |       |       |       |       |       |                          | 0000 0000                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used by the BRG.

#### TABLE 12-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Address | Name                                   | Bit 7                | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|----------------------------------------|----------------------|-----------|---------|-------|-------|--------|--------|-----------|--------------------------|---------------------------|

| 0Ch     | PIR1                                   | PSPIF <sup>(1)</sup> | ADIF      | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF    | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA                                  | SPEN                 | RX9       | SREN    | CREN  | _     | FERR   | OERR   | RX9D      | 0000 -00x                | 0000 -00x                 |

| 19h     | TXREG                                  | USART Tra            | ansmit Re | egister |       |       |        |        |           | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1                                   | PSPIE <sup>(1)</sup> | ADIE      | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE    | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA                                  | CSRC                 | TX9       | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D      | 0000 -010                | 0000 -010                 |

| 99h     | 99h SPBRG Baud Rate Generator Register |                      |           |         |       |       |        |        | 0000 0000 | 0000 0000                |                           |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Transmission. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

#### TABLE 12-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address | Name                                   | Bit 7                | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|----------------------------------------|----------------------|-----------|---------|-------|-------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1                                   | PSPIF <sup>(1)</sup> | ADIF      | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA                                  | SPEN                 | RX9       | SREN    | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                 |

| 1Ah     | RCREG                                  | USART Re             | eceive Re | egister |       |       |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1                                   | PSPIE <sup>(1)</sup> | ADIE      | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA                                  | CSRC                 | TX9       | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | 99h SPBRG Baud Rate Generator Register |                      |           |         |       |       |        |        |        | 0000 0000                | 0000 0000                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

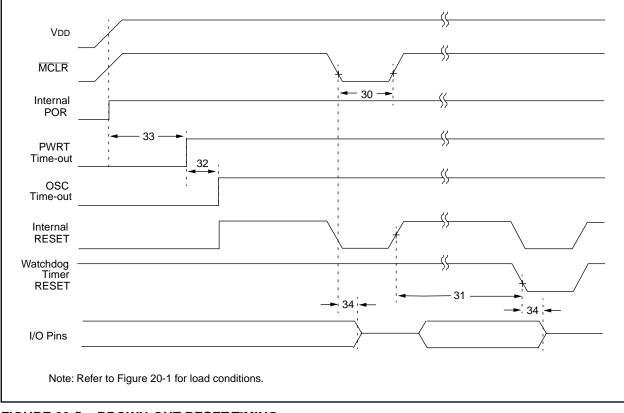

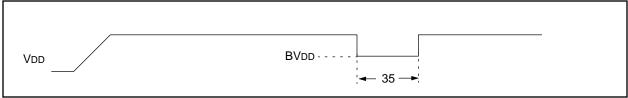

#### 14.4.5 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 14-10, Figure 14-11, and Figure 14-12 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 14-11). This is useful for testing purposes or to synchronize more than one PIC16CXX device operating in parallel.

Table 14-7 shows the reset conditions for some special function registers, while Table 14-8 shows the reset conditions for all the registers.

#### 14.4.6 POWER CONTROL/STATUS REGISTER (PCON)

| -  | •  | cabl |    |     |    |    |

|----|----|------|----|-----|----|----|

| 72 | 73 | 73A  | 74 | 74A | 76 | 77 |

The Power Control/Status Register, PCON has up to two bits, depending upon the device. Bit0 is not implemented on the PIC16C73 or PIC16C74.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent resets to see if bit BOR cleared, indicating a BOR occurred. The BOR bit is a "Don't Care" bit and is not necessarily predictable if the Brown-out Reset circuitry is disabled (by clearing bit BODEN in the Configuration Word).

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

#### TABLE 14-3: TIME-OUT IN VARIOUS SITUATIONS, PIC16C73/74

| Oscillator Configuration | Powe             | Wake-up from SLEEP |           |

|--------------------------|------------------|--------------------|-----------|

|                          | PWRTE = 1        | PWRTE = 0          |           |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc           | 1024 Tosc |

| RC                       | 72 ms            | _                  |           |

#### TABLE 14-4: TIME-OUT IN VARIOUS SITUATIONS, PIC16C72/73A/74A/76/77

| Oscillator Configuration | Power            | r-up      | Brown-out        | Wake-up from SLEEP |  |

|--------------------------|------------------|-----------|------------------|--------------------|--|

|                          | PWRTE = 0        | PWRTE = 1 | Brown-out        |                    |  |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc           |  |

| RC                       | 72 ms            |           | 72 ms            | _                  |  |

#### TABLE 14-5: STATUS BITS AND THEIR SIGNIFICANCE, PIC16C73/74

| POR | TO | PD |                                                         |

|-----|----|----|---------------------------------------------------------|

| 0   | 1  | 1  | Power-on Reset                                          |

| 0   | 0  | х  | Illegal, TO is set on POR                               |

| 0   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0  | 1  | WDT Reset                                               |

| 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

Legend: u = unchanged, x = unknown

| TABLE 14-6: | STATUS BITS AND THEIR SIGNIFICANCE, PIC16C72/73A/74A/76/77 |

|-------------|------------------------------------------------------------|

|-------------|------------------------------------------------------------|

| POR | BOR | TO | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | x  | x  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

#### TABLE 14-7: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register<br>PIC16C73/74 | PCON<br>Register<br>PIC16C72/73A/74A/76/77 |

|------------------------------------|-----------------------|--------------------|---------------------------------|--------------------------------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0-                              | 0x                                         |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | u-                              | uu                                         |

| MCLR Reset during SLEEP            | 000h                  | 0001 Ouuu          | u-                              | uu                                         |

| WDT Reset                          | 000h                  | 0000 luuu          | u-                              | uu                                         |

| WDT Wake-up                        | PC + 1                | uuu0 Ouuu          | u-                              | uu                                         |

| Brown-out Reset                    | 000h                  | 0001 luuu          | N/A                             | u0                                         |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | u-                              | uu                                         |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

| TABLE 14-8: | INITIALIZATION CONDITIONS FOR ALL REGISTERS |

|-------------|---------------------------------------------|

|-------------|---------------------------------------------|

| Register | Applicable Devices |    |     |    |     | es |    | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT<br>or<br>Interrupt |  |

|----------|--------------------|----|-----|----|-----|----|----|------------------------------------|--------------------------|------------------------------------|--|

| W        | 72                 | 73 | 73A | 74 | 74A | 76 | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                          |  |

| INDF     | 72                 | 73 | 73A | 74 | 74A | 76 | 77 | N/A                                | N/A                      | N/A                                |  |

| TMR0     | 72                 | 73 | 73A | 74 | 74A | 76 | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                          |  |

| PCL      | 72                 | 73 | 73A | 74 | 74A | 76 | 77 | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>              |  |

| STATUS   | 72                 | 73 | 73A | 74 | 74A | 76 | 77 | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <b>(3)</b>               |  |

| FSR      | 72                 | 73 | 73A | 74 | 74A | 76 | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                          |  |

| PORTA    | 72                 | 73 | 73A | 74 | 74A | 76 | 77 | 0x 0000                            | 0u 0000                  | uu uuuu                            |  |

| PORTB    | 72                 | 73 | 73A | 74 | 74A | 76 | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                          |  |

| PORTC    | 72                 | 73 | 73A | 74 | 74A | 76 | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                          |  |

| PORTD    | 72                 | 73 | 73A | 74 | 74A | 76 | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                          |  |

| PORTE    | 72                 | 73 | 73A | 74 | 74A | 76 | 77 | xxx                                | uuu                      | uuu                                |  |

| PCLATH   | 72                 | 73 | 73A | 74 | 74A | 76 | 77 | 0 0000                             | 0 0000                   | u uuuu                             |  |

Legend: u = unchanged, x = unknown, -= unimplemented bit, read as '0', <math>q = value depends on condition

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 14-7 for reset value for specific condition.

#### FIGURE 14-20: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| ; a1   a2   a3   a4 ; a1   a2   a<br>osc1/^_/_/_/_//                               | 23 Q4 Q1              | Q1  Q2  Q3  Q4 | ; q1   q2   q3   q4 ;<br>//////////////////////////////////// | Q1   Q2   Q3   Q4 ; | Q1   Q2   Q3   Q4;<br>∕──∕──∕─ |

|------------------------------------------------------------------------------------|-----------------------|----------------|---------------------------------------------------------------|---------------------|--------------------------------|

| CLKOUT(4) ,//                                                                      | Tost(2)               |                |                                                               | \'                  | '                              |

| INT pin                                                                            |                       |                |                                                               | 1<br>1<br>1         |                                |

| INTF flag<br>(INTCON<1>)                                                           | <b>`</b>              | 1              | Interrupt Latency<br>(Note 2)                                 |                     |                                |

| GIE bit<br>(INTCON<7>)                                                             | Processor in<br>SLEEP |                |                                                               | ו<br>ו<br>ו<br>ו    | 1<br>1<br>1                    |

| INSTRUCTION FLOW                                                                   |                       |                |                                                               | 1                   | 1                              |

| PC X PC X PC+1                                                                     | X PC+2                | PC+2           | PC + 2                                                        | X 0004h             | 0005h                          |

| Instruction $\begin{cases} \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $ | + 1)                  | Inst(PC + 2)   |                                                               | Inst(0004h)         | Inst(0005h)                    |

| Instruction<br>executed I Inst(PC - 1) SLEEP                                       |                       | Inst(PC + 1)   | Dummy cycle                                                   | Dummy cycle         | Inst(0004h)                    |

| Note 1. XT US or Descillator mode on                                               |                       |                |                                                               |                     |                                |

Note 1: XT, HS or LP oscillator mode assumed.

2: TOST = 1024TOSC (drawing not to scale) This delay will not be there for RC osc mode.

3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

#### 14.9 <u>Program Verification/Code Protection</u>

Applicable Devices

72 73 73A 74 74A 76 77

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting windowed devices.              |

#### 14.10 ID Locations

Applicable Devices

72 73 73A 74 74A 76 77

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

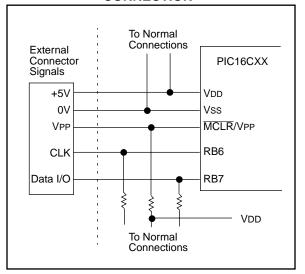

## 14.11 In-Circuit Serial Programming Applicable Devices 72/73/73A/74/74A/76/77

PIC16CXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed. The device is placed into a program/verify mode by holding the RB6 and RB7 pins low while raising the  $\overline{\text{MCLR}}$  (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After reset, to place the device into programming/verify mode, the program counter (PC) is at location 00h. A 6bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X Programming Specifications (Literature #DS30228).

#### FIGURE 14-21: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

#### 17.1 DC Characteristics: PIC16C72-04 (Commercial, Industrial, Extended) PIC16C72-10 (Commercial, Industrial, Extended) PIC16C72-20 (Commercial, Industrial, Extended)

| DC CHA                         | RACTERISTICS                                                      |       | <b>Standa</b><br>Operati |                           |                      | ure -4<br>-4         | Itions (unless otherwise stated) $40^{\circ}C \leq TA \leq +125^{\circ}C$ for extended, $40^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial and $40^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial                                                                                                                   |

|--------------------------------|-------------------------------------------------------------------|-------|--------------------------|---------------------------|----------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                   | Characteristic                                                    | Sym   | Min                      | Тур†                      | Max                  | Units                | Conditions                                                                                                                                                                                                                                                                                                                  |

| D001<br>D001A                  | Supply Voltage                                                    | Vdd   | 4.0<br>4.5               |                           | 6.0<br>5.5           | V<br>V               | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                                                                                                                                                     |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                            | Vdr   | -                        | 1.5                       | -                    | V                    |                                                                                                                                                                                                                                                                                                                             |

| D003                           | VDD start voltage to<br>ensure internal Power-<br>on Reset Signal | VPOR  | -                        | Vss                       | -                    | V                    | See section on Power-on Reset for details                                                                                                                                                                                                                                                                                   |

| D004*                          | VDD rise rate to ensure<br>internal Power-on Reset<br>Signal      | SVDD  | 0.05                     | -                         | -                    | V/ms                 | See section on Power-on Reset for details                                                                                                                                                                                                                                                                                   |

| D005                           | Brown-out Reset Voltage                                           | Bvdd  | 3.7                      | 4.0                       | 4.3                  | V                    | BODEN bit in configuration word enabled                                                                                                                                                                                                                                                                                     |

|                                |                                                                   |       | 3.7                      | 4.0                       | 4.4                  | V                    | Extended Only                                                                                                                                                                                                                                                                                                               |

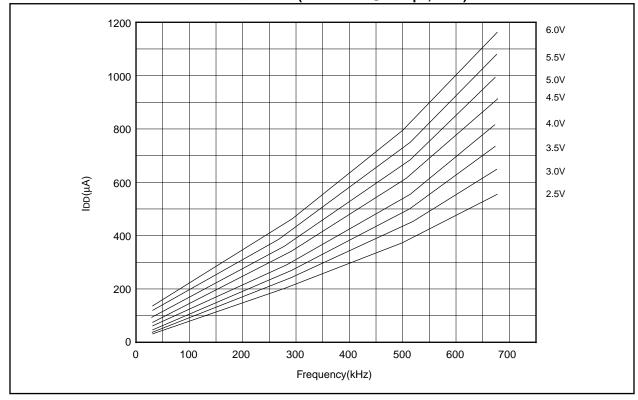

| D010                           | Supply Current<br>(Note 2,5)                                      | IDD   | -                        | 2.7                       | 5.0                  | mA                   | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                                                                                                                                                                                                                               |

| D013                           |                                                                   |       | -                        | 10                        | 20                   | mA                   | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                                                                                                                                                                           |

| D015                           | Brown-out Reset Current<br>(Note 6)                               | ΔIBOR | -                        | 350                       | 425                  | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                                                                                                                      |

| D020<br>D021<br>D021A<br>D021B | Power-down Current<br>(Note 3,5)                                  | IPD   | -<br>-<br>-<br>-         | 10.5<br>1.5<br>1.5<br>2.5 | 42<br>16<br>19<br>19 | μΑ<br>μΑ<br>μΑ<br>μΑ | $ \begin{array}{l} VDD = 4.0V, WDT \text{ enabled}, -40^\circC \text{ to } +85^\circC \\ VDD = 4.0V, WDT \text{ disabled}, -0^\circC \text{ to } +70^\circC \\ VDD = 4.0V, WDT \text{ disabled}, -40^\circC \text{ to } +85^\circC \\ VDD = 4.0V, WDT \text{ disabled}, -40^\circC \text{ to } +125^\circC \\ \end{array} $ |

| D023                           | Brown-out Reset Current<br>(Note 6)                               | ΔIBOR | -                        | 350                       | 425                  | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                                                                                                                      |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD  $\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VbD and Vss.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

#### Applicable Devices 72 73 73A 74 74A 76 77

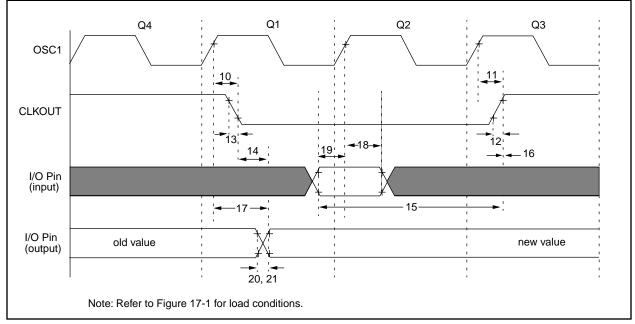

#### FIGURE 17-3: CLKOUT AND I/O TIMING

| TABLE 17-3: CLKOUT AND I/O TIMING REQUIREMENTS | ГABLE 17-3: |

|------------------------------------------------|-------------|

|------------------------------------------------|-------------|

| Parameter<br>No. | Sym      | Characteristic                                    |                     | Min        | Тур† | Мах         | Units | Conditions |

|------------------|----------|---------------------------------------------------|---------------------|------------|------|-------------|-------|------------|

| 10*              | TosH2ckL | OSC1 <sup>↑</sup> to CLKOUT↓                      |                     | _          | 75   | 200         | ns    | Note 1     |

| 11*              | TosH2ckH | OSC1 <sup>↑</sup> to CLKOUT <sup>↑</sup>          |                     | _          | 75   | 200         | ns    | Note 1     |

| 12*              | TckR     | CLKOUT rise time                                  |                     | _          | 35   | 100         | ns    | Note 1     |

| 13*              | TckF     | CLKOUT fall time                                  |                     | _          | 35   | 100         | ns    | Note 1     |

| 14*              | TckL2ioV | CLKOUT ↓ to Port out vali                         | d                   | _          | —    | 0.5Tcy + 20 | ns    | Note 1     |

| 15*              | TioV2ckH | Port in valid before CLKOU                        | T ↑                 | Tosc + 200 | -    | _           | ns    | Note 1     |

| 16*              | TckH2iol | Port in hold after CLKOUT                         | $\uparrow$          | 0          | -    | -           | ns    | Note 1     |

| 17*              | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to<br>Port out valid |                     | _          | 50   | 150         | ns    |            |

| 18*              | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to                   | PIC16 <b>C</b> 72   | 100        | -    | -           | ns    |            |

|                  |          | Port input invalid (I/O in hold time)             | PIC16 <b>LC</b> 72  | 200        | -    | _           | ns    |            |

| 19*              | TioV2osH | Port input valid to OSC11                         | (I/O in setup time) | 0          | -    | _           | ns    |            |

| 20*              | TioR     | Port output rise time                             | PIC16 <b>C</b> 72   | —          | 10   | 40          | ns    |            |

|                  |          |                                                   | PIC16 <b>LC</b> 72  | _          | —    | 80          | ns    |            |

| 21*              | TioF     | Port output fall time                             | PIC16 <b>C</b> 72   | _          | 10   | 40          | ns    |            |

|                  |          |                                                   | PIC16 <b>LC</b> 72  | _          | -    | 80          | ns    |            |

| 22††*            | Tinp     | INT pin high or low time                          |                     | Тсү        | -    | _           | ns    |            |

| 23††*            | Trbp     | RB7:RB4 change INT high                           | n or low time       | Тсү        | -    | _           | ns    |            |

$^{\ast}$  These parameters are characterized but not tested.

†Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

these parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

# TABLE 17-10:A/D CONVERTER CHARACTERISTICS:<br/>PIC16C72-04 (Commercial, Industrial, Extended)<br/>PIC16C72-10 (Commercial, Industrial, Extended)<br/>PIC16C72-20 (Commercial, Industrial, Extended)<br/>PIC16LC72-04 (Commercial, Industrial)

| Param<br>No. | Sym  | Characteristic                                 |                    | Min       | Тур†       | Max        | Units | Conditions                                                                                                  |

|--------------|------|------------------------------------------------|--------------------|-----------|------------|------------|-------|-------------------------------------------------------------------------------------------------------------|

| A01          | Nr   | Resolution                                     |                    |           | —          | 8-bits     | bit   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A02          | Eabs | Total Absolute error                           |                    | —         | —          | <±1        | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A03          | EIL  | Integral linearity error                       |                    | _         | —          | <±1        | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A04          | EDL  | Differential linearity error                   |                    | _         | —          | <±1        | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A05          | EFS  | Full scale error                               |                    | —         | —          | <±1        | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A06          | EOFF | Offset error                                   |                    | _         | —          | <±1        | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A10          | —    | Monotonicity                                   |                    | —         | guaranteed | _          | _     | $VSS \leq VAIN \leq VREF$                                                                                   |

| A20          | Vref | Reference voltage                              |                    | 3.0V      | —          | VDD + 0.3  | V     |                                                                                                             |

| A25          | VAIN | Analog input voltage                           |                    | Vss - 0.3 | —          | Vref + 0.3 | V     |                                                                                                             |

| A30          | Zain | Recommended impedance of analog voltage source |                    |           | _          | 10.0       | kΩ    |                                                                                                             |

| A40          | IAD  | A/D conversion current (VDD)                   | PIC16 <b>C</b> 72  | —         | 180        | _          | μΑ    | Average current consump-                                                                                    |

|              |      |                                                | PIC16 <b>LC</b> 72 | —         | 90         | —          | μA    | tion when A/D is on.<br>(Note 1)                                                                            |

| A50          | IREF | VREF input current (Note 2)                    |                    | 10        | _          | 1000       | μA    | During VAIN acquisition.<br>Based on differential of<br>VHOLD to VAIN to charge<br>CHOLD, see Section 13.1. |

|              |      |                                                |                    | —         | —          | 10         | μA    | During A/D Conversion cycle                                                                                 |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

#### 18.0 ELECTRICAL CHARACTERISTICS FOR PIC16C73/74

#### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                                    | 55 to +125°C                       |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage temperature                                                                                                               | 65°C to +150°C                     |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                                                | 0.3V to (VDD + 0.3V)               |

| Voltage on VDD with respect to Vss                                                                                                | 0.3 to +7.5V                       |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                      | 0 to +14V                          |

| Voltage on RA4 with respect to Vss                                                                                                | 0 to +14V                          |

| Total power dissipation (Note 1)                                                                                                  | 1.0W                               |

| Maximum current out of Vss pin                                                                                                    | 300 mA                             |

| Maximum current into VDD pin                                                                                                      | 250 mA                             |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                                      |                                    |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                                                    | ±20 mA                             |

| Maximum output current sunk by any I/O pin                                                                                        | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                                                     | 25 mA                              |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                                               | 200 mA                             |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                                            | 200 mA                             |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                                                       | 200 mA                             |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                                                    | 200 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\Sigma$ IOH} + $\Sigma$ {(VDD -                   | Voh) x Ioh} + $\Sigma$ (Vol x Iol) |

| Note $0$ , $\lambda$ (alternative balance) (as a table $\overline{\mathbf{MOLD}}$ are inducting summation matching the $0$ or $0$ |                                    |

- **Note 2:** Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

- Note 3: PORTD and PORTE are not implemented on the PIC16C73.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### TABLE 18-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C73-04<br>PIC16C74-04                                                                                                                          | PIC16C73-10<br>PIC16C74-10                                                                                                                         | PIC16C73-20<br>PIC16C74-20                                                                                                                         | PIC16LC73-04<br>PIC16LC74-04                                                                               | JW Devices                                                                                                                                         |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                            | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 3.0V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 13.5 μA max. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                           |

| хт  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                            | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 3.0V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 13.5 μA max. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                           |

| HS  | VDD:         4.5V to 5.5V           IDD:         13.5 mA typ. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         4 MHz max. | VDD:         4.5V to 5.5V           IDD:         15 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         10 MHz max. | VDD:         4.5V to 5.5V           IDD:         30 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         20 MHz max. | Not recommended for<br>use in HS mode                                                                      | VDD:         4.5V to 5.5V           IDD:         30 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         20 MHz max. |

| LP  | VDD: 4.0V to 6.0V<br>IDD: 52.5 μA typ. at<br>32 kHz, 4.0V<br>IPD: 0.9 μA typ. at 4.0V<br>Freq: 200 kHz max.                                         | Not recommended for<br>use in LP mode                                                                                                              | Not recommended for<br>use in LP mode                                                                                                              | VDD: 3.0V to 6.0V<br>IDD: 48 μA max. at<br>32 kHz, 3.0V<br>IPD: 13.5 μA max. at 3.0V<br>Freq: 200 kHz max. | VDD: 3.0V to 6.0V<br>IDD: 48 μA max. at<br>32 kHz, 3.0V<br>IPD: 13.5 μA max. at 3.0V<br>Freq: 200 kHz max.                                         |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

#### 18.2 DC Characteristics: PIC16LC73/74-04 (Commercial, Industrial)

| DC CHARACTERISTICS    |                                                                  |      |      | ard Ope<br>ing tem |                  | -              | itions (unless otherwise stated) $0^{\circ}C$ $\leq TA \leq +85^{\circ}C$ for industrial and $C$ $\leq TA \leq +70^{\circ}C$ for commercial                                                  |  |  |  |

|-----------------------|------------------------------------------------------------------|------|------|--------------------|------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No.          |                                                                  |      | Min  | Тур†               | Conditions       |                |                                                                                                                                                                                              |  |  |  |

| D001                  | Supply Voltage                                                   | Vdd  | 3.0  | -                  | 6.0              | V              | LP, XT, RC osc configuration (DC - 4 MHz)                                                                                                                                                    |  |  |  |

| D002*                 | RAM Data Retention<br>Voltage (Note 1)                           | Vdr  | -    | 1.5                | -                | V              |                                                                                                                                                                                              |  |  |  |

| D003                  | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR | -    | Vss                | -                | V              | See section on Power-on Reset for details                                                                                                                                                    |  |  |  |

| D004*                 | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | Svdd | 0.05 | -                  | -                | V/ms           | See section on Power-on Reset for details                                                                                                                                                    |  |  |  |

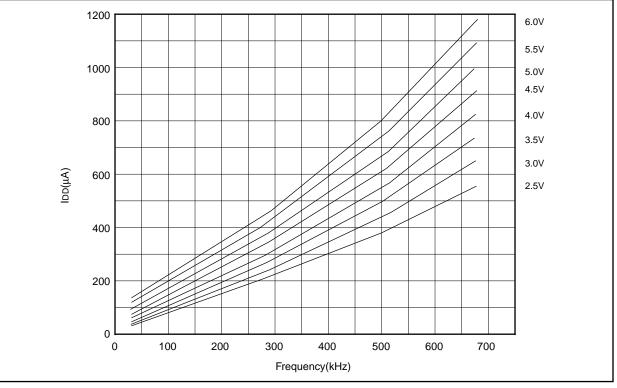

| D010                  | Supply Current (Note 2,5)                                        | IDD  | -    | 2.0                | 3.8              | mA             | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                                                                                |  |  |  |

| D010A                 |                                                                  |      | -    | 22.5               | 48               | μA             | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                                                                                                              |  |  |  |

| D020<br>D021<br>D021A | Power-down Current<br>(Note 3,5)                                 | IPD  |      | 7.5<br>0.9<br>0.9  | 30<br>13.5<br>18 | μΑ<br>μΑ<br>μΑ | VDD = $3.0V$ , WDT enabled, $-40^{\circ}C$ to $+85^{\circ}C$<br>VDD = $3.0V$ , WDT disabled, $0^{\circ}C$ to $+70^{\circ}C$<br>VDD = $3.0V$ , WDT disabled, $-40^{\circ}C$ to $+85^{\circ}C$ |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

$\overline{\text{MCLR}}$  = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

#### Applicable Devices 72 73 73A 74 74A 76 77

19.1 DC Characteristics: PIC16C73A/74A-04 (Commercial, Industrial, Extended) PIC16C73A/74A-10 (Commercial, Industrial, Extended) PIC16C73A/74A-20 (Commercial, Industrial, Extended)

| DC CHA                         |                                                                  | <b>Standa</b><br>Operati |                  |                           | ure -4<br>-4         | litions (unless otherwise stated) $0^{\circ}C \leq TA \leq +125^{\circ}C$ for extended, $0^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial and $C \leq TA \leq +70^{\circ}C$ for commercial |                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------|------------------------------------------------------------------|--------------------------|------------------|---------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                   | Characteristic                                                   | Sym                      | Min              | Тур†                      | Max                  | Units                                                                                                                                                                                          | Conditions                                                                                                                                                                                                                                                                                                                            |

| D001<br>D001A                  | Supply Voltage                                                   | Vdd                      | 4.0<br>4.5       | -                         | 6.0<br>5.5           | V<br>V                                                                                                                                                                                         | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                                                                                                                                                               |