#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I²C, SPI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                    |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c73a-04i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 3-3: PIC16C74/74A/77 PINOUT DESCRIPTION (Cont.'d)

| Pin Name          | DIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                            |

|-------------------|-------------|--------------|-------------|---------------|-----------------------|--------------------------------------------------------------------------------------------------------|

|                   |             |              |             |               |                       | PORTC is a bi-directional I/O port.                                                                    |

| RC0/T1OSO/T1CKI   | 15          | 16           | 32          | I/O           | ST                    | RC0 can also be the Timer1 oscillator output or a<br>Timer1 clock input.                               |

| RC1/T1OSI/CCP2    | 16          | 18           | 35          | I/O           | ST                    | RC1 can also be the Timer1 oscillator input or<br>Capture2 input/Compare2 output/PWM2 output.          |

| RC2/CCP1          | 17          | 19           | 36          | I/O           | ST                    | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                    |

| RC3/SCK/SCL       | 18          | 20           | 37          | I/O           | ST                    | RC3 can also be the synchronous serial clock input/<br>output for both SPI and I <sup>2</sup> C modes. |

| RC4/SDI/SDA       | 23          | 25           | 42          | I/O           | ST                    | RC4 can also be the SPI Data In (SPI mode) or data I/O ( $I^2$ C mode).                                |

| RC5/SDO           | 24          | 26           | 43          | I/O           | ST                    | RC5 can also be the SPI Data Out (SPI mode).                                                           |

| RC6/TX/CK         | 25          | 27           | 44          | I/O           | ST                    | RC6 can also be the USART Asynchronous Transmit or<br>Synchronous Clock.                               |

| RC7/RX/DT         | 26          | 29           | 1           | I/O           | ST                    | RC7 can also be the USART Asynchronous Receive or<br>Synchronous Data.                                 |

|                   |             |              |             |               |                       | PORTD is a bi-directional I/O port or parallel slave port when interfacing to a microprocessor bus.    |

| RD0/PSP0          | 19          | 21           | 38          | I/O           | ST/TTL <sup>(3)</sup> | when interfacing to a microprocessor bus.                                                              |

| RD1/PSP1          | 20          | 21           | 39          | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD2/PSP2          | 20          | 22           | 40          | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD3/PSP3          | 22          | 23           | 41          | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD4/PSP4          | 27          | 30           | 2           | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD5/PSP5          | 28          | 31           | 3           | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD6/PSP6          | 29          | 32           | 4           | 1/O           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD7/PSP7          | 30          | 33           | 5           | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

|                   |             |              |             | 1/0           | OI/ITE                | PORTE is a bi-directional I/O port.                                                                    |

| RE0/RD/AN5        | 8           | 9            | 25          | I/O           | ST/TTL <sup>(3)</sup> | RE0 can also be read control for the parallel slave port,<br>or analog input5.                         |

| RE1/WR/AN6        | 9           | 10           | 26          | I/O           | ST/TTL <sup>(3)</sup> | RE1 can also be write control for the parallel slave port, or analog input6.                           |

| RE2/CS/AN7        | 10          | 11           | 27          | I/O           | ST/TTL <sup>(3)</sup> | RE2 can also be select control for the parallel slave port, or analog input7.                          |

| Vss               | 12,31       | 13,34        | 6,29        | Р             |                       | Ground reference for logic and I/O pins.                                                               |

| Vdd               | 11,32       | 12,35        | 7,28        | Р             | _                     | Positive supply for logic and I/O pins.                                                                |

| NC                | —           | 1,17,28,     | 12,13,      |               |                       | These pins are not internally connected. These pins should                                             |

|                   |             | 40           | 33,34       |               |                       | be left unconnected.                                                                                   |

| Legend: I = input | 0 = oi      | •            |             |               | put/output            | P = power                                                                                              |

|                   |             | lot used     |             |               | TL input              | ST = Schmitt Trigger input<br>external interrupt.                                                      |

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

This buffer is a Schmitt Trigger input when used in serial programming mode.

This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel

Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

# 5.5 PORTE and TRISE Register Applicable Devices 72/73/73A/74/74A/76/77

PORTE has three pins RE0/RD/AN5, RE1/WR/AN6 and RE2/CS/AN7, which are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers.

I/O PORTE becomes control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs) and that register ADCON1 is configured for digital I/O. In this mode the input buffers are TTL.

Figure 5-9 shows the TRISE register, which also controls the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. The operation of these pins is selected by control bits in the ADCON1 register. When selected as an analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

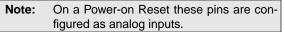

### FIGURE 5-8: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

#### FIGURE 5-9: TRISE REGISTER (ADDRESS 89h)

|             | <b>D</b> 0                                                                                                                                                            | D AAA A                                                                                                                                                                 | <b>D</b> 444 a                                      |             |             | <b>D</b> 444 4 | <b>D</b> 444 4 |                   |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------|-------------|----------------|----------------|-------------------|--|--|--|

| R-0         | R-0                                                                                                                                                                   | R/W-0                                                                                                                                                                   | R/W-0                                               | U-0         | R/W-1       | R/W-1          | R/W-1          |                   |  |  |  |

| IBF<br>bit7 | OBF     IBOV     PSPMODE     —     bit2     bit1     bit0     R     = Readable bit       bit0     U     = Unimplemented bit, read as '0'     - n = Value at POR reset |                                                                                                                                                                         |                                                     |             |             |                |                |                   |  |  |  |

| bit 7 :     | 1 = A word                                                                                                                                                            | <ul> <li>IBF: Input Buffer Full Status bit</li> <li>1 = A word has been received and is waiting to be read by the CPU</li> <li>0 = No word has been received</li> </ul> |                                                     |             |             |                |                |                   |  |  |  |

| bit 6:      | 1 = The ou                                                                                                                                                            | tput buffer                                                                                                                                                             | ull Status bit<br>still holds a pi<br>has been read |             | ritten word |                |                |                   |  |  |  |

| bit 5:      |                                                                                                                                                                       | occurred                                                                                                                                                                |                                                     |             |             | ,              | (must be cle   | ared in software) |  |  |  |

| bit 4:      | PSPMODE<br>1 = Paralle<br>0 = Genera                                                                                                                                  | I slave por                                                                                                                                                             |                                                     | de Select b | bit         |                |                |                   |  |  |  |

| bit 3:      | Unimplem                                                                                                                                                              | ented: Re                                                                                                                                                               | ad as '0'                                           |             |             |                |                |                   |  |  |  |

| bit 2:      | PORTE Data Direction Bits<br>Bit2: Direction Control bit for pin RE2/CS/AN7<br>1 = Input<br>0 = Output                                                                |                                                                                                                                                                         |                                                     |             |             |                |                |                   |  |  |  |

| bit 1:      | Bit1: Direction Control bit for pin RE1/WR/AN6<br>1 = Input<br>0 = Output                                                                                             |                                                                                                                                                                         |                                                     |             |             |                |                |                   |  |  |  |

| bit 0:      | <b>Bit0</b> : Direction Control bit for pin RE0/RD/AN5<br>1 = Input<br>0 = Output                                                                                     |                                                                                                                                                                         |                                                     |             |             |                |                |                   |  |  |  |

٦

#### FIGURE 11-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)

| R/W-0    | R/W-0                                                                | R/W-0                                                                   | R/W-0                                                                            | R/W-0                                                                        | R/W-0                                    | R/W-0                    | R/W-0                        |                                                                                                                           |

|----------|----------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------|--------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| WCOL     | SSPOV                                                                | SSPEN                                                                   | CKP                                                                              | SSPM3                                                                        | SSPM2                                    | SSPM1                    | SSPM0                        | R = Readable bit                                                                                                          |

| bit7     |                                                                      |                                                                         |                                                                                  |                                                                              |                                          |                          | bit0                         | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset                                      |

| bit 7:   | WCOL: W                                                              | rite Collisio                                                           | n Detect l                                                                       | oit                                                                          |                                          |                          |                              |                                                                                                                           |

|          | 1 = The S                                                            | SPBUF reg                                                               | jister is wr                                                                     |                                                                              | it is still tr                           | ansmitting               | the previou                  | us word                                                                                                                   |

| bit 6:   | SSPOV: R                                                             | eceive Ove                                                              | erflow Det                                                                       | ect bit                                                                      |                                          |                          |                              |                                                                                                                           |

|          | the data ir<br>BUF, even                                             | byte is rece<br>SSPSR re<br>if only train<br>new rece                   | egister is I                                                                     | ost. Overfl<br>data, to av                                                   | ow can on<br>oid setting                 | ly occur in<br>overflow. | slave mod<br>In master       | revious data. In case of overflow<br>e. The user must read the SSP<br>mode the overflow bit is not se<br>SSPBUF register. |

|          | In I <sup>2</sup> C mod                                              | <u>de</u>                                                               |                                                                                  |                                                                              |                                          |                          |                              |                                                                                                                           |

|          | 1 = A byte<br>in transmit<br>0 = No ove                              | mode. SS                                                                |                                                                                  |                                                                              |                                          |                          |                              | us byte. SSPOV is a "don't care                                                                                           |

| bit 5:   | SSPEN: S                                                             | ynchronou                                                               | s Serial P                                                                       | ort Enable                                                                   | bit                                      |                          |                              |                                                                                                                           |

|          | $\frac{\text{In SPI model}}{1 = \text{Enable}}$ $0 = \text{Disable}$ | es serial po                                                            |                                                                                  |                                                                              |                                          |                          | s serial por<br>pins         | t pins                                                                                                                    |

|          | 0 = Disabl                                                           | es the seria                                                            | ort and co                                                                       | nfigures th                                                                  | nese pins a                              | as I/O port              | pins                         | ial port pins<br>s input or output.                                                                                       |

| bit 4:   | CKP: Cloc                                                            | k Polarity                                                              | Select bit                                                                       |                                                                              |                                          |                          |                              |                                                                                                                           |

|          |                                                                      | ate for cloc                                                            |                                                                                  |                                                                              |                                          |                          |                              | receive on rising edge.<br>ceive on falling edge.                                                                         |

|          | $\frac{\ln l^2 C \mod SCK \text{ relea}}{1 = \text{Enable}}$         | se control<br>e clock                                                   | -11                                                                              |                                                                              | 4                                        |                          | . (: )                       |                                                                                                                           |

|          | 0 = Holds                                                            |                                                                         |                                                                                  | , ,                                                                          |                                          |                          | o time)                      |                                                                                                                           |

| bit 3-0: | 0001 = SF<br>0010 = SF<br>0011 = SF<br>0100 = SF<br>0101 = SF        | PI master n<br>PI master n<br>PI master n<br>PI master n<br>PI slave mo | node, cloc<br>node, cloc<br>node, cloc<br>node, cloc<br>ode, clock<br>ode, clock | k = Fosc/4<br>k = Fosc/1<br>k = Fosc/6<br>k = TMR2<br>= SCK pir<br>= SCK pir | l<br>6<br>64<br>output/2<br>1. SS pin co | ontrol enal              |                              | n be used as I/O pin.                                                                                                     |

|          | $0111 =  ^{2}(0)$<br>$1011 =  ^{2}(0)$<br>$1110 =  ^{2}(0)$          | C slave mo<br>C firmware<br>C slave mo                                  | de, 10-bit<br>controlled<br>de, 7-bit a                                          | address<br>I Master M<br>ddress wi                                           | th start an                              | d stop bit i             | nterrupts er<br>interrupts o |                                                                                                                           |

Г

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON register, and then set bit SSPEN. This configures the SDI, SDO, SCK, and SS pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value. An example would be in master mode where you are only sending data (to a display driver), then both SDI and SS could be used as general purpose outputs by clearing their corresponding TRIS register bits.

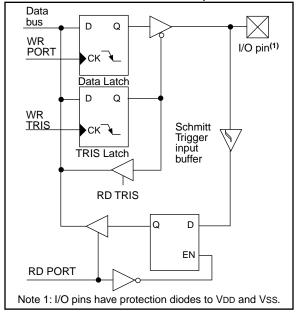

Figure 11-10 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge, and latched on the opposite edge of the clock. Both processors should be programmed to same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application firmware. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- Master sends dummy data Slave sends data

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2) is to broadcast data by the firmware protocol.

In master mode the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SCK output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "line activity monitor" mode.

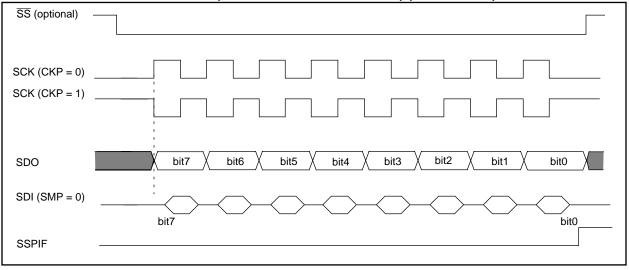

In slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched the interrupt flag bit SSPIF (PIR1<3>) is set.

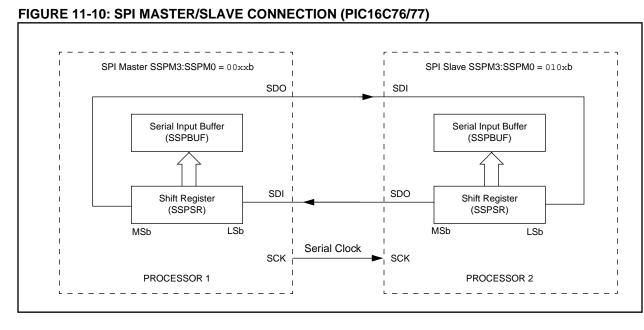

The clock polarity is selected by appropriately programming bit CKP (SSPCON<4>). This then would give waveforms for SPI communication as shown in Figure 11-11, Figure 11-12, and Figure 11-13 where the MSB is transmitted first. In master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum bit clock frequency (at 20 MHz) of 5 MHz. When in slave mode the external clock must meet the minimum high and low times.

In sleep mode, the slave can transmit and receive data and wake the device from sleep.

The  $\overline{SS}$  pin allows a synchronous slave mode. The SPI must be in slave mode (SSPCON<3:0> = 04h) and the TRISA<5> bit must be set for the synchronous slave mode to be enabled. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. If the  $\overline{SS}$  pin is taken low without resetting SPI mode, the transmission will continue from the point at which it was taken high. External pull-up/ pull-down resistors may be desirable, depending on the application.

| Note: | When the SPI is in Slave Mode with $\overline{SS}$ pin<br>control enabled, (SSPCON<3:0> = 0100)<br>the SPI module will reset if the $\overline{SS}$ pin is set<br>to VDD. |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | If the SPI is used in Slave Mode with                                                                                                                                     |

CKE = '1', then the SS pin control must be enabled. To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as

be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

#### FIGURE 11-11: SPI MODE TIMING, MASTER MODE (PIC16C76/77)

#### FIGURE 11-12: SPI MODE TIMING (SLAVE MODE WITH CKE = 0) (PIC16C76/77)

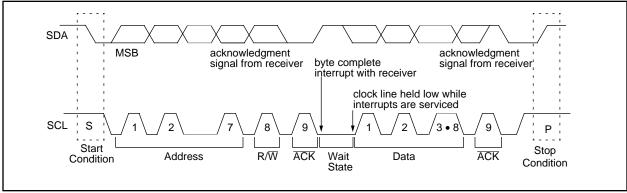

#### 11.4.2 ADDRESSING I<sup>2</sup>C DEVICES

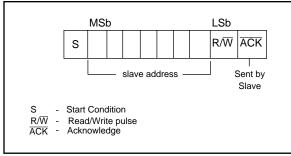

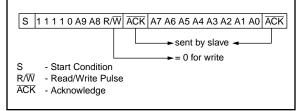

There are two address formats. The simplest is the 7-bit address format with a  $R/\overline{W}$  bit (Figure 11-15). The more complex is the 10-bit address with a  $R/\overline{W}$  bit (Figure 11-16). For 10-bit address format, two bytes must be transmitted with the first five bits specifying this to be a 10-bit address.

#### FIGURE 11-15: 7-BIT ADDRESS FORMAT

#### FIGURE 11-16: I<sup>2</sup>C 10-BIT ADDRESS FORMAT

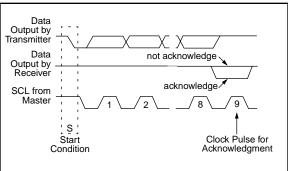

#### 11.4.3 TRANSFER ACKNOWLEDGE

All data must be transmitted per byte, with no limit to the number of bytes transmitted per data transfer. After each byte, the slave-receiver generates an acknowledge bit ( $\overline{ACK}$ ) (Figure 11-17). When a slave-receiver doesn't acknowledge the slave address or received data, the master must abort the transfer. The slave must leave SDA high so that the master can generate the STOP condition (Figure 11-14).

#### FIGURE 11-17: SLAVE-RECEIVER ACKNOWLEDGE

If the master is receiving the data (master-receiver), it generates an acknowledge signal for each received byte of data, except for the last byte. To signal the end of data to the slave-transmitter, the master does not generate an acknowledge (not acknowledge). The slave then releases the SDA line so the master can generate the STOP condition. The master can also generate the STOP condition during the acknowledge pulse for valid termination of data transfer.

If the slave needs to delay the transmission of the next byte, holding the SCL line low will force the master into a wait state. Data transfer continues when the slave releases the SCL line. This allows the slave to move the received data or fetch the data it needs to transfer before allowing the clock to start. This wait state technique can also be implemented at the bit level, Figure 11-18. The slave will inherently stretch the clock, when it is a transmitter, but will not when it is a receiver. The slave will have to clear the SSPCON<4> bit to enable clock stretching when it is a receiver.

#### FIGURE 11-18: DATA TRANSFER WAIT STATE

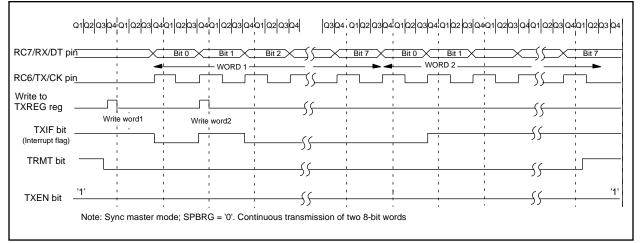

#### TABLE 12-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address | Name  | Bit 7                | Bit 6                       | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|-------|----------------------|-----------------------------|---------|-------|-------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF                        | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA | SPEN                 | RX9                         | SREN    | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                 |

| 19h     | TXREG | USART Tra            | ansmit Re                   | egister |       |       |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE                        | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA | CSRC                 | TX9                         | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | SPBRG | Baud Rate            | aud Rate Generator Register |         |       |       |        |        |        | 0000 0000                | 0000 0000                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for Synchronous Master Transmission. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

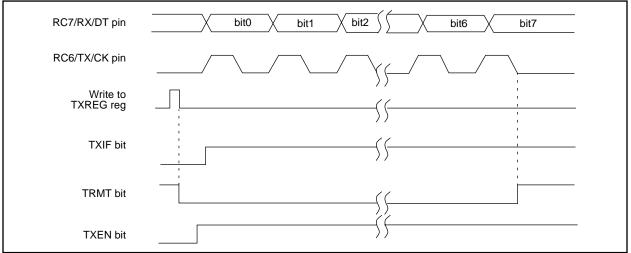

#### FIGURE 12-12: SYNCHRONOUS TRANSMISSION

#### FIGURE 12-13: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

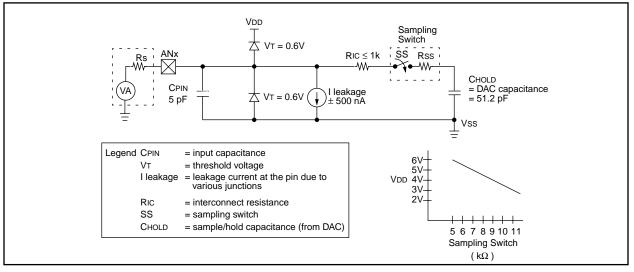

#### 13.1 A/D Acquisition Requirements

### Applicable Devices 72 73 73 74 74 76 77

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 13-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), Figure 13-4. The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 10 k $\Omega$ . After the analog input channel is selected (changed) this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 13-1 may be used. This equation calculates the acquisition time to within 1/2 LSb error is used (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified accuracy.

### EQUATION 13-1: A/D MINIMUM CHARGING TIME

$VHOLD = (VREF - (VREF/512)) \bullet (1 - e^{(-TCAP/CHOLD(RIC + RSS + RS))})$

Given: VHOLD = (VREF/512), for 1/2 LSb resolution

The above equation reduces to:

$TCAP = -(51.2 \text{ pF})(1 \text{ k}\Omega + \text{Rss} + \text{Rs}) \ln(1/511)$

Example 13-1 shows the calculation of the minimum required acquisition time TACQ. This calculation is based on the following system assumptions.

CHOLD = 51.2 pF

Rs = 10 kΩ

1/2 LSb error

#### FIGURE 13-4: ANALOG INPUT MODEL

$VDD = 5V \rightarrow Rss = 7 \text{ k}\Omega$

Temp (application system max.) = 50°C

VHOLD = 0 @ t = 0

- Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- Note 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **Note 3:** The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

- Note 4: After a conversion has completed, a 2.0TAD delay must complete before acquisition can begin again. During this time the holding capacitor is not connected to the selected A/D input channel.

#### EXAMPLE 13-1: CALCULATING THE MINIMUM REQUIRED ACQUISITION TIME

- TACQ = Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient

- TACQ =  $5 \mu s + TCAP + [(Temp 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$

- TCAP = -CHOLD (Ric + Rss + Rs) ln(1/511)-51.2 pF (1 k $\Omega$  + 7 k $\Omega$  + 10 k $\Omega$ ) ln(0.0020) -51.2 pF (18 k $\Omega$ ) ln(0.0020) -0.921 µs (-6.2364) 5.747 µs

- TACQ = 5 μs + 5.747 μs + [(50°C 25°C)(0.05 μs/°C)] 10.747 μs + 1.25 μs 11.997 μs

#### 14.4.5 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 14-10, Figure 14-11, and Figure 14-12 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 14-11). This is useful for testing purposes or to synchronize more than one PIC16CXX device operating in parallel.

Table 14-7 shows the reset conditions for some special function registers, while Table 14-8 shows the reset conditions for all the registers.

#### 14.4.6 POWER CONTROL/STATUS REGISTER (PCON)

| -  | •  | cabl |    |     |    |    |

|----|----|------|----|-----|----|----|

| 72 | 73 | 73A  | 74 | 74A | 76 | 77 |

The Power Control/Status Register, PCON has up to two bits, depending upon the device. Bit0 is not implemented on the PIC16C73 or PIC16C74.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent resets to see if bit BOR cleared, indicating a BOR occurred. The BOR bit is a "Don't Care" bit and is not necessarily predictable if the Brown-out Reset circuitry is disabled (by clearing bit BODEN in the Configuration Word).

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

#### TABLE 14-3: TIME-OUT IN VARIOUS SITUATIONS, PIC16C73/74

| Oscillator Configuration | Powe             | Wake-up from SLEEP |           |

|--------------------------|------------------|--------------------|-----------|

|                          | PWRTE = 1        | PWRTE = 0          |           |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc           | 1024 Tosc |

| RC                       | 72 ms            | _                  |           |

#### TABLE 14-4: TIME-OUT IN VARIOUS SITUATIONS, PIC16C72/73A/74A/76/77

| Oscillator Configuration | Power-up         |           | Brown-out        | Wake-up from SLEEP |

|--------------------------|------------------|-----------|------------------|--------------------|

|                          | PWRTE = 0        | PWRTE = 1 | Brown-out        |                    |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc           |

| RC                       | 72 ms            |           | 72 ms            | _                  |

#### TABLE 14-5: STATUS BITS AND THEIR SIGNIFICANCE, PIC16C73/74

| POR | TO | PD |                                                         |

|-----|----|----|---------------------------------------------------------|

| 0   | 1  | 1  | Power-on Reset                                          |

| 0   | 0  | х  | Illegal, TO is set on POR                               |

| 0   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0  | 1  | WDT Reset                                               |

| 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

Legend: u = unchanged, x = unknown

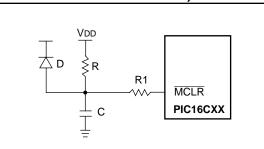

#### FIGURE 14-13: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

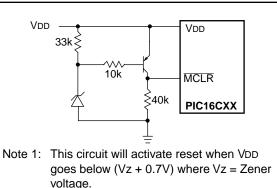

#### FIGURE 14-14: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- 2: Internal brown-out detection on the PIC16C72/73A/74A/76/77 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

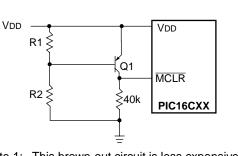

#### FIGURE 14-15: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

- 2: Internal brown-out detection on the PIC16C72/73A/74A/76/77 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

# PIC16C7X

| IORWF             | Inclusive                                                        | e OR W v                     | with f           |                      |

|-------------------|------------------------------------------------------------------|------------------------------|------------------|----------------------|

| Syntax:           | [ label ]                                                        | IORWF                        | f,d              |                      |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$ | 27                           |                  |                      |

| Operation:        | (W) .OR.                                                         | (f) $\rightarrow$ (de        | estination       | )                    |

| Status Affected:  | Z                                                                |                              |                  |                      |

| Encoding:         | 00                                                               | 0100                         | dfff             | ffff                 |

| Description:      | Inclusive C<br>ter 'f'. If 'd'<br>W register<br>back in reg      | is 0 the re<br>. If 'd' is 1 | sult is plac     | ced in the           |

| Words:            | 1                                                                |                              |                  |                      |

| Cycles:           | 1                                                                |                              |                  |                      |

| Q Cycle Activity: | Q1                                                               | Q2                           | Q3               | Q4                   |

|                   | Decode                                                           | Read<br>register<br>'f'      | Process<br>data  | Write to destination |

| Example           | IORWF                                                            |                              | RESULT,          | 0                    |

|                   | Before In                                                        |                              |                  |                      |

|                   |                                                                  | RESULT<br>W                  | = 0x13<br>= 0x91 | -                    |

|                   | After Inst                                                       |                              |                  | 3                    |

| MOVLW             | Move Literal to W                                                                          |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:           | [ <i>label</i> ] MOVLW k                                                                   |  |  |  |  |

| Operands:         | $0 \le k \le 255$                                                                          |  |  |  |  |

| Operation:        | $k \rightarrow (W)$                                                                        |  |  |  |  |

| Status Affected:  | None                                                                                       |  |  |  |  |

| Encoding:         | 11 00xx kkkk kkkk                                                                          |  |  |  |  |

| Description:      | The eight bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |  |  |  |  |

| Words:            | 1                                                                                          |  |  |  |  |

| Cycles:           | 1                                                                                          |  |  |  |  |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                |  |  |  |  |

|                   | Decode Read literal 'k' Process Write to W                                                 |  |  |  |  |

| Example           | MOVLW $0x5A$<br>After Instruction<br>W = 0x5A                                              |  |  |  |  |

| MOVF              | Move f                                                                                  |                                                      |                                                             |                                                    |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|

| Syntax:           | [ <i>label</i> ] MOVF f,d                                                               |                                                      |                                                             |                                                    |  |  |  |  |  |

| Operands:         | $0 \le f \le 127$<br>$d \in [0,1]$                                                      |                                                      |                                                             |                                                    |  |  |  |  |  |

| Operation:        | $(f) \rightarrow (de)$                                                                  | stination                                            | )                                                           |                                                    |  |  |  |  |  |

| Status Affected:  | Z                                                                                       |                                                      |                                                             |                                                    |  |  |  |  |  |

| Encoding:         | 00                                                                                      | 1000                                                 | dfff                                                        | ffff                                               |  |  |  |  |  |

| Description:      | The contendestination<br>of d. If $d =$<br>d = 1, the<br>itself. $d = 1$<br>ter since s | n dependa<br>0, destina<br>destinatio<br>I is useful | ant upon th<br>ition is W r<br>n is file reg<br>to test a f | ne status<br>egister. If<br>gister f<br>ile regis- |  |  |  |  |  |

| Words:            | 1                                                                                       |                                                      |                                                             |                                                    |  |  |  |  |  |

| Cycles:           | 1                                                                                       |                                                      |                                                             |                                                    |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                      | Q2                                                   | Q3                                                          | Q4                                                 |  |  |  |  |  |

|                   | Decode                                                                                  | Read<br>register<br>'f'                              | Process<br>data                                             | Write to destination                               |  |  |  |  |  |

| Example           | MOVF                                                                                    | ,                                                    | 0                                                           |                                                    |  |  |  |  |  |

|                   |                                                                                         |                                                      | ie in FSR i                                                 | register                                           |  |  |  |  |  |

| MOVWF             | Move W to f       |                         |                 |                       |  |  |  |  |

|-------------------|-------------------|-------------------------|-----------------|-----------------------|--|--|--|--|

| Syntax:           | [ label ]         | MOVW                    | = f             |                       |  |  |  |  |

| Operands:         | $0 \le f \le 12$  | 27                      |                 |                       |  |  |  |  |

| Operation:        | $(W) \to (f)$     |                         |                 |                       |  |  |  |  |

| Status Affected:  | None              |                         |                 |                       |  |  |  |  |

| Encoding:         | 00                | 0000                    | lfff            | ffff                  |  |  |  |  |

| Description:      | Move data<br>'f'. | from W r                | egister to      | register              |  |  |  |  |

| Words:            | 1                 |                         |                 |                       |  |  |  |  |

| Cycles:           | 1                 |                         |                 |                       |  |  |  |  |

| Q Cycle Activity: | Q1                | Q2                      | Q3              | Q4                    |  |  |  |  |

|                   | Decode            | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |  |  |  |

| Example           | MOVWF             | OPTIC                   | DN_REG          |                       |  |  |  |  |

|                   | Before In         |                         |                 | -                     |  |  |  |  |

|                   |                   | OPTION<br>W             | = 0xF<br>= 0x4  | -                     |  |  |  |  |

|                   | After Inst        | ruction                 |                 |                       |  |  |  |  |

|                   |                   | OPTION                  |                 |                       |  |  |  |  |

|                   |                   | W                       | = 0x4           | F                     |  |  |  |  |

#### Applicable Devices 72 73 73A 74 74A 76 77

#### 17.4 **Timing Parameter Symbology**

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2p             | pS                                      | 3. TCC:ST | (I <sup>2</sup> C specifications only) |

|-----------------------|-----------------------------------------|-----------|----------------------------------------|

| 2. TppS               |                                         | 4. Ts     | (I <sup>2</sup> C specifications only) |

| т                     |                                         |           |                                        |

| F                     | Frequency                               | Т         | Time                                   |

| Lowerca               | ase letters (pp) and their meanings:    |           |                                        |

| рр                    |                                         |           |                                        |

| CC                    | CCP1                                    | OSC       | OSC1                                   |

| ck                    | CLKOUT                                  | rd        | RD                                     |

| CS                    | CS                                      | rw        | $\overline{RD}$ or $\overline{WR}$     |

| di                    | SDI                                     | SC        | SCK                                    |

| do                    | SDO                                     | SS        | SS                                     |

| dt                    | Data in                                 | tO        | TOCKI                                  |

| io                    | I/O port                                | t1        | T1CKI                                  |

| mc                    | MCLR                                    | wr        | WR                                     |

| Upperca               | ase letters and their meanings:         |           |                                        |

| S                     |                                         |           |                                        |

| F                     | Fall                                    | P         | Period                                 |

| Н                     | High                                    | R         | Rise                                   |

| I                     | Invalid (Hi-impedance)                  | V         | Valid                                  |

| L                     | Low                                     | Z         | Hi-impedance                           |

| I <sup>2</sup> C only |                                         |           |                                        |

| AA                    | output access                           | High      | High                                   |

| BUF                   | Bus free                                | Low       | Low                                    |

| Tcc:st (              | (I <sup>2</sup> C specifications only)  | I         |                                        |

| CC                    |                                         |           |                                        |

| HD                    | Hold                                    | SU        | Setup                                  |

| ST                    |                                         |           | Comp                                   |

| DAT                   | DATA input hold                         | STO       | STOP condition                         |

| STA                   | START condition                         |           |                                        |

|                       |                                         |           |                                        |

| FIGURE 1              | 17-1: LOAD CONDITIONS                   |           |                                        |

|                       | Load condition 1                        |           | Load condition 2                       |

|                       | N = = /0                                |           |                                        |

|                       |                                         |           |                                        |

|                       | J                                       |           |                                        |

|                       | $\leq$ RL                               |           |                                        |

|                       | $ \leq $                                | N         |                                        |

|                       | I → I                                   |           | X                                      |

|                       |                                         | F         |                                        |

|                       | • • • • • • • • • • • • • • • • • • • • | ,         | ··· ↓                                  |

|                       | Vss                                     |           | Vss                                    |

|                       | $RL$ = 464 $\Omega$                     |           |                                        |

|                       |                                         |           |                                        |

|                       | $C_L = 50 \text{ pF}$ for all pins ex   | cept 0502 |                                        |

15 pF for OSC2 output

Applicable Devices 72 73 73A 74 74A 76 77

#### 18.0 ELECTRICAL CHARACTERISTICS FOR PIC16C73/74

#### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                                    | 55 to +125°C                       |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage temperature                                                                                                               | 65°C to +150°C                     |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                                                | 0.3V to (VDD + 0.3V)               |

| Voltage on VDD with respect to Vss                                                                                                | 0.3 to +7.5V                       |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                      | 0 to +14V                          |

| Voltage on RA4 with respect to Vss                                                                                                | 0 to +14V                          |

| Total power dissipation (Note 1)                                                                                                  | 1.0W                               |

| Maximum current out of Vss pin                                                                                                    | 300 mA                             |

| Maximum current into VDD pin                                                                                                      | 250 mA                             |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                                      |                                    |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                                                    |                                    |

| Maximum output current sunk by any I/O pin                                                                                        | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                                                     | 25 mA                              |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                                               | 200 mA                             |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                                            | 200 mA                             |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                                                       | 200 mA                             |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                                                    | 200 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\Sigma$ IOH} + $\Sigma$ {(VDD -                   | Voh) x Ioh} + $\Sigma$ (Vol x Iol) |

| Note $0$ , $\lambda$ (alternative balance) (as a table $\overline{\mathbf{MOLD}}$ are inducting summation matching the $0$ or $0$ |                                    |

- **Note 2:** Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

- Note 3: PORTD and PORTE are not implemented on the PIC16C73.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### TABLE 18-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C73-04<br>PIC16C74-04                                                                                                                          | PIC16C73-10<br>PIC16C74-10                                                                                                                         | PIC16C73-20<br>PIC16C74-20                                                                                                                         | PIC16LC73-04<br>PIC16LC74-04                                                                               | JW Devices                                                                                                                                         |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                            | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 3.0V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 13.5 μA max. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                           |

| хт  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                            | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 3.0V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 13.5 μA max. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                           |

| HS  | VDD:         4.5V to 5.5V           IDD:         13.5 mA typ. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         4 MHz max. | VDD:         4.5V to 5.5V           IDD:         15 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         10 MHz max. | VDD:         4.5V to 5.5V           IDD:         30 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         20 MHz max. | Not recommended for<br>use in HS mode                                                                      | VDD:         4.5V to 5.5V           IDD:         30 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         20 MHz max. |

| LP  | VDD: 4.0V to 6.0V<br>IDD: 52.5 μA typ. at<br>32 kHz, 4.0V<br>IPD: 0.9 μA typ. at 4.0V<br>Freq: 200 kHz max.                                         | Not recommended for<br>use in LP mode                                                                                                              | Not recommended for<br>use in LP mode                                                                                                              | VDD: 3.0V to 6.0V<br>IDD: 48 μA max. at<br>32 kHz, 3.0V<br>IPD: 13.5 μA max. at 3.0V<br>Freq: 200 kHz max. | VDD: 3.0V to 6.0V<br>IDD: 48 μA max. at<br>32 kHz, 3.0V<br>IPD: 13.5 μA max. at 3.0V<br>Freq: 200 kHz max.                                         |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

Applicable Devices

72

73

73A

74

74A

76

77

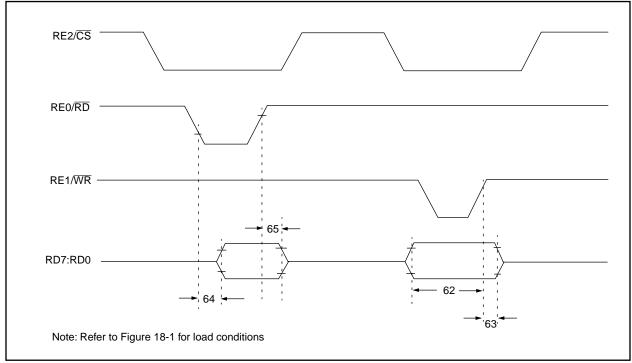

#### FIGURE 18-7: PARALLEL SLAVE PORT TIMING (PIC16C74)

#### TABLE 18-7: PARALLEL SLAVE PORT REQUIREMENTS (PIC16C74)

| Parameter<br>No. | Sym      | Characteristic                                                                          | Min                                                                       | Тур† | Max | Units | Conditions |  |

|------------------|----------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------|-----|-------|------------|--|

| 62               | TdtV2wrH | Data in valid before $\overline{WR}\uparrow$ or $\overline{CS}\uparrow$ (setup time     | 20                                                                        | —    | -   | ns    |            |  |

| 63*              | TwrH2dtl | $\overline{WR}^{\uparrow}$ or $\overline{CS}^{\uparrow}$ to data–in invalid (hold time) | PIC16 <b>C</b> 74                                                         | 20   | —   | —     | ns         |  |

|                  |          |                                                                                         | PIC16 <b>LC</b> 74                                                        | 35   | —   | —     | ns         |  |

| 64               | TrdL2dtV | $\overline{RD}\downarrow$ and $\overline{CS}\downarrow$ to data–out valid               | $\overline{RD}\downarrow$ and $\overline{CS}\downarrow$ to data–out valid |      |     | 80    | ns         |  |

| 65               | TrdH2dtl | $\overline{RD}$ or $\overline{CS}$ to data–out invalid                                  | 10                                                                        | —    | 30  | ns    |            |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## PIC16C7X

Applicable Devices 72 73 73A 74 74A 76 77

#### 19.0 ELECTRICAL CHARACTERISTICS FOR PIC16C73A/74A

#### Absolute Maximum Ratings †

| -                                                                                                           |                                    |

|-------------------------------------------------------------------------------------------------------------|------------------------------------|

| Ambient temperature under bias                                                                              | 55 to +125°C                       |

| Storage temperature                                                                                         | 65°C to +150°C                     |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                          | 0.3V to (VDD + 0.3V)               |

| Voltage on VDD with respect to Vss                                                                          | 0.3 to +7.5V                       |

| Voltage on MCLR with respect to Vss (Note 2)                                                                | 0 to +14V                          |

| Voltage on RA4 with respect to Vss                                                                          | 0 to +14V                          |

| Total power dissipation (Note 1)                                                                            | 1.0W                               |

| Maximum current out of Vss pin                                                                              | 300 mA                             |

| Maximum current into VDD pin                                                                                | 250 mA                             |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                | ±20 mA                             |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                              |                                    |

| Maximum output current sunk by any I/O pin                                                                  | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                               | 25 mA                              |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                         | 200 mA                             |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                      | 200 mA                             |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                                 | 200 mA                             |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                              | 200 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - | VOH) x IOH} + $\Sigma$ (VOI x IOL) |

|                                                                                                             |                                    |

**Note 2:** Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

Note 3: PORTD and PORTE are not implemented on the PIC16C73A.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### TABLE 19-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C73A-04<br>PIC16C74A-04                                                                                                                        | PIC16C73A-10<br>PIC16C74A-10                                                                                                                       | PIC16C73A-20<br>PIC16C74A-20                                                                                                                       | PIC16LC73A-04<br>PIC16LC74A-04                                                                            | JW Devices                                                                                                                                         |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                                                            | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 2.5V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 5 μA max. at 3V<br>Freq: 4 MHz max.                 | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                                                           |