Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                               |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c73a-10i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|            |                                                 | PIC16C710                           | PIC16C71            | PIC16C711                           | PIC16C715                           | PIC16C72                   | PIC16CR72 <sup>(1)</sup>   |

|------------|-------------------------------------------------|-------------------------------------|---------------------|-------------------------------------|-------------------------------------|----------------------------|----------------------------|

| Clock      | Maximum Frequency<br>of Operation (MHz)         | 20                                  | 20                  | 20                                  | 20                                  | 20                         | 20                         |

|            | EPROM Program Memory<br>(x14 words)             | 512                                 | 1K                  | 1K                                  | 2К                                  | 2К                         | —                          |

| lemory     | ROM Program Memory<br>(14K words)               | _                                   | _                   | _                                   | _                                   | _                          | 2К                         |

|            | Data Memory (bytes)                             | 36                                  | 36                  | 68                                  | 128                                 | 128                        | 128                        |

|            | Timer Module(s)                                 | TMR0                                | TMR0                | TMR0                                | TMR0                                | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2     |

| eripherals | Capture/Compare/<br>PWM Module(s)               | —                                   | _                   | —                                   | —                                   | 1                          | 1                          |

|            | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | _                                   | _                   | —                                   | —                                   | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C       |

|            | Parallel Slave Port                             | _                                   | —                   | —                                   | _                                   | _                          | —                          |

|            | A/D Converter (8-bit) Channels                  | 4                                   | 4                   | 4                                   | 4                                   | 5                          | 5                          |

|            | Interrupt Sources                               | 4                                   | 4                   | 4                                   | 4                                   | 8                          | 8                          |

|            | I/O Pins                                        | 13                                  | 13                  | 13                                  | 13                                  | 22                         | 22                         |

|            | Voltage Range (Volts)                           | 3.0-6.0                             | 3.0-6.0             | 3.0-6.0                             | 3.0-5.5                             | 2.5-6.0                    | 3.0-5.5                    |

| atures     | In-Circuit Serial Programming                   | Yes                                 | Yes                 | Yes                                 | Yes                                 | Yes                        | Yes                        |

|            | Brown-out Reset                                 | Yes                                 | —                   | Yes                                 | Yes                                 | Yes                        | Yes                        |

|            | Packages                                        | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC, SSOP |

# TABLE 1-1: PIC16C7XX FAMILY OF DEVCES

|             |                                                   | PIC16C73A                   | PIC16C74A                                 | PIC16C76                    | PIC16C77                                  |

|-------------|---------------------------------------------------|-----------------------------|-------------------------------------------|-----------------------------|-------------------------------------------|

| Clock       | Maximum Frequency of Oper-<br>ation (MHz)         | 20                          | 20                                        | 20                          | 20                                        |

| Memory      | EPROM Program Memory<br>(x14 words)               | 4K                          | 4K                                        | 8K                          | 8K                                        |

|             | Data Memory (bytes)                               | 192                         | 192                                       | 368                         | 368                                       |

|             | Timer Module(s)                                   | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    |

| Peripherals | Capture/Compare/PWM Mod-<br>ule(s)                | 2                           | 2                                         | 2                           | 2                                         |

|             | Serial Port(s) (SPI/I <sup>2</sup> C, US-<br>ART) | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               |

|             | Parallel Slave Port                               | —                           | Yes                                       | —                           | Yes                                       |

|             | A/D Converter (8-bit) Channels                    | 5                           | 8                                         | 5                           | 8                                         |

|             | Interrupt Sources                                 | 11                          | 12                                        | 11                          | 12                                        |

|             | I/O Pins                                          | 22                          | 33                                        | 22                          | 33                                        |

|             | Voltage Range (Volts)                             | 2.5-6.0                     | 2.5-6.0                                   | 2.5-6.0                     | 2.5-6.0                                   |

| eatures     | In-Circuit Serial Programming                     | Yes                         | Yes                                       | Yes                         | Yes                                       |

|             | Brown-out Reset                                   | Yes                         | Yes                                       | Yes                         | Yes                                       |

|             | Packages                                          | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C7XX Family devices use serial programming with clock pin RB6 and data pin RB7.

Note 1: Please contact your local Microchip sales office for availability of these devices.

NOTES:

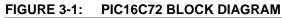

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXX uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture in which program and data are fetched from the same memory using the same bus. Separating program and data buses further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The table below lists program memory (EPROM) and data memory (RAM) for each PIC16C7X device.

| Device    | Program<br>Memory | Data Memory |

|-----------|-------------------|-------------|

| PIC16C72  | 2K x 14           | 128 x 8     |

| PIC16C73  | 4K x 14           | 192 x 8     |

| PIC16C73A | 4K x 14           | 192 x 8     |

| PIC16C74  | 4K x 14           | 192 x 8     |

| PIC16C74A | 4K x 14           | 192 x 8     |

| PIC16C76  | 8K x 14           | 368 x 8     |

| PIC16C77  | 8K x 14           | 386 x 8     |

The PIC16CXX can directly or indirectly address its register files or data memory. All special function registers, including the program counter, are mapped in the data memory. The PIC16CXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16CXX simple yet efficient. In addition, the learning curve is reduced significantly.

PIC16CXX devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between the data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow bit and a digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

# FIGURE 4-4: PIC16C72 REGISTER FILE MAP

| File<br>Address   | 3                     |                     | File<br>Address |

|-------------------|-----------------------|---------------------|-----------------|

| 00h               | INDF <sup>(1)</sup>   | INDF <sup>(1)</sup> | 80h             |

| 01h               | TMR0                  | OPTION              | 81h             |

| 02h               | PCL                   | PCL                 |                 |

| 03h               | STATUS                | STATUS              |                 |

| 04h               | FSR                   | FSR                 |                 |

| 05h               | PORTA                 | TRISA               | 85h             |

| 06h               | PORTB                 | TRISB               | 86h             |

| 07h               | PORTC                 | TRISC               |                 |

| 08h               |                       |                     |                 |

| 09h               |                       |                     | 89h             |

| 0Ah               | PCLATH                | PCLATH              | 8Ah             |

| 0Bh               | INTCON                | INTCON              | 8Bh             |

| 0Ch               | PIR1                  | PIE1                | 8Ch             |

| 0Dh               |                       |                     | 8Dh             |

| 0Eh               | TMR1L                 | PCON                | 8Eh             |

| 0Fh               | TMR1H                 |                     | 8Fh             |

| 10h               | T1CON                 |                     | 90h             |

| 11h               | TMR2                  |                     | 91h             |

| 12h               | T2CON                 | PR2                 | 92h             |

| 13h               | SSPBUF                | SSPADD              | 93h             |

| 14h               | SSPCON                | SSPSTAT             |                 |

| 15h               | CCPR1L                |                     | 95h             |

| 16h               | CCPR1H                |                     | 96h             |

| 17h               | CCP1CON               |                     | 97h             |

| 18h               |                       |                     | 98h             |

| 19h               |                       |                     | 99h             |

| 1Ah               |                       |                     | 9Ah             |

| 1Bh               |                       |                     | 9Bh             |

| 1Ch               |                       |                     | 9Ch             |

| 1Dh               |                       |                     | 9Dh             |

| 1Eh               | ADRES                 |                     | 9Eh             |

| 1Fh               | ADCON0                | ADCON1              | 9Fh             |

| 20h               |                       |                     | A0h             |

|                   | General<br>Purpose    | General<br>Purpose  |                 |

|                   | Register              | Register            |                 |

|                   | U U                   |                     | BFh             |

|                   |                       |                     | C0h             |

|                   |                       |                     |                 |

| 1                 |                       |                     |                 |

|                   |                       |                     |                 |

| 7Fh               |                       |                     | FFh             |

|                   | Bank 0                | Bank 1              |                 |

|                   |                       |                     |                 |

|                   | nimplemented data     | a memory locations  | s, read as      |

| '0'.<br>Note 1: 1 | Not a physical regis  | stor                |                 |

|                   | tot a priysical regit | лот.                |                 |

|                   |                       |                     |                 |

#### FIGURE 4-5: PIC16C73/73A/74/74A REGISTER FILE MAP

| REGISTER FILE MAP |                                                               |                                |                 |  |  |  |  |  |  |

|-------------------|---------------------------------------------------------------|--------------------------------|-----------------|--|--|--|--|--|--|

| File<br>Addres    | SS                                                            |                                | File<br>Address |  |  |  |  |  |  |

| 00h               | INDF <sup>(1)</sup>                                           | INDF <sup>(1)</sup>            | 80h             |  |  |  |  |  |  |

| 01h               | TMR0                                                          | OPTION                         |                 |  |  |  |  |  |  |

| 02h               | PCL                                                           | PCL                            | 82h             |  |  |  |  |  |  |

| 03h               | STATUS                                                        | STATUS                         | 83h             |  |  |  |  |  |  |

| 04h               | FSR                                                           | FSR                            |                 |  |  |  |  |  |  |

| 05h               | PORTA                                                         | TRISA                          | 85h             |  |  |  |  |  |  |

| 06h               | PORTB                                                         | TRISB                          | 86h             |  |  |  |  |  |  |

| 07h               | PORTC                                                         | TRISC                          |                 |  |  |  |  |  |  |

| 08h               | PORTD <sup>(2)</sup>                                          | TRISD <sup>(2)</sup>           |                 |  |  |  |  |  |  |

| 09h               | PORTE <sup>(2)</sup>                                          | TRISE <sup>(2)</sup>           | 89h             |  |  |  |  |  |  |

| 0Ah               | PCLATH                                                        | PCLATH                         | 8Ah             |  |  |  |  |  |  |

| 0Bh               | INTCON                                                        | INTCON                         | 8Bh             |  |  |  |  |  |  |

| 0Ch               | PIR1                                                          | PIE1                           | 8Ch             |  |  |  |  |  |  |

| 0Dh               | PIR2                                                          | PIE2                           | 8Dh             |  |  |  |  |  |  |

| 0Eh               | TMR1L                                                         | PCON                           | 8Eh             |  |  |  |  |  |  |

| 0Fh               | TMR1H                                                         |                                | 8Fh             |  |  |  |  |  |  |

| 10h               | T1CON                                                         |                                | 90h             |  |  |  |  |  |  |

| 11h               | TMR2                                                          |                                | 91h             |  |  |  |  |  |  |

| 12h               | T2CON                                                         | PR2                            |                 |  |  |  |  |  |  |

| 13h               | SSPBUF                                                        | SSPADD                         | 93h             |  |  |  |  |  |  |

| 14h               | SSPCON                                                        | SSPSTAT                        | 94h             |  |  |  |  |  |  |

| 15h               | CCPR1L                                                        |                                | 95h             |  |  |  |  |  |  |

| 16h               | CCPR1H                                                        |                                | 96h             |  |  |  |  |  |  |

| 17h               | CCP1CON                                                       |                                | 97h             |  |  |  |  |  |  |

| 18h               | RCSTA                                                         | TXSTA                          |                 |  |  |  |  |  |  |

| 19h               | TXREG                                                         | SPBRG                          | 99h             |  |  |  |  |  |  |

| 1Ah               | RCREG                                                         |                                | 9Ah             |  |  |  |  |  |  |

| 1Bh               | CCPR2L                                                        |                                | 9Bh             |  |  |  |  |  |  |

| 1Ch               | CCPR2H                                                        |                                | 9Ch             |  |  |  |  |  |  |

| 1Dh               | CCP2CON                                                       |                                | 9Dh             |  |  |  |  |  |  |

| 1Eh               | ADRES                                                         |                                | 9Eh             |  |  |  |  |  |  |

| 1Fh               | ADCON0                                                        | ADCON1                         | 9Fh             |  |  |  |  |  |  |

| 20h               |                                                               |                                | A0h             |  |  |  |  |  |  |

|                   | General<br>Purpose<br>Register                                | General<br>Purpose<br>Register |                 |  |  |  |  |  |  |

| 7Fh               |                                                               |                                | FFh             |  |  |  |  |  |  |

|                   | Bank 0                                                        | Bank 1                         |                 |  |  |  |  |  |  |

|                   | Unimplemented da                                              | -                              | ons, read as    |  |  |  |  |  |  |

| Note 1:<br>2:     | Not a physical reg<br>These registers ar<br>mented on the PIC | e not physically               |                 |  |  |  |  |  |  |

|                   |                                                               |                                |                 |  |  |  |  |  |  |

#### FIGURE 4-6: PIC16C76/77 REGISTER FILE MAP

| Indirect addr.(*)                          | 00h       | Indirect addr.(*)                          | 80h        | Indirect addr.(*)                          | 100h         | Indirect addr.(*)                          | 180        |

|--------------------------------------------|-----------|--------------------------------------------|------------|--------------------------------------------|--------------|--------------------------------------------|------------|

| TMR0                                       | 01h       | OPTION                                     | 81h        | TMR0                                       | 101h         | OPTION                                     | 181        |

| PCL                                        | 02h       | PCL                                        | 82h        | PCL                                        | 102h         | PCL                                        | 182        |

| STATUS                                     | 03h       | STATUS                                     | 83h        | STATUS                                     | 103h         | STATUS                                     | 183        |

| FSR                                        | 04h       | FSR                                        | 84h        | FSR                                        | 104h         | FSR                                        | 184        |

| PORTA                                      | 05h       | TRISA                                      | 85h        |                                            | 105h         |                                            | 185        |

| PORTB                                      | 06h       | TRISB                                      | 86h        | PORTB                                      | 106h         | TRISB                                      | 186        |

| PORTC                                      | 07h       | TRISC                                      | 87h        |                                            | 107h         |                                            | 187        |

| PORTD (1)                                  | 08h       | TRISD <sup>(1)</sup>                       | 88h        |                                            | 108h         |                                            | 188        |

| PORTE (1)                                  | 09h       | TRISE (1)                                  | 89h        |                                            | 109h         |                                            | 189        |

| PCLATH                                     | 0Ah       | PCLATH                                     | 8Ah        | PCLATH                                     | 10Ah         | PCLATH                                     | 18A        |

| INTCON                                     | 0Bh       | INTCON                                     | 8Bh        | INTCON                                     | 10Bh         | INTCON                                     | 18B        |

| PIR1                                       | 0Ch       | PIE1                                       | 8Ch        |                                            | 10Ch         |                                            | 1 18C      |

| PIR2                                       | 0Dh       | PIE2                                       | 8Dh        |                                            | 10Dh         |                                            | 18D        |

| TMR1L                                      | 0Eh       | PCON                                       | 8Eh        |                                            | 10Eh         |                                            | 18E        |

| TMR1H                                      | 0Fh       |                                            | 8Fh        |                                            | 10Fh         |                                            | 18F        |

| T1CON                                      | 10h       |                                            | 90h        |                                            | 110h         |                                            | 190        |

| TMR2                                       | 11h       |                                            | 91h        |                                            | 111h         |                                            | 191        |

| T2CON                                      | 12h       | PR2                                        | 92h        |                                            | 112h         |                                            | 192        |

| SSPBUF                                     | 13h       | SSPADD                                     | 93h        |                                            | 113h         |                                            | 193        |

| SSPCON                                     | 14h       | SSPSTAT                                    | 94h        |                                            | 114h         |                                            | 194        |

| CCPR1L                                     | 15h       |                                            | 95h        |                                            | 115h         |                                            | 195        |

| CCPR1H                                     | 16h       |                                            | 96h        |                                            | 116h         |                                            | 196        |

| CCP1CON                                    | 17h       |                                            | 97h        | General                                    | 117h         | General                                    | 197        |

| RCSTA                                      | 18h       | TXSTA                                      | 98h        | Purpose<br>Register                        | 118h         | Purpose<br>Register                        | 198        |

| TXREG                                      | 19h       | SPBRG                                      | 99h        | 16 Bytes                                   | 119h         | 16 Bytes                                   | 199        |

| RCREG                                      | 1Ah       |                                            | 9Ah        |                                            | 11Ah         |                                            | 19A        |

| CCPR2L                                     | 1Bh       |                                            | 9Bh        |                                            | 11Bh         |                                            | 19B        |

| CCPR2H                                     | 1Ch       |                                            | 9Ch        |                                            | 11Ch         |                                            | 19C        |

| CCP2CON                                    | 1Dh       |                                            | 9Dh        |                                            | 11Dh         |                                            | 19D        |

| ADRES                                      | 1Eh       |                                            | 9Eh        |                                            | 11Eh         |                                            | 19E        |

| ADCON0                                     | 1Fh       | ADCON1                                     | 9Fh        |                                            | 11Fh         |                                            | 19F        |

|                                            | 20h       |                                            | A0h        |                                            | 120h         |                                            | 1A0        |

| General<br>Purpose<br>Register<br>96 Bytes |           | General<br>Purpose<br>Register<br>80 Bytes | EFh        | General<br>Purpose<br>Register<br>80 Bytes | 16Fh         | General<br>Purpose<br>Register<br>80 Bytes | 1EF        |

| -                                          | 7Fh       | accesses<br>70h-7Fh                        | F0h<br>FFh | accesses<br>70h-7Fh                        | 170h<br>17Fh | accesses<br>70h - 7Fh                      | ] 1F0 <br> |

| Bank 0                                     |           | Bank 1                                     |            | Bank 2                                     |              | Bank 3                                     |            |

| _                                          | nted data | memory locations, re                       |            |                                            |              | Bank 3                                     |            |

**Note:** The upper 16 bytes of data memory in banks 1, 2, and 3 are mapped in Bank 0. This may require relocation of data memory usage in the user application code if upgrading to the PIC16C76/77.

# PIC16C7X

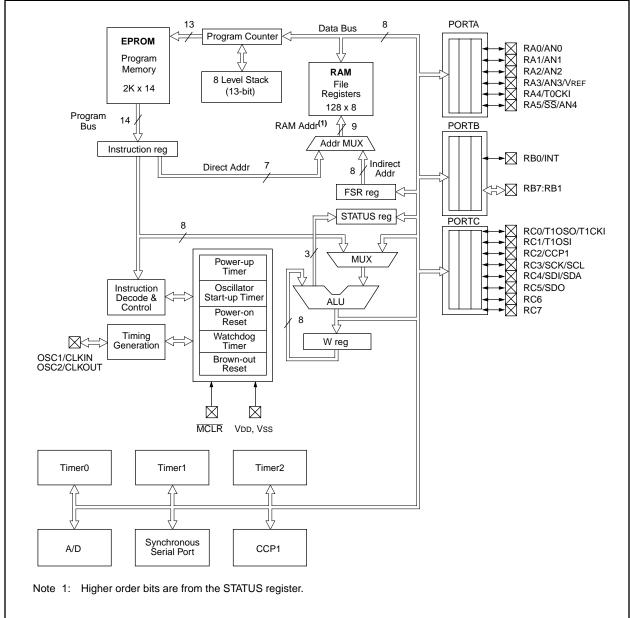

### FIGURE 7-3: TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2

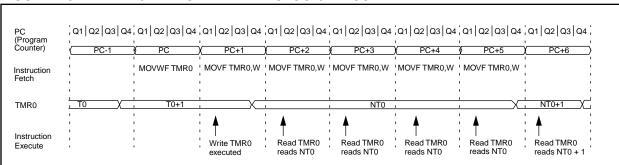

#### FIGURE 7-4: TIMER0 INTERRUPT TIMING

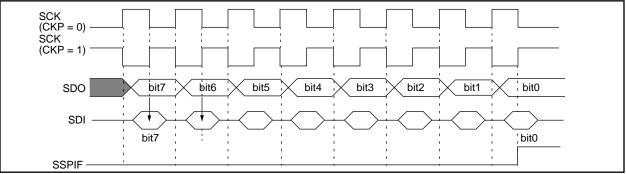

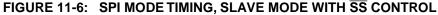

The  $\overline{SS}$  pin allows a synchronous slave mode. The SPI must be in slave mode (SSPCON<3:0> = 04h) and the TRISA<5> bit must be set the for synchronous slave mode to be enabled. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. If the  $\overline{SS}$  pin is taken low without resetting SPI mode, the transmission will continue from the

point at which it was taken high. External pull-up/ pull-down resistors may be desirable, depending on the application.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

|  | <b>TABLE 11-1:</b> | <b>REGISTERS ASSOCIATED WITH SPI OPERATION</b> |

|--|--------------------|------------------------------------------------|

|--|--------------------|------------------------------------------------|

| Address | Name    | Bit 7                  | Bit 6       | Bit 5               | Bit 4                         | Bit 3     | Bit 2    | Bit 1  | Bit 0  | Value<br>POF<br>BOF | ٦,   | all o | e on<br>ther<br>ets |

|---------|---------|------------------------|-------------|---------------------|-------------------------------|-----------|----------|--------|--------|---------------------|------|-------|---------------------|

| 0Bh,8Bh | INTCON  | GIE                    | PEIE        | TOIE                | INTE                          | RBIE      | TOIF     | INTF   | RBIF   | 0000 0              | 200x | 0000  | 000u                |

| 0Ch     | PIR1    | PSPIF <sup>(1,2)</sup> | ADIF        | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup>           | SSPIF     | CCP1IF   | TMR2IF | TMR1IF | 0000 0              | 0000 | 0000  | 0000                |

| 8Ch     | PIE1    | PSPIE <sup>(1,2)</sup> | ADIE        | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup>           | SSPIE     | CCP1IE   | TMR2IE | TMR1IE | 0000 0              | 0000 | 0000  | 0000                |

| 87h     | TRISC   | PORTC Da               | ta Directio | on Registe          | er                            |           |          |        |        | 1111 1              | 1111 | 1111  | 1111                |

| 13h     | SSPBUF  | Synchronou             | us Serial I | Port Rece           | ive Buffer                    | /Transmit | Register |        |        | XXXX X              | xxxx | uuuu  | uuuu                |

| 14h     | SSPCON  | WCOL                   | SSPOV       | SSPEN               | CKP                           | SSPM3     | SSPM2    | SSPM1  | SSPM0  | 0000 0              | 0000 | 0000  | 0000                |

| 85h     | TRISA   | _                      | _           | PORTA I             | PORTA Data Direction Register |           |          |        |        |                     |      | 11    | 1111                |

| 94h     | SSPSTAT | —                      | —           | D/Ā                 | Р                             | S         | R/W      | UA     | BF     | 00 C                | 0000 | 00    | 0000                |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the SSP in SPI mode.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A, always maintain these bits clear.

2: The PIC16C72 does not have a Parallel Slave Port or USART, these bits are unimplemented, read as '0'.

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON register, and then set bit SSPEN. This configures the SDI, SDO, SCK, and SS pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value. An example would be in master mode where you are only sending data (to a display driver), then both SDI and SS could be used as general purpose outputs by clearing their corresponding TRIS register bits.

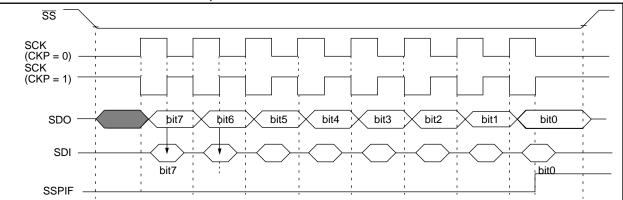

Figure 11-10 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge, and latched on the opposite edge of the clock. Both processors should be programmed to same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application firmware. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- Master sends dummy data Slave sends data

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2) is to broadcast data by the firmware protocol.

In master mode the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SCK output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "line activity monitor" mode.

In slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched the interrupt flag bit SSPIF (PIR1<3>) is set.

The clock polarity is selected by appropriately programming bit CKP (SSPCON<4>). This then would give waveforms for SPI communication as shown in Figure 11-11, Figure 11-12, and Figure 11-13 where the MSB is transmitted first. In master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum bit clock frequency (at 20 MHz) of 5 MHz. When in slave mode the external clock must meet the minimum high and low times.

In sleep mode, the slave can transmit and receive data and wake the device from sleep.

#### 12.1.1 SAMPLING

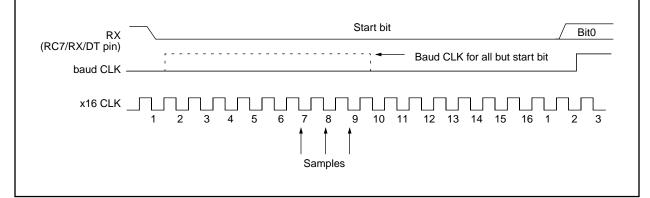

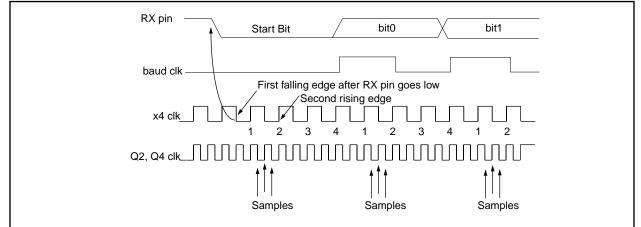

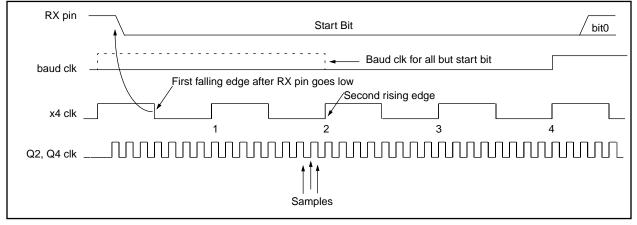

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin. If bit BRGH (TXSTA<2>) is clear (i.e., at the low baud rates), the sampling is done on the seventh, eighth and ninth falling edges of a x16 clock (Figure 12-3). If bit BRGH is set (i.e., at the high baud rates), the sampling is done on the 3 clock edges preceding the second rising edge after the first falling edge of a x4 clock (Figure 12-4 and Figure 12-5).

#### FIGURE 12-3: RX PIN SAMPLING SCHEME. BRGH = 0 (PIC16C73/73A/74/74A)

#### FIGURE 12-4: RX PIN SAMPLING SCHEME, BRGH = 1 (PIC16C73/73A/74/74A)

| COMF                                                                                                                          | Complement f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DECFSZ            | Decrement f, Skip if 0                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                                       | [ <i>label</i> ] COMF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Syntax:           | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                        |

| Operands:                                                                                                                     | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Operands:         | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                 |

| Operation:                                                                                                                    | $(\overline{f}) \rightarrow$ (destination)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Operation:        | (f) - 1 $\rightarrow$ (destination);                                                                                                                                                                                                                                                               |

| Status Affected:                                                                                                              | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   | skip if result = 0                                                                                                                                                                                                                                                                                 |

| Encoding:                                                                                                                     | 00 1001 dfff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Status Affected:  | None                                                                                                                                                                                                                                                                                               |

| Description:                                                                                                                  | The contents of register 'f' are comple-<br>mented. If 'd' is 0 the result is stored in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Encoding:         | 00 1011 dfff ffff                                                                                                                                                                                                                                                                                  |

|                                                                                                                               | W. If 'd' is 1 the result is stored back in register 'f'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Description:      | The contents of register 'f' are decre-<br>mented. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed                                                                                                                                                         |

| Words:                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   | back in register 'f'.<br>If the result is 1, the next instruction, is                                                                                                                                                                                                                              |

| Cycles:                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   | executed. If the result is 0, then a NOP is<br>executed instead making it a 2TCY instruc-                                                                                                                                                                                                          |

| Q Cycle Activity:                                                                                                             | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   | tion.                                                                                                                                                                                                                                                                                              |

|                                                                                                                               | Decode Read Process Write to register data destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Words:            | 1                                                                                                                                                                                                                                                                                                  |

|                                                                                                                               | f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Cycles:           | 1(2)                                                                                                                                                                                                                                                                                               |

|                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                        |

| Example                                                                                                                       | COMF REG1,0<br>Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   | Decode Read register 'f' Process Write to destination                                                                                                                                                                                                                                              |

|                                                                                                                               | REG1 = 0x13<br>After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | If Skip:          | (2nd Cycle)                                                                                                                                                                                                                                                                                        |

|                                                                                                                               | REG1 = 0x13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                        |