Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                    |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c73a-20i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

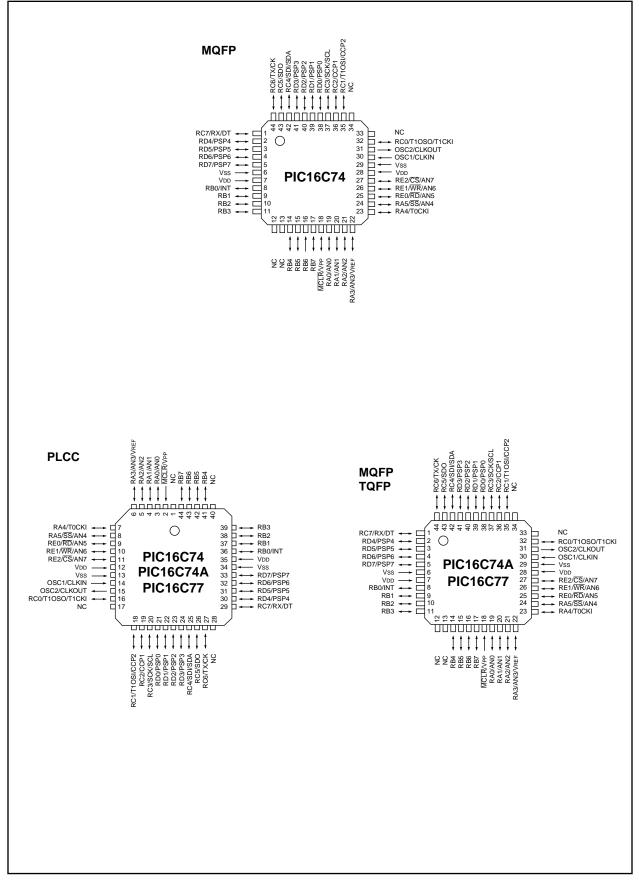

#### Pin Diagrams (Cont.'d)

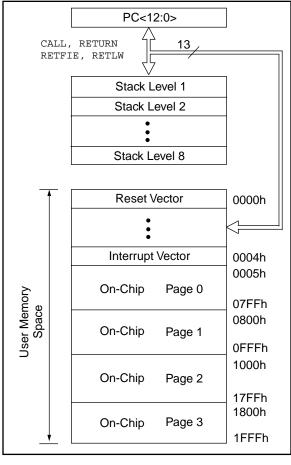

#### FIGURE 4-3: PIC16C76/77 PROGRAM MEMORY MAP AND STACK

# 4.2 Data Memory Organization

Applicable Devices

72

73

73

74

74

76

77

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

RP1:RP0 (STATUS<6:5>)

- = 00  $\rightarrow$  Bank0

- = 01  $\rightarrow$  Bank1

- =  $10 \rightarrow \text{Bank2}$

- = 11  $\rightarrow$  Bank3

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain special function registers. Some "high use" special function registers from one bank may be mirrored in another bank for code reduction and quicker access.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR (Section 4.5).

4.2.2.5 PIR1 REGISTER

Applicable Devices

This register contains the individual flag bits for the Peripheral interrupts.

FIGURE 4-12: PIR1 REGISTER PIC16C72 (ADDRESS 0Ch)

# Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### U-0 R/W-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 ADIF SSPIF CCP1IF TMR2IF TMR1IF = Readable bit R = Writable bit W bit0 bit7 = Unimplemented bit, U read as '0' n = Value at POR reset bit 7: Unimplemented: Read as '0' bit 6: ADIF: A/D Converter Interrupt Flag bit 1 = An A/D conversion completed (must be cleared in software) 0 = The A/D conversion is not complete bit 5-4: Unimplemented: Read as '0' bit 3: SSPIF: Synchronous Serial Port Interrupt Flag bit 1 = The transmission/reception is complete (must be cleared in software) 0 = Waiting to transmit/receive bit 2: CCP1IF: CCP1 Interrupt Flag bit Capture Mode 1 = A TMR1 register capture occurred (must be cleared in software) 0 = No TMR1 register capture occurred Compare Mode 1 = A TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred PWM Mode Unused in this mode TMR2IF: TMR2 to PR2 Match Interrupt Flag bit bit 1: 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR2 to PR2 match occurred bit 0: TMR1IF: TMR1 Overflow Interrupt Flag bit 1 = TMR1 register overflowed (must be cleared in software) 0 = TMR1 register did not overflow Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

|  | TABLE 10-5: | <b>REGISTERS ASSOCIATED WITH PWM AND TIMER2</b> |

|--|-------------|-------------------------------------------------|

|--|-------------|-------------------------------------------------|

| Address               | Name    | Bit 7                  | Bit 6          | Bit 5               | Bit 4               | Bit 3     | Bit 2  | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|-----------------------|---------|------------------------|----------------|---------------------|---------------------|-----------|--------|---------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                    | PEIE           | TOIE                | INTE                | RBIE      | TOIF   | INTF    | RBIF    | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1    | PSPIF <sup>(1,2)</sup> | ADIF           | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | SSPIF     | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000                | 0000 0000                       |

| 0Dh <sup>(2)</sup>    | PIR2    | —                      | CCP2IF         |                     |                     |           |        |         |         | 0                        | 0                               |

| 8Ch                   | PIE1    | PSPIE <sup>(1,2)</sup> | ADIE           | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup> | SSPIE     | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000                | 0000 0000                       |

| 8Dh <sup>(2)</sup>    | PIE2    | —                      | _              | —                   | _                   | —         | —      | —       | CCP2IE  | 0                        | 0                               |

| 87h                   | TRISC   | PORTC Da               | ata Directio   |                     | 1111 1111           | 1111 1111 |        |         |         |                          |                                 |

| 11h                   | TMR2    | Timer2 mod             | dule's registe | ər                  |                     |           |        |         |         | 0000 0000                | 0000 0000                       |

| 92h                   | PR2     | Timer2 mod             | dule's perioc  | l register          |                     |           |        |         |         | 1111 1111                | 1111 1111                       |

| 12h                   | T2CON   | —                      | TOUTPS3        | TOUTPS2             | TOUTPS1             | TOUTPS0   | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000                | -000 0000                       |

| 15h                   | CCPR1L  | Capture/Co             | mpare/PWN      | / register1 (       | LSB)                |           |        |         |         | xxxx xxxx                | uuuu uuuu                       |

| 16h                   | CCPR1H  | Capture/Co             | mpare/PWN      | / register1 (       | (MSB)               |           |        |         |         | xxxx xxxx                | uuuu uuuu                       |

| 17h                   | CCP1CON | —                      | —              | CCP1X               | CCP1Y               | CCP1M3    | CCP1M2 | CCP1M1  | CCP1M0  | 00 0000                  | 00 0000                         |

| 1Bh <b>(2)</b>        | CCPR2L  | Capture/Co             | mpare/PWN      | / register2 (       | LSB)                |           |        |         |         | xxxx xxxx                | uuuu uuuu                       |

| 1Ch <sup>(2)</sup>    | CCPR2H  | Capture/Co             | mpare/PWN      |                     | xxxx xxxx           | uuuu uuuu |        |         |         |                          |                                 |

| 1Dh <sup>(2)</sup>    | CCP2CON | —                      | —              | CCP2X               | CCP2Y               | CCP2M3    | CCP2M2 | CCP2M1  | CCP2M0  | 00 0000                  | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PWM and Timer2.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

2: The PIC16C72 does not have a Parallel Slave Port, USART or CCP2 module, these bits are unimplemented, read as '0'.

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH. (Section 12.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC, and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

### TABLE 12-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address | Name                               | Bit 7                | Bit 6    | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|------------------------------------|----------------------|----------|--------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Ch     | PIR1                               | PSPIF <sup>(1)</sup> | ADIF     | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h     | RCSTA                              | SPEN                 | RX9      | SREN   | CREN  |       | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 1Ah     | RCREG                              | USART Rec            | eive Reg | gister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1                               | PSPIE <sup>(1)</sup> | ADIE     | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h     | TXSTA                              | CSRC                 | TX9      | TXEN   | SYNC  |       | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h     | SPBRG Baud Rate Generator Register |                      |          |        |       |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

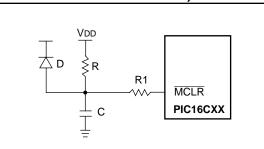

#### FIGURE 14-13: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

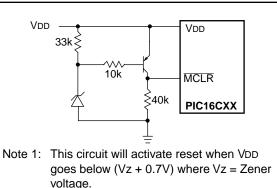

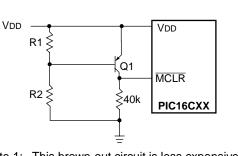

#### FIGURE 14-14: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- 2: Internal brown-out detection on the PIC16C72/73A/74A/76/77 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

#### FIGURE 14-15: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

- 2: Internal brown-out detection on the PIC16C72/73A/74A/76/77 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

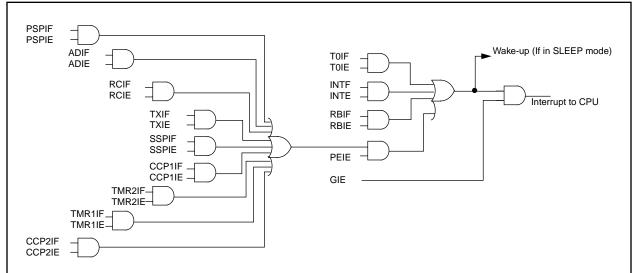

# 14.5 <u>Interrupts</u> Applicable Devices 72|73|73|74|74|76|77

The PIC16C7X family has up to 12 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |   |

|-------|------------------------------------------------|---|

|       | less of the status of their corresponding      | l |

|       | mask bit or the GIE bit.                       | l |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set regardless of the status of the GIE bit. The GIE bit is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

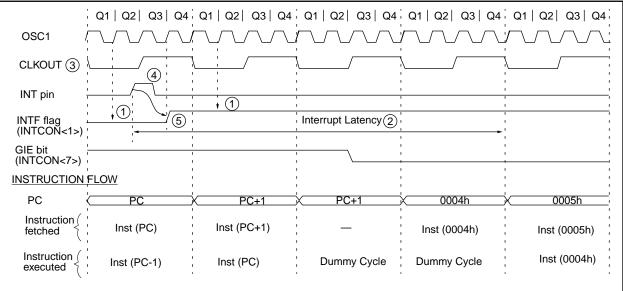

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 14-17). The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- Note: For the PIC16C73/74, if an interrupt occurs while the Global Interrupt Enable (GIE) bit is being cleared, the GIE bit may unintentionally be re-enabled by the user's Interrupt Service Routine (the RETFIE instruction). The events that would cause this to occur are:

- 1. An instruction clears the GIE bit while an interrupt is acknowledged.

- 2. The program branches to the Interrupt vector and executes the Interrupt Service Routine.

- The Interrupt Service Routine completes with the execution of the RET-FIE instruction. This causes the GIE bit to be set (enables interrupts), and the program returns to the instruction after the one which was meant to disable interrupts.

Perform the following to ensure that interrupts are globally disabled:

| LOOP | BCF   | INTCON, | GIE | ; | Disable global   |

|------|-------|---------|-----|---|------------------|

|      |       |         |     | ; | interrupt bit    |

|      | BTFSC | INTCON, | GIE | ; | Global interrupt |

|      |       |         |     | ; | disabled?        |

|      | GOTO  | LOOP    |     | ; | NO, try again    |

|      | :     |         |     | ; | Yes, continue    |

|      |       |         |     | ; | with program     |

|      |       |         |     | ; | flow             |

#### FIGURE 14-16: INTERRUPT LOGIC

The following table shows which devices have which interrupts.

| Device    | TOIF | INTF | RBIF | PSPIF | ADIF | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF | CCP2IF |

|-----------|------|------|------|-------|------|------|------|-------|--------|--------|--------|--------|

| PIC16C72  | Yes  | Yes  | Yes  | -     | Yes  | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C73  | Yes  | Yes  | Yes  | -     | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C73A | Yes  | Yes  | Yes  | -     | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C74  | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C74A | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C76  | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C77  | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

#### FIGURE 14-17: INT PIN INTERRUPT TIMING

Note 1: INTF flag is sampled here (every Q1).

- 2: Interrupt latency = 3-4 Tcy where Tcy = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

3: CLKOUT is available only in RC oscillator mode.

4: For minimum width of INT pulse, refer to AC specs.

5: INTF is enabled to be set anytime during the Q4-Q1 cycles.

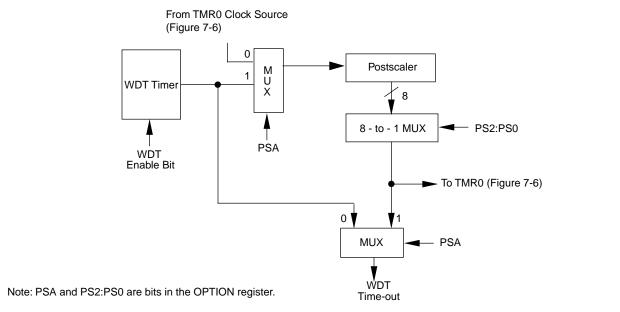

#### 14.7 Watchdog Timer (WDT) **Applicable Devices** 72 73 73A 74 74A 76 77

The Watchdog Timer is as a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The WDT can be permanently disabled by clearing configuration bit WDTE (Section 14.1).

#### 14.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a

FIGURE 14-18: WATCHDOG TIMER BLOCK DIAGRAM

prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

14.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken into account that under worst case conditions (VDD = Min., Temperature = Max., and max. WDT prescaler) it may take several seconds before a WDT time-out occurs.

Note: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

# FIGURE 14-19: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h,181h | OPTION       | RBPU  | INTEDG               | TOCS  | TOSE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Figure 14-1, and Figure 14-2 for operation of these bits.

#### TABLE 15-2: PIC16CXX INSTRUCTION SET

| Mnemonic,  |        | Description                  | Cycles |       | 14-Bit | Opcode | 9        | Status   | Notes |

|------------|--------|------------------------------|--------|-------|--------|--------|----------|----------|-------|

| Operands   |        |                              |        | MSb   | I      |        | LSb      | Affected |       |

| BYTE-ORIE  | NTED   | FILE REGISTER OPERATIONS     |        |       |        |        |          |          |       |

| ADDWF      | f, d   | Add W and f                  | 1      | 00    | 0111   | dfff   | ffff     | C,DC,Z   | 1,2   |

| ANDWF      | f, d   | AND W with f                 | 1      | 00    | 0101   | dfff   | ffff     | Z        | 1,2   |

| CLRF       | f      | Clear f                      | 1      | 00    | 0001   | lfff   | ffff     | Z        | 2     |

| CLRW       | -      | Clear W                      | 1      | 00    | 0001   | 0xxx   | xxxx     | Z        |       |

| COMF       | f, d   | Complement f                 | 1      | 00    | 1001   | dfff   | ffff     | Z        | 1,2   |

| DECF       | f, d   | Decrement f                  | 1      | 00    | 0011   | dfff   | ffff     | Z        | 1,2   |

| DECFSZ     | f, d   | Decrement f, Skip if 0       | 1(2)   | 00    | 1011   | dfff   | ffff     |          | 1,2,3 |

| INCF       | f, d   | Increment f                  | 1      | 00    | 1010   | dfff   | ffff     | Z        | 1,2   |

| INCFSZ     | f, d   | Increment f, Skip if 0       | 1(2)   | 00    | 1111   | dfff   | ffff     |          | 1,2,3 |

| IORWF      | f, d   | Inclusive OR W with f        | 1      | 00    | 0100   | dfff   | ffff     | Z        | 1,2   |

| MOVF       | f, d   | Move f                       | 1      | 00    | 1000   | dfff   | ffff     | Z        | 1,2   |

| MOVWF      | f      | Move W to f                  | 1      | 00    | 0000   | lfff   | ffff     |          |       |

| NOP        | -      | No Operation                 | 1      | 00    | 0000   | 0xx0   | 0000     |          |       |

| RLF        | f, d   | Rotate Left f through Carry  | 1      | 00    | 1101   | dfff   | ffff     | С        | 1,2   |

| RRF        | f, d   | Rotate Right f through Carry | 1      | 00    | 1100   | dfff   | ffff     | С        | 1,2   |

| SUBWF      | f, d   | Subtract W from f            | 1      | 00    | 0010   | dfff   | ffff     | C,DC,Z   | 1,2   |

| SWAPF      | f, d   | Swap nibbles in f            | 1      | 00    | 1110   | dfff   | ffff     |          | 1,2   |

| XORWF      | f, d   | Exclusive OR W with f        | 1      | 00    | 0110   | dfff   | ffff     | Z        | 1,2   |

| BIT-ORIENT | ED FIL | E REGISTER OPERATIONS        |        |       |        |        |          | _        |       |

| BCF        | f, b   | Bit Clear f                  | 1      | 01    | 00bb   | bfff   | ffff     |          | 1,2   |

| BSF        | f, b   | Bit Set f                    | 1      | 01    | 01bb   | bfff   | ffff     |          | 1,2   |

| BTFSC      | f, b   | Bit Test f, Skip if Clear    | 1 (2)  | 01    | 10bb   | bfff   | ffff     |          | 3     |

| BTFSS      | f, b   | Bit Test f, Skip if Set      | 1 (2)  | 01    | 11bb   | bfff   | ffff     |          | 3     |

| LITERAL AI | ND CO  | NTROL OPERATIONS             |        |       |        |        |          |          |       |

| ADDLW      | k      | Add literal and W            | 1      | 11    | 111x   | kkkk   | kkkk     | C,DC,Z   |       |

| ANDLW      | k      | AND literal with W           | 1      | 11    | 1001   | kkkk   | kkkk     | Z        |       |

| CALL       | k      | Call subroutine              | 2      | 10    | 0kkk   | kkkk   | kkkk     |          |       |

| CLRWDT     | -      | Clear Watchdog Timer         | 1      | 00    | 0000   | 0110   | 0100     | TO,PD    |       |

| GOTO       | k      | Go to address                | 2      | 10    | 1kkk   | kkkk   | kkkk     |          |       |

| IORLW      | k      | Inclusive OR literal with W  | 1      | 11    | 1000   | kkkk   | kkkk     | Z        |       |

| MOVLW      | k      | Move literal to W            | 1      | 11    | 00xx   | kkkk   | kkkk     |          |       |

| RETFIE     | -      | Return from interrupt        | 2      | 00    | 0000   | 0000   | 1001     |          |       |

| RETLW      | k      | Return with literal in W     | 2      | 11    | 01xx   | kkkk   | kkkk     |          |       |

| RETURN     | -      | Return from Subroutine       | 2      | 00    | 0000   | 0000   | 1000     |          |       |

| SLEEP      | -      | Go into standby mode         | 1      | 00    | 0000   | 0110   | 0011     | TO, PD   |       |

|            |        | Subtract W from literal      | 1      | 11    | 110x   | kkkk   | 1-1-1-1- | C,DC,Z   |       |

| SUBLW      | k      |                              |        | L T T | TTOX   | KKKK   | кккк     | 0,DC,Z   |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

# 15.1 Instruction Descriptions

| ADDLW             | Add Lite                                   | ral and \                 | ~               |               |  |  |  |  |  |

|-------------------|--------------------------------------------|---------------------------|-----------------|---------------|--|--|--|--|--|

| Syntax:           | [label] Al                                 |                           | k               |               |  |  |  |  |  |

| Operands:         | $0 \le k \le 2$                            |                           | ĸ               |               |  |  |  |  |  |

| ·                 |                                            | $(W) + k \rightarrow (W)$ |                 |               |  |  |  |  |  |

| Operation:        | . ,                                        | → (vv)                    |                 |               |  |  |  |  |  |

| Status Affected:  | C, DC, Z                                   |                           |                 |               |  |  |  |  |  |

| Encoding:         | 11                                         | 111x                      | kkkk            | kkkk          |  |  |  |  |  |

| Description:      | The conter<br>added to the<br>result is pl | he eight b                | oit literal 'k' | and the       |  |  |  |  |  |

| Words:            | 1                                          |                           |                 |               |  |  |  |  |  |

| Cycles:           | 1                                          |                           |                 |               |  |  |  |  |  |

| Q Cycle Activity: | Q1                                         | Q2                        | Q3              | Q4            |  |  |  |  |  |

|                   | Decode                                     | Read<br>literal 'k'       | Process<br>data | Write to<br>W |  |  |  |  |  |

| Example:          | ADDLW                                      | 0x15                      |                 |               |  |  |  |  |  |

|                   | Before In                                  | struction                 | ì               |               |  |  |  |  |  |

|                   |                                            | - W                       | 0x10            |               |  |  |  |  |  |

|                   | After Inst                                 |                           | 0.05            |               |  |  |  |  |  |

|                   |                                            | W =                       | 0x25            |               |  |  |  |  |  |

|                   |                                            |                           |                 |               |  |  |  |  |  |

| ADDWF             | Add W a                                    | nd f                      |                 |               |  |  |  |  |  |

| Syntax:           | [ <i>label</i> ] A                         | DDWF                      | f,d             |               |  |  |  |  |  |

| Operands:         | $0 \le f \le 12$                           | 27                        |                 |               |  |  |  |  |  |

| ANDLW             | AND Lite                                                                                                            | eral with              | w               |               |  |  |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------|------------------------|-----------------|---------------|--|--|--|--|--|--|

| Syntax:           | [ <i>label</i> ] A                                                                                                  | NDLW                   | k               |               |  |  |  |  |  |  |

| Operands:         | $0 \le k \le 2$                                                                                                     | 55                     |                 |               |  |  |  |  |  |  |

| Operation:        | (W) .AND                                                                                                            | D. (k) $\rightarrow$ ( | W)              |               |  |  |  |  |  |  |

| Status Affected:  | Z                                                                                                                   | Z                      |                 |               |  |  |  |  |  |  |

| Encoding:         | 11                                                                                                                  | 1001                   | kkkk            | kkkk          |  |  |  |  |  |  |

| Description:      | The contents of W register are<br>AND'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |                        |                 |               |  |  |  |  |  |  |

| Words:            | 1                                                                                                                   |                        |                 |               |  |  |  |  |  |  |

| Cycles:           | 1                                                                                                                   |                        |                 |               |  |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                  | Q2                     | Q3              | Q4            |  |  |  |  |  |  |

|                   | Decode                                                                                                              | Read<br>literal "k"    | Process<br>data | Write to<br>W |  |  |  |  |  |  |

| Example           | ANDLW                                                                                                               | 0x5F                   |                 |               |  |  |  |  |  |  |

|                   | Before In                                                                                                           | struction              | 1               |               |  |  |  |  |  |  |

|                   |                                                                                                                     | W =                    | 0xA3            |               |  |  |  |  |  |  |

|                   | After Inst                                                                                                          | W =                    | 0x03            |               |  |  |  |  |  |  |

|                   |                                                                                                                     |                        |                 |               |  |  |  |  |  |  |

| ANDWF             | AND W v                                                                                                             | vith f                 |                 |               |  |  |  |  |  |  |

| Syntax:           | [ <i>label</i> ] A                                                                                                  | NDWF                   | f,d             |               |  |  |  |  |  |  |

| Operands:         | $0 \le f \le 12$                                                                                                    | 27                     |                 |               |  |  |  |  |  |  |

| ADDWF             | Add W a                                                                                                                                                                   | nd f                    |                 |                      |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|----------------------|--|--|--|--|

| Syntax:           | [ <i>label</i> ] A                                                                                                                                                        | DDWF                    | f,d             |                      |  |  |  |  |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$                                                                                                                                            | 7                       |                 |                      |  |  |  |  |

| Operation:        | (W) + (f) $\rightarrow$ (destination)                                                                                                                                     |                         |                 |                      |  |  |  |  |

| Status Affected:  | C, DC, Z                                                                                                                                                                  |                         |                 |                      |  |  |  |  |

| Encoding:         | 00                                                                                                                                                                        | 0111                    | dfff            | ffff                 |  |  |  |  |

| Description:      | Add the contents of the W register with<br>register 'f'. If 'd' is 0 the result is stored<br>in the W register. If 'd' is 1 the result is<br>stored back in register 'f'. |                         |                 |                      |  |  |  |  |

| Words:            | 1                                                                                                                                                                         |                         |                 |                      |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                         |                         |                 |                      |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                        | Q2                      | Q3              | Q4                   |  |  |  |  |

|                   | Decode                                                                                                                                                                    | Read<br>register<br>'f' | Process<br>data | Write to destination |  |  |  |  |

| Example           | ADDWF                                                                                                                                                                     | FSR,                    | 0               |                      |  |  |  |  |

|                   | Before In                                                                                                                                                                 |                         |                 |                      |  |  |  |  |

|                   |                                                                                                                                                                           | W =<br>FSR =            | 0x17<br>0xC2    |                      |  |  |  |  |

|                   | After Inst                                                                                                                                                                | ruction                 |                 |                      |  |  |  |  |

|                   |                                                                                                                                                                           | W =<br>FSR =            | 0xD9<br>0xC2    |                      |  |  |  |  |

| ANDWF             | AND W v                                                      | vith f                   |                 |                      |

|-------------------|--------------------------------------------------------------|--------------------------|-----------------|----------------------|

| Syntax:           | [ <i>label</i> ] A                                           | NDWF                     | f,d             |                      |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$                               | 27                       |                 |                      |

| Operation:        | (W) .AND                                                     | D. (f) $\rightarrow$ (d  | destinatio      | n)                   |

| Status Affected:  | Z                                                            |                          |                 |                      |

| Encoding:         | 00                                                           | 0101                     | dfff            | ffff                 |

| Description:      | AND the V<br>is 0 the re-<br>ter. If 'd' is<br>register 'f'. | sult is sto<br>1 the res | red in the      | N regis-             |

| Words:            | 1                                                            |                          |                 |                      |

| Cycles:           | 1                                                            |                          |                 |                      |

| Q Cycle Activity: | Q1                                                           | Q2                       | Q3              | Q4                   |

|                   | Decode                                                       | Read<br>register<br>'f'  | Process<br>data | Write to destination |

| Example           | ANDWF                                                        | FSR,                     | 1               |                      |

|                   | Before In                                                    |                          |                 |                      |

|                   |                                                              | W =<br>FSR =             | 0x17<br>0xC2    |                      |

|                   | After Inst                                                   |                          |                 |                      |

|                   |                                                              |                          | 0x17            |                      |

|                   |                                                              | FSR =                    | 0x02            |                      |

Applicable Devices 72 73 73A 74 74A 76 77

# 18.0 ELECTRICAL CHARACTERISTICS FOR PIC16C73/74

#### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                                    | 55 to +125°C                       |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage temperature                                                                                                               | 65°C to +150°C                     |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                                                | 0.3V to (VDD + 0.3V)               |

| Voltage on VDD with respect to Vss                                                                                                | 0.3 to +7.5V                       |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                      | 0 to +14V                          |

| Voltage on RA4 with respect to Vss                                                                                                | 0 to +14V                          |

| Total power dissipation (Note 1)                                                                                                  | 1.0W                               |

| Maximum current out of Vss pin                                                                                                    | 300 mA                             |

| Maximum current into VDD pin                                                                                                      | 250 mA                             |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                                      |                                    |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                                                    |                                    |

| Maximum output current sunk by any I/O pin                                                                                        | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                                                     | 25 mA                              |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                                               | 200 mA                             |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                                            | 200 mA                             |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                                                       | 200 mA                             |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                                                    | 200 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\Sigma$ IOH} + $\Sigma$ {(VDD -                   | Voh) x Ioh} + $\Sigma$ (Vol x Iol) |

| Note $0$ , $\lambda$ (alternative balance) (as a table $\overline{\mathbf{MOLD}}$ are inducting summation matching the $0$ or $0$ |                                    |

- **Note 2:** Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

- Note 3: PORTD and PORTE are not implemented on the PIC16C73.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### TABLE 18-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C73-04<br>PIC16C74-04                                                                                                                          | PIC16C73-10<br>PIC16C74-10                                                                                                                         | PIC16C73-20<br>PIC16C74-20                                                                                                                         | PIC16LC73-04<br>PIC16LC74-04                                                                               | JW Devices                                                                                                                                         |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                            | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 3.0V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 13.5 μA max. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                           |

| хт  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                            | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 3.0V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 13.5 μA max. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                           |

| HS  | VDD:         4.5V to 5.5V           IDD:         13.5 mA typ. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         4 MHz max. | VDD:         4.5V to 5.5V           IDD:         15 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         10 MHz max. | VDD:         4.5V to 5.5V           IDD:         30 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         20 MHz max. | Not recommended for<br>use in HS mode                                                                      | VDD:         4.5V to 5.5V           IDD:         30 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         20 MHz max. |

| LP  | VDD: 4.0V to 6.0V<br>IDD: 52.5 μA typ. at<br>32 kHz, 4.0V<br>IPD: 0.9 μA typ. at 4.0V<br>Freq: 200 kHz max.                                         | Not recommended for<br>use in LP mode                                                                                                              | Not recommended for<br>use in LP mode                                                                                                              | VDD: 3.0V to 6.0V<br>IDD: 48 μA max. at<br>32 kHz, 3.0V<br>IPD: 13.5 μA max. at 3.0V<br>Freq: 200 kHz max. | VDD: 3.0V to 6.0V<br>IDD: 48 μA max. at<br>32 kHz, 3.0V<br>IPD: 13.5 μA max. at 3.0V<br>Freq: 200 kHz max.                                         |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

| Applic       | able Devices 72 73 73A 74             | 74A 76 | 6 77                 |            |                                                    |                  |                                                                                                                      |

|--------------|---------------------------------------|--------|----------------------|------------|----------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------|

| 18.3         | PIC16<br>PIC16                        | 6C73/7 | 4-10 (Co<br>4-20 (Co | omr<br>omr | mercial,  <br>mercial,  <br>mercial,  <br>mercial, | Indust<br>Indust | rial)<br>rial)                                                                                                       |

|              |                                       |        |                      |            |                                                    |                  | less otherwise stated)                                                                                               |

| DC CH4       | ARACTERISTICS                         |        |                      |            | 0°C                                                | ; ≤              | $TA \le +85^{\circ}C$ for industrial and<br>$TA \le +70^{\circ}C$ for commercial<br>ibed in DC spec Section 18.1 and |

| Param<br>No. | Characteristic                        | Sym    | Min                  | Тур        | Max                                                | Units            | Conditions                                                                                                           |

| INO.         |                                       |        |                      | 1          |                                                    |                  |                                                                                                                      |

|              | Input Low Voltage                     | VIL    |                      |            |                                                    |                  |                                                                                                                      |

| D030         | with TTL buffer                       |        | Vss                  | -          | 0.15VDD                                            | v                | For entire VDD range                                                                                                 |

| D030A        |                                       |        | VSS                  | _          | 0.10VDD                                            | v                | $4.5V \le VDD \le 5.5V$                                                                                              |

| D031         | with Schmitt Trigger buffer           |        | VSS                  | -          | 0.2VDD                                             | v                |                                                                                                                      |

| D032         | MCLR, OSC1 (in RC mode)               |        | Vss                  | -          | 0.2VDD                                             | v                |                                                                                                                      |

| D033         | OSC1 (in XT, HS and LP)               |        | Vss                  | -          | 0.3VDD                                             | V                | Note1                                                                                                                |

|              | Input High Voltage                    |        |                      |            |                                                    |                  |                                                                                                                      |

|              | I/O ports                             | Vih    |                      | -          |                                                    |                  |                                                                                                                      |

| D040         | with TTL buffer                       |        | 2.0                  | -          | Vdd                                                | V                | $4.5V \le VDD \le 5.5V$                                                                                              |

| D040A        |                                       |        | 0.25VDD<br>+ 0.8V    | -          | Vdd                                                | V                | For entire VDD range                                                                                                 |

| D041         | with Schmitt Trigger buffer           |        | 0.8Vdd               | -          | Vdd                                                | v                | For entire VDD range                                                                                                 |

| D041         | MCLR                                  |        | 0.8VDD               | _          | VDD                                                | v                | Tor entire VDD range                                                                                                 |

| D042A        | OSC1 (XT, HS and LP)                  |        | 0.7VDD               | -          | VDD                                                | v                | Note1                                                                                                                |

| D043         | OSC1 (in RC mode)                     |        | 0.9VDD               | -          | VDD                                                | v                |                                                                                                                      |

| D070         | PORTB weak pull-up current            | IPURB  | 50                   | 250        |                                                    | μA               | VDD = 5V, VPIN = VSS                                                                                                 |

|              | Input Leakage Current<br>(Notes 2, 3) |        |                      |            |                                                    | Pr. 1            |                                                                                                                      |

| D060         | I/O ports                             | lı∟    | -                    | -          | ±1                                                 | μA               | Vss $\leq$ VPIN $\leq$ VDD, Pin at hi-impedance                                                                      |

| D061         | MCLR, RA4/T0CKI                       |        | -                    | -          | ±5                                                 | μA               | $Vss \le VPIN \le VDD$                                                                                               |

| D063         | OSC1                                  |        | -                    | -          | ±5                                                 | μA               | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration                                                          |

|              | Output Low Voltage                    |        |                      |            |                                                    |                  |                                                                                                                      |

| D080         | I/O ports                             | Vol    | -                    | -          | 0.6                                                | V                | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                                                                          |

| D083         | OSC2/CLKOUT (RC osc config)           |        | -                    | -          | 0.6                                                | V                | lOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                                                                          |

|              | Output High Voltage                   |        |                      |            |                                                    |                  |                                                                                                                      |

| D090         | I/O ports (Note 3)                    | Vон    | Vdd - 0.7            | -          | -                                                  | V                | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                                                                         |

| D092         | OSC2/CLKOUT (RC osc config)           |        | Vdd - 0.7            | -          | -                                                  | V                | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                                                                         |

| D150*        | Open-Drain High Voltage               | Vod    | -                    | -          | 14                                                 | V                | RA4 pin                                                                                                              |

|              |                                       | L      | L                    | L          | I                                                  | I                | · ·                                                                                                                  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C7X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

# Applicable Devices 72 73 73A 74 74A 76 77

# 19.2 DC Characteristics: PIC16LC73A/74A-04 (Commercial, Industrial)

| DC CHA                | RACTERISTICS                                                     |               |             | ard Ope<br>ing tem |              |                | itions (unless otherwise stated) $0^{\circ}C$ $\leq TA \leq +85^{\circ}C$ for industrial and $C$ $\leq TA \leq +70^{\circ}C$ for commercial                                                        |

|-----------------------|------------------------------------------------------------------|---------------|-------------|--------------------|--------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.          | Characteristic                                                   | Sym           | Min         | Тур†               | Max          | Units          | Conditions                                                                                                                                                                                         |

| D001                  | Supply Voltage                                                   | Vdd           | 2.5         | -                  | 6.0          | V              | LP, XT, RC osc configuration (DC - 4 MHz)                                                                                                                                                          |

| D002*                 | RAM Data Retention<br>Voltage (Note 1)                           | Vdr           | -           | 1.5                | -            | V              |                                                                                                                                                                                                    |

| D003                  | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR          | -           | Vss                | -            | V              | See section on Power-on Reset for details                                                                                                                                                          |

| D004*                 | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | Svdd          | 0.05        | -                  | -            | V/ms           | See section on Power-on Reset for details                                                                                                                                                          |

| D005                  | Brown-out Reset Voltage                                          | Bvdd          | 3.7         | 4.0                | 4.3          | V              | BODEN bit in configuration word enabled                                                                                                                                                            |

| D010                  | Supply Current (Note 2,5)                                        | IDD           | -           | 2.0                | 3.8          | mA             | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                                                                                      |

| D010A                 |                                                                  |               | -           | 22.5               | 48           | μA             | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                                                                                                                    |

| D015*                 | Brown-out Reset Current (Note 6)                                 | $\Delta$ IBOR | -           | 350                | 425          | μΑ             | BOR enabled VDD = 5.0V                                                                                                                                                                             |

| D020<br>D021<br>D021A | Power-down Current<br>(Note 3,5)                                 | IPD           | -<br>-<br>- | 7.5<br>0.9<br>0.9  | 30<br>5<br>5 | μΑ<br>μΑ<br>μΑ | $VDD = 3.0V$ , $WDT$ enabled, $-40^{\circ}C$ to $+85^{\circ}C$<br>$VDD = 3.0V$ , $WDT$ disabled, $0^{\circ}C$ to $+70^{\circ}C$<br>$VDD = 3.0V$ , $WDT$ disabled, $-40^{\circ}C$ to $+85^{\circ}C$ |

| D023*                 | Brown-out Reset Current<br>(Note 6)                              | ΔIBOR         | -           | 350                | 425          | μA             | BOR enabled VDD = 5.0V                                                                                                                                                                             |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD  $\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

# Applicable Devices 72 73 73A 74 74A 76 77

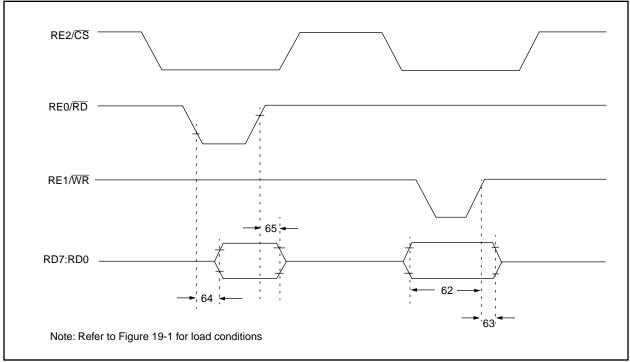

#### FIGURE 19-8: PARALLEL SLAVE PORT TIMING (PIC16C74A)

#### TABLE 19-7: PARALLEL SLAVE PORT REQUIREMENTS (PIC16C74A)

| Parameter<br>No. | Sym      | Characteristic                                                                          |                     | Min      | Тур† | Max      | Units    | Conditions             |

|------------------|----------|-----------------------------------------------------------------------------------------|---------------------|----------|------|----------|----------|------------------------|

| 62               | TdtV2wrH | Data in valid before $\overline{WR}^\uparrow$ or $\overline{CS}^\uparrow$ (setup time)  |                     | 20<br>25 | _    | _        | ns<br>ns | Extended<br>Range Only |

| 63*              | TwrH2dtl | $\overline{WR}^{\uparrow}$ or $\overline{CS}^{\uparrow}$ to data–in invalid (hold time) | PIC16 <b>C</b> 74A  | 20       | —    | —        | ns       |                        |

|                  |          |                                                                                         | PIC16 <b>LC</b> 74A | 35       | —    | -        | ns       |                        |

| 64               | TrdL2dtV | $\overline{RD}\downarrow$ and $\overline{CS}\downarrow$ to data–out valid               |                     | =        | _    | 80<br>90 | ns<br>ns | Extended<br>Range Only |

| 65               | TrdH2dtl | $\overline{RD}$ or $\overline{CS}$ to data–out invalid                                  |                     | 10       | —    | 30       | ns       |                        |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Applicable Devices

72

73

73A

74

76

77

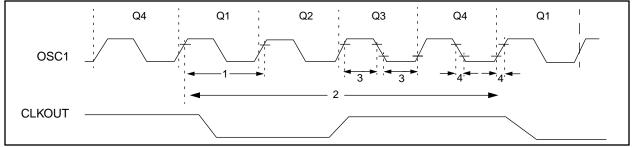

## 20.5 <u>Timing Diagrams and Specifications</u>

#### FIGURE 20-2: EXTERNAL CLOCK TIMING

#### TABLE 20-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                   | Min | Тур† | Мах    | Units | Conditions                             |

|------------------|-------|----------------------------------|-----|------|--------|-------|----------------------------------------|

|                  | Fosc  | External CLKIN Frequency         | DC  |      | 4      | MHz   | XT and RC osc mode                     |

|                  |       | (Note 1)                         | DC  | _    | 4      | MHz   | HS osc mode (-04)                      |

|                  |       |                                  | DC  | _    | 10     | MHz   | HS osc mode (-10)                      |

|                  |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)                      |

|                  |       |                                  | DC  | _    | 200    | kHz   | LP osc mode                            |

|                  |       | Oscillator Frequency             | DC  |      | 4      | MHz   | RC osc mode                            |

|                  |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode                            |

|                  |       |                                  | 4   | _    | 20     | MHz   | HS osc mode                            |

|                  |       |                                  | 5   | —    | 200    | kHz   | LP osc mode                            |

| 1                | Tosc  | External CLKIN Period            | 250 | _    | —      | ns    | XT and RC osc mode                     |

|                  |       | (Note 1)                         | 250 | _    | _      | ns    | HS osc mode (-04)                      |

|                  |       |                                  | 100 | _    | _      | ns    | HS osc mode (-10)                      |

|                  |       |                                  | 50  | _    | _      | ns    | HS osc mode (-20)                      |

|                  |       |                                  | 5   | _    | _      | μs    | LP osc mode                            |

|                  |       | Oscillator Period                | 250 |      | _      | ns    | RC osc mode                            |

|                  |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode                            |

|                  |       |                                  | 250 | _    | 250    | ns    | HS osc mode (-04)                      |

|                  |       |                                  | 100 | —    | 250    | ns    | HS osc mode (-10)<br>HS osc mode (-20) |

|                  |       |                                  | 50  | —    | 250    | ns    |                                        |

|                  |       |                                  | 5   | _    | _      | μs    | LP osc mode                            |

| 2                | Тсү   | Instruction Cycle Time (Note 1)  | 200 | Тсү  | DC     | ns    | Tcy = 4/Fosc                           |

| 3                | TosL, | External Clock in (OSC1) High or | 100 | _    | _      | ns    | XT oscillator                          |

|                  | TosH  | Low Time                         | 2.5 | —    | _      | μs    | LP oscillator                          |

|                  |       |                                  | 15  | —    | _      | ns    | HS oscillator                          |

| 4                | TosR, | External Clock in (OSC1) Rise or | _   | _    | 25     | ns    | XT oscillator                          |

|                  | TosF  | Fall Time                        | _   | _    | 50     | ns    | LP oscillator                          |

|                  |       |                                  | _   | _    | 15     | ns    | HS oscillator                          |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

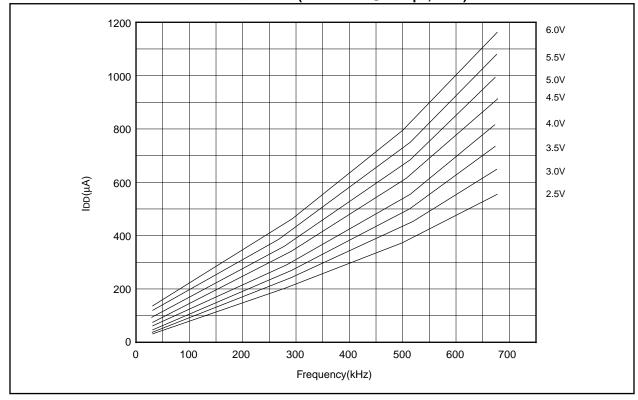

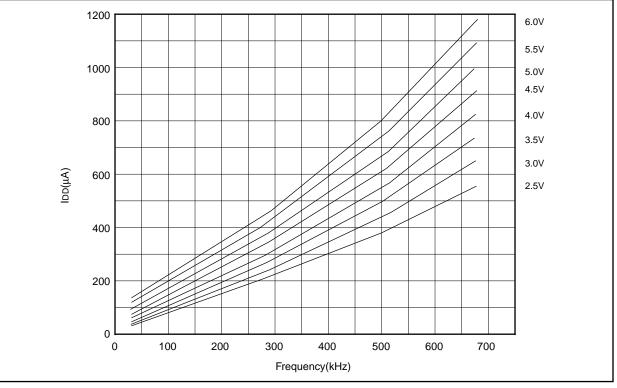

# Applicable Devices 72 73 73 74 74 76 77 FIGURE 21-16: TYPICAL IDD vs. FREQUENCY (RC MODE @ 300 pF, 25°C)

FIGURE 21-17: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 300 pF, -40°C TO 85°C)

Data based on matrix samples. See first page of this section for details.

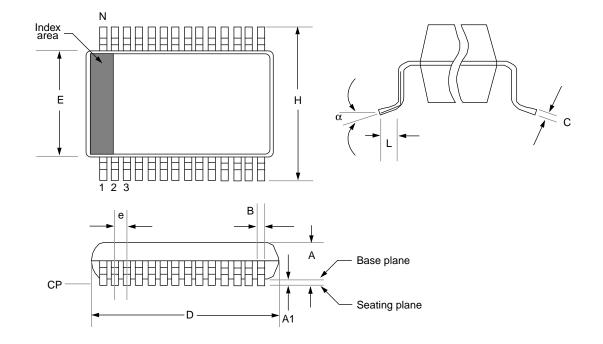

#### 22.6 28-Lead Plastic Surface Mount (SSOP - 209 mil Body 5.30 mm) (SS)

|        | Package Group: Plastic SSOP |             |           |       |            |           |

|--------|-----------------------------|-------------|-----------|-------|------------|-----------|

|        |                             | Millimeters |           |       |            |           |

| Symbol | Min                         | Max         | Notes     | Min   | Max        | Notes     |

| α      | 0°                          | <b>8</b> °  |           | 0°    | <b>8</b> ° |           |

| А      | 1.730                       | 1.990       |           | 0.068 | 0.078      |           |

| A1     | 0.050                       | 0.210       |           | 0.002 | 0.008      |           |

| В      | 0.250                       | 0.380       |           | 0.010 | 0.015      |           |

| С      | 0.130                       | 0.220       |           | 0.005 | 0.009      |           |

| D      | 10.070                      | 10.330      |           | 0.396 | 0.407      |           |

| E      | 5.200                       | 5.380       |           | 0.205 | 0.212      |           |

| е      | 0.650                       | 0.650       | Reference | 0.026 | 0.026      | Reference |

| Н      | 7.650                       | 7.900       |           | 0.301 | 0.311      |           |

| L      | 0.550                       | 0.950       |           | 0.022 | 0.037      |           |

| N      | 28                          | 28          |           | 28    | 28         |           |

| CP     | -                           | 0.102       |           | -     | 0.004      |           |

# APPENDIX C: WHAT'S NEW

Added the following devices:

- PIC16C76

- PIC16C77

Removed the PIC16C710, PIC16C71, PIC16C711 from this datasheet.