Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                    |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c73at-10-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.2.2.2 OPTION REGISTER

Applicable Devices 72 73 73 A 74 74 A 76 77

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the External INT Interrupt, TMR0, and the weak pull-ups on PORTB.

**Note:** To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer.

### FIGURE 4-8: OPTION REGISTER (ADDRESS 81h, 181h)

R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 **RBPU** INTEDG T0CS T0SE **PSA** PS2 PS<sub>1</sub> PS0 bit7 bit0

R = Readable bit W = Writable bit

U = Unimplemented bit, read as '0'

n = Value at POR reset

bit 7: RBPU: PORTB Pull-up Enable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

bit 6: INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RB0/INT pin

0 = Interrupt on falling edge of RB0/INT pin

bit 5: TOCS: TMR0 Clock Source Select bit

1 = Transition on RA4/T0CKI pin

0 = Internal instruction cycle clock (CLKOUT)

bit 4: T0SE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on RA4/T0CKI pin

0 = Increment on low-to-high transition on RA4/T0CKI pin

bit 3: PSA: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0: PS2:PS0: Prescaler Rate Select bits

| Bit Value | TMR0 Rate | WDT Rate |

|-----------|-----------|----------|

| 000       | 1:2       | 1:1      |

| 001       | 1:4       | 1:2      |

| 010       | 1:8       | 1:4      |

| 011       | 1:16      | 1:8      |

| 100       | 1:32      | 1:16     |

| 101       | 1:64      | 1:32     |

| 110       | 1:128     | 1:64     |

| 111       | 1:256     | 1 : 128  |

#### 4.2.2.4 PIE1 REGISTER

Applicable Devices 72 73 73 A 74 74 A 76 77

**Note:** Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

This register contains the individual enable bits for the peripheral interrupts.

# FIGURE 4-10: PIE1 REGISTER PIC16C72 (ADDRESS 8Ch)

| U-0       | R/W-0                                          | U-0        | U-0        | R/W-0      | R/W-0        | R/W-0  | R/W-0          |                                                                                               |  |  |  |  |

|-----------|------------------------------------------------|------------|------------|------------|--------------|--------|----------------|-----------------------------------------------------------------------------------------------|--|--|--|--|

| —<br>bit7 | ADIE                                           |            |            | SSPIE      | CCP1IE       | TMR2IE | TMR1IE<br>bit0 | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset |  |  |  |  |

| bit 7:    | Unimplen                                       | nented: R  | ead as '0' |            |              |        |                |                                                                                               |  |  |  |  |

| bit 6:    | <b>ADIE</b> : A/D<br>1 = Enable<br>0 = Disable | es the A/D | interrupt  |            | it           |        |                |                                                                                               |  |  |  |  |

| bit 5-4:  | Unimplemented: Read as '0'                     |            |            |            |              |        |                |                                                                                               |  |  |  |  |

| bit 3:    | SSPIE: Sy<br>1 = Enable<br>0 = Disable         | es the SSI | P interrup | t          | ipt Enable b | it     |                |                                                                                               |  |  |  |  |

| bit 2:    | <b>CCP1IE</b> : 0<br>1 = Enable<br>0 = Disable | es the CC  | P1 interru | pt         |              |        |                |                                                                                               |  |  |  |  |

| bit 1:    | <b>TMR2IE</b> : 7<br>1 = Enable<br>0 = Disabl  | es the TM  | R2 to PR2  | 2 match in | •            |        |                |                                                                                               |  |  |  |  |

| bit 0:    | TMR1IE: 7<br>1 = Enable<br>0 = Disable         | es the TM  | R1 overflo | w interrup | ot           |        |                |                                                                                               |  |  |  |  |

# 10.0 CAPTURE/COMPARE/PWM MODULE(s)

| Аp |    |     |    |     |    |    |      |

|----|----|-----|----|-----|----|----|------|

|    |    |     |    |     |    |    | CCP1 |

| 72 | 73 | 73A | 74 | 74A | 76 | 77 | CCP2 |

Each CCP (Capture/Compare/PWM) module contains a 16-bit register which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave Duty Cycle register. Both the CCP1 and CCP2 modules are identical in operation, with the exception of the operation of the special event trigger. Table 10-1 and Table 10-2 show the resources and interactions of the CCP module(s). In the following sections, the operation of a CCP module is described with respect to CCP1. CCP2 operates the same as CCP1, except where noted.

#### **CCP1** module:

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

#### **CCP2** module:

Capture/Compare/PWM Register2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. All are readable and writable.

For use of the CCP modules, refer to the Embedded Control Handbook, "Using the CCP Modules" (AN594).

TABLE 10-1: CCP MODE - TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

TABLE 10-2: INTERACTION OF TWO CCP MODULES

| CCPx Mode | <b>CCPy Mode</b> | Interaction                                                                           |

|-----------|------------------|---------------------------------------------------------------------------------------|

| Capture   | Capture          | Same TMR1 time-base.                                                                  |

| Capture   | Compare          | The compare should be configured for the special event trigger, which clears TMR1.    |

| Compare   | Compare          | The compare(s) should be configured for the special event trigger, which clears TMR1. |

| PWM       | PWM              | The PWMs will have the same frequency, and update rate (TMR2 interrupt).              |

| PWM       | Capture          | None                                                                                  |

| PWM       | Compare          | None                                                                                  |

### 11.2 SPI Mode for PIC16C72/73/73A/74/74A

This section contains register definitions and operational characteristics of the SPI module for the PIC16C72, PIC16C73, PIC16C73A, PIC16C74, PIC16C74A.

# FIGURE 11-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h)

| U-0      | U-0      | R-0                           | R-0         | R-0                                                  | R-0                          | R-0          | R-0          |                                                                              |

|----------|----------|-------------------------------|-------------|------------------------------------------------------|------------------------------|--------------|--------------|------------------------------------------------------------------------------|

| _        | _        | D/Ā                           | Р           | S                                                    | R/W                          | UA           | BF           | R = Readable bit                                                             |

| bit7     |          |                               |             |                                                      |                              |              | bit0         | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset |

| bit 7-6: | Unimpl   | emented                       | : Read as   | '0'                                                  |                              |              |              |                                                                              |

| bit 5:   | 1 = Indi | cates that                    | the last b  |                                                      | d or transmi<br>d or transmi |              |              |                                                                              |

| bit 4:   | 1 = Indi |                               | a stop bit  | has been                                             | leared wher<br>detected las  |              |              | abled, SSPEN is cleared)<br>T)                                               |

| bit 3:   | 1 = Indi |                               | a start bit | has been                                             | leared wher<br>detected las  |              |              | abled, SSPEN is cleared)<br>T)                                               |

| bit 2:   | This bit | holds the<br>o the next<br>ad | R/W bit i   | ation (I <sup>2</sup> C nnformation stop bit, or     | following the                | e last addre | ess match. T | his bit is valid from the addres                                             |

| bit 1:   | 1 = Indi | cates that                    | the user    | t I <sup>2</sup> C mode<br>needs to up<br>to be upda | date the ad                  | dress in the | SSPADD re    | egister                                                                      |

| bit 0:   | BF: Buf  | fer Full St                   | atus bit    |                                                      |                              |              |              |                                                                              |

|          | 1 = Rec  |                               | olete, SSF  | es)<br>PBUF is full<br>SSPBUF is                     | empty                        |              |              |                                                                              |

|          | 1 = Trar |                               | ogress, S   | SPBUF is f                                           |                              |              |              |                                                                              |

TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD<br>RATE<br>(K) | FOSC = 2 | 0 MHz<br>%<br>ERROR | SPBRG<br>value<br>(decimal) | 16 MHz<br>KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) | 10 MHz<br>KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) | 7.16 MH:<br>KBAUD | z<br>%<br>ERROR | SPBRG<br>value<br>(decimal) |

|---------------------|----------|---------------------|-----------------------------|-----------------|------------|-----------------------------|-----------------|------------|-----------------------------|-------------------|-----------------|-----------------------------|

| 9.6                 | 9.615    | +0.16               | 129                         | 9.615           | +0.16      | 103                         | 9.615           | +0.16      | 64                          | 9.520             | -0.83           | 46                          |

| 19.2                | 19.230   | +0.16               | 64                          | 19.230          | +0.16      | 51                          | 18.939          | -1.36      | 32                          | 19.454            | +1.32           | 22                          |

| 38.4                | 37.878   | -1.36               | 32                          | 38.461          | +0.16      | 25                          | 39.062          | +1.7       | 15                          | 37.286            | -2.90           | 11                          |

| 57.6                | 56.818   | -1.36               | 21                          | 58.823          | +2.12      | 16                          | 56.818          | -1.36      | 10                          | 55.930            | -2.90           | 7                           |

| 115.2               | 113.636  | -1.36               | 10                          | 111.111         | -3.55      | 8                           | 125             | +8.51      | 4                           | 111.860           | -2.90           | 3                           |

| 250                 | 250      | 0                   | 4                           | 250             | 0          | 3                           | NA              | -          | -                           | NA                | -               | -                           |

| 625                 | 625      | 0                   | 1                           | NA              | -          | -                           | 625             | 0          | 0                           | NA                | -               | -                           |

| 1250                | 1250     | 0                   | 0                           | NA              | -          | -                           | NA              | -          | -                           | NA                | -               | -                           |

| BAUD        | Fosc = 5 | .068 MHz   | SPBRG              | 4 MHz  |            | SPBRG              | 3.579 MH | Ηz         | SPBRG              | 1 MHz  |            | SPBRG              | 32.768 k | кНz        | SPBRG              |

|-------------|----------|------------|--------------------|--------|------------|--------------------|----------|------------|--------------------|--------|------------|--------------------|----------|------------|--------------------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD    | %<br>ERROR | value<br>(decimal) |

| 9.6         | 9.6      | 0          | 32                 | NA     | -          | -                  | 9.727    | +1.32      | 22                 | 8.928  | -6.99      | 6                  | NA       | -          | -                  |

| 19.2        | 18.645   | -2.94      | 16                 | 1.202  | +0.17      | 207                | 18.643   | -2.90      | 11                 | 20.833 | +8.51      | 2                  | NA       | -          | -                  |

| 38.4        | 39.6     | +3.12      | 7                  | 2.403  | +0.13      | 103                | 37.286   | -2.90      | 5                  | 31.25  | -18.61     | 1                  | NA       | -          | -                  |

| 57.6        | 52.8     | -8.33      | 5                  | 9.615  | +0.16      | 25                 | 55.930   | -2.90      | 3                  | 62.5   | +8.51      | 0                  | NA       | -          | -                  |

| 115.2       | 105.6    | -8.33      | 2                  | 19.231 | +0.16      | 12                 | 111.860  | -2.90      | 1                  | NA     | -          | -                  | NA       | -          | -                  |

| 250         | NA       | -          | -                  | NA     | -          | -                  | 223.721  | -10.51     | 0                  | NA     | -          | -                  | NA       | -          | -                  |

| 625         | NA       | -          | -                  | NA     | -          | -                  | NA       | -          | -                  | NA     | -          | -                  | NA       | -          | -                  |

| 1250        | NA       | -          | -                  | NA     | -          | -                  | NA       | -          | -                  | NA     | -          | -                  | NA       | -          | -                  |

**Note:** For the PIC16C73/73A/74/74A, the asynchronous high speed mode (BRGH = 1) may experience a high rate of receive errors. It is recommended that BRGH = 0. If you desire a higher baud rate than BRGH = 0 can support, refer to the device errata for additional information, or use the PIC16C76/77.

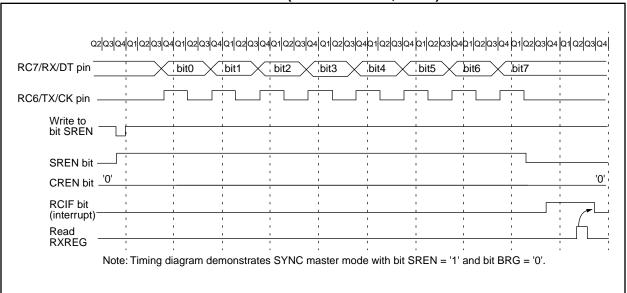

# 12.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>) or enable bit CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set then CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit which is reset by the hardware. In this case it is reset when the RCREG register has been read and is empty. The RCREG is a double buffered register, i.e. it is a two deep FIFO. It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full then overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set. The 9th receive bit is buffered the same way as the receive data. Reading the RCREG register, will load bit RX9D with a new value, therefore it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old RX9D information.

Steps to follow when setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. (Section 12.1)

- Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- If a single reception is required, set bit SREN. For continuous reception set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- If any error occurred, clear the error by clearing bit CREN.

TABLE 12-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Address | Name  | Bit 7                | Bit 6     | Bit 5     | Bit 4     | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|-------|----------------------|-----------|-----------|-----------|-------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF      | RCIF      | TXIF      | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA | SPEN                 | RX9       | SREN      | CREN      | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                 |

| 1Ah     | RCREG | USART R              | eceive Re | egister   |           |       |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE      | RCIE      | TXIE      | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA | CSRC                 | TX9       | TXEN      | SYNC      | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | SPBRG | Baud Rate            | Generat   | 0000 0000 | 0000 0000 |       |        |        |        |                          |                           |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

#### 12.4 <u>USART Synchronous Slave Mode</u>

Applicable Devices 72 73 73 A 74 74 A 76 77

Synchronous slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

# 12.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the synchronous master and slave modes are identical except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Transmission:

- Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- Enable the transmission by setting enable bit TXEN.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- Start transmission by loading data to the TXREG register.

# 12.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the synchronous master and slave modes is identical except in the case of the SLEEP mode. Also, bit SREN is a don't care in slave mode.

If receive is enabled, by setting bit CREN, prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- If interrupts are desired, then set enable bit RCIE.

- 3. If 9-bit reception is desired, then set bit RX9.

- 4. To enable reception, set enable bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- If any error occurred, clear the error by clearing bit CREN.

## FIGURE 13-2: ADCON1 REGISTER (ADDRESS 9Fh)

U-0

U-0

U-0

U-0

R/W-0

R/W-0

R/W-0

—

—

—

—

PCFG2

PCFG1

PCFG0

bit7

bit0

R = Readable bit W = Writable bit

U = Unimplementedbit, read as '0'n = Value at POR reset

bit 7-3: Unimplemented: Read as '0'

bit 2-0: PCFG2:PCFG0: A/D Port Configuration Control bits

| PCFG2:PCFG0 | RA0 | RA1 | RA2 | RA5 | RA3  | RE0 <sup>(1)</sup> | RE1 <sup>(1)</sup> | RE2 <sup>(1)</sup> | VREF |

|-------------|-----|-----|-----|-----|------|--------------------|--------------------|--------------------|------|

| 000         | Α   | Α   | Α   | Α   | Α    | Α                  | Α                  | Α                  | VDD  |

| 001         | Α   | Α   | Α   | Α   | VREF | Α                  | Α                  | Α                  | RA3  |

| 010         | Α   | Α   | Α   | Α   | Α    | D                  | D                  | D                  | VDD  |

| 011         | Α   | Α   | Α   | Α   | VREF | D                  | D                  | D                  | RA3  |

| 100         | Α   | Α   | D   | D   | Α    | D                  | D                  | D                  | VDD  |

| 101         | Α   | Α   | D   | D   | VREF | D                  | D                  | D                  | RA3  |

| 11x         | D   | D   | D   | D   | D    | D                  | D                  | D                  | _    |

A = Analog input

D = Digital I/O

Note 1: RE0, RE1, and RE2 are implemented on the PIC16C74/74A/77 only.

| BTFSS             | Bit Test 1              | f, Skip if S                                  | Set                  |                  | CALL              | Call Sul                             | oroutine                        |                                                           |                                |  |  |

|-------------------|-------------------------|-----------------------------------------------|----------------------|------------------|-------------------|--------------------------------------|---------------------------------|-----------------------------------------------------------|--------------------------------|--|--|

| Syntax:           | [ <i>label</i> ] B1     | ΓFSS f,b                                      |                      |                  | Syntax:           | [ label ]                            | CALL I                          | <b>(</b>                                                  |                                |  |  |

| Operands:         | $0 \le f \le 12$        | = =                                           |                      |                  | Operands:         | $0 \le k \le 2$                      | 2047                            |                                                           |                                |  |  |

|                   | $0 \le b < 7$           |                                               |                      |                  | Operation:        | (PC)+ 1-                             | → TOS,                          |                                                           |                                |  |  |

| Operation:        | skip if (f<             | :b>) = 1                                      |                      |                  |                   | $k \rightarrow PC$                   | ,                               |                                                           |                                |  |  |

| Status Affected:  | None                    |                                               |                      |                  |                   | (PCLATI                              | (PCLATH<4:3>) → PC<12:11>       |                                                           |                                |  |  |

| Encoding:         | 01 11bb bfff ffff       |                                               |                      |                  | Status Affected:  | None                                 | 1                               |                                                           |                                |  |  |

| Description:      |                         | register 'f' i                                |                      | he next          | Encoding:         | 10                                   | 0kkk                            | kkkk                                                      | kkkk                           |  |  |

|                   | If bit 'b' is discarded | is execute '1', then the and a NOF aking this | e next instr         | ed               | Description:      | (PC+1) is<br>eleven bit<br>into PC b | pushed or immediate its <10:0>. | st, return ac<br>nto the stac<br>e address i<br>The upper | ck. The<br>s loaded<br>bits of |  |  |

| Words:            | 1                       |                                               |                      |                  |                   |                                      | e loaded fi<br>ycle instru      | rom PĊĹAī<br>ction.                                       | Γ <b>H</b> . CALL              |  |  |

| Cycles:           | 1(2)                    |                                               |                      |                  | Words:            | 1                                    | ,                               |                                                           |                                |  |  |

| Q Cycle Activity: | Q1                      | Q2                                            | Q3                   | Q4               | Cycles:           | 2                                    |                                 |                                                           |                                |  |  |

|                   | Decode                  | Read<br>register 'f'                          | Process<br>data      | No-<br>Operation | Q Cycle Activity: | Q1                                   | Q2                              | Q3                                                        | Q4                             |  |  |

| If Skip:          | (2nd Cyc                | cle)                                          |                      |                  | 1st Cycle         | Decode                               | Read<br>literal 'k',            | Process<br>data                                           | Write to<br>PC                 |  |  |

| ·                 | Q1                      | Q2                                            | Q3                   | Q4               |                   |                                      | Push PC<br>to Stack             | data                                                      |                                |  |  |

|                   | No-<br>Operation        | No-<br>Operation                              | No-<br>Operation     | No-<br>Operation | 2nd Cycle         | No-<br>Operation                     | No-<br>Operation                | No-<br>Operation                                          | No-<br>Operation               |  |  |

| Example           | HERE<br>FALSE           | BTFSC<br>GOTO                                 | FLAG,1<br>PROCESS    | _CODE            | Example           | HERE                                 | CALL                            | THERE                                                     |                                |  |  |

|                   | TRUE                    | •                                             |                      |                  |                   | Before II                            | nstruction                      |                                                           |                                |  |  |

|                   |                         | •                                             |                      |                  |                   | After Ins                            | _                               | Address HE                                                | RE                             |  |  |

|                   | Before In               | etruction                                     |                      |                  |                   | 711101 1110                          |                                 | Address TH                                                | IERE                           |  |  |

|                   | After Inst              | PC = a<br>ruction<br>if FLAG<1:<br>PC =       | address F            |                  |                   |                                      | TOS = A                         | Address HE                                                | RE+1                           |  |  |

|                   |                         | if FLAG<1:<br>PC =                            | > = 1,<br>address TI | RUE              |                   |                                      |                                 |                                                           |                                |  |  |

DC CHARACTERISTICS

## **Applicable Devices** 72 73 73A 74 74A 76 77

18.3 DC Characteristics: PIC16C73/74-04 (Commercial, Industrial)

PIC16C73/74-10 (Commercial, Industrial) PIC16C73/74-20 (Commercial, Industrial)

PIC16LC73/74-04 (Commercial, Industrial)

#### Standard Operating Conditions (unless otherwise stated)

Operating temperature  $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$  for industrial and

$0^{\circ}$ C  $\leq TA \leq +70^{\circ}$ C for commercial

Operating voltage  $\ensuremath{\text{VDD}}$  range as described in DC spec Section 18.1 and

Section 18.2.

| Param | Characteristic              | Sym   | Min       | Тур | Max     | Units | Conditions                            |

|-------|-----------------------------|-------|-----------|-----|---------|-------|---------------------------------------|

| No.   |                             |       |           | l í |         |       |                                       |

|       | Input Low Voltage           |       |           |     |         |       |                                       |

|       | I/O ports                   | VIL   |           |     |         |       |                                       |

| D030  | with TTL buffer             |       | Vss       | -   | 0.15VDD | V     | For entire VDD range                  |

| D030A |                             |       | Vss       | -   | 0.8V    | V     | 4.5V ≤ VDD ≤ 5.5V                     |

| D031  | with Schmitt Trigger buffer |       | Vss       | -   | 0.2Vdd  | V     |                                       |

| D032  | MCLR, OSC1 (in RC mode)     |       | Vss       | -   | 0.2Vdd  | V     |                                       |

| D033  | OSC1 (in XT, HS and LP)     |       | Vss       | -   | 0.3Vdd  | V     | Note1                                 |

|       | Input High Voltage          |       |           |     |         |       |                                       |

|       | I/O ports                   | ViH   |           | -   |         |       |                                       |

| D040  | with TTL buffer             |       | 2.0       | -   | VDD     | V     | 4.5V ≤ VDD ≤ 5.5V                     |

| D040A |                             |       | 0.25VDD   | -   | VDD     | V     | For entire VDD range                  |

|       |                             |       | + 0.8V    |     |         |       |                                       |

|       |                             |       |           |     |         |       |                                       |

| D041  | with Schmitt Trigger buffer |       | 0.8VDD    | -   | VDD     | V     | For entire VDD range                  |

| D042  | MCLR                        |       | 0.8VDD    | -   | VDD     | V     |                                       |

| D042A | OSC1 (XT, HS and LP)        |       | 0.7VDD    | -   | VDD     | V     | Note1                                 |

| D043  | OSC1 (in RC mode)           |       | 0.9VDD    | -   | VDD     | V     |                                       |

| D070  | PORTB weak pull-up current  | IPURB | 50        | 250 | 400     | μΑ    | VDD = 5V, VPIN = VSS                  |

|       | Input Leakage Current       |       |           |     |         |       |                                       |

| Doco  | (Notes 2, 3)                | 1     |           |     |         |       | Vec < Ven < Ven CVen Die et hi immed  |

| D060  | I/O ports                   | lıL   | -         | -   | ±1      | μΑ    | Vss ≤ VPIN ≤ VDD, Pin at hi-impedance |

| D061  | MCLR, RA4/T0CKI             |       | _         | _   | ±5      | μA    | Vss ≤ VPIN ≤ VDD                      |

| D063  | OSC1                        |       | _         |     | ±5      | μA    | Vss ≤ VPIN ≤ VDD, XT, HS and LP osc   |

| D003  | 0361                        |       | _         | _   |         | μΛ    | configuration                         |

|       | Output Low Voltage          |       |           |     |         |       |                                       |

| D080  | I/O ports                   | VOL   | _         | _   | 0.6     | V     | IOL = 8.5 mA, VDD = 4.5V,             |

|       |                             |       |           |     |         | -     | -40°C to +85°C                        |

| D083  | OSC2/CLKOUT (RC osc config) |       | -         | -   | 0.6     | V     | IOL = 1.6 mA, VDD = 4.5V,             |

|       |                             |       |           |     |         |       | -40°C to +85°C                        |

|       | Output High Voltage         |       |           |     |         |       |                                       |

| D090  | I/O ports (Note 3)          | Voн   | VDD - 0.7 | -   | -       | V     | IOH = -3.0  mA, VDD = 4.5V,           |

|       |                             |       |           |     |         |       | -40°C to +85°C                        |

| D092  | OSC2/CLKOUT (RC osc config) |       | VDD - 0.7 | -   | -       | V     | IOH = -1.3  mA, VDD = 4.5V,           |

|       |                             |       |           |     |         |       | -40°C to +85°C                        |

| D150* | Open-Drain High Voltage     | Vod   | -         | -   | 14      | V     | RA4 pin                               |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C7X be driven with external clock in RC mode.

<sup>2:</sup> The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>3:</sup> Negative current is defined as current sourced by the pin.

**Applicable Devices** 72 73 73A 74 74A 76 77

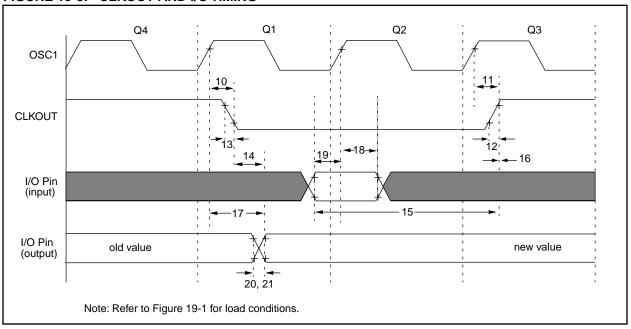

FIGURE 19-3: CLKOUT AND I/O TIMING

TABLE 19-3: CLKOUT AND I/O TIMING REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                        |                         | Min | Тур† | Max         | Units  | Conditions |

|--------------|----------|---------------------------------------|-------------------------|-----|------|-------------|--------|------------|

| 10*          | TosH2ckL | OSC1↑ to CLKOUT↓                      | _                       | 75  | 200  | ns          | Note 1 |            |

| 11*          | TosH2ckH | OSC1↑ to CLKOUT↑                      |                         | _   | 75   | 200         | ns     | Note 1     |

| 12*          | TckR     | CLKOUT rise time                      |                         | _   | 35   | 100         | ns     | Note 1     |

| 13*          | TckF     | CLKOUT fall time                      |                         | _   | 35   | 100         | ns     | Note 1     |

| 14*          | TckL2ioV | CLKOUT ↓ to Port out valid            | d                       | _   | _    | 0.5Tcy + 20 | ns     | Note 1     |

| 15*          | TioV2ckH | Port in valid before CLKOL            | Tosc + 200              | _   | _    | ns          | Note 1 |            |

| 16*          | TckH2ioI | Port in hold after CLKOUT ↑           |                         | 0   | _    | _           | ns     | Note 1     |

| 17*          | TosH2ioV | OSC1↑ (Q1 cycle) to<br>Port out valid |                         | _   | 50   | 150         | ns     |            |

| 18*          | TosH2ioI | OSC1↑ (Q2 cycle) to                   | PIC16 <b>C</b> 73A/74A  | 100 | _    | _           | ns     |            |

|              |          | Port input invalid (I/O in hold time) | PIC16 <b>LC</b> 73A/74A | 200 | _    | _           | ns     |            |

| 19*          | TioV2osH | Port input valid to OSC1↑             | (I/O in setup time)     | 0   | _    | _           | ns     |            |

| 20*          | TioR     | Port output rise time                 | PIC16 <b>C</b> 73A/74A  | _   | 10   | 40          | ns     |            |

|              |          |                                       | PIC16 <b>LC</b> 73A/74A | _   | _    | 80          | ns     |            |

| 21*          | TioF     | Port output fall time                 | PIC16 <b>C</b> 73A/74A  | _   | 10   | 40          | ns     |            |

|              |          |                                       | PIC16 <b>LC</b> 73A/74A | _   | _    | 80          | ns     |            |

| 22††*        | Tinp     | INT pin high or low time              | 1                       | Tcy | _    | _           | ns     |            |

| 23††*        | Trbp     | RB7:RB4 change INT high               | or low time             | Tcy | _    | _           | ns     |            |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup>Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>††</sup> These parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

# PIC16C7X

**Applicable Devices** 72 73 73A 74 74A 76 77

#### **TABLE 20-13: A/D CONVERTER CHARACTERISTICS:**

PIC16C76/77-04 (Commercial, Industrial, Extended) PIC16C76/77-10 (Commercial, Industrial, Extended) PIC16C76/77-20 (Commercial, Industrial, Extended) PIC16LC76/77-04 (Commercial, Industrial)

| Param<br>No. | Sym                                      | Characteristic                            |                       | Min       | Тур†       | Max        | Units                                                                                              | Conditions                                     |

|--------------|------------------------------------------|-------------------------------------------|-----------------------|-----------|------------|------------|----------------------------------------------------------------------------------------------------|------------------------------------------------|

| A01          | NR                                       | Resolution                                |                       | _         | _          | 8-bits     | bit                                                                                                | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF       |

| A02          | EABS                                     | Total Absolute error                      |                       | _         | _          | < ± 1      | LSb                                                                                                | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF       |

| A03          | EIL                                      | Integral linearity error                  |                       | _         | _          | < ± 1      | LSb                                                                                                | $VREF = VDD = 5.12V$ , $VSS \le VAIN \le VREF$ |

| A04          | EDL                                      | Differential linearity error              |                       | _         | _          | < ± 1      | LSb                                                                                                | $VREF = VDD = 5.12V$ , $VSS \le VAIN \le VREF$ |

| A05          | EFS                                      | Full scale error                          |                       | _         | _          | < ± 1      | LSb                                                                                                | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF       |

| A06          | Eoff                                     | Offset error                              |                       | _         | _          | < ± 1      | LSb                                                                                                | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF       |

| A10          | _                                        | Monotonicity                              |                       | _         | guaranteed | _          | _                                                                                                  | Vss ≤ Vain ≤ Vref                              |

| A20          | VREF                                     | Reference voltage                         |                       | 3.0V      | _          | VDD + 0.3  | V                                                                                                  |                                                |

| A25          | VAIN                                     | Analog input voltage                      |                       | Vss - 0.3 | _          | VREF + 0.3 | V                                                                                                  |                                                |

| A30          | ZAIN                                     | Recommended impedar analog voltage source | ce of                 | _         | _          | 10.0       | kΩ                                                                                                 |                                                |

| A40          | IAD                                      | A/D conversion current                    | PIC16 <b>C</b> 76/77  | _         | 180        | _          | μΑ                                                                                                 | Average current consump-                       |

|              |                                          | (VDD)                                     | PIC16 <b>LC</b> 76/77 | _         | 90         | _          | μА                                                                                                 | tion when A/D is on.<br>(Note 1)               |

| A50          | A50   IREF   VREF input current (Note 2) |                                           | 10                    | _         | 1000       | μА         | During VAIN acquisition. Based on differential of VHOLD to VAIN to charge CHOLD, see Section 13.1. |                                                |

|              |                                          |                                           |                       | _         | _          | 10         | μА                                                                                                 | During A/D Conversion cycle                    |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: When A/D is off, it will not consume any current other than minor leakage current.

- The power-down current spec includes any such leakage from the A/D module.

- 2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

# **Applicable Devices** 72 73 73A 74 74A 76 77

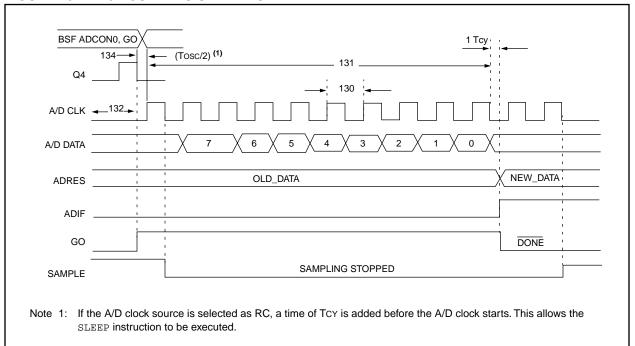

#### FIGURE 20-17: A/D CONVERSION TIMING

#### **TABLE 20-14: A/D CONVERSION REQUIREMENTS**

| Param<br>No. | Sym  | Characteristic                                    |                       | Min    | Тур†     | Max | Units | Conditions                                                                                                                                                                                                  |

|--------------|------|---------------------------------------------------|-----------------------|--------|----------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D clock period                                  | PIC16 <b>C</b> 76/77  | 1.6    | _        |     | μs    | Tosc based, VREF ≥ 3.0V                                                                                                                                                                                     |

|              |      |                                                   | PIC16 <b>LC</b> 76/77 | 2.0    | _        | _   | μs    | Tosc based, VREF full range                                                                                                                                                                                 |

|              |      |                                                   | PIC16 <b>C</b> 76/77  | 2.0    | 4.0      | 6.0 | μs    | A/D RC Mode                                                                                                                                                                                                 |

|              |      |                                                   | PIC16 <b>LC</b> 76/77 | 3.0    | 6.0      | 9.0 | μs    | A/D RC Mode                                                                                                                                                                                                 |

| 131          | TCNV | Conversion time (not including S/H time) (Note 1) |                       | _      | 9.5      | _   | TAD   |                                                                                                                                                                                                             |

| 132          | TACQ | Acquisition time                                  |                       | Note 2 | 20       | _   | μs    |                                                                                                                                                                                                             |

|              |      |                                                   |                       | 5*     | _        | _   | μs    | The minimum time is the amplifier settling time. This may be used if the "new" input voltage has not changed by more than 1 LSb (i.e., 20.0 mV @ 5.12V) from the last sampled voltage (as stated on CHOLD). |

| 134          | TGO  | Q4 to A/D clock start                             |                       | _      | Tosc/2 § | _   | _     | If the A/D clock source is selected as RC, a time of Tcy is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                            |

| 135          | Tswc | Switching from convert                            | → sample time         | 1.5 §  | _        | _   | TAD   |                                                                                                                                                                                                             |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- § This specification ensured by design.

- Note 1: ADRES register may be read on the following TcY cycle.

- 2: See Section 13.1 for min conditions.

**Applicable Devices** 72 73 73A 74 74A 76 77

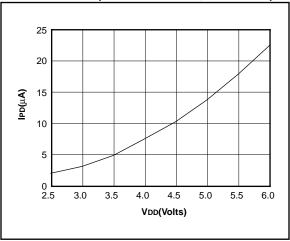

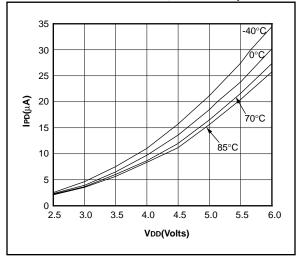

FIGURE 21-3: TYPICAL IPD vs. VDD @ 25°C (WDT ENABLED, RC MODE)

FIGURE 21-4: MAXIMUM IPD vs. VDD (WDT ENABLED, RC MODE)

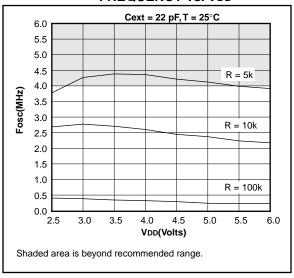

FIGURE 21-5: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

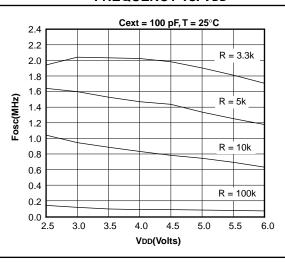

FIGURE 21-6: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

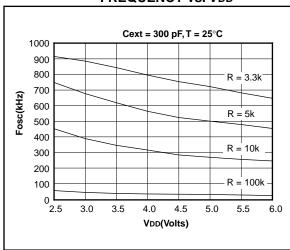

FIGURE 21-7: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

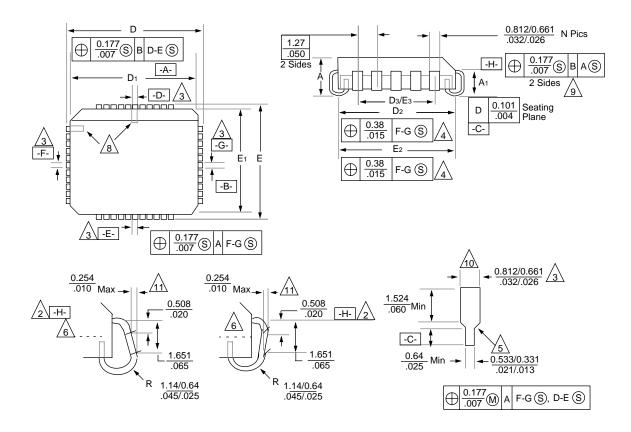

## 22.7 44-Lead Plastic Leaded Chip Carrier (Square)(PLCC)

|        | Package Group: Plastic Leaded Chip Carrier (PLCC) |             |           |       |       |           |  |  |  |

|--------|---------------------------------------------------|-------------|-----------|-------|-------|-----------|--|--|--|

|        |                                                   | Millimeters |           |       |       |           |  |  |  |

| Symbol | Min                                               | Max         | Notes     | Min   | Max   | Notes     |  |  |  |

| Α      | 4.191                                             | 4.572       |           | 0.165 | 0.180 |           |  |  |  |

| A1     | 2.413                                             | 2.921       |           | 0.095 | 0.115 |           |  |  |  |

| D      | 17.399                                            | 17.653      |           | 0.685 | 0.695 |           |  |  |  |

| D1     | 16.510                                            | 16.663      |           | 0.650 | 0.656 |           |  |  |  |

| D2     | 15.494                                            | 16.002      |           | 0.610 | 0.630 |           |  |  |  |

| D3     | 12.700                                            | 12.700      | Reference | 0.500 | 0.500 | Reference |  |  |  |

| Е      | 17.399                                            | 17.653      |           | 0.685 | 0.695 |           |  |  |  |

| E1     | 16.510                                            | 16.663      |           | 0.650 | 0.656 |           |  |  |  |

| E2     | 15.494                                            | 16.002      |           | 0.610 | 0.630 |           |  |  |  |

| E3     | 12.700                                            | 12.700      | Reference | 0.500 | 0.500 | Reference |  |  |  |

| N      | 44                                                | 44          |           | 44    | 44    |           |  |  |  |

| CP     | _                                                 | 0.102       |           | _     | 0.004 |           |  |  |  |

| LT     | 0.203                                             | 0.381       |           | 0.008 | 0.015 |           |  |  |  |

#### 1.0ø (0.039ø) Ref. 11°/13°(4x) Pin#1 Pin#1 2 == 0° Min Ε E1 11°/13°(4x) Detail B -3.0ø (0<sup>.</sup>.118ø) Ref. R1 0.08 Min Option 1 (TOP side) R 0.08/0.20 Option 2 (TOP side) Gage Plane Base Metal Lead Finish 0.20 Min С · c1 **Detail A Detail B** 1.00 Ref 1.00 Ref. b1 **Detail B Detail A**

### 22.9 44-Lead Plastic Surface Mount (TQFP 10x10 mm Body 1.0/0.10 mm Lead Form) (TQ)

|        | Package Group: Plastic TQFP |             |       |       |        |       |  |  |

|--------|-----------------------------|-------------|-------|-------|--------|-------|--|--|

|        |                             | Millimeters |       |       | Inches |       |  |  |

| Symbol | Min                         | Max         | Notes | Min   | Max    | Notes |  |  |

| А      | 1.00                        | 1.20        |       | 0.039 | 0.047  |       |  |  |

| A1     | 0.05                        | 0.15        |       | 0.002 | 0.006  |       |  |  |

| A2     | 0.95                        | 1.05        |       | 0.037 | 0.041  |       |  |  |

| D      | 11.75                       | 12.25       |       | 0.463 | 0.482  |       |  |  |

| D1     | 9.90                        | 10.10       |       | 0.390 | 0.398  |       |  |  |

| Е      | 11.75                       | 12.25       |       | 0.463 | 0.482  |       |  |  |

| E1     | 9.90                        | 10.10       |       | 0.390 | 0.398  |       |  |  |

| L      | 0.45                        | 0.75        |       | 0.018 | 0.030  |       |  |  |

| е      | 0.80                        | BSC         |       | 0.031 | BSC    |       |  |  |

| b      | 0.30                        | 0.45        |       | 0.012 | 0.018  |       |  |  |

| b1     | 0.30                        | 0.40        |       | 0.012 | 0.016  |       |  |  |

| С      | 0.09                        | 0.20        |       | 0.004 | 0.008  |       |  |  |

| c1     | 0.09                        | 0.16        |       | 0.004 | 0.006  |       |  |  |

| N      | 44                          | 44          |       | 44    | 44     |       |  |  |

| Θ      | 0°                          | 7°          |       | 0°    | 7°     |       |  |  |

- Note 1: Dimensions D1 and E1 do not include mold protrusion. Allowable mold protrusion is 0.25m/m (0.010") per side. D1 and E1 dimensions including mold mismatch.

- 2: Dimension "b" does not include Dambar protrusion, allowable Dambar protrusion shall be 0.08m/m (0.003")max.

- 3: This outline conforms to JEDEC MS-026.

## **APPENDIX E: PIC16/17 MICROCONTROLLERS**

# E.1 PIC12CXXX Family of Devices

|             |                                      | PIC12C508       | PIC12C509       | PIC12C671       | PIC12C672       |

|-------------|--------------------------------------|-----------------|-----------------|-----------------|-----------------|

| Clock       | Maximum Frequency of Operation (MHz) | 4               | 4               | 4               | 4               |

| Memory      | EPROM Program Memory                 | 512 x 12        | 1024 x 12       | 1024 x 14       | 2048 x 14       |

| Wellioty    | Data Memory (bytes)                  | 25              | 41              | 128             | 128             |

| Peripherals | Timer Module(s)                      | TMR0            | TMR0            | TMR0            | TMR0            |

| rempherais  | A/D Converter (8-bit) Channels       | _               | _               | 4               | 4               |

|             | Wake-up from SLEEP on pin change     | Yes             | Yes             | Yes             | Yes             |

|             | I/O Pins                             | 5               | 5               | 5               | 5               |

|             | Input Pins                           | 1               | 1               | 1               | 1               |

| Features    | Internal Pull-ups                    | Yes             | Yes             | Yes             | Yes             |

|             | Voltage Range (Volts)                | 2.5-5.5         | 2.5-5.5         | 2.5-5.5         | 2.5-5.5         |

|             | In-Circuit Serial Programming        | Yes             | Yes             | Yes             | Yes             |

|             | Number of Instructions               | 33              | 33              | 35              | 35              |

|             | Packages                             | 8-pin DIP, SOIC | 8-pin DIP, SOIC | 8-pin DIP, SOIC | 8-pin DIP, SOIC |

All PIC12C5XX devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC12C5XX devices use serial programming with data pin GP1 and clock pin GP0.

# E.2 PIC14C000 Family of Devices

|             |                                                 | PIC14C000                                                                                                                                                                  |

|-------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock       | Maximum Frequency of Operation (MHz)            | 20                                                                                                                                                                         |

|             | EPROM Program Memory (x14 words)                | 4K                                                                                                                                                                         |

| Memory      | Data Memory (bytes)                             | 192                                                                                                                                                                        |

| incilior y  | Timer Module(s)                                 | TMR0<br>ADTMR                                                                                                                                                              |

| Peripherals | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | I <sup>2</sup> C with SMBus<br>Support                                                                                                                                     |

|             | Slope A/D Converter Channels                    | 8 External; 6 Internal                                                                                                                                                     |

|             | Interrupt Sources                               | 11                                                                                                                                                                         |

|             | I/O Pins                                        | 22                                                                                                                                                                         |

|             | Voltage Range (Volts)                           | 2.7-6.0                                                                                                                                                                    |

| Features    | In-Circuit Serial Programming                   | Yes                                                                                                                                                                        |

|             | Additional On-chip Features                     | Internal 4MHz Oscillator, Bandgap Reference, Temperature Sensor, Calibration Factors, Low Voltage Detector, SLEEP, HIBERNATE, Comparators with Programmable References (2) |

|             | Packages                                        | 28-pin DIP (.300 mil), SOIC, SSOP                                                                                                                                          |

# PIC16C7X

| CCP2IF bit38                                 | F                                         |           |

|----------------------------------------------|-------------------------------------------|-----------|

| CCPR1H Register25, 27, 29, 71                | Family of Devices                         |           |

| CCPR1L Register29, 71                        | PIC12CXXX                                 | 265       |

| CCPR2H Register25, 27, 29, 71                | PIC14C000                                 |           |

| CCPR2L Register25, 27, 29, 71                | PIC16C15X                                 |           |

| CCPxM0 bit                                   | PIC16C55X                                 |           |

| CCPxM1 bit72                                 | PIC16C5X                                  | 266       |

| CCPxM2 bit72                                 | PIC16C62X and PIC16C64X                   |           |

| CCPxM3 bit72                                 | PIC16C6X                                  |           |

| CCPxX bit72                                  | PIC16C7XX                                 | 6         |

| CCPxY bit72                                  | PIC16C8X                                  | 269       |

| CKE83                                        | PIC16C9XX                                 | 269       |

| CKP                                          | PIC17CXX                                  | 270       |

| Clock Polarity Select bit, CKP79, 84         | FERR bit                                  | 100       |

| Clock Polarity, SPI Mode81                   | FSR Register 23, 24, 25, 26, 27, 2        | 8, 29, 41 |

| Clocking Scheme17                            | Fuzzy Logic Dev. System (fuzzyTECH®-MP)   | 163, 165  |

| Code Examples                                |                                           |           |

| Call of a Subroutine in Page 1 from Page 041 | G                                         |           |

| Changing Between Capture Prescalers          | General Description                       | 5         |

| Changing Prescaler (Timer0 to WDT)           | GIE bit                                   | 141       |

| Changing Prescaler (WDT to Timer0)63         | 1                                         |           |

| I/O Programming53                            | 1                                         |           |

| Indirect Addressing41                        | I/O Ports                                 |           |

| Initializing PORTA                           | PORTA                                     |           |

| Initializing PORTB                           | PORTB                                     |           |

| Initializing PORTC                           | PORTC                                     |           |

| Loading the SSPBUF Register                  | PORTD                                     | ,         |

| Code Protection                              | PORTE                                     |           |

| Computed GOTO                                | Section                                   |           |

| Configuration Bits                           | I/O Programming Considerations            | 53        |

| Configuration Word                           | I <sup>2</sup> C                          |           |

| Connecting Two Microcontrollers              | Addressing                                |           |

| CREN bit                                     | Addressing I <sup>2</sup> C Devices       |           |

| <u>CS</u> pin54                              | Arbitration                               |           |

| D                                            | Block Diagram                             |           |

|                                              | Clock Synchronization                     |           |

| Data/Address bit, D/A                        | Combined Format                           |           |

| DC bit                                       | I <sup>2</sup> C Operation                |           |

| DC Characteristics                           | I <sup>2</sup> C Overview                 |           |

| PIC16C72168                                  | Initiating and Terminating Data Transfer  |           |

| PIC16C73184                                  | Master Mode                               |           |

| PIC16C73A 202                                | Master-Receiver Sequence                  |           |

| PIC16C74                                     | Master-Transmitter Sequence               |           |

| PIC16C74A                                    | Mode                                      |           |

| PIC16C76                                     | Mode Selection                            |           |

| PIC16C76                                     | Multi-master                              |           |

| Development Support                          | Multi-Master Mode                         |           |

| Development Tools                            | Reception                                 |           |

| Digit Carry bit9                             | Reception Timing Diagram                  |           |

| Direct Addressing41                          | SCL and SDA pins                          |           |

| Direct Addressing                            | Slave Mode                                |           |

| E                                            | START                                     |           |

| Electrical Characteristics                   | STOP                                      |           |

| PIC16C72167                                  | Transfer Acknowledge                      |           |

| PIC16C73183                                  | Transmission                              |           |

| PIC16C73A201                                 | IDLE_MODE                                 |           |

| PIC16C74183                                  | In-Circuit Serial Programming             |           |

| PIC16C74A201                                 | INDE Desister                             |           |

| PIC16C76219                                  | INDF Register                             |           |

| PIC16C77219                                  | Indirect Addressing                       |           |

| External Brown-out Protection Circuit140     | Initialization Condition for all Register |           |

| External Power-on Reset Circuit140           | Instruction Cycle                         |           |

|                                              | Instruction Flow/Pipelining               |           |

|                                              | Instruction Format                        | 147       |

# PIC16C7X

| LIST OF      | FIGURES                                | Figure 8-1:                | T1CON: Timer1 Control Register              | 0.5   |

|--------------|----------------------------------------|----------------------------|---------------------------------------------|-------|

| Fig 2. 4.    | DICACCZO Dia da Dia mana               | Figure 9.2:                | (Address 10h)                               |       |

| Figure 3-1:  | PIC16C72 Block Diagram                 | Figure 8-2:<br>Figure 9-1: | Timer1 Block Diagram                        |       |

| Figure 3-2:  | PIC16C73/73A/76 Block Diagram          | -                          | Timer2 Block Diagram                        | 09    |

| Figure 3-3:  | PIC16C74/74A/77 Block Diagram12        | Figure 9-2:                | T2CON: Timer2 Control Register              | 70    |

| Figure 3-4:  | Clock/Instruction Cycle17              | Figure 40.4.               | (Address 12h)                               | 70    |

| Figure 4-1:  | PIC16C72 Program Memory Map            | Figure 10-1:               | CCP1CON Register (Address 17h)/             | 70    |

| =            | and Stack                              | F: 40.0                    | CCP2CON Register (Address 1Dh)              | / 2   |

| Figure 4-2:  | PIC16C73/73A/74/74A Program            | Figure 10-2:               | Capture Mode Operation                      | 70    |

|              | Memory Map and Stack19                 | Fi                         | Block Diagram                               | 72    |

| Figure 4-3:  | PIC16C76/77 Program Memory             | Figure 10-3:               | Compare Mode Operation                      | 70    |

|              | Map and Stack20                        | F: 40 4                    | Block Diagram                               |       |

| Figure 4-4:  | PIC16C72 Register File Map21           | Figure 10-4:               | Simplified PWM Block Diagram                |       |

| Figure 4-5:  | PIC16C73/73A/74/74A Register           | Figure 10-5:               | PWM Output                                  | /4    |

| =            | File Map21                             | Figure 11-1:               | SSPSTAT: Sync Serial Port Status            | 70    |

| Figure 4-6:  | PIC16C76/77 Register File Map22        | Firm 44.0                  | Register (Address 94h)                      | /8    |

| Figure 4-7:  | Status Register (Address 03h,          | Figure 11-2:               | SSPCON: Sync Serial Port Control            | 70    |

|              | 83h, 103h, 183h)30                     | F: 44.0                    | Register (Address 14h)                      |       |

| Figure 4-8:  | OPTION Register (Address 81h,          | Figure 11-3:               | SSP Block Diagram (SPI Mode)                |       |

|              | 181h)31                                | Figure 11-4:               | SPI Master/Slave Connection                 | 81    |

| Figure 4-9:  | INTCON Register                        | Figure 11-5:               | SPI Mode Timing, Master Mode                | 00    |

|              | (Address 0Bh, 8Bh, 10bh, 18bh)32       | F: 44.0                    | or Slave Mode w/o SS Control                | 82    |

| Figure 4-10: | PIE1 Register PIC16C72                 | Figure 11-6:               | SPI Mode Timing, Slave Mode with            |       |

|              | (Address 8Ch)33                        | F: 44.7                    | SS Control                                  | 82    |

| Figure 4-11: | PIE1 Register PIC16C73/73A/            | Figure 11-7:               | SSPSTAT: Sync Serial Port Status            |       |

|              | 74/74A/76/77 (Address 8Ch)34           | =                          | Register (Address 94h)(PIC16C76/77)         | 83    |

| Figure 4-12: | PIR1 Register PIC16C72                 | Figure 11-8:               | SSPCON: Sync Serial Port Control            |       |

|              | (Address 0Ch)35                        |                            | Register (Address 14h)(PIC16C76/77)         | 84    |

| Figure 4-13: | PIR1 Register PIC16C73/73A/            | Figure 11-9:               | SSP Block Diagram (SPI Mode)                |       |

|              | 74/74A/76/77 (Address 0Ch)36           |                            | (PIC16C76/77)                               | 85    |