Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | A/D 8x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c74a-04-l |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

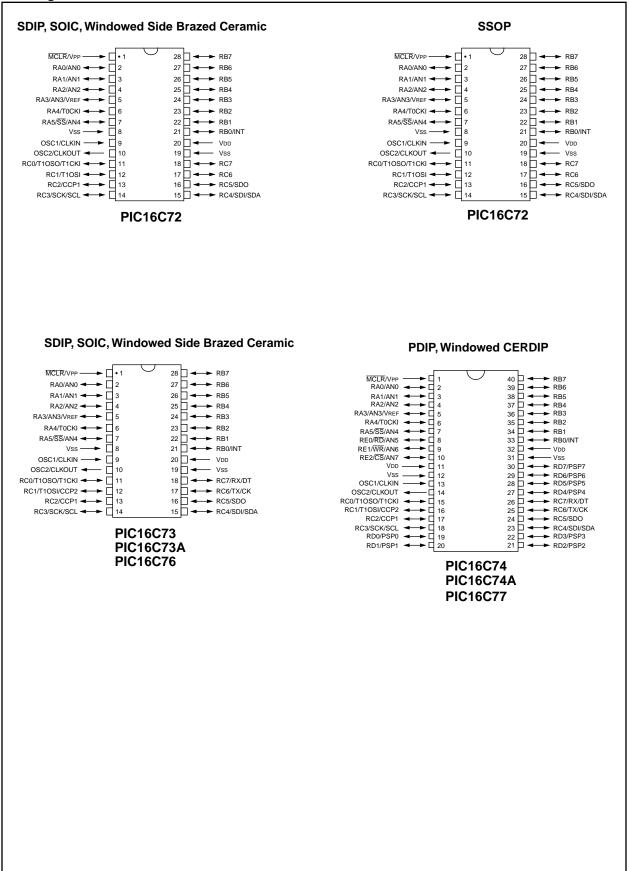

#### **Pin Diagrams**

| Address              | Name    | Bit 7              | Bit 6              | Bit 5                   | Bit 4          | Bit 3        | Bit 2           | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(3) |  |  |  |

|----------------------|---------|--------------------|--------------------|-------------------------|----------------|--------------|-----------------|---------------|-----------|--------------------------|-------------------------------------|--|--|--|

| Bank 1               | •       | •                  |                    |                         | •              | •            |                 | •             | •         |                          | ·                                   |  |  |  |

| 80h <sup>(1)</sup>   | INDF    | Addressing         | this location      | uses conter             | nts of FSR to  | address data | a memory (n     | ot a physical | register) | 0000 0000                | 0000 0000                           |  |  |  |

| 81h                  | OPTION  | RBPU               | INTEDG             | TOCS                    | TOSE           | PSA          | PS2             | PS1           | PS0       | 1111 1111                | 1111 1111                           |  |  |  |

| 82h <sup>(1)</sup>   | PCL     | Program Co         | ounter's (PC)      | Least Signi             | ficant Byte    |              |                 |               |           | 0000 0000                | 0000 0000                           |  |  |  |

| 83h <sup>(1)</sup>   | STATUS  | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup> | С                       | 0001 1xxx      | 000q quuu    |                 |               |           |                          |                                     |  |  |  |

| 84h <sup>(1)</sup>   | FSR     | Indirect data      | a memory ad        | dress pointe            | er             |              |                 |               |           | xxxx xxxx                | uuuu uuuu                           |  |  |  |

| 85h                  | TRISA   | _                  | —                  | PORTA Dat               | ta Direction F | Register     |                 |               |           | 11 1111                  | 11 1111                             |  |  |  |

| 86h                  | TRISB   | PORTB Dat          | ta Direction F     | Register                |                |              |                 |               |           | 1111 1111                | 1111 1111                           |  |  |  |

| 87h                  | TRISC   | PORTC Da           | ta Direction F     | Register                |                |              |                 |               |           | 1111 1111                | 1111 1111                           |  |  |  |

| 88h                  | _       | Unimpleme          | nted               |                         | -              | _            |                 |               |           |                          |                                     |  |  |  |

| 89h                  | -       | Unimpleme          | nted               |                         |                |              |                 |               |           | -                        | -                                   |  |  |  |

| 8Ah <sup>(1,2)</sup> | PCLATH  | —                  | —                  | —                       | Write Buffe    | for the uppe | er 5 bits of th | e PC          |           | 0 0000                   | 0 0000                              |  |  |  |

| 8Bh <b>(1)</b>       | INTCON  | GIE                | PEIE               | TOIE                    | INTE           | RBIE         | TOIF            | INTF          | RBIF      | 0000 000x                | 0000 000u                           |  |  |  |

| 8Ch                  | PIE1    | —                  | ADIE               | —                       | _              | SSPIE        | CCP1IE          | TMR2IE        | TMR1IE    | -0 0000                  | -0 0000                             |  |  |  |

| 8Dh                  | —       | Unimpleme          | nted               |                         |                |              |                 |               |           | —                        | —                                   |  |  |  |

| 8Eh                  | PCON    | —                  | —                  | —                       | _              | —            | —               | POR           | BOR       | dd                       | uu                                  |  |  |  |

| 8Fh                  | —       | Unimpleme          | nted               |                         |                |              |                 |               |           | —                        | —                                   |  |  |  |

| 90h                  | _       | Unimpleme          | nted               |                         |                |              |                 |               |           | _                        | —                                   |  |  |  |

| 91h                  | _       | Unimpleme          | nted               |                         |                |              |                 |               |           | _                        | —                                   |  |  |  |

| 92h                  | PR2     | Timer2 Peri        | od Register        |                         |                |              |                 |               |           | 1111 1111                | 1111 1111                           |  |  |  |

| 93h                  | SSPADD  | Synchronou         | us Serial Port     | (I <sup>2</sup> C mode) | Address Re     | gister       |                 |               |           | 0000 0000                | 0000 0000                           |  |  |  |

| 94h                  | SSPSTAT | —                  | —                  | D/Ā                     | Р              | S            | R/W             | UA            | BF        | 00 0000                  | 00 0000                             |  |  |  |

| 95h                  | —       | Unimpleme          | nted               |                         |                |              |                 |               |           | —                        | —                                   |  |  |  |

| 96h                  | _       | Unimpleme          | nted               |                         |                |              |                 |               |           | _                        | _                                   |  |  |  |

| 97h                  | —       | Unimpleme          | nted               |                         |                |              |                 |               |           | _                        | _                                   |  |  |  |

| 98h                  | —       | Unimpleme          | nted               |                         |                |              |                 |               |           | —                        | —                                   |  |  |  |

| 99h                  | —       | Unimpleme          | nted               |                         |                |              |                 |               |           | —                        | —                                   |  |  |  |

| 9Ah                  | _       | Unimpleme          | nted               |                         |                |              |                 |               |           | _                        | —                                   |  |  |  |

| 9Bh                  | —       | Unimpleme          | nted               |                         |                |              |                 |               |           | —                        | —                                   |  |  |  |

| 9Ch                  | _       | Unimpleme          | nted               |                         | -              | —            |                 |               |           |                          |                                     |  |  |  |

| 9Dh                  | —       | Unimpleme          | Unimplemented      |                         |                |              |                 |               |           |                          |                                     |  |  |  |

| 9Eh                  | —       | Unimpleme          | nted               |                         | _              | _            |                 |               |           |                          |                                     |  |  |  |

| 9Fh                  | ADCON1  | —                  | -                  | —                       | -              | _            | PCFG2           | PCFG1         | PCFG0     | 000                      | 000                                 |  |  |  |

## TABLE 4-1: PIC16C72 SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

$\label{eq:legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.$

Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

4: The IRP and RP1 bits are reserved on the PIC16C72, always maintain these bits clear.

# FIGURE 4-13: PIR1 REGISTER PIC16C73/73A/74/74A/76/77 (ADDRESS 0Ch)

| 0<br>(1)                                             | R/W-0<br>ADIF                                                                    |                                                                | R-0<br>RCIF                                               |                                  | R-0<br>TXIF       | R/W                        |              |            | R/W-0<br>CCP1IF |     | 1        | 2/W-0<br>//R2IF |      | R/W<br>TMR | -      | D      |      | Read                  | doblo                      | hit           |                  |                                                                                   |

|------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------|----------------------------------|-------------------|----------------------------|--------------|------------|-----------------|-----|----------|-----------------|------|------------|--------|--------|------|-----------------------|----------------------------|---------------|------------------|-----------------------------------------------------------------------------------|

|                                                      | ADI                                                                              |                                                                | Keir                                                      |                                  |                   | 001                        |              |            |                 |     | <u> </u> | /1//211         |      |            | bit0   | W<br>U | / =  | Writa<br>Unim<br>read | able b<br>nplen<br>  as '( | oit<br>nenteo |                  |                                                                                   |

| 1                                                    | = A re                                                                           | ad                                                             | arallel<br>or a wr<br>d or wri                            | ite o                            | peratic           | n has                      |              |            |                 |     |          |                 | eare | ed in      | soft   | war    | e)   |                       |                            |               |                  |                                                                                   |

| 1                                                    | = An A                                                                           | A/D                                                            | Conver<br>conver<br>Conve                                 | rsion                            | compl             | leted (I                   | mus          |            | e clear         | ed  | l in     | softwa          | are  | e)         |        |        |      |                       |                            |               |                  |                                                                                   |

| 1                                                    | = The                                                                            | US                                                             | RT Rec<br>ART re<br>ART re                                | eceiv                            | e buffe           | er is ful                  | l (cle       | ear        | ed by           | rea | adir     | ig RC           | RE   | G)         |        |        |      |                       |                            |               |                  |                                                                                   |

| 1                                                    | = The                                                                            | US                                                             | RT Trar<br>ART tr<br>ART tr                               | ansr                             | nit buff          | er is e                    | mpty         |            | cleare          | d b | by w     | /riting         | to   | TXR        | EG)    |        |      |                       |                            |               |                  |                                                                                   |

| 1                                                    | = The                                                                            | tra                                                            | ichrono<br>nsmiss<br>to tran                              | ion/r                            | eceptio           | on is co                   |              |            |                 |     | be c     | leared          | d ir | n sof      | tware  | e)     |      |                       |                            |               |                  |                                                                                   |

| <u>C</u><br>1<br>0<br><u>C</u><br>1<br>0<br><u>P</u> | <u>Capture</u><br>= A T<br>= No<br><u>Compa</u><br>= A T<br>= No<br><u>PWM N</u> | <u>e Mo</u><br>MR´<br>TMF<br><u>re M</u><br>MR´<br>TMF<br>Iode | 1 regist<br>R1 regi<br><u>1ode</u><br>1 regist<br>R1 regi | ter ca<br>ster<br>ter co<br>ster | apture<br>capture | occurr<br>e occu<br>e matc | rred<br>h oc | ccu        | rred (n         |     |          |                 |      |            | -      | are    | e)   |                       |                            |               |                  |                                                                                   |

| 1                                                    | = TMF                                                                            | R2 t                                                           | MR2 to<br>o PR2<br>R2 to P                                | mate                             | ch occu           | urred (                    | mus          |            | -               | ed  | l in     | softw           | are  | e)         |        |        |      |                       |                            |               |                  |                                                                                   |

| 1                                                    | = TMF                                                                            | R1 r                                                           | /IR1 O<br>egister<br>egister                              | ove                              | rflowed           | l (mus                     |              |            |                 | ו s | soft     | ware)           |      |            |        |        |      |                       |                            |               |                  |                                                                                   |

|                                                      |                                                                                  |                                                                | 73A/76<br>evices,                                         |                                  |                   |                            |              |            |                 | S   | lav      | e Port          | im   | plen       | nente  | ed,    | this | s bit l               | ocat                       | ion is        | rese             | rved                                                                              |

| o<br>errupt<br>pal er                                | on thes                                                                          | e de<br>ts ge<br>it, G                                         | evices,<br>et set wh<br>IE (INT)                          | alwa<br>nen a                    | ays mai           | intain t                   | his l        | bit<br>n o | clear.          | ga  | ardle    | ess of t        | he   | state      | of its | cor    | rre  | es                    | espondi                    | esponding e   | esponding enable | is bit location is rese<br>esponding enable bit or<br>lag bits are clear prior to |

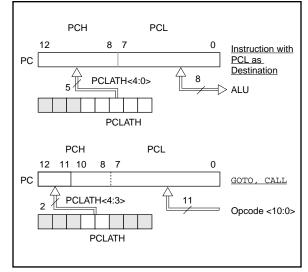

# 4.3 PCL and PCLATH Applicable Devices 72/73/73A/74/74A/76/77

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any reset, the upper bits of the PC will be cleared. Figure 4-17 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 4-17: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note *"Implementing a Table Read"* (AN556).

#### 4.3.2 STACK

The PIC16CXX family has an 8 level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no status bits to indicate stack overflow or stack underflow conditions.

- Note 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address.

#### 4.4 Program Memory Paging Applicable Devices 72|73|73A|74|74A|76|77

PIC16C7X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<4:3> bits are not required for the return instructions (which POPs the address from the stack).

Note: PIC16C7X devices with 4K or less of program memory ignore paging bit PCLATH<4>. The use of PCLATH<4> as a general purpose read/write bit is not recommended since this may affect upward compatibility with future products.

# 8.5 <u>Resetting Timer1 using a CCP Trigger</u> Output

# Applicable Devices

The CCP2 module is not implemented on the PIC16C72 device.

If the CCP1 or CCP2 module is configured in compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |

|-------|------------------------------------------|

|       | and CCP2 modules will not set interrupt  |

|       | flag bit TMR1IF (PIR1<0>).               |

Timer1 must be configured for either timer or synchronized counter mode to take advantage of this feature. If Timer1 is running in asynchronous counter mode, this reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL registers pair effectively becomes the period register for Timer1.

### 8.6 Resetting of Timer1 Register Pair (TMR1H, TMR1L) Applicable Devices 72|73|73A|74|74A|76|77

TMR1H and TMR1L registers are not reset to 00h on a POR or any other reset except by the CCP1 and CCP2 special event triggers.

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other resets, the register is unaffected.

#### 8.7 <u>Timer1 Prescaler</u> Applicable Devices

72 73 73A 74 74A 76 77

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

| Address               | Name   | Bit 7                  | Bit 6     | Bit 5               | Bit 4               | Bit 3         | Bit 2     | Bit 1    | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|-----------------------|--------|------------------------|-----------|---------------------|---------------------|---------------|-----------|----------|--------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                    | PEIE      | TOIE                | INTE                | RBIE          | TOIF      | INTF     | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1   | PSPIF <sup>(1,2)</sup> | ADIF      | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | SSPIF         | CCP1IF    | TMR2IF   | TMR1IF | 0000 0000                | 0000 0000                       |

| 8Ch                   | PIE1   | PSPIE <sup>(1,2)</sup> | ADIE      | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup> | SSPIE         | CCP1IE    | TMR2IE   | TMR1IE | 0000 0000                | 0000 0000                       |

| 0Eh                   | TMR1L  | Holding reg            | jister fo | r the Least S       | Significant B       | yte of the 16 | -bit TMR1 | register |        | XXXX XXXX                | uuuu uuuu                       |

| 0Fh                   | TMR1H  | Holding reg            | ister fo  |                     | xxxx xxxx           | uuuu uuuu     |           |          |        |                          |                                 |

| 10h                   | T1CON  | _                      | _         | T1CKPS1             | T1CKPS0             | T1OSCEN       | T1SYNC    | TMR1CS   | TMR10N | 00 0000                  | uu uuuu                         |

## TABLE 8-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

2: The PIC16C72 does not have a Parallel Slave Port or a USART, these bits are unimplemented, read as '0'.

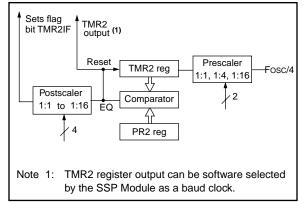

## 9.0 TIMER2 MODULE

#### Applicable Devices 72|73|73A|74|74A|76|77

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time-base for PWM mode of the CCP module(s). The TMR2 register is readable and writable, and is cleared on any device reset.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon reset.

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

Timer2 can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Figure 9-2 shows the Timer2 control register.

#### 9.1 <u>Timer2 Prescaler and Postscaler</u> Applicable Devices

72 73 73A 74 74A 76 77

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device reset (Power-on Reset, MCLR reset, Watchdog Timer reset, or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module which optionally uses it to generate shift clock.

#### FIGURE 9-1: TIMER2 BLOCK DIAGRAM

#### FIGURE 9-2: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

| U-0      | R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0                                                                                                     |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| <u> </u> | TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0 R = Readable bit                                                                 |  |

| bit7     | bit0<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset                                           |  |

| bit 7:   | Unimplemented: Read as '0'                                                                                                              |  |

| bit 6-3: | TOUTPS3:TOUTPS0: Timer2 Output Postscale Select bits<br>0000 = 1:1 Postscale<br>0001 = 1:2 Postscale<br>•<br>•<br>1111 = 1:16 Postscale |  |

| bit 2:   | TMR2ON: Timer2 On bit<br>1 = Timer2 is on<br>0 = Timer2 is off                                                                          |  |

| bit 1-0: | <b>T2CKPS1:T2CKPS0</b> : Timer2 Clock Prescale Select bits<br>00 = Prescaler is 1<br>01 = Prescaler is 4<br>1x = Prescaler is 16        |  |

#### **TABLE 9-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER**

| Address               | Name   | Bit 7                  | Bit 6          | Bit 5               | Bit 4               | Bit 3     | Bit 2  | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|-----------------------|--------|------------------------|----------------|---------------------|---------------------|-----------|--------|---------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                    | PEIE           | TOIE                | INTE                | RBIE      | TOIF   | INTF    | RBIF    | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1   | PSPIF <sup>(1,2)</sup> | ADIF           | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | SSPIF     | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000                | 0000 0000                       |

| 8Ch                   | PIE1   | PSPIE <sup>(1,2)</sup> | ADIE           | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup> | SSPIE     | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000                | 0000 0000                       |

| 11h                   | TMR2   | Timer2 mod             | lule's registe | r                   |                     |           |        |         |         | 0000 0000                | 0000 0000                       |

| 12h                   | T2CON  | _                      | TOUTPS3        | TOUTPS2             | TOUTPS1             | TOUTPS0   | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000                | -000 0000                       |

| 92h                   | PR2    | Timer2 Peri            | od Register    |                     | 1111 1111           | 1111 1111 |        |         |         |                          |                                 |

Legend:

x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

Note

1:

Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

2:

The PIC16C72 does not have a Parallel Slave Port or a USART, these bits are unimplemented, read as '0'.

٦

# FIGURE 11-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)

| R/W-0    | R/W-0                                                                | R/W-0                                                                   | R/W-0                                                                            | R/W-0                                                                        | R/W-0                                    | R/W-0                    | R/W-0                        |                                                                                                                           |

|----------|----------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------|--------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| WCOL     | SSPOV                                                                | SSPEN                                                                   | CKP                                                                              | SSPM3                                                                        | SSPM2                                    | SSPM1                    | SSPM0                        | R = Readable bit                                                                                                          |

| bit7     |                                                                      |                                                                         |                                                                                  |                                                                              |                                          |                          | bit0                         | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset                                      |

| bit 7:   | WCOL: W                                                              | rite Collisio                                                           | n Detect l                                                                       | oit                                                                          |                                          |                          |                              |                                                                                                                           |

|          | 1 = The S                                                            | SPBUF reg                                                               | jister is wr                                                                     |                                                                              | it is still tr                           | ansmitting               | the previou                  | us word                                                                                                                   |

| bit 6:   | SSPOV: R                                                             | eceive Ove                                                              | erflow Det                                                                       | ect bit                                                                      |                                          |                          |                              |                                                                                                                           |

|          | the data ir<br>BUF, even                                             | byte is rece<br>SSPSR re<br>if only train<br>new rece                   | egister is I                                                                     | ost. Overfl<br>data, to av                                                   | ow can on<br>oid setting                 | ly occur in<br>overflow. | slave mod<br>In master       | revious data. In case of overflow<br>e. The user must read the SSP<br>mode the overflow bit is not se<br>SSPBUF register. |

|          | In I <sup>2</sup> C mod                                              | <u>de</u>                                                               |                                                                                  |                                                                              |                                          |                          |                              |                                                                                                                           |

|          | 1 = A byte<br>in transmit<br>0 = No ove                              | mode. SS                                                                |                                                                                  |                                                                              |                                          |                          |                              | us byte. SSPOV is a "don't care                                                                                           |

| bit 5:   | SSPEN: S                                                             | ynchronou                                                               | s Serial P                                                                       | ort Enable                                                                   | bit                                      |                          |                              |                                                                                                                           |

|          | $\frac{\text{In SPI model}}{1 = \text{Enable}}$ $0 = \text{Disable}$ | es serial po                                                            |                                                                                  |                                                                              |                                          |                          | s serial por<br>pins         | t pins                                                                                                                    |

|          | 0 = Disabl                                                           | es the seria                                                            | ort and co                                                                       | nfigures th                                                                  | nese pins a                              | as I/O port              | pins                         | ial port pins<br>s input or output.                                                                                       |

| bit 4:   | CKP: Cloc                                                            | k Polarity                                                              | Select bit                                                                       |                                                                              |                                          |                          |                              |                                                                                                                           |

|          |                                                                      | ate for cloc                                                            |                                                                                  |                                                                              |                                          |                          |                              | receive on rising edge.<br>ceive on falling edge.                                                                         |

|          | $\frac{\ln l^2 C \mod SCK \text{ relea}}{1 = \text{Enable}}$         | se control<br>e clock                                                   | -11                                                                              |                                                                              | 4                                        |                          | . (: )                       |                                                                                                                           |

|          | 0 = Holds                                                            |                                                                         |                                                                                  | , ,                                                                          |                                          |                          | o time)                      |                                                                                                                           |

| bit 3-0: | 0001 = SF<br>0010 = SF<br>0011 = SF<br>0100 = SF<br>0101 = SF        | PI master n<br>PI master n<br>PI master n<br>PI master n<br>PI slave mo | node, cloc<br>node, cloc<br>node, cloc<br>node, cloc<br>ode, clock<br>ode, clock | k = Fosc/4<br>k = Fosc/1<br>k = Fosc/6<br>k = TMR2<br>= SCK pir<br>= SCK pir | l<br>6<br>64<br>output/2<br>1. SS pin co | ontrol enal              |                              | n be used as I/O pin.                                                                                                     |

|          | $0111 = I^{2}(0)$<br>$1011 = I^{2}(0)$<br>$1110 = I^{2}(0)$          | C slave mo<br>C firmware<br>C slave mo                                  | de, 10-bit<br>controlled<br>de, 7-bit a                                          | address<br>I Master M<br>ddress wi                                           | th start an                              | d stop bit i             | nterrupts er<br>interrupts o |                                                                                                                           |

Г

To enable the serial port, SSP enable bit SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear enable bit SSPEN, re-initialize SSPCON register, and then set enable bit SSPEN. This configures the SDI, SDO, SCK, and SS pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- <u>SS</u> must have TRISA<5> set (if implemented)

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value. An example would be in master mode where you are only sending data (to a display driver), then both SDI and SS could be used as general purpose outputs by clearing their corresponding TRIS register bits.

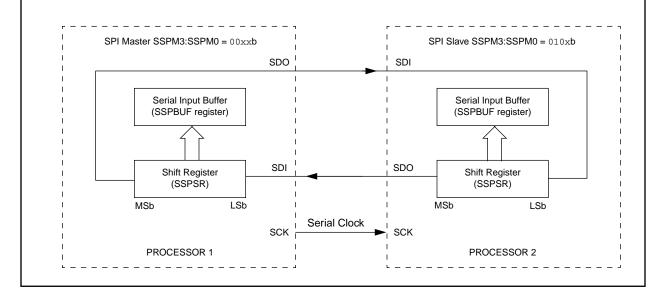

Figure 11-4 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge, and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- · Master sends dummy data Slave sends data

#### FIGURE 11-4: SPI MASTER/SLAVE CONNECTION

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2) is to broadcast data by the software protocol.

In master mode the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SCK output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "line activity monitor" mode.

In slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched interrupt flag bit SSPIF (PIR1<3>) is set.

The clock polarity is selected by appropriately programming bit CKP (SSPCON<4>). This then would give waveforms for SPI communication as shown in Figure 11-5 and Figure 11-6 where the MSB is transmitted first. In master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or TCY)

- Fosc/16 (or 4 TCY)

- Fosc/64 (or 16 TCY)

- Timer2 output/2

This allows a maximum bit clock frequency (at 20 MHz) of 5 MHz. When in slave mode the external clock must meet the minimum high and low times.

In sleep mode, the slave can transmit and receive data and wake the device from sleep.

Г

# FIGURE 11-8: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)(PIC16C76/77)

| R/W-0<br>WCOL | R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         SSPOV       SSPEN       CKP       SSPM3       SSPM2       SSPM1       SSPM0       R = Readable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit7          | bit0<br>bit0<br>bit0<br>bit0<br>bit0<br>bit0<br>bit0<br>bit0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| bit 7:        | <ul> <li>WCOL: Write Collision Detect bit</li> <li>1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)</li> <li>0 = No collision</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| bit 6:        | SSPOV: Receive Overflow Indicator bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|               | In SPI mode<br>1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflet<br>the data in SSPSR is lost. Overflow can only occur in slave mode. The user must read the SSPBUF, ev<br>if only transmitting data, to avoid setting overflow. In master mode the overflow bit is not set since ea<br>new reception (and transmission) is initiated by writing to the SSPBUF register.<br>0 = No overflow                                                                                                                                                                                                                              |

|               | <u>In I<sup>2</sup>C mode</u><br>1 = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't call in transmit mode. SSPOV must be cleared in software in either mode.<br>0 = No overflow                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| bit 5:        | SSPEN: Synchronous Serial Port Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|               | In SPI mode         1 = Enables serial port and configures SCK, SDO, and SDI as serial port pins         0 = Disables serial port and configures these pins as I/O port pins         In I <sup>2</sup> C mode         1 = Enables the serial port and configures the SDA and SCL pins as serial port pins         0 = Disables serial port and configures these pins as I/O port pins         1 = Enables the serial port and configures these pins as I/O port pins         0 = Disables serial port and configures these pins as I/O port pins         In both modes, when enabled, these pins must be properly configured as input or output.                                    |

| bit 4:        | <b>CKP</b> : Clock Polarity Select bit<br>In SPI mode<br>1 = Idle state for clock is a high level<br>0 = Idle state for clock is a low level<br>In $I^2C$ mode<br>SCK release control<br>1 = Enable clock<br>0 = Holds clock low (clock stretch) (Used to ensure data setup time)                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 3-0:      | <b>SSPM3:SSPM0</b> : Synchronous Serial Port Mode Select bits<br>0000 = SPI master mode, clock = Fosc/4<br>0011 = SPI master mode, clock = Fosc/64<br>0011 = SPI master mode, clock = TMR2 output/2<br>$0100 = SPI$ slave mode, clock = SCK pin. $\overline{SS}$ pin control enabled.<br>$0101 = SPI$ slave mode, clock = SCK pin. $\overline{SS}$ pin control disabled. $\overline{SS}$ can be used as I/O pin<br>$0110 = I^2C$ slave mode, 7-bit address<br>$1011 = I^2C$ slave mode, 10-bit address<br>$1011 = I^2C$ slave mode, 7-bit address with start and stop bit interrupts enabled<br>$1111 = I^2C$ slave mode, 10-bit address with start and stop bit interrupts enabled |

#### 12.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>) or enable bit CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set then CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit which is reset by the hardware. In this case it is reset when the RCREG register has been read and is empty. The RCREG is a double buffered register, i.e. it is a two deep FIFO. It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full then overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set. The 9th receive bit is buffered the same way as the receive data. Reading the RCREG register, will load bit RX9D with a new value, therefore it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old RX9D information.

Steps to follow when setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. (Section 12.1)

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

| Address | Name  | Bit 7                | Bit 6     | Bit 5    | Bit 4 | Bit 3     | Bit 2     | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|-------|----------------------|-----------|----------|-------|-----------|-----------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF      | RCIF     | TXIF  | SSPIF     | CCP1IF    | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA | SPEN                 | RX9       | SREN     | CREN  | _         | FERR      | OERR   | RX9D   | 0000 -00x                | 0000 -00x                 |

| 1Ah     | RCREG | USART Re             | eceive Re | egister  |       |           |           |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE      | RCIE     | TXIE  | SSPIE     | CCP1IE    | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA | CSRC                 | TX9       | TXEN     | SYNC  |           | BRGH      | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | SPBRG | Baud Rate            | Generat   | or Regis |       | 0000 0000 | 0000 0000 |        |        |                          |                           |

#### TABLE 12-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

#### TABLE 12-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Address | Name  | Bit 7                | Bit 6     | Bit 5   | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|-------|----------------------|-----------|---------|-----------|-----------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF      | RCIF    | TXIF      | SSPIF     | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA | SPEN                 | RX9       | SREN    | CREN      | _         | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                 |

| 19h     | TXREG | USART Tra            | ansmit Re | egister |           |           |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE      | RCIE    | TXIE      | SSPIE     | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA | CSRC                 | TX9       | TXEN    | SYNC      | _         | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | SPBRG | Baud Rate            | Generat   |         | 0000 0000 | 0000 0000 |        |        |        |                          |                           |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Transmission. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

#### TABLE 12-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address | Name  | Bit 7                | Bit 6     | Bit 5    | Bit 4 | Bit 3     | Bit 2     | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|-------|----------------------|-----------|----------|-------|-----------|-----------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF      | RCIF     | TXIF  | SSPIF     | CCP1IF    | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA | SPEN                 | RX9       | SREN     | CREN  | _         | FERR      | OERR   | RX9D   | 0000 -00x                | 0000 -00x                 |

| 1Ah     | RCREG | USART Re             | eceive Re | egister  |       |           |           |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE      | RCIE     | TXIE  | SSPIE     | CCP1IE    | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA | CSRC                 | TX9       | TXEN     | SYNC  | _         | BRGH      | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | SPBRG | Baud Rate            | Generat   | or Regis |       | 0000 0000 | 0000 0000 |        |        |                          |                           |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

| Register |    | Α  | pplica | ble | Device | es |    | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT<br>or<br>Interrupt |

|----------|----|----|--------|-----|--------|----|----|------------------------------------|--------------------------|------------------------------------|

| SSPADD   | 72 | 73 | 73A    | 74  | 74A    | 76 | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                          |

| SSPSTAT  | 72 | 73 | 73A    | 74  | 74A    | 76 | 77 | 00 0000                            | 00 0000                  | uu uuuu                            |

| TXSTA    | 72 | 73 | 73A    | 74  | 74A    | 76 | 77 | 0000 -010                          | 0000 -010                | uuuu -uuu                          |

| SPBRG    | 72 | 73 | 73A    | 74  | 74A    | 76 | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                          |

| ADCON1   | 72 | 73 | 73A    | 74  | 74A    | 76 | 77 | 000                                | 000                      | uuu                                |

#### TABLE 14-8: INITIALIZATION CONDITIONS FOR ALL REGISTERS (Cont.'d)

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 14-7 for reset value for specific condition.

Applicable Devices 72 73 73A 74 74A 76 77

# 19.0 ELECTRICAL CHARACTERISTICS FOR PIC16C73A/74A

#### Absolute Maximum Ratings †

| -                                                                                                           |                                    |

|-------------------------------------------------------------------------------------------------------------|------------------------------------|

| Ambient temperature under bias                                                                              | 55 to +125°C                       |

| Storage temperature                                                                                         | 65°C to +150°C                     |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                          | 0.3V to (VDD + 0.3V)               |

| Voltage on VDD with respect to Vss                                                                          | 0.3 to +7.5V                       |

| Voltage on MCLR with respect to Vss (Note 2)                                                                | 0 to +14V                          |

| Voltage on RA4 with respect to Vss                                                                          | 0 to +14V                          |

| Total power dissipation (Note 1)                                                                            | 1.0W                               |

| Maximum current out of Vss pin                                                                              | 300 mA                             |

| Maximum current into VDD pin                                                                                | 250 mA                             |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                | ±20 mA                             |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                              |                                    |

| Maximum output current sunk by any I/O pin                                                                  | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                               | 25 mA                              |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                         | 200 mA                             |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                      | 200 mA                             |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                                 | 200 mA                             |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                              | 200 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - | VOH) x IOH} + $\Sigma$ (VOI x IOL) |

|                                                                                                             |                                    |

**Note 2:** Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

Note 3: PORTD and PORTE are not implemented on the PIC16C73A.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### TABLE 19-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C73A-04<br>PIC16C74A-04                                                                                                                        | PIC16C73A-10<br>PIC16C74A-10                                                                                                                       | PIC16C73A-20<br>PIC16C74A-20                                                                                                                       | PIC16LC73A-04<br>PIC16LC74A-04                                                                            | JW Devices                                                                                                                                         |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                                                            | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 2.5V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 5 μA max. at 3V<br>Freq: 4 MHz max.                 | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                                                           |

| хт  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                                                            | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 2.5V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 5 μA max. at 3V<br>Freq: 4 MHz max.                 | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                                                           |

| HS  | VDD:         4.5V to 5.5V           IDD:         13.5 mA typ. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         4 MHz max. | VDD:         4.5V to 5.5V           IDD:         10 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         10 MHz max. | VDD:         4.5V to 5.5V           IDD:         20 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         20 MHz max. | Not recommended for use in HS mode                                                                        | VDD:         4.5V to 5.5V           IDD:         20 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         20 MHz max. |

| LP  | VDD: 4.0V to 6.0V<br>IDD: 52.5 μA typ. at<br>32 kHz, 4.0V<br>IPD: 0.9 μA typ. at 4.0V<br>Freq: 200 kHz max.                                         | Not recommended for use in LP mode                                                                                                                 | Not recommended for use in LP mode                                                                                                                 | VDD: 2.5V to 6.0V<br>IDD: 48 μA max. at<br>32 kHz, 3.0V<br>IPD: 5.0 μA max. at 3.0V<br>Freq: 200 kHz max. | VDD: 2.5V to 6.0V<br>IDD: 48 μA max. at<br>32 kHz, 3.0V<br>IPD: 5.0 μA max. at 3.0V<br>Freq: 200 kHz max.                                          |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

# Applicable Devices 72 73 73A 74 74A 76 77

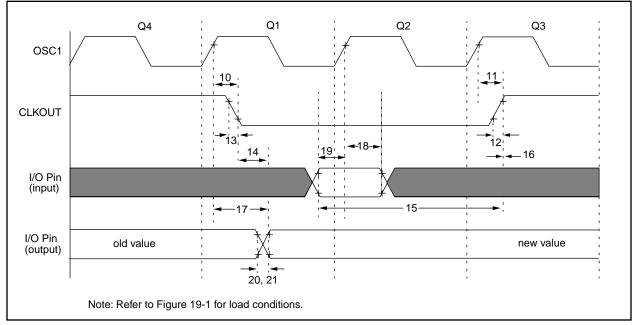

### FIGURE 19-3: CLKOUT AND I/O TIMING

### TABLE 19-3: CLKOUT AND I/O TIMING REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                                    |                         | Min        | Тур† | Max         | Units | Conditions |

|--------------|----------|---------------------------------------------------|-------------------------|------------|------|-------------|-------|------------|

| 10*          | TosH2ckL | OSC1 <sup>↑</sup> to CLKOUT↓                      |                         | _          | 75   | 200         | ns    | Note 1     |

| 11*          | TosH2ckH | OSC1 <sup>↑</sup> to CLKOUT <sup>↑</sup>          |                         | _          | 75   | 200         | ns    | Note 1     |

| 12*          | TckR     | CLKOUT rise time                                  |                         | —          | 35   | 100         | ns    | Note 1     |

| 13*          | TckF     | CLKOUT fall time                                  |                         | —          | 35   | 100         | ns    | Note 1     |

| 14*          | TckL2ioV | CLKOUT $\downarrow$ to Port out valid             | Ł                       | _          | —    | 0.5Tcy + 20 | ns    | Note 1     |

| 15*          | TioV2ckH | Port in valid before CLKOU                        | JT ↑                    | Tosc + 200 | —    | _           | ns    | Note 1     |

| 16*          | TckH2iol | Port in hold after CLKOUT                         | $\uparrow$              | 0          | -    | —           | ns    | Note 1     |

| 17*          | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to<br>Port out valid |                         | -          | 50   | 150         | ns    |            |

| 18*          | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to                   | PIC16 <b>C</b> 73A/74A  | 100        | -    | —           | ns    |            |

|              |          | Port input invalid (I/O in hold time)             | PIC16 <b>LC</b> 73A/74A | 200        | —    | —           | ns    |            |

| 19*          | TioV2osH | Port input valid to OSC1 <sup>↑</sup>             | (I/O in setup time)     | 0          | —    | —           | ns    |            |

| 20*          | TioR     | Port output rise time                             | PIC16 <b>C</b> 73A/74A  | _          | 10   | 40          | ns    |            |

|              |          |                                                   | PIC16 <b>LC</b> 73A/74A | —          | —    | 80          | ns    |            |

| 21*          | TioF     | Port output fall time                             | PIC16 <b>C</b> 73A/74A  | —          | 10   | 40          | ns    |            |

|              |          |                                                   | PIC16 <b>LC</b> 73A/74A | _          | —    | 80          | ns    |            |

| 22††*        | Tinp     | INT pin high or low time                          |                         | Тсү        | —    | —           | ns    |            |

| 23††*        | Trbp     | RB7:RB4 change INT high                           | or low time             | Тсү        | _    | —           | ns    |            |

$^{\ast}$  These parameters are characterized but not tested.

†Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

these parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

# Applicable Devices 72 73 73A 74 74A 76 77

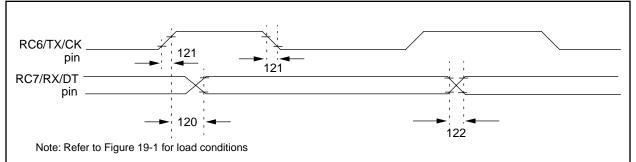

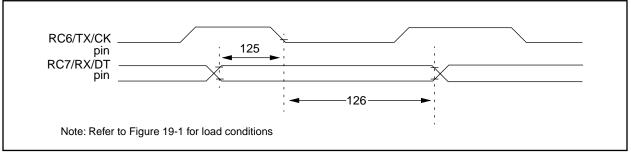

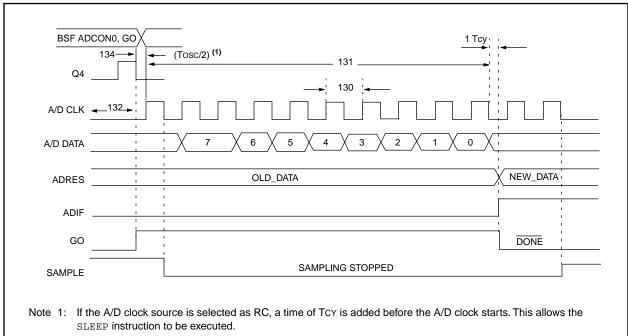

#### FIGURE 19-12: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 19-11: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                    |                         | Min | Тур† | Мах | Units | Conditions |

|--------------|----------|-----------------------------------|-------------------------|-----|------|-----|-------|------------|

| 120          | TckH2dtV | SYNC XMIT (MASTER &<br>SLAVE)     | PIC16 <b>C</b> 73A/74A  | _   | _    | 80  | ns    |            |

|              |          | Clock high to data out valid      | PIC16 <b>LC</b> 73A/74A | _   | —    | 100 | ns    |            |

| 121          | Tckrf    | Clock out rise time and fall time | PIC16 <b>C</b> 73A/74A  | -   | —    | 45  | ns    |            |

|              |          | (Master Mode)                     | PIC16 <b>LC</b> 73A/74A | -   | —    | 50  | ns    |            |

| 122          | Tdtrf    | Data out rise time and fall time  | PIC16 <b>C</b> 73A/74A  | - 1 | -    | 45  | ns    |            |

|              |          |                                   | PIC16 <b>LC</b> 73A/74A | -   | —    | 50  | ns    |            |

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### FIGURE 19-13: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 19-12: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                                                            | Min | Тур† | Мах | Units | Conditions |

|------------------|----------|-----------------------------------------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | $\frac{\text{SYNC RCV (MASTER \& SLAVE)}}{\text{Data setup before CK} \downarrow (\text{DT setup time})}$ | 15  | _    | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                                            | 15  | —    | —   | ns    |            |

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Applicable Devices 72 73 73A 74 74A 76 77

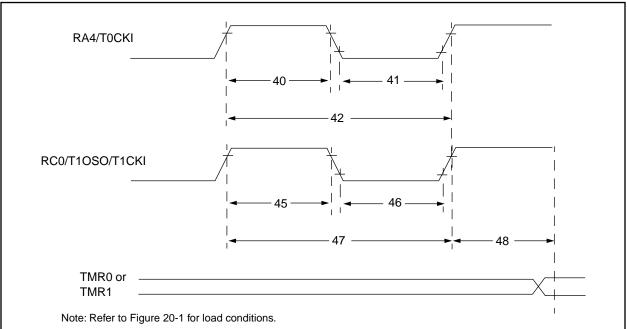

#### TABLE 20-5: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS