Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 10MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | ОТР                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                             |

| Data Converters            | A/D 8x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c74a-10-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|            |                                                 | PIC16C710                           | PIC16C71            | PIC16C711                           | PIC16C715                           | PIC16C72                   | PIC16CR72 <sup>(1)</sup>   |  |  |  |  |  |

|------------|-------------------------------------------------|-------------------------------------|---------------------|-------------------------------------|-------------------------------------|----------------------------|----------------------------|--|--|--|--|--|

| Clock      | Maximum Frequency<br>of Operation (MHz)         | 20                                  | 20                  | 20                                  | 20                                  | 20                         | 20                         |  |  |  |  |  |

|            | EPROM Program Memory<br>(x14 words)             | 512                                 | 1K                  | 1K                                  | 2К                                  | 2К                         | —                          |  |  |  |  |  |

| lemory     | ROM Program Memory<br>(14K words)               | _                                   | _                   | _                                   | _                                   | _                          | 2К                         |  |  |  |  |  |

|            | Data Memory (bytes)                             | 36                                  | 36                  | 68                                  | 128                                 | 128                        | 128                        |  |  |  |  |  |

|            | Timer Module(s)                                 | TMR0                                | TMR0                | TMR0                                | TMR0                                | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2     |  |  |  |  |  |

| eripherals | Capture/Compare/<br>PWM Module(s)               | —                                   | _                   | —                                   | —                                   | 1                          | 1                          |  |  |  |  |  |

|            | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | _                                   | _                   | —                                   | —                                   | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C       |  |  |  |  |  |

|            | Parallel Slave Port                             | _                                   | —                   | —                                   | _                                   | _                          | —                          |  |  |  |  |  |

|            | A/D Converter (8-bit) Channels                  | 4                                   | 4                   | 4                                   | 4                                   | 5                          | 5                          |  |  |  |  |  |

|            | Interrupt Sources                               | 4                                   | 4                   | 4                                   | 4                                   | 8                          | 8                          |  |  |  |  |  |

|            | I/O Pins                                        | 13                                  | 13                  | 13                                  | 13                                  | 22                         | 22                         |  |  |  |  |  |

|            | Voltage Range (Volts)                           | 3.0-6.0                             | 3.0-6.0             | 3.0-6.0                             | 3.0-5.5                             | 2.5-6.0                    | 3.0-5.5                    |  |  |  |  |  |

| atures     | In-Circuit Serial Programming                   | Yes                                 | Yes                 | Yes                                 | Yes                                 | Yes                        | Yes                        |  |  |  |  |  |

|            | Brown-out Reset                                 | Yes                                 | —                   | Yes                                 | Yes                                 | Yes                        | Yes                        |  |  |  |  |  |

|            | Packages                                        | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC, SSOP |  |  |  |  |  |

## TABLE 1-1: PIC16C7XX FAMILY OF DEVCES

|             |                                                   | PIC16C73A                   | PIC16C74A                                 | PIC16C76                    | PIC16C77                                  |

|-------------|---------------------------------------------------|-----------------------------|-------------------------------------------|-----------------------------|-------------------------------------------|

| Clock       | Maximum Frequency of Oper-<br>ation (MHz)         | 20                          | 20                                        | 20                          | 20                                        |

| Memory      | EPROM Program Memory<br>(x14 words)               | 4K                          | 4K                                        | 8K                          | 8K                                        |

|             | Data Memory (bytes)                               | 192                         | 192                                       | 368                         | 368                                       |

|             | Timer Module(s)                                   | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    |

| Peripherals | Capture/Compare/PWM Mod-<br>ule(s)                | 2                           | 2                                         | 2                           | 2                                         |

|             | Serial Port(s) (SPI/I <sup>2</sup> C, US-<br>ART) | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               |

|             | Parallel Slave Port                               | —                           | Yes                                       | —                           | Yes                                       |

|             | A/D Converter (8-bit) Channels                    | 5                           | 8                                         | 5                           | 8                                         |

|             | Interrupt Sources                                 | 11                          | 12                                        | 11                          | 12                                        |

|             | I/O Pins                                          | 22                          | 33                                        | 22                          | 33                                        |

|             | Voltage Range (Volts)                             | 2.5-6.0                     | 2.5-6.0                                   | 2.5-6.0                     | 2.5-6.0                                   |

| eatures     | In-Circuit Serial Programming                     | Yes                         | Yes                                       | Yes                         | Yes                                       |

|             | Brown-out Reset                                   | Yes                         | Yes                                       | Yes                         | Yes                                       |

|             | Packages                                          | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C7XX Family devices use serial programming with clock pin RB6 and data pin RB7.

Note 1: Please contact your local Microchip sales office for availability of these devices.

NOTES:

### 4.2.2.1 STATUS REGISTER Applicable Devices 72|73|73A|74|74A|76|77

The STATUS register, shown in Figure 4-7, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- **Note 1:** For those devices that do not use bits IRP and RP1 (STATUS<7:6>), maintain these bits clear to ensure upward compatibility with future products.

- Note 2: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| R/W-0    | R/W-0                                            | R/W-0                                                                                     | R-1                                  | R-1                                       | R/W-x                                          | R/W-x                                      | R/W-x                       |                                                                                       |

|----------|--------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------|------------------------------------------------|--------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------|

| IRP      | RP1                                              | RP0                                                                                       | TO                                   | PD                                        | Z                                              | DC                                         | С                           | R = Readable bit                                                                      |

| bit7     |                                                  |                                                                                           |                                      |                                           |                                                |                                            | bit0                        | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 7:   | 1 = Bank 2                                       | ster Bank \$<br>2, 3 (100h<br>0, 1 (00h -                                                 | - 1FFh)                              | used for ir                               | ndirect addr                                   | essing)                                    |                             |                                                                                       |

| bit 6-5: | 11 = Bank<br>10 = Bank<br>01 = Bank<br>00 = Bank | : Register E<br>< 3 (180h -<br>< 2 (100h -<br>< 1 (80h - F<br>< 0 (00h - 7<br>k is 128 by | 1FFh)<br>17Fh)<br>Fh)<br>′Fh)        | ct bits (use                              | ed for direct                                  | addressin                                  | g)                          |                                                                                       |

| oit 4:   | •                                                |                                                                                           |                                      | struction,                                | or sleep ir                                    | struction                                  |                             |                                                                                       |

| bit 3:   | •                                                | r-down bit<br>oower-up o<br>ecution of t                                                  | •                                    |                                           |                                                |                                            |                             |                                                                                       |

| bit 2:   |                                                  | sult of an a                                                                              |                                      |                                           | peration is z                                  |                                            |                             |                                                                                       |

| bit 1:   | 1 = A carr                                       | y-out from                                                                                | the 4th lo                           | w order bi                                | N, SUBLW, S<br>t of the resu<br>bit of the res | It occurred                                |                             | r borrow the polarity is reversed                                                     |

| bit 0:   | 1 = A carr<br>0 = No car<br>Note: For            | y-out from<br>rry-out fror<br>borrow the<br>berand. For                                   | the most<br>n the mos<br>polarity is | significant<br>t significar<br>s reversed |                                                | esult occuri<br>result occu<br>ion is exec | red<br>irred<br>uted by add | ding the two's complement of the either the high or low order bit o                   |

### FIGURE 4-7: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

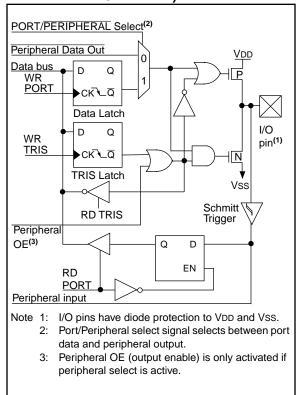

### 5.3 <u>PORTC and TRISC Registers</u> Applicable Devices

72 73 73A 74 74A 76 77

PORTC is an 8-bit bi-directional port. Each pin is individually configurable as an input or output through the TRISC register. PORTC is multiplexed with several peripheral functions (Table 5-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

### EXAMPLE 5-3: INITIALIZING PORTC

| BCF   | STATUS, | RP0 | ; | Select Bank 0         |

|-------|---------|-----|---|-----------------------|

| BCF   | STATUS, | RP1 | ; | PIC16C76/77 only      |

| CLRF  | PORTC   |     | ; | Initialize PORTC by   |

|       |         |     | ; | clearing output       |

|       |         |     | ; | data latches          |

| BSF   | STATUS, | RP0 | ; | Select Bank 1         |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISC   |     | ; | Set RC<3:0> as inputs |

|       |         |     | ; | RC<5:4> as outputs    |

|       |         |     | ; | RC<7:6> as inputs     |

|       |         |     |   |                       |

### FIGURE 5-6: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

### TABLE 5-5:PORTC FUNCTIONS

| Name                          | Bit# | Buffer Type | Function                                                                                           |

|-------------------------------|------|-------------|----------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI               | bit0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input                               |

| RC1/T1OSI/CCP2 <sup>(1)</sup> | bit1 | ST          | Input/output port pin or Timer1 oscillator input or Capture2 input/<br>Compare2 output/PWM2 output |

| RC2/CCP1                      | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output                                |

| RC3/SCK/SCL                   | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and $^2C$ modes.                         |

| RC4/SDI/SDA                   | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or data I/O (PC mode).                                  |

| RC5/SDO                       | bit5 | ST          | Input/output port pin or Synchronous Serial Port data output                                       |

| RC6/TX/CK <sup>(2)</sup>      | bit6 | ST          | Input/output port pin or USART Asynchronous Transmit, or USART Synchronous Clock                   |

| RC7/RX/DT <sup>(2)</sup>      | bit7 | ST          | Input/output port pin or USART Asynchronous Receive, or USART Synchronous Data                     |

Legend: ST = Schmitt Trigger input

Note 1: The CCP2 multiplexed function is not enabled on the PIC16C72.

2: The TX/CK and RX/DT multiplexed functions are not enabled on the PIC16C72.

### 11.3 SPI Mode for PIC16C76/77

Γ

This section contains register definitions and operational characteristics of the SPI module on the PIC16C76 and PIC16C77 only.

### FIGURE 11-7: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h)(PIC16C76/77)

| R/W-0  | R/W-0                                                            | R-0                                                                      | R-0                                          | R-0                                                                     | R-0                                            | R-0          | R-0          |                                                                                      |

|--------|------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------|--------------|--------------|--------------------------------------------------------------------------------------|

| SMP    | CKE                                                              | D/Ā                                                                      | Р                                            | S                                                                       | R/W                                            | UA           | BF           | R = Readable bit                                                                     |

| bit7   |                                                                  |                                                                          |                                              |                                                                         |                                                |              | bit0         | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset |

| bit 7: | <u>SPI Ma</u><br>1 = Inpu<br>0 = Inpu<br><u>SPI Sla</u>          | <u>ster Mod</u> ut data sa<br>ut data sa<br>ut data sa<br><u>ve Mode</u> | ampled at o<br>ampled at i                   | end of data<br>middle of d                                              | output time<br>ata output tir<br>ed in slave n |              |              |                                                                                      |

| bit 6: | $\frac{CKP = 0}{1 = Data}$ $0 = Data$ $\frac{CKP = 1}{1 = Data}$ | <u>0</u><br>a transmi<br>a transmi<br><u>1</u><br>a transmi              | itted on ris<br>itted on fal<br>itted on fal | ect (Figure<br>ing edge of<br>ling edge o<br>ling edge o<br>ing edge of | f SCK<br>f SCK                                 | e 11-12, and | d Figure 11- | 13)                                                                                  |

| bit 5: | 1 = Indi                                                         | cates tha                                                                | t the last b                                 |                                                                         | )<br>ed or transmi<br>ed or transmi            |              |              |                                                                                      |

| bit 4: | detecte<br>1 = Indi                                              | d last, SS<br>cates tha                                                  | SPEN is cl                                   | eared)<br>t has been                                                    | cleared whe                                    |              |              | lisabled, or when the Start bit is                                                   |

| bit 3: | detecte<br>1 = Indi                                              | d last, SS<br>cates tha                                                  | SPEN is cl                                   | eared)<br>t has been                                                    | cleared whe                                    |              |              | lisabled, or when the Stop bit is                                                    |

| bit 2: | This bit                                                         | holds th<br>match to<br>d                                                | ne R/W bit                                   |                                                                         |                                                |              | dress match  | . This bit is only valid from the                                                    |

| bit 1: | 1 = Indi                                                         | cates tha                                                                | t the user                                   | it I <sup>2</sup> C mode<br>needs to u<br>I to be upda                  | pdate the ad                                   | dress in the | e SSPADD re  | egister                                                                              |

| bit 0: | BF: Buf                                                          | fer Full S                                                               | tatus bit                                    |                                                                         |                                                |              |              |                                                                                      |

|        | 1 = Rec<br>0 = Rec                                               | eive com<br>eive not                                                     | complete,                                    | es)<br>PBUF is ful<br>SSPBUF is                                         |                                                |              |              |                                                                                      |

|        | 1 = Trar                                                         |                                                                          | rogress, S                                   | SPBUF is t<br>PBUF is en                                                |                                                |              |              |                                                                                      |

### TABLE 12-3: BAUD RATES FOR SYNCHRONOUS MODE

| BAUD        | Fosc = 2 | 20 MHz     | SPBRG              | 16 MHz |            | SPBRG              | 10 MHz |            | SPBRG              | 7.15909 I | MHz        | SPBRG              |

|-------------|----------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|-----------|------------|--------------------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD     | %<br>ERROR | value<br>(decimal) |

| 0.3         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 1.2         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 2.4         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 9.6         | NA       | -          | -                  | NA     | -          | -                  | 9.766  | +1.73      | 255                | 9.622     | +0.23      | 185                |

| 19.2        | 19.53    | +1.73      | 255                | 19.23  | +0.16      | 207                | 19.23  | +0.16      | 129                | 19.24     | +0.23      | 92                 |

| 76.8        | 76.92    | +0.16      | 64                 | 76.92  | +0.16      | 51                 | 75.76  | -1.36      | 32                 | 77.82     | +1.32      | 22                 |

| 96          | 96.15    | +0.16      | 51                 | 95.24  | -0.79      | 41                 | 96.15  | +0.16      | 25                 | 94.20     | -1.88      | 18                 |

| 300         | 294.1    | -1.96      | 16                 | 307.69 | +2.56      | 12                 | 312.5  | +4.17      | 7                  | 298.3     | -0.57      | 5                  |

| 500         | 500      | 0          | 9                  | 500    | 0          | 7                  | 500    | 0          | 4                  | NA        | -          | -                  |

| HIGH        | 5000     | -          | 0                  | 4000   | -          | 0                  | 2500   | -          | 0                  | 1789.8    | -          | 0                  |

| LOW         | 19.53    | -          | 255                | 15.625 | -          | 255                | 9.766  | -          | 255                | 6.991     | -          | 255                |

|                     | Fosc = | 5.0688 M   | Hz                          | 4 MHz  |            |                             | 3.579545 | 5 MHz      |                             | 1 MHz  |            |                             | 32.768 k | Hz         |                             |

|---------------------|--------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | NA     | -          | -                           | 0.303    | +1.14      | 26                          |

| 1.2                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | 1.202  | +0.16      | 207                         | 1.170    | -2.48      | 6                           |

| 2.4                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | 2.404  | +0.16      | 103                         | NA       | -          | -                           |

| 9.6                 | 9.6    | 0          | 131                         | 9.615  | +0.16      | 103                         | 9.622    | +0.23      | 92                          | 9.615  | +0.16      | 25                          | NA       | -          | -                           |

| 19.2                | 19.2   | 0          | 65                          | 19.231 | +0.16      | 51                          | 19.04    | -0.83      | 46                          | 19.24  | +0.16      | 12                          | NA       | -          | -                           |

| 76.8                | 79.2   | +3.13      | 15                          | 76.923 | +0.16      | 12                          | 74.57    | -2.90      | 11                          | 83.34  | +8.51      | 2                           | NA       | -          | -                           |

| 96                  | 97.48  | +1.54      | 12                          | 1000   | +4.17      | 9                           | 99.43    | +3.57      | 8                           | NA     | -          | -                           | NA       | -          | -                           |

| 300                 | 316.8  | +5.60      | 3                           | NA     | -          | -                           | 298.3    | -0.57      | 2                           | NA     | -          | -                           | NA       | -          | -                           |

| 500                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| HIGH                | 1267   | -          | 0                           | 100    | -          | 0                           | 894.9    | -          | 0                           | 250    | -          | 0                           | 8.192    | -          | 0                           |

| LOW                 | 4.950  | -          | 255                         | 3.906  | -          | 255                         | 3.496    | -          | 255                         | 0.9766 | -          | 255                         | 0.032    | -          | 255                         |

## TABLE 12-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD | Fosc = 2 | 20 MHz     | SPBRG     | 16 MHz |       | SPBRG     | 10 MHz |       | SPBRG     | 7.15909 | MHz        | SPBRG     |

|------|----------|------------|-----------|--------|-------|-----------|--------|-------|-----------|---------|------------|-----------|

| RATE |          | %<br>ERROR | value     |        | %     | value     |        | %     | value     |         | %<br>ERROR | value     |

| (K)  | KBAUD    | ERROR      | (decimal) | RBAUD  | ERROR | (decimal) | REAUD  | ERROR | (decimal) | REAUD   | EKKUK      | (decimal) |

| 0.3  | NA       | -          | -         | NA     | -     | -         | NA     | -     | -         | NA      | -          | -         |

| 1.2  | 1.221    | +1.73      | 255       | 1.202  | +0.16 | 207       | 1.202  | +0.16 | 129       | 1.203   | +0.23      | 92        |

| 2.4  | 2.404    | +0.16      | 129       | 2.404  | +0.16 | 103       | 2.404  | +0.16 | 64        | 2.380   | -0.83      | 46        |

| 9.6  | 9.469    | -1.36      | 32        | 9.615  | +0.16 | 25        | 9.766  | +1.73 | 15        | 9.322   | -2.90      | 11        |

| 19.2 | 19.53    | +1.73      | 15        | 19.23  | +0.16 | 12        | 19.53  | +1.73 | 7         | 18.64   | -2.90      | 5         |

| 76.8 | 78.13    | +1.73      | 3         | 83.33  | +8.51 | 2         | 78.13  | +1.73 | 1         | NA      | -          | -         |

| 96   | 104.2    | +8.51      | 2         | NA     | -     | -         | NA     | -     | -         | NA      | -          | -         |

| 300  | 312.5    | +4.17      | 0         | NA     | -     | -         | NA     | -     | -         | NA      | -          | -         |

| 500  | NA       | -          | -         | NA     | -     | -         | NA     | -     | -         | NA      | -          | -         |

| HIGH | 312.5    | -          | 0         | 250    | -     | 0         | 156.3  | -     | 0         | 111.9   | -          | 0         |

| LOW  | 1.221    | -          | 255       | 0.977  | -     | 255       | 0.6104 | -     | 255       | 0.437   | -          | 255       |

|                     | Fosc = | 5.0688 MI  | Hz                          | 4 MHz  |            |                             | 3.57954 | 5 MHz      |                             | 1 MHz  |            |                             | 32.768 k | Hz         |                             |

|---------------------|--------|------------|-----------------------------|--------|------------|-----------------------------|---------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3                 | 0.31   | +3.13      | 255                         | 0.3005 | -0.17      | 207                         | 0.301   | +0.23      | 185                         | 0.300  | +0.16      | 51                          | 0.256    | -14.67     | 1                           |

| 1.2                 | 1.2    | 0          | 65                          | 1.202  | +1.67      | 51                          | 1.190   | -0.83      | 46                          | 1.202  | +0.16      | 12                          | NA       | -          | -                           |

| 2.4                 | 2.4    | 0          | 32                          | 2.404  | +1.67      | 25                          | 2.432   | +1.32      | 22                          | 2.232  | -6.99      | 6                           | NA       | -          | -                           |

| 9.6                 | 9.9    | +3.13      | 7                           | NA     | -          | -                           | 9.322   | -2.90      | 5                           | NA     | -          | -                           | NA       | -          | -                           |

| 19.2                | 19.8   | +3.13      | 3                           | NA     | -          | -                           | 18.64   | -2.90      | 2                           | NA     | -          | -                           | NA       | -          | -                           |

| 76.8                | 79.2   | +3.13      | 0                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 96                  | NA     | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 300                 | NA     | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 500                 | NA     | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| HIGH                | 79.2   | -          | 0                           | 62.500 | -          | 0                           | 55.93   | -          | 0                           | 15.63  | -          | 0                           | 0.512    | -          | 0                           |

| LOW                 | 0.3094 | -          | 255                         | 3.906  | -          | 255                         | 0.2185  | -          | 255                         | 0.0610 | -          | 255                         | 0.0020   | -          | 255                         |

### Applicable Devices 72 73 73A 74 74A 76 77

### 17.5 <u>Timing Diagrams and Specifications</u>

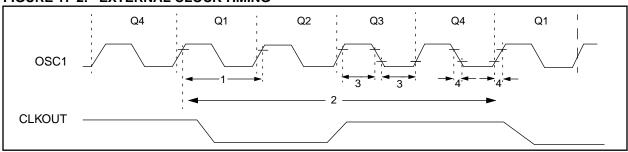

## FIGURE 17-2: EXTERNAL CLOCK TIMING

### TABLE 17-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                   | Min | Тур† | Max    | Units | Conditions         |

|------------------|-------|----------------------------------|-----|------|--------|-------|--------------------|

|                  | Fosc  | External CLKIN Frequency         | DC  | _    | 4      | MHz   | XT and RC osc mode |

|                  |       | (Note 1)                         | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|                  |       |                                  | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|                  |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|                  |       |                                  | DC  | _    | 200    | kHz   | LP osc mode        |

|                  |       | Oscillator Frequency             | DC  | _    | 4      | MHz   | RC osc mode        |

|                  |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode        |

|                  |       |                                  | 4   | _    | 20     | MHz   | HS osc mode        |

|                  |       |                                  | 5   | —    | 200    | kHz   | LP osc mode        |

| 1                | Tosc  | External CLKIN Period            | 250 | —    | —      | ns    | XT and RC osc mode |

|                  |       | (Note 1)                         | 250 | —    | —      | ns    | HS osc mode (-04)  |

|                  |       |                                  | 100 | _    | _      | ns    | HS osc mode (-10)  |

|                  |       |                                  | 50  | _    | _      | ns    | HS osc mode (-20)  |

|                  |       |                                  | 5   | _    | _      | μs    | LP osc mode        |

|                  |       | Oscillator Period                | 250 | _    | _      | ns    | RC osc mode        |

|                  |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode        |

|                  |       |                                  | 250 | _    | 250    | ns    | HS osc mode (-04)  |

|                  |       |                                  | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|                  |       |                                  | 50  | —    | 250    | ns    | HS osc mode (-20)  |

|                  |       |                                  | 5   | —    | _      | μs    | LP osc mode        |

| 2                | Тсү   | Instruction Cycle Time (Note 1)  | 200 | —    | DC     | ns    | TCY = 4/FOSC       |

| 3                | TosL, | External Clock in (OSC1) High or | 100 | _    | —      | ns    | XT oscillator      |

|                  | TosH  | Low Time                         | 2.5 | _    | _      | μs    | LP oscillator      |

|                  |       |                                  | 15  | _    | _      | ns    | HS oscillator      |

| 4                | TosR, | External Clock in (OSC1) Rise or | _   | _    | 25     | ns    | XT oscillator      |

|                  | TosF  | Fall Time                        | _   | _    | 50     | ns    | LP oscillator      |

|                  |       |                                  |     | _    | 15     | ns    | HS oscillator      |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

### Applicable Devices 72 73 73A 74 74A 76 77

### 19.2 DC Characteristics: PIC16LC73A/74A-04 (Commercial, Industrial)

| DC CHA                | RACTERISTICS                                                     |               |             | ard Ope<br>ing tem |              |                | itions (unless otherwise stated) $0^{\circ}C$ $\leq TA \leq +85^{\circ}C$ for industrial and $C$ $\leq TA \leq +70^{\circ}C$ for commercial                             |

|-----------------------|------------------------------------------------------------------|---------------|-------------|--------------------|--------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.          | Characteristic                                                   | Sym           | Min         | Тур†               | Max          | Units          | Conditions                                                                                                                                                              |

| D001                  | Supply Voltage                                                   | Vdd           | 2.5         | -                  | 6.0          | V              | LP, XT, RC osc configuration (DC - 4 MHz)                                                                                                                               |

| D002*                 | RAM Data Retention<br>Voltage (Note 1)                           | Vdr           | -           | 1.5                | -            | V              |                                                                                                                                                                         |

| D003                  | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR          | -           | Vss                | -            | V              | See section on Power-on Reset for details                                                                                                                               |

| D004*                 | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | Svdd          | 0.05        | -                  | -            | V/ms           | See section on Power-on Reset for details                                                                                                                               |

| D005                  | Brown-out Reset Voltage                                          | Bvdd          | 3.7         | 4.0                | 4.3          | V              | BODEN bit in configuration word enabled                                                                                                                                 |

| D010                  | Supply Current (Note 2,5)                                        | IDD           | -           | 2.0                | 3.8          | mA             | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                                                           |

| D010A                 |                                                                  |               | -           | 22.5               | 48           | μΑ             | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                                                                                         |

| D015*                 | Brown-out Reset Current (Note 6)                                 | $\Delta$ IBOR | -           | 350                | 425          | μΑ             | BOR enabled VDD = 5.0V                                                                                                                                                  |

| D020<br>D021<br>D021A | Power-down Current<br>(Note 3,5)                                 | IPD           | -<br>-<br>- | 7.5<br>0.9<br>0.9  | 30<br>5<br>5 | μΑ<br>μΑ<br>μΑ | $VDD = 3.0V, WDT enabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 3.0V, WDT disabled, 0^{\circ}C to +70^{\circ}C$ $VDD = 3.0V, WDT disabled, -40^{\circ}C to +85^{\circ}C$ |

| D023*                 | Brown-out Reset Current<br>(Note 6)                              | $\Delta$ IBOR | -           | 350                | 425          | μA             | BOR enabled VDD = 5.0V                                                                                                                                                  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD  $\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

## Applicable Devices 72 73 73A 74 74A 76 77

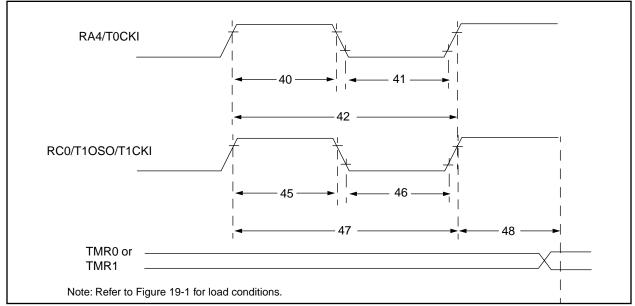

### FIGURE 19-6: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

### TABLE 19-5: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym                                | Characteristic                                 |                      |                    | Min                                              | Тур† | Max   | Units | Conditions                         |

|--------------|------------------------------------|------------------------------------------------|----------------------|--------------------|--------------------------------------------------|------|-------|-------|------------------------------------|

| 40*          | Tt0H                               | T0CKI High Pulse V                             | Vidth                | No Prescaler       | 0.5Tcy + 20                                      | —    | —     | ns    | Must also meet                     |

|              |                                    |                                                |                      | With Prescaler     | 10                                               | _    | _     | ns    | parameter 42                       |

| 41*          | Tt0L                               | T0CKI Low Pulse W                              | /idth                | No Prescaler       | 0.5TCY + 20                                      | -    | —     | ns    | Must also meet                     |

|              |                                    |                                                |                      | With Prescaler     | 10                                               | —    | —     | ns    | parameter 42                       |

| 42*          | Tt0P                               |                                                |                      | No Prescaler       | Tcy + 40                                         | _    | —     | ns    |                                    |

|              |                                    |                                                |                      | With Prescaler     | Greater of:<br>20 or <u>Tcy + 40</u><br>N        | -    | _     | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | 45* Tt1H T1CKI High Time Synchrono |                                                | Synchronous, P       | Prescaler = 1      | 0.5Tcy + 20                                      | - 1  | —     | ns    | Must also meet                     |

|              |                                    |                                                | Synchronous,         | PIC16 <b>C</b> 7X  | 15                                               | -    | —     | ns    | parameter 47                       |

|              |                                    |                                                | Prescaler = 2,4,8    | PIC16 <b>LC</b> 7X | 25                                               | -    | —     | ns    |                                    |

|              |                                    |                                                | Asynchronous         | PIC16 <b>C</b> 7X  | 30                                               | —    | —     | ns    |                                    |

|              |                                    |                                                |                      | PIC16 <b>LC</b> 7X | 50                                               | —    | —     | ns    |                                    |

| 46*          | 16* Tt1L T1CKI Low Time Synchronou |                                                | Synchronous, P       |                    | 0.5Tcy + 20                                      | -    | —     | ns    | Must also meet                     |

|              |                                    |                                                | Synchronous,         | PIC16 <b>C</b> 7X  | 15                                               |      | —     | ns    | parameter 47                       |

|              |                                    |                                                | Prescaler =<br>2,4,8 | PIC16 <b>LC</b> 7X | 25                                               | -    | -     | ns    |                                    |

|              |                                    |                                                | Asynchronous         | PIC16 <b>C</b> 7X  | 30                                               | —    | —     | ns    | ]                                  |

|              |                                    |                                                |                      | PIC16 <b>LC</b> 7X | 50                                               | —    | —     | ns    |                                    |

| 47*          | Tt1P                               | T1CKI input period                             | Synchronous          | PIC16 <b>C</b> 7X  | <u>Greater of:</u><br>30 OR <u>TCY + 40</u><br>N | -    | _     | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |                                    |                                                |                      | PIC16 <b>LC</b> 7X | <u>Greater of:</u><br>50 OR <u>TCY + 40</u><br>N |      |       |       | N = prescale value<br>(1, 2, 4, 8) |

|              |                                    |                                                | Asynchronous         | PIC16 <b>C</b> 7X  | 60                                               | -    | —     | ns    |                                    |

|              |                                    |                                                |                      | PIC16 <b>LC</b> 7X | 100                                              | -    | —     | ns    |                                    |

|              | Ft1                                | Timer1 oscillator inp<br>(oscillator enabled b |                      |                    | DC                                               | -    | 200   | kHz   |                                    |

| 48           | TCKEZtmr1                          | Delay from external                            | clock edge to tin    | ner increment      | 2Tosc                                            | —    | 7Tosc | -     |                                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## Applicable Devices 72 73 73A 74 74A 76 77

### 20.2 DC Characteristics: PIC16LC76/77-04 (Commercial, Industrial)

| DC CHA       | RACTERISTICS                                                     |               |      | ard Ope<br>ing tem | •   |       | itions (unless otherwise stated) $D^{\circ}C$ $\leq TA \leq +85^{\circ}C$ for industrial and $C$ $\leq TA \leq +70^{\circ}C$ for commercial |

|--------------|------------------------------------------------------------------|---------------|------|--------------------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Characteristic                                                   | Sym           | Min  | Тур†               | Max | Units | Conditions                                                                                                                                  |

| D001         | Supply Voltage                                                   | Vdd           | 2.5  | -                  | 6.0 | V     | LP, XT, RC osc configuration (DC - 4 MHz)                                                                                                   |

| D002*        | RAM Data Retention<br>Voltage (Note 1)                           | Vdr           | -    | 1.5                | -   | V     |                                                                                                                                             |

| D003         | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR          | -    | Vss                | -   | V     | See section on Power-on Reset for details                                                                                                   |

| D004*        | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | Svdd          | 0.05 | -                  | -   | V/ms  | See section on Power-on Reset for details                                                                                                   |

| D005         | Brown-out Reset Voltage                                          | Bvdd          | 3.7  | 4.0                | 4.3 | V     | BODEN bit in configuration word enabled                                                                                                     |

| D010         | Supply Current (Note 2,5)                                        | IDD           | -    | 2.0                | 3.8 | mA    | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                               |

| D010A        |                                                                  |               | -    | 22.5               | 48  | μA    | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                                                             |

| D015*        | Brown-out Reset Current (Note 6)                                 | $\Delta$ IBOR | -    | 350                | 425 | μA    | BOR enabled VDD = 5.0V                                                                                                                      |

| D020         | Power-down Current                                               | IPD           | -    | 7.5                | 30  | μA    | VDD = 3.0V, WDT enabled, -40°C to +85°C                                                                                                     |

| D021         | (Note 3,5)                                                       |               | -    | 0.9                | 5   | μA    | VDD = $3.0V$ , WDT disabled, 0°C to +70°C                                                                                                   |

| D021A        |                                                                  |               | -    | 0.9                | 5   | μA    | VDD = 3.0V, WDT disabled, -40°C to +85°C                                                                                                    |

| D023*        | Brown-out Reset Current<br>(Note 6)                              | ∆IBOR         | -    | 350                | 425 | μA    | BOR enabled VDD = 5.0V                                                                                                                      |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD  $\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSs.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

## Applicable Devices 72 73 73A 74 74A 76 77

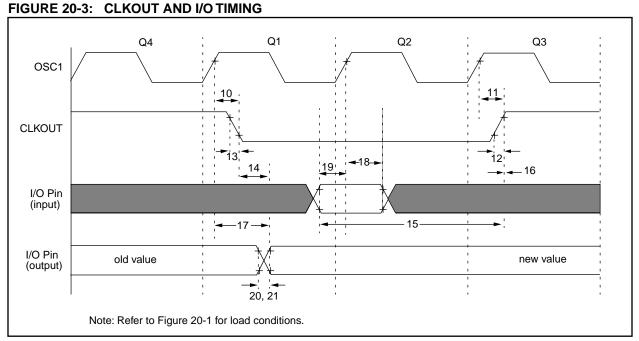

| TABLE 20-3: | <b>CLKOUT AND I/O TIMING REQUIREMENTS</b> |

|-------------|-------------------------------------------|

| IADEE 20-3. |                                           |

| Param<br>No. | Sym      | Characteristic                           |                       | Min        | Тур† | Мах         | Units  | Conditions |

|--------------|----------|------------------------------------------|-----------------------|------------|------|-------------|--------|------------|

| 10*          | TosH2ckL | OSC1 <sup>↑</sup> to CLKOUT↓             | _                     | 75         | 200  | ns          | Note 1 |            |

| 11*          | TosH2ckH | OSC1 <sup>↑</sup> to CLKOUT <sup>↑</sup> |                       | _          | 75   | 200         | ns     | Note 1     |

| 12*          | TckR     | CLKOUT rise time                         |                       | _          | 35   | 100         | ns     | Note 1     |

| 13*          | TckF     | CLKOUT fall time                         |                       | _          | 35   | 100         | ns     | Note 1     |

| 14*          | TckL2ioV | CLKOUT $\downarrow$ to Port out valid    |                       | _          | —    | 0.5Tcy + 20 | ns     | Note 1     |

| 15*          | TioV2ckH | Port in valid before CLKOUT ↑            |                       | Tosc + 200 | —    | _           | ns     | Note 1     |

| 16*          | TckH2iol | Port in hold after CLKOUT $\uparrow$     |                       | 0          | —    | _           | ns     | Note 1     |

| 17*          | TosH2ioV | OSC1↑ (Q1 cycle) to<br>Port out valid    |                       | _          | 50   | 150         | ns     |            |

| 18*          | TosH2iol | OSC1↑ (Q2 cycle) to                      | PIC16 <b>C</b> 76/77  | 100        | —    | _           | ns     |            |

|              |          | Port input invalid (I/O in hold time)    | PIC16 <b>LC</b> 76/77 | 200        | -    | _           | ns     |            |

| 19*          | TioV2osH | Port input valid to OSC1↑                | (I/O in setup time)   | 0          | —    | _           | ns     |            |

| 20*          | TioR     | Port output rise time                    | PIC16 <b>C</b> 76/77  | _          | 10   | 40          | ns     |            |

|              |          |                                          | PIC16 <b>LC</b> 76/77 | _          | —    | 80          | ns     |            |

| 21*          | TioF     | Port output fall time                    | PIC16 <b>C</b> 76/77  | _          | 10   | 40          | ns     |            |

|              |          |                                          | PIC16 <b>LC</b> 76/77 | _          | —    | 80          | ns     |            |

| 22††*        | Tinp     | INT pin high or low time                 |                       | Тсү        | —    | —           | ns     |            |

| 23††*        | Trbp     | RB7:RB4 change INT hig                   | n or low time         | Тсү        | —    | —           | ns     |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

## Applicable Devices 72 73 73A 74 74A 76 77

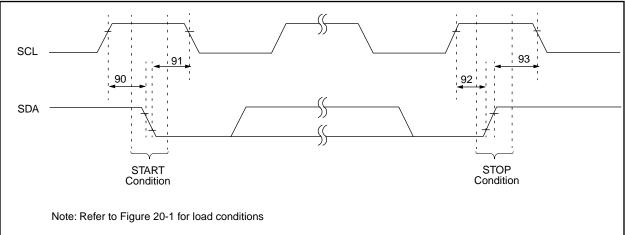

## TABLE 20-9: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Parameter<br>No. | Sym     | Characteristic  |              | Min  | Тур | Max | Units | Conditions                        |

|------------------|---------|-----------------|--------------|------|-----|-----|-------|-----------------------------------|

| 90               | TSU:STA | START condition | 100 kHz mode | 4700 | —   | —   | ns    | Only relevant for repeated START  |

|                  |         | Setup time      | 400 kHz mode | 600  | -   | —   |       | condition                         |

| 91               | THD:STA | START condition | 100 kHz mode | 4000 | —   | —   | ns    | After this period the first clock |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | 115   | pulse is generated                |

| 92               | Tsu:sto | STOP condition  | 100 kHz mode | 4700 | —   | —   | ns    |                                   |

|                  |         | Setup time      | 400 kHz mode | 600  | —   | —   |       |                                   |

| 93               | THD:STO | STOP condition  | 100 kHz mode | 4000 | —   | —   | ns    |                                   |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | 113   |                                   |

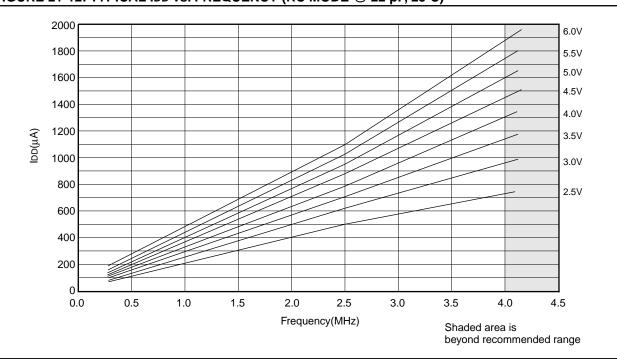

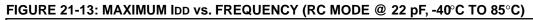

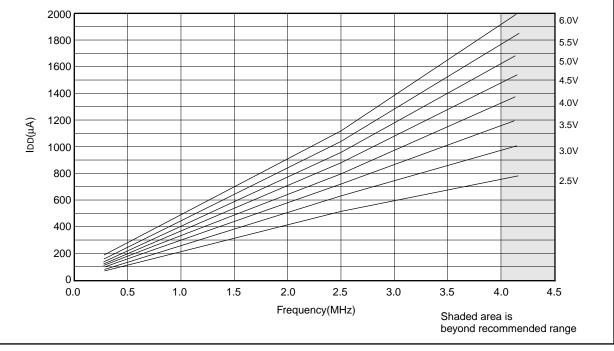

## Applicable Devices 72 73 73A 74 74A 76 77 FIGURE 21-12: TYPICAL IDD vs. FREQUENCY (RC MODE @ 22 pF, 25°C)

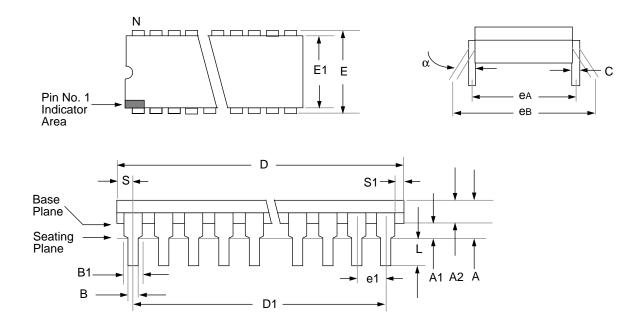

## 22.4 40-Lead Plastic Dual In-line (600 mil) (P)

|        |             | Package Gro | up: Plastic Dual | In-Line (PLA) |       |           |

|--------|-------------|-------------|------------------|---------------|-------|-----------|

|        | Millimeters |             |                  |               |       |           |

| Symbol | Min         | Мах         | Notes            | Min           | Max   | Notes     |

| α      | 0°          | 10°         |                  | 0°            | 10°   |           |

| А      | _           | 5.080       |                  | _             | 0.200 |           |

| A1     | 0.381       | -           |                  | 0.015         | -     |           |

| A2     | 3.175       | 4.064       |                  | 0.125         | 0.160 |           |

| В      | 0.355       | 0.559       |                  | 0.014         | 0.022 |           |

| B1     | 1.270       | 1.778       | Typical          | 0.050         | 0.070 | Typical   |

| С      | 0.203       | 0.381       | Typical          | 0.008         | 0.015 | Typical   |

| D      | 51.181      | 52.197      |                  | 2.015         | 2.055 |           |

| D1     | 48.260      | 48.260      | Reference        | 1.900         | 1.900 | Reference |

| E      | 15.240      | 15.875      |                  | 0.600         | 0.625 |           |

| E1     | 13.462      | 13.970      |                  | 0.530         | 0.550 |           |

| e1     | 2.489       | 2.591       | Typical          | 0.098         | 0.102 | Typical   |

| eA     | 15.240      | 15.240      | Reference        | 0.600         | 0.600 | Reference |

| eB     | 15.240      | 17.272      |                  | 0.600         | 0.680 |           |

| L      | 2.921       | 3.683       |                  | 0.115         | 0.145 |           |

| Ν      | 40          | 40          |                  | 40            | 40    |           |

| S      | 1.270       | _           |                  | 0.050         | _     |           |

| S1     | 0.508       | _           |                  | 0.020         | -     |           |

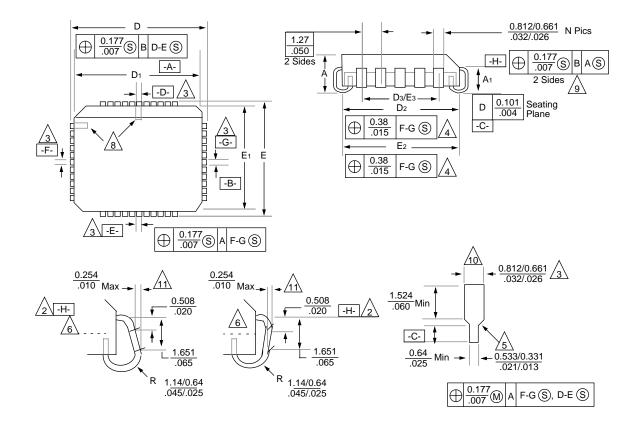

### 22.7 44-Lead Plastic Leaded Chip Carrier (Square)(PLCC)

|        | Pa          | ackage Group: F | Plastic Leaded C | hip Carrier (PL | CC)    |           |

|--------|-------------|-----------------|------------------|-----------------|--------|-----------|

|        | Millimeters |                 |                  |                 | Inches |           |

| Symbol | Min         | Max             | Notes            | Min             | Max    | Notes     |

| А      | 4.191       | 4.572           |                  | 0.165           | 0.180  |           |

| A1     | 2.413       | 2.921           |                  | 0.095           | 0.115  |           |

| D      | 17.399      | 17.653          |                  | 0.685           | 0.695  |           |

| D1     | 16.510      | 16.663          |                  | 0.650           | 0.656  |           |

| D2     | 15.494      | 16.002          |                  | 0.610           | 0.630  |           |

| D3     | 12.700      | 12.700          | Reference        | 0.500           | 0.500  | Reference |

| E      | 17.399      | 17.653          |                  | 0.685           | 0.695  |           |

| E1     | 16.510      | 16.663          |                  | 0.650           | 0.656  |           |

| E2     | 15.494      | 16.002          |                  | 0.610           | 0.630  |           |

| E3     | 12.700      | 12.700          | Reference        | 0.500           | 0.500  | Reference |

| Ν      | 44          | 44              |                  | 44              | 44     |           |

| CP     | -           | 0.102           |                  | _               | 0.004  |           |

| LT     | 0.203       | 0.381           |                  | 0.008           | 0.015  |           |

## **APPENDIX A:**

The following are the list of modifications over the PIC16C5X microcontroller family:

- 1. Instruction word length is increased to 14-bits. This allows larger page sizes both in program memory (2K now as opposed to 512 before) and register file (128 bytes now versus 32 bytes before).

- 2. A PC high latch register (PCLATH) is added to handle program memory paging. Bits PA2, PA1, PA0 are removed from STATUS register.

- 3. Data memory paging is redefined slightly. STATUS register is modified.

- Four new instructions have been added: RETURN, RETFIE, ADDLW, and SUBLW. Two instructions TRIS and OPTION are being phased out although they are kept for compati-bility with PIC16C5X.

- 5. OPTION and TRIS registers are made addressable.

- 6. Interrupt capability is added. Interrupt vector is at 0004h.

- 7. Stack size is increased to 8 deep.

- 8. Reset vector is changed to 0000h.

- Reset of all registers is revisited. Five different reset (and wake-up) types are recognized. Registers are reset differently.

- 10. Wake up from SLEEP through interrupt is added.

- 11. Two separate timers, Oscillator Start-up Timer (OST) and Power-up Timer (PWRT) are included for more reliable power-up. These timers are invoked selectively to avoid unnecessary delays on power-up and wake-up.

- 12. PORTB has weak pull-ups and interrupt on change feature.

- 13. T0CKI pin is also a port pin (RA4) now.

- 14. FSR is made a full eight bit register.

- "In-circuit serial programming" is made possible. The user can program PIC16CXX devices using only five pins: VDD, Vss, MCLR/VPP, RB6 (clock) and RB7 (data in/out).

- PCON status register is added with a Power-on Reset status bit (POR).

- 17. Code protection scheme is enhanced such that portions of the program memory can be protected, while the remainder is unprotected.

- Brown-out protection circuitry has been added. Controlled by configuration word bit BODEN. Brown-out reset ensures the device is placed in a reset condition if VDD dips below a fixed setpoint.

## APPENDIX B: COMPATIBILITY

To convert code written for PIC16C5X to PIC16CXX, the user should take the following steps:

- 1. Remove any program memory page select operations (PA2, PA1, PA0 bits) for CALL, GOTO.

- 2. Revisit any computed jump operations (write to PC or add to PC, etc.) to make sure page bits are set properly under the new scheme.

- 3. Eliminate any data memory page switching. Redefine data variables to reallocate them.

- 4. Verify all writes to STATUS, OPTION, and FSR registers since these have changed.

- 5. Change reset vector to 0000h.

## APPENDIX C: WHAT'S NEW

Added the following devices:

- PIC16C76

- PIC16C77

Removed the PIC16C710, PIC16C71, PIC16C711 from this datasheet.

Added PIC16C76 and PIC16C77 devices. The PIC16C76/77 devices have 368 bytes of data memory distributed in 4 banks and 8K of program memory in 4 pages. These two devices have an enhanced SPI that supports both clock phase and polarity. The USART has been enhanced.

When upgrading to the PIC16C76/77 please note that the upper 16 bytes of data memory in banks 1,2, and 3 are mapped into bank 0. This may require relocation of data memory usage in the user application code.

Added Q-cycle definitions to the Instruction Set Summary section.

### **APPENDIX D: WHAT'S CHANGED**

Minor changes, spelling and grammatical changes.

Added the following note to the USART section. This note applies to all devices except the PIC16C76 and PIC16C77.

For the PIC16C73/73A/74/74A the asynchronous high speed mode (BRGH = 1) may experience a high rate of receive errors. It is recommended that BRGH = 0. If you desire a higher baud rate than BRGH = 0 can support, refer to the device errata for additional information or use the PIC16C76/77.

Divided SPI section into SPI for the PIC16C76/77 and SPI for all other devices.

## APPENDIX E: PIC16/17 MICROCONTROLLERS

### E.1 PIC12CXXX Family of Devices

|            |                                         | PIC12C508       | PIC12C509       | PIC12C671       | PIC12C672       |

|------------|-----------------------------------------|-----------------|-----------------|-----------------|-----------------|

| Clock      | Maximum Frequency<br>of Operation (MHz) | 4               | 4               | 4               | 4               |

| lomony     | EPROM Program Memory                    | 512 x 12        | 1024 x 12       | 1024 x 14       | 2048 x 14       |

| lemory     | Data Memory (bytes)                     | 25              | 41              | 128             | 128             |

|            | Timer Module(s)                         | TMR0            | TMR0            | TMR0            | TMR0            |

| eripherals | A/D Converter (8-bit) Channels          | —               | —               | 4               | 4               |

|            | Wake-up from SLEEP on<br>pin change     | Yes             | Yes             | Yes             | Yes             |

|            | I/O Pins                                | 5               | 5               | 5               | 5               |

|            | Input Pins                              | 1               | 1               | 1               | 1               |