Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                              |

| Data Converters            | A/D 8x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-QFP                                                                    |

| Supplier Device Package    | 44-MQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c74a-20-pq |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address                   | Name    | Bit 7                | Bit 6              | Bit 5          | Bit 4           | Bit 3          | Bit 2           | Bit 1         | Bit 0    | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(2) |

|---------------------------|---------|----------------------|--------------------|----------------|-----------------|----------------|-----------------|---------------|----------|--------------------------|-------------------------------------|

| Bank 0                    |         |                      |                    |                |                 |                |                 |               |          |                          |                                     |

| 00h <sup>(4)</sup>        | INDF    | Addressing           | this location      | uses conten    | ts of FSR to a  | ddress data r  | nemory (not     | a physical re | egister) | 0000 0000                | 0000 0000                           |

| 01h                       | TMR0    | Timer0 mod           | lule's registe     | r              |                 |                |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 02h <sup>(4)</sup>        | PCL     | Program Co           | ounter's (PC)      | Least Signif   | icant Byte      |                |                 |               |          | 0000 0000                | 0000 0000                           |

| 03h <b>(4)</b>            | STATUS  | IRP <sup>(7)</sup>   | RP1 <sup>(7)</sup> | RP0            | TO              | PD             | Z               | DC            | С        | 0001 1xxx                | 000q quuu                           |

| 04h <b>(4)</b>            | FSR     | Indirect data        | a memory ad        | dress pointe   | er              |                |                 |               | •        | XXXX XXXX                | uuuu uuuu                           |

| 05h                       | PORTA   | _                    | _                  | PORTA Dat      | a Latch when    | written: POR   | TA pins wher    | read          |          | 0x 0000                  | 0u 0000                             |

| 06h                       | PORTB   | PORTB Dat            | a Latch whe        | n written: PC  | ORTB pins whe   | n read         |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 07h                       | PORTC   | PORTC Dat            | ta Latch whe       | n written: PC  | DRTC pins whe   | en read        |                 |               |          | XXXX XXXX                | uuuu uuuu                           |

| 08h <sup>(5)</sup>        | PORTD   | PORTD Dat            | a Latch whe        | n written: PC  | ORTD pins whe   | en read        |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 09h <b>(5)</b>            | PORTE   | _                    | _                  | _              | _               | _              | RE2             | RE1           | RE0      | xxx                      | uuu                                 |

| 0Ah <b>(1,4)</b>          | PCLATH  | _                    | _                  | _              | Write Buffer fo | or the upper t | 5 bits of the I | Program Cou   | unter    | 0 0000                   | 0 0000                              |

| 0Bh <b><sup>(4)</sup></b> | INTCON  | GIE                  | PEIE               | TOIE           | INTE            | RBIE           | T0IF            | INTF          | RBIF     | 0000 000x                | 0000 000u                           |

| 0Ch                       | PIR1    | PSPIF <sup>(3)</sup> | ADIF               | RCIF           | TXIF            | SSPIF          | CCP1IF          | TMR2IF        | TMR1IF   | 0000 0000                | 0000 0000                           |

| 0Dh                       | PIR2    | —                    | —                  | -              | -               | -              | —               | —             | CCP2IF   | 0                        | 0                                   |

| 0Eh                       | TMR1L   | Holding reg          | ister for the L    | east Signific  | ant Byte of the | e 16-bit TMR1  | l register      |               |          | xxxx xxxx                | uuuu uuuu                           |

| 0Fh                       | TMR1H   | Holding reg          | ister for the N    | lost Significa | ant Byte of the | 16-bit TMR1    | register        |               |          | XXXX XXXX                | uuuu uuuu                           |

| 10h                       | T1CON   | —                    | —                  | T1CKPS1        | T1CKPS0         | T1OSCEN        | <b>T1SYNC</b>   | TMR1CS        | TMR10N   | 00 0000                  | uu uuuu                             |

| 11h                       | TMR2    | Timer2 mod           | lule's registe     | r              |                 |                |                 |               |          | 0000 0000                | 0000 0000                           |

| 12h                       | T2CON   | —                    | TOUTPS3            | TOUTPS2        | TOUTPS1         | TOUTPS0        | TMR2ON          | T2CKPS1       | T2CKPS0  | -000 0000                | -000 0000                           |

| 13h                       | SSPBUF  | Synchronou           | is Serial Port     | Receive Bu     | ffer/Transmit R | egister        |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 14h                       | SSPCON  | WCOL                 | SSPOV              | SSPEN          | СКР             | SSPM3          | SSPM2           | SSPM1         | SSPM0    | 0000 0000                | 0000 0000                           |

| 15h                       | CCPR1L  | Capture/Co           | mpare/PWM          | Register1 (L   | _SB)            |                |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 16h                       | CCPR1H  | Capture/Co           | mpare/PWM          | Register1 (N   | MSB)            |                |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 17h                       | CCP1CON | —                    | —                  | CCP1X          | CCP1Y           | CCP1M3         | CCP1M2          | CCP1M1        | CCP1M0   | 00 0000                  | 00 0000                             |

| 18h                       | RCSTA   | SPEN                 | RX9                | SREN           | CREN            | —              | FERR            | OERR          | RX9D     | 0000 -00x                | 0000 -00x                           |

| 19h                       | TXREG   | USART Trar           | nsmit Data R       | egister        |                 |                |                 |               |          | 0000 0000                | 0000 0000                           |

| 1Ah                       | RCREG   | USART Red            | ceive Data R       | egister        |                 |                |                 |               |          | 0000 0000                | 0000 0000                           |

| 1Bh                       | CCPR2L  | Capture/Co           | mpare/PWM          | Register2 (L   | _SB)            |                |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 1Ch                       | CCPR2H  | Capture/Co           | mpare/PWM          | Register2 (N   | MSB)            |                |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 1Dh                       | CCP2CON | —                    | —                  | CCP2X          | CCP2Y           | CCP2M3         | CCP2M2          | CCP2M1        | CCP2M0   | 00 0000                  | 00 0000                             |

| 1Eh                       | ADRES   | A/D Result           | Register           |                |                 |                |                 |               |          | XXXX XXXX                | uuuu uuuu                           |

| 1Fh                       | ADCON0  | ADCS1                | ADCS0              | CHS2           | CHS1            | CHS0           | GO/DONE         | —             | ADON     | 0000 00-0                | 0000 00-0                           |

TABLE 4-2:

PIC16C73/73A/74/74A SPECIAL FUNCTION REGISTER SUMMARY

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A, always maintain these bits clear.

4: These registers can be addressed from either bank.

5: PORTD and PORTE are not physically implemented on the PIC16C73/73A, read as '0'.

6: Brown-out Reset is not implemented on the PIC16C73 or the PIC16C74, read as '0'.

7: The IRP and RP1 bits are reserved on the PIC16C73/73A/74/74A, always maintain these bits clear.

4.2.2.4 PIE1 REGISTER

Applicable Devices

72 73 73A 74 74A 76 77

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

This register contains the individual enable bits for the peripheral interrupts.

#### FIGURE 4-10: PIE1 REGISTER PIC16C72 (ADDRESS 8Ch)

| U-0      | R/W-0                                                                                                                                                 | U-0        | U-0                                       | R/W-0      | R/W-0  | R/W-0  | R/W-0  |                                                                                                                        |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------|------------|--------|--------|--------|------------------------------------------------------------------------------------------------------------------------|--|--|--|

|          | ADIE                                                                                                                                                  | _          | —                                         | SSPIE      | CCP1IE | TMR2IE | TMR1IE | R = Readable bit                                                                                                       |  |  |  |

| bit7     |                                                                                                                                                       |            |                                           |            |        |        | bitO   | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>- n = Value at POR reset</li> </ul> |  |  |  |

| bit 7:   | Unimpler                                                                                                                                              | nented: R  | lead as '0'                               |            |        |        |        |                                                                                                                        |  |  |  |

| bit 6:   |                                                                                                                                                       | es the A/D | er Interrup<br>D interrupt<br>D interrupt |            | it     |        |        |                                                                                                                        |  |  |  |

| bit 5-4: | Unimpler                                                                                                                                              | nented: R  | ead as '0'                                |            |        |        |        |                                                                                                                        |  |  |  |

| bit 3:   | <b>SSPIE</b> : Synchronous Serial Port Interrupt Enable bit<br>1 = Enables the SSP interrupt<br>0 = Disables the SSP interrupt                        |            |                                           |            |        |        |        |                                                                                                                        |  |  |  |

| bit 2:   | <b>CCP1IE</b> : 0<br>1 = Enabl<br>0 = Disab                                                                                                           | es the CC  | P1 interru                                | pt         |        |        |        |                                                                                                                        |  |  |  |

| bit 1:   | <b>TMR2IE</b> : TMR2 to PR2 Match Interrupt Enable bit<br>1 = Enables the TMR2 to PR2 match interrupt<br>0 = Disables the TMR2 to PR2 match interrupt |            |                                           |            |        |        |        |                                                                                                                        |  |  |  |

| bit 0:   | 1 = Enabl                                                                                                                                             | es the TM  | erflow Inte<br>R1 overflo<br>IR1 overflo  | w interrup | ot     |        |        |                                                                                                                        |  |  |  |

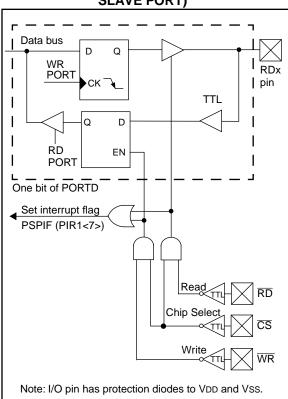

#### 5.7 Parallel Slave Port Applicable Devices 72 73 73 74 74 76 77

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port when control bit PSPMODE (TRISE<4>) is set. In slave mode it is asynchronously readable and writable by the external world through  $\overline{RD}$  control input pin RE0/ $\overline{RD}$ /AN5 and  $\overline{WR}$  control input pin RE1/ $\overline{WR}$ /AN6.

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD/AN5 to be the RD input, RE1/ WR/AN6 to be the WR input and RE2/CS/AN7 to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set) and the A/D port configuration bits PCFG2:PCFG0 (ADCON1<2:0>) must be set, which will configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches, one for data-out (from the PIC16/17) and one for data input. The user writes 8-bit data to PORTD data latch and reads data from the port pin latch (note that they have the same address). In this mode, the TRISD register is ignored, since the microprocessor is controlling the direction of data flow.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$ lines are first detected low. When either the  $\overline{CS}$  or  $\overline{WR}$ lines become high (level triggered), then the Input Buffer Full status flag bit IBF (TRISE<7>) is set on the Q4 clock cycle, following the next Q2 cycle, to signal the write is complete (Figure 5-12). The interrupt flag bit PSPIF (PIR1<7>) is also set on the same Q4 clock cycle. IBF can only be cleared by reading the PORTD input latch. The input Buffer Overflow status flag bit IBOV (TRISE<5>) is set if a second write to the Parallel Slave Port is attempted when the previous byte has not been read out of the buffer.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The Output Buffer Full status flag bit OBF (TRISE<6>) is cleared immediately (Figure 5-13) indicating that the PORTD latch is waiting to be read by the external bus. When either the  $\overline{CS}$  or  $\overline{RD}$  pin becomes high (level triggered), the interrupt flag bit PSPIF is set on the Q4 clock cycle, following the next Q2 cycle, indicating that the read is complete. OBF remains low until data is written to PORTD by the user firmware.

When not in Parallel Slave Port mode, the IBF and OBF bits are held clear. However, if flag bit IBOV was previously set, it must be cleared in firmware.

An interrupt is generated and latched into flag bit PSPIF when a read or write operation is completed. PSPIF must be cleared by the user in firmware and the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

#### FIGURE 5-11: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

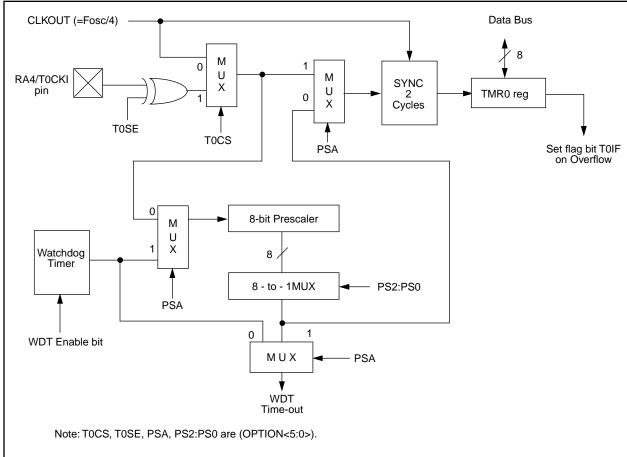

### 7.3 <u>Prescaler</u> Applicable Devices 72|73|73A|74|74A|76|77

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The PSA and PS2:PS0 bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

#### FIGURE 7-6: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

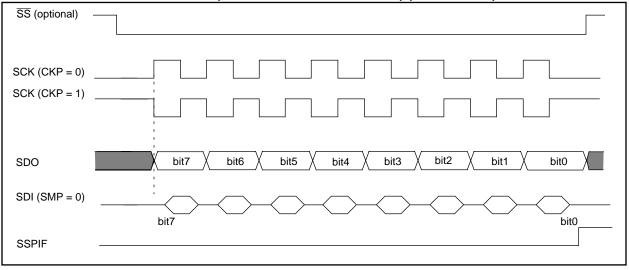

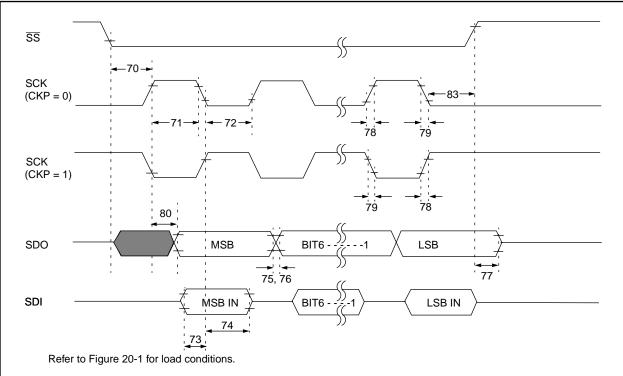

The  $\overline{SS}$  pin allows a synchronous slave mode. The SPI must be in slave mode (SSPCON<3:0> = 04h) and the TRISA<5> bit must be set for the synchronous slave mode to be enabled. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. If the  $\overline{SS}$  pin is taken low without resetting SPI mode, the transmission will continue from the point at which it was taken high. External pull-up/ pull-down resistors may be desirable, depending on the application.

| Note: | When the SPI is in Slave Mode with $\overline{SS}$ pin<br>control enabled, (SSPCON<3:0> = 0100)<br>the SPI module will reset if the $\overline{SS}$ pin is set<br>to VDD. |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | If the SPI is used in Slave Mode with                                                                                                                                     |

CKE = '1', then the SS pin control must be enabled. To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as

be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

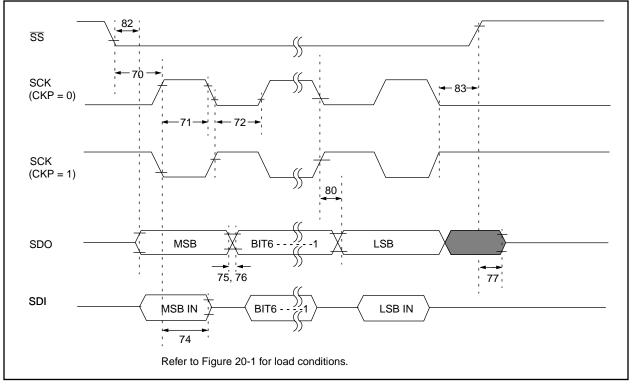

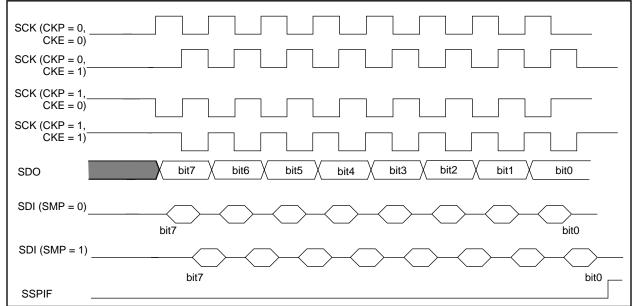

#### FIGURE 11-11: SPI MODE TIMING, MASTER MODE (PIC16C76/77)

#### FIGURE 11-12: SPI MODE TIMING (SLAVE MODE WITH CKE = 0) (PIC16C76/77)

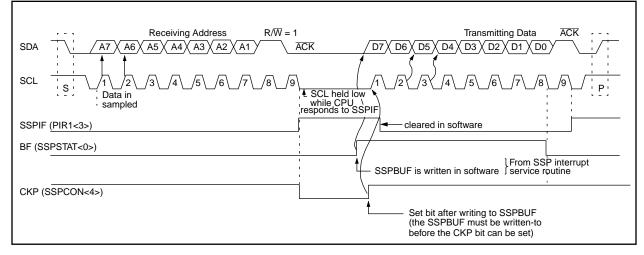

#### 11.5.1.3 TRANSMISSION

When the  $R\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The  $\overline{ACK}$  pulse will be sent on the ninth bit, and pin RC3/SCK/SCL is held low. The transmit data must be loaded into the SSP-BUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 11-26). An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software, and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP.

#### FIGURE 11-26: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

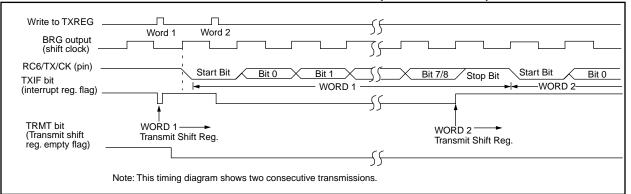

Steps to follow when setting up an Asynchronous Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH. (Section 12.1)

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

#### FIGURE 12-8: ASYNCHRONOUS MASTER TRANSMISSION

#### FIGURE 12-9: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

#### TABLE 12-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address | Name  | Bit 7                           | Bit 6    | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|---------------------------------|----------|--------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup>            | ADIF     | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h     | RCSTA | SPEN                            | RX9      | SREN   | CREN  | —     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 19h     | TXREG | USART Trar                      | nsmit Re | gister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup>            | ADIE     | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h     | TXSTA | CSRC                            | TX9      | TXEN   | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h     | SPBRG | RG Baud Rate Generator Register |          |        |       |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

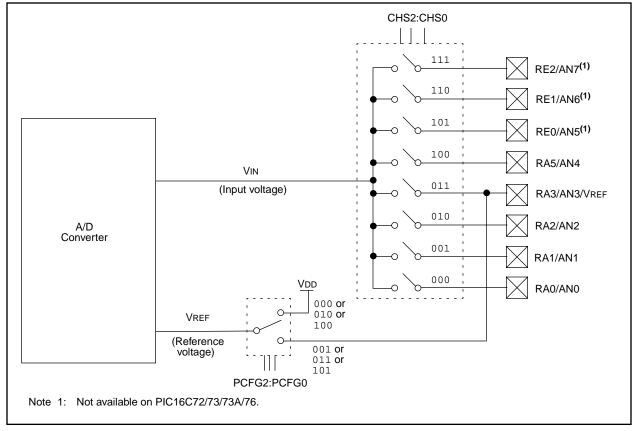

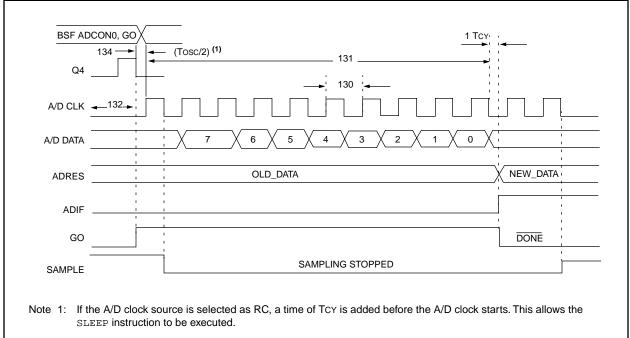

The ADRES register contains the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRES register, the GO/DONE bit (ADCON0<2>) is cleared, and A/D interrupt flag bit ADIF is set. The block diagrams of the A/D module are shown in Figure 13-3.

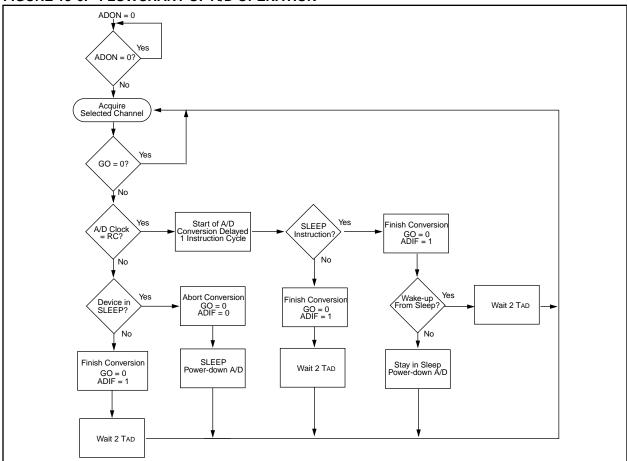

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 13.1. After this acquisition time has elapsed the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins / voltage reference / and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set GIE bit

#### FIGURE 13-3: A/D BLOCK DIAGRAM

- 3. Wait the required acquisition time.

- 4. Start conversion:Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:Polling for the GO/DONE bit to be cleared

- OR

- Waiting for the A/D interrupt

- Read A/D Result register (ADRES), clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before next acquisition starts.

TABLE 13-2: REGISTERS/BITS ASSOCIATED WITH A/D, PIC16C72

| Address | Name   | Bit 7   | Bit 6       | Bit 5 | Bit 4                         | Bit 3 | Bit 2   | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|--------|---------|-------------|-------|-------------------------------|-------|---------|--------|--------|--------------------------|---------------------------|

| 0Bh,8Bh | INTCON | GIE     | PEIE        | TOIE  | INTE                          | RBIE  | T0IF    | INTF   | RBIF   | 0000 000x                | 0000 000u                 |

| 0Ch     | PIR1   | —       | ADIF        | -     | —                             | SSPIF | CCP1IF  | TMR2IF | TMR1IF | -0 0000                  | -0 0000                   |

| 8Ch     | PIE1   | —       | ADIE        | -     | _                             | SSPIE | CCP1IE  | TMR2IE | TMR1IE | -0 0000                  | -0 0000                   |

| 1Eh     | ADRES  | A/D Res | sult Regist | ter   |                               |       |         |        |        | xxxx xxxx                | uuuu uuuu                 |

| 1Fh     | ADCON0 | ADCS1   | ADCS0       | CHS2  | CHS1                          | CHS0  | GO/DONE | —      | ADON   | 0000 00-0                | 0000 00-0                 |

| 9Fh     | ADCON1 | —       | —           | _     | _                             | _     | PCFG2   | PCFG1  | PCFG0  | 000                      | 000                       |

| 05h     | PORTA  | _       | _           | RA5   | RA4                           | RA3   | RA2     | RA1    | RA0    | 0x 0000                  | 0u 0000                   |

| 85h     | TRISA  | _       |             | PORTA | PORTA Data Direction Register |       |         |        |        |                          | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

#### FIGURE 14-2: CONFIGURATION WORD FOR PIC16C72/73A/74A/76/77

|          | P0 CP1                 | CP0     | CP1      | CP0      | _        | BODEN     | CP1     | CP0     | PWRTE    | WDTE    | FOSC1    |            | Register:<br>Address | CONFIG<br>2007h |

|----------|------------------------|---------|----------|----------|----------|-----------|---------|---------|----------|---------|----------|------------|----------------------|-----------------|

| bit13    |                        |         |          |          |          |           |         |         |          |         |          | bit0       | Address              | 200711          |

| bit 13-8 | CP1:CP0                |         |          |          | ; (2)    |           |         |         |          |         |          |            |                      |                 |

| 5-4:     | 11 = Cod               | •       |          |          |          |           |         |         |          |         |          |            |                      |                 |

|          | 10 = Upp               |         |          |          |          |           |         |         |          |         |          |            |                      |                 |

|          | 01 = Upp<br>00 = All m |         |          |          |          | / code pr | otected | 1       |          |         |          |            |                      |                 |

| bit 7:   | Unimpler               | ,       |          |          |          |           |         |         |          |         |          |            |                      |                 |

| bit 6:   | BODEN:                 |         |          |          | hle hit  | (1)       |         |         |          |         |          |            |                      |                 |

| 511 0.   | 1 = BOR (              |         |          |          |          |           |         |         |          |         |          |            |                      |                 |

|          | 0 = BOR (              | disable | d        |          |          |           |         |         |          |         |          |            |                      |                 |

| bit 3:   | PWRTE:                 | Power-u | up Time  | er Enab  | le bit ( | 1)        |         |         |          |         |          |            |                      |                 |

|          | 1 = PWR1               |         |          |          |          |           |         |         |          |         |          |            |                      |                 |

|          | 0 = PWRT               | enabl   | ed       |          |          |           |         |         |          |         |          |            |                      |                 |

| bit 2:   | WDTE: W                |         |          | Enabl    | e bit    |           |         |         |          |         |          |            |                      |                 |

|          | 1 = WDT                |         | -        |          |          |           |         |         |          |         |          |            |                      |                 |

|          | 0 = WDT                |         | -        |          |          |           |         |         |          |         |          |            |                      |                 |

| bit 1-0: | FOSC1:F                |         |          | tor Sele | ection   | bits      |         |         |          |         |          |            |                      |                 |

|          | 11 = RC (<br>10 = HS ( |         |          |          |          |           |         |         |          |         |          |            |                      |                 |

|          | 10 = HSC<br>01 = XTC   |         |          |          |          |           |         |         |          |         |          |            |                      |                 |

|          | 01 = 100               |         |          |          |          |           |         |         |          |         |          |            |                      |                 |

|          |                        |         |          |          |          |           |         |         |          |         |          |            |                      |                 |

| Note 1:  | -                      |         |          |          |          | •         |         |         |          | ,       | -        | ess of the | value of bit F       | PWRTE.          |

| ~        | Ensure th              |         |          |          |          | ,         |         |         |          |         |          |            |                      |                 |

| 2:       | All of the             | CP1:CF  | 20 pairs | s have t | to be g  | jiven the | same \  | alue to | o enable | the coo | de prote | ction sch  | eme listed.          |                 |

| BTFSS             | Bit Test                                 | f, Skip if S                                | Set                |                  | CALL        |                                                                                                                                                       | Call Sub                               | routine                              |                                                            |                               |

|-------------------|------------------------------------------|---------------------------------------------|--------------------|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------|------------------------------------------------------------|-------------------------------|

| Syntax:           | [ <i>label</i> ] B1                      | TFSS f,b                                    |                    |                  | Syntax:     |                                                                                                                                                       | [ label ]                              | CALL 4                               | κ                                                          |                               |

| Operands:         | $0 \le f \le 12$                         |                                             |                    |                  | Operands:   |                                                                                                                                                       | $0 \le k \le 2$                        | 047                                  |                                                            |                               |

|                   | 0 ≤ b < 7                                |                                             |                    |                  | Operation:  |                                                                                                                                                       | (PC)+ 1-                               | → TOS,                               |                                                            |                               |

| Operation:        | skip if (f<                              | skip if (f <b>) = 1</b>                     |                    |                  |             | $\label{eq:kappa} \begin{array}{l} k \rightarrow \text{PC}{<}10{:}0{>}, \\ (\text{PCLATH}{<}4{:}3{>}) \rightarrow \text{PC}{<}12{:}11{>} \end{array}$ |                                        |                                      |                                                            |                               |

| Status Affected:  | None                                     |                                             |                    |                  | <b>.</b>    |                                                                                                                                                       |                                        | 1<4:3>) -                            | $\rightarrow$ PC<12                                        | :11>                          |

| Encoding:         | 01                                       | 11bb                                        | bfff               | ffff             | Status Affe | ected:                                                                                                                                                | None                                   |                                      | 1                                                          |                               |

| Description:      |                                          | register 'f' i                              |                    | he next          | Encoding:   |                                                                                                                                                       | 10                                     | 0kkk                                 | kkkk                                                       | kkkk                          |

|                   | If bit 'b' is<br>discarded<br>instead, m | '1', then the<br>and a NOF                  | e next instr       | ed               | Descriptior | n:                                                                                                                                                    | (PC+1) is<br>eleven bit<br>into PC bit | pushed or<br>immediate<br>ts <10:0>. | st, return ac<br>nto the stac<br>e address is<br>The upper | k. The<br>s loaded<br>bits of |

| Words:            | 1                                        |                                             |                    |                  |             |                                                                                                                                                       | is a two cy                            |                                      | rom PCLAT<br>ction.                                        | H. CALL                       |

| Cycles:           | 1(2)                                     |                                             |                    |                  | Words:      |                                                                                                                                                       | 1                                      |                                      |                                                            |                               |

| Q Cycle Activity: | Q1                                       | Q2                                          | Q3                 | Q4               | Cycles:     |                                                                                                                                                       | 2                                      |                                      |                                                            |                               |

|                   | Decode                                   | Read<br>register 'f'                        | Process<br>data    | No-<br>Operation | Q Cycle Ad  | ctivity:                                                                                                                                              | Q1                                     | Q2                                   | Q3                                                         | Q4                            |

| If Skip:          | (2nd Cyc                                 | le)                                         |                    |                  | 15          | st Cycle                                                                                                                                              | Decode                                 | Read<br>literal 'k',                 | Process<br>data                                            | Write to<br>PC                |

| ·                 | Q1                                       | Q2                                          | Q3                 | Q4               |             |                                                                                                                                                       |                                        | Push PC<br>to Stack                  |                                                            |                               |

|                   | No-<br>Operation                         | No-<br>Operation                            | No-<br>Operation   | No-<br>Operation | 2n          | d Cycle                                                                                                                                               | No-<br>Operation                       | No-<br>Operation                     | No-<br>Operation                                           | No-<br>Operation              |

| Example           | HERE<br>FALSE                            | BTFSC<br>GOTO                               | FLAG,1<br>PROCESS_ | _CODE            | Example     |                                                                                                                                                       | HERE<br>Before Ir                      | CALL                                 | THERE                                                      |                               |

|                   | TRUE                                     | •                                           |                    |                  |             |                                                                                                                                                       | Delote II                              |                                      | ₁<br>\ddress н≘                                            | RE                            |

|                   |                                          | •                                           |                    |                  |             |                                                                                                                                                       | After Inst                             | truction                             |                                                            |                               |

|                   | Before In                                |                                             |                    |                  |             |                                                                                                                                                       |                                        |                                      | Address TH<br>Address HE                                   |                               |

|                   | After Inst                               | ruction<br>if FLAG<1:<br>PC =<br>if FLAG<1: | address F          | ALSE             |             |                                                                                                                                                       |                                        | 103 = 7                              |                                                            | RE+1                          |

# PIC16C7X

| IORWF             | Inclusive                                                        | e OR W v                     | with f           |                      |  |  |  |  |

|-------------------|------------------------------------------------------------------|------------------------------|------------------|----------------------|--|--|--|--|

| Syntax:           | [ label ]                                                        | IORWF                        | f,d              |                      |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$ | 27                           |                  |                      |  |  |  |  |

| Operation:        | (W) .OR. (f) $\rightarrow$ (destination)                         |                              |                  |                      |  |  |  |  |

| Status Affected:  | Z                                                                |                              |                  |                      |  |  |  |  |

| Encoding:         | 00                                                               | 0100                         | dfff             | ffff                 |  |  |  |  |

| Description:      | Inclusive C<br>ter 'f'. If 'd'<br>W register<br>back in reg      | is 0 the re<br>. If 'd' is 1 | sult is place    | ced in the           |  |  |  |  |

| Words:            | 1                                                                |                              |                  |                      |  |  |  |  |

| Cycles:           | 1                                                                |                              |                  |                      |  |  |  |  |

| Q Cycle Activity: | Q1                                                               | Q2                           | Q3               | Q4                   |  |  |  |  |

|                   | Decode                                                           | Read<br>register<br>'f'      | Process<br>data  | Write to destination |  |  |  |  |

| Example           | IORWF                                                            |                              | RESULT,          | 0                    |  |  |  |  |

|                   | Before In                                                        |                              |                  |                      |  |  |  |  |

|                   |                                                                  | RESULT<br>W                  | = 0x13<br>= 0x91 | -                    |  |  |  |  |

|                   | After Inst                                                       |                              |                  | 3                    |  |  |  |  |

| MOVLW             | Move Literal to W                                                                          |  |  |  |  |  |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Syntax:           | [ <i>label</i> ] MOVLW k                                                                   |  |  |  |  |  |  |  |  |  |

| Operands:         | $0 \le k \le 255$                                                                          |  |  |  |  |  |  |  |  |  |

| Operation:        | $k \rightarrow (W)$                                                                        |  |  |  |  |  |  |  |  |  |

| Status Affected:  | None                                                                                       |  |  |  |  |  |  |  |  |  |

| Encoding:         | 11 00xx kkkk kkkk                                                                          |  |  |  |  |  |  |  |  |  |

| Description:      | The eight bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |  |  |  |  |  |  |  |  |  |

| Words:            | 1                                                                                          |  |  |  |  |  |  |  |  |  |

| Cycles:           | 1                                                                                          |  |  |  |  |  |  |  |  |  |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                |  |  |  |  |  |  |  |  |  |

|                   | Decode Read literal 'k' Process Write to W                                                 |  |  |  |  |  |  |  |  |  |

| Example           | MOVLW $0x5A$<br>After Instruction<br>W = 0x5A                                              |  |  |  |  |  |  |  |  |  |

| MOVF              | Move f                                                                                                                                                                                                                                                          |                         |                 |                      |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|----------------------|--|--|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                                                                                       | MOVF                    | f,d             |                      |  |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                               |                         |                 |                      |  |  |  |  |  |

| Operation:        | (f) $\rightarrow$ (destination)                                                                                                                                                                                                                                 |                         |                 |                      |  |  |  |  |  |

| Status Affected:  | Z                                                                                                                                                                                                                                                               |                         |                 |                      |  |  |  |  |  |

| Encoding:         | 00                                                                                                                                                                                                                                                              | 1000                    | dfff            | ffff                 |  |  |  |  |  |

| Description:      | The contents of register f is moved to a destination dependant upon the status of d. If $d = 0$ , destination is W register. If $d = 1$ , the destination is file register f itself. $d = 1$ is useful to test a file register since status flag Z is affected. |                         |                 |                      |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                               |                         |                 |                      |  |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                               |                         |                 |                      |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                                                              | Q2                      | Q3              | Q4                   |  |  |  |  |  |

|                   | Decode                                                                                                                                                                                                                                                          | Read<br>register<br>'f' | Process<br>data | Write to destination |  |  |  |  |  |

| Example           | MOVF                                                                                                                                                                                                                                                            | ,                       | 0               |                      |  |  |  |  |  |

|                   |                                                                                                                                                                                                                                                                 |                         | ie in FSR i     | register             |  |  |  |  |  |

| MOVWF             | Move W            | to f                    |                 |                       |  |  |  |  |  |

|-------------------|-------------------|-------------------------|-----------------|-----------------------|--|--|--|--|--|

| Syntax:           | [ label ]         | MOVW                    | = f             |                       |  |  |  |  |  |

| Operands:         | $0 \le f \le 12$  | 27                      |                 |                       |  |  |  |  |  |

| Operation:        | $(W) \to (f)$     | $(W) \rightarrow (f)$   |                 |                       |  |  |  |  |  |

| Status Affected:  | None              |                         |                 |                       |  |  |  |  |  |

| Encoding:         | 00                | 0000                    | lfff            | ffff                  |  |  |  |  |  |

| Description:      | Move data<br>'f'. | from W r                | egister to      | register              |  |  |  |  |  |

| Words:            | 1                 |                         |                 |                       |  |  |  |  |  |

| Cycles:           | 1                 |                         |                 |                       |  |  |  |  |  |

| Q Cycle Activity: | Q1                | Q2                      | Q3              | Q4                    |  |  |  |  |  |

|                   | Decode            | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |  |  |  |  |

| Example           | MOVWF             | OPTIC                   | DN_REG          |                       |  |  |  |  |  |

|                   | Before In         |                         |                 | -                     |  |  |  |  |  |

|                   |                   | OPTION<br>W             | = 0xF<br>= 0x4  | -                     |  |  |  |  |  |

|                   | After Inst        | ruction                 |                 |                       |  |  |  |  |  |

|                   |                   | OPTION                  |                 |                       |  |  |  |  |  |

|                   |                   | W                       | = 0x4           | F                     |  |  |  |  |  |

| NOP               | No Operation |                  |                  |                  |  |  |  |  |  |  |

|-------------------|--------------|------------------|------------------|------------------|--|--|--|--|--|--|

| Syntax:           | [ label ]    | NOP              |                  |                  |  |  |  |  |  |  |

| Operands:         | None         |                  |                  |                  |  |  |  |  |  |  |

| Operation:        | No opera     | ation            |                  |                  |  |  |  |  |  |  |

| Status Affected:  | None         |                  |                  |                  |  |  |  |  |  |  |

| Encoding:         | 00           | 0000             | 0xx0             | 0000             |  |  |  |  |  |  |

| Description:      | No operat    | ion.             |                  |                  |  |  |  |  |  |  |

| Words:            | 1            |                  |                  |                  |  |  |  |  |  |  |

| Cycles:           | 1            |                  |                  |                  |  |  |  |  |  |  |

| Q Cycle Activity: | Q1           | Q2               | Q3               | Q4               |  |  |  |  |  |  |

|                   | Decode       | No-<br>Operation | No-<br>Operation | No-<br>Operation |  |  |  |  |  |  |

| Example           | NOP          |                  |                  |                  |  |  |  |  |  |  |

| RETFIE Return from Interrupt |                                                                       |                                                            |                                                           |                            |  |  |  |  |

|------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------|----------------------------|--|--|--|--|

| Syntax:                      | [label] RETFIE                                                        |                                                            |                                                           |                            |  |  |  |  |

| Operands:                    | None                                                                  |                                                            |                                                           |                            |  |  |  |  |

| Operation:                   | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$               |                                                            |                                                           |                            |  |  |  |  |

| Status Affected:             | None                                                                  |                                                            |                                                           |                            |  |  |  |  |

| Encoding:                    | 00                                                                    | 0000                                                       | 0000                                                      | 1001                       |  |  |  |  |

|                              | •                                                                     | · ·                                                        | ) is load                                                 |                            |  |  |  |  |

|                              | PC. Interru<br>Global Inte                                            | upts are er<br>errupt Ena<br><7>). This i                  | ble bit, GIE                                              | setting                    |  |  |  |  |

| Words:                       | PC. Interru<br>Global Inte<br>(INTCON<                                | upts are er<br>errupt Ena<br><7>). This i                  | habled by s<br>ble bit, GIE                               | setting                    |  |  |  |  |

| Words:<br>Cycles:            | PC. Interru<br>Global Inte<br>(INTCON-<br>instruction                 | upts are er<br>errupt Ena<br><7>). This i                  | habled by s<br>ble bit, GIE                               | setting                    |  |  |  |  |

|                              | PC. Interru<br>Global Inte<br>(INTCON-<br>instruction                 | upts are er<br>errupt Ena<br><7>). This i                  | habled by s<br>ble bit, GIE                               | setting                    |  |  |  |  |

| Cycles:                      | PC. Interru<br>Global Inte<br>(INTCON-<br>instruction<br>1<br>2       | upts are er<br>errupt Ena<br><7>). This i                  | nabled by s<br>ble bit, GIE<br>is a two cy                | setting<br>cle<br>Q4       |  |  |  |  |

| Cycles:<br>Q Cycle Activity: | PC. Interru<br>Global Inte<br>(INTCON-<br>instruction<br>1<br>2<br>Q1 | upts are er<br>errupt Ena<br><7>). This i<br><br>Q2<br>No- | abled by s<br>ble bit, GIE<br>s a two cy<br>Q3<br>Set the | setting<br><u>=</u><br>cle |  |  |  |  |

After Interrupt PC = TOS GIE = 1

| OPTION                 | Load Op                                                                       | tion Reg                                       | gister                                                 |                                         |  |  |  |  |

|------------------------|-------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------|-----------------------------------------|--|--|--|--|

| Syntax:                | [label] OPTION                                                                |                                                |                                                        |                                         |  |  |  |  |

| Operands:              | None                                                                          |                                                |                                                        |                                         |  |  |  |  |

| Operation:             | $(W) \rightarrow OPTION$                                                      |                                                |                                                        |                                         |  |  |  |  |

| Status Affected:       | None                                                                          |                                                |                                                        |                                         |  |  |  |  |

| Encoding:              | 00                                                                            | 0000                                           | 0110                                                   | 0010                                    |  |  |  |  |

| Description:<br>Words: | The contelloaded in the instruction patibility we since OPT register, the it. | he OPTIC<br>is suppo<br>ith PIC16<br>ΓΙΟΝ is a | DN register<br>rted for coo<br>C5X produ<br>readable/v | r. This<br>de com-<br>ucts.<br>vritable |  |  |  |  |

| Cycles:                | 1                                                                             |                                                |                                                        |                                         |  |  |  |  |

| Example                |                                                                               |                                                |                                                        |                                         |  |  |  |  |

|                        |                                                                               | re PIC16                                       | rd compa<br>CXX produ<br>uction.                       | -                                       |  |  |  |  |

|                        |                                                                               |                                                |                                                        |                                         |  |  |  |  |

# PIC16C7X

| XORLW             | Exclusive OR Literal with W |                                                                                                                             |                 |               |  |  |  |  |  |  |  |

|-------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|--|--|--|--|--|--|--|

| Syntax:           | [label]                     | XORL                                                                                                                        | V k             |               |  |  |  |  |  |  |  |

| Operands:         | $0 \le k \le 2$             | $0 \le k \le 255$                                                                                                           |                 |               |  |  |  |  |  |  |  |

| Operation:        | (W) .XO                     | $R.k \rightarrow (N)$                                                                                                       | N)              |               |  |  |  |  |  |  |  |

| Status Affected:  | Z                           |                                                                                                                             |                 |               |  |  |  |  |  |  |  |

| Encoding:         | 11                          | 1010                                                                                                                        | kkkk            | kkkk          |  |  |  |  |  |  |  |

| Description:      | XOR'ed v                    | The contents of the W register are<br>XOR'ed with the eight bit literal 'k'.<br>The result is placed in the W regis-<br>ter |                 |               |  |  |  |  |  |  |  |

| Words:            | 1                           |                                                                                                                             |                 |               |  |  |  |  |  |  |  |

| Cycles:           | 1                           |                                                                                                                             |                 |               |  |  |  |  |  |  |  |

| Q Cycle Activity: | Q1                          | Q2                                                                                                                          | Q3              | Q4            |  |  |  |  |  |  |  |

|                   | Decode                      | Read<br>literal 'k'                                                                                                         | Process<br>data | Write to<br>W |  |  |  |  |  |  |  |

| Example:          | XORLW                       | 0xAF                                                                                                                        |                 |               |  |  |  |  |  |  |  |

|                   | Before I                    | nstructio                                                                                                                   | n               |               |  |  |  |  |  |  |  |

|                   |                             | W =                                                                                                                         | 0xB5            |               |  |  |  |  |  |  |  |

|                   | After Ins                   | truction                                                                                                                    |                 |               |  |  |  |  |  |  |  |

|                   |                             | W =                                                                                                                         | 0x1A            |               |  |  |  |  |  |  |  |

|                   |                             |                                                                                                                             |                 |               |  |  |  |  |  |  |  |

| XORWF             | Exclusiv                                               | e OR W                    | with f                         |                        |

|-------------------|--------------------------------------------------------|---------------------------|--------------------------------|------------------------|

| Syntax:           | [label]                                                | XORWF                     | f,d                            |                        |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$                         | 27                        |                                |                        |

| Operation:        | (W) .XOF                                               | $R.\left(f\right)\to(o$   | destinatio                     | on)                    |

| Status Affected:  | Z                                                      |                           |                                |                        |

| Encoding:         | 00                                                     | 0110                      | dfff                           | ffff                   |

| Description:      | Exclusive<br>register wi<br>result is st<br>1 the resu | th registe<br>ored in the | r 'f'. If 'd' is<br>e W regist | 0 the<br>er. If 'd' is |

| Words:            | 1                                                      |                           |                                |                        |

| Cycles:           | 1                                                      |                           |                                |                        |

| Q Cycle Activity: | Q1                                                     | Q2                        | Q3                             | Q4                     |

|                   | Decode                                                 | Read<br>register<br>'f'   | Process<br>data                | Write to destination   |

| Example           | XORWF                                                  |                           | 1                              |                        |

|                   | Before In                                              | struction                 |                                |                        |

|                   |                                                        | REG<br>W                  | ••••                           | AF<br>B5               |

|                   | After Inst                                             | ruction                   |                                |                        |

|                   |                                                        | REG<br>W                  | 0/1                            | 1A<br>B5               |

| <u> 8</u> 8 5              |                                                    |                                       |                                                    |                      |                                                                  |                                                |                                    |                                              |                                                     |                                         |                                   |                                      |          |          |          |                                       |

|----------------------------|----------------------------------------------------|---------------------------------------|----------------------------------------------------|----------------------|------------------------------------------------------------------|------------------------------------------------|------------------------------------|----------------------------------------------|-----------------------------------------------------|-----------------------------------------|-----------------------------------|--------------------------------------|----------|----------|----------|---------------------------------------|

| HCS200<br>HCS300<br>HCS301 |                                                    |                                       |                                                    |                      |                                                                  |                                                |                                    |                                              |                                                     | 7                                       | 7                                 |                                      |          |          |          | 7                                     |

| 24CXX<br>25CXX<br>93CXX    |                                                    |                                       |                                                    |                      |                                                                  |                                                | 7                                  |                                              |                                                     | 7                                       |                                   | 7                                    |          |          |          |                                       |

| PIC17C75X                  | Available<br>3Q97                                  |                                       | 7                                                  | 7                    |                                                                  |                                                |                                    |                                              | 7                                                   | 7                                       |                                   |                                      |          |          |          |                                       |

| PIC17C4X                   | 7                                                  |                                       | 7                                                  | 7                    | 7                                                                | 7                                              |                                    |                                              | 7                                                   | 7                                       |                                   |                                      | 7        |          |          |                                       |