Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                    |

| Data Converters            | A/D 8x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

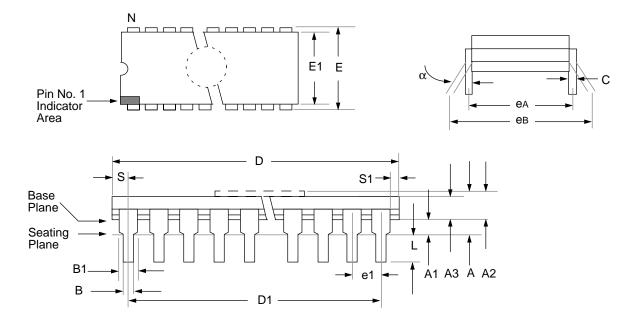

| Mounting Type              | Surface Mount                                                              |

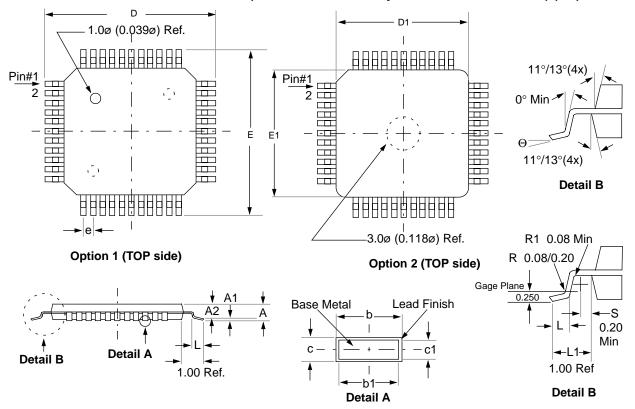

| Package / Case             | 44-QFP                                                                     |

| Supplier Device Package    | 44-MQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c74a-20e-pq |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXX uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture in which program and data are fetched from the same memory using the same bus. Separating program and data buses further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The table below lists program memory (EPROM) and data memory (RAM) for each PIC16C7X device.

| Device    | Program<br>Memory | Data Memory |

|-----------|-------------------|-------------|

| PIC16C72  | 2K x 14           | 128 x 8     |

| PIC16C73  | 4K x 14           | 192 x 8     |

| PIC16C73A | 4K x 14           | 192 x 8     |

| PIC16C74  | 4K x 14           | 192 x 8     |

| PIC16C74A | 4K x 14           | 192 x 8     |

| PIC16C76  | 8K x 14           | 368 x 8     |

| PIC16C77  | 8K x 14           | 386 x 8     |

The PIC16CXX can directly or indirectly address its register files or data memory. All special function registers, including the program counter, are mapped in the data memory. The PIC16CXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16CXX simple yet efficient. In addition, the learning curve is reduced significantly.

PIC16CXX devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between the data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow bit and a digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

NOTES:

# 5.0 I/O PORTS Applicable Devices 72 73 73A 74 74A 76 77

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

# 5.1 PORTA and TRISA Registers Applicable Devices 72 73 73A 74 74A 76 77

#### PORTA is a 6-bit latch.

The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as output or input.

Setting a TRISA register bit puts the corresponding output driver in a hi-impedance mode. Clearing a bit in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

Note: On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

# EXAMPLE 5-1: INITIALIZING PORTA

| BCF   | STATUS, | RP0 | ; |                       |

|-------|---------|-----|---|-----------------------|

| BCF   | STATUS, | RP1 | ; | PIC16C76/77 only      |

| CLRF  | PORTA   |     | ; | Initialize PORTA by   |

|       |         |     | ; | clearing output       |

|       |         |     | ; | data latches          |

| BSF   | STATUS, | RP0 | ; | Select Bank 1         |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISA   |     | ; | Set RA<3:0> as inputs |

|       |         |     | ; | RA<5:4> as outputs    |

|       |         |     | ; | TRISA<7:6> are always |

|       |         |     | ; | read as '0'.          |

|       |         |     |   |                       |

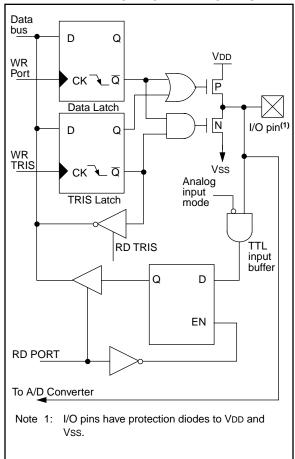

#### FIGURE 5-1: BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

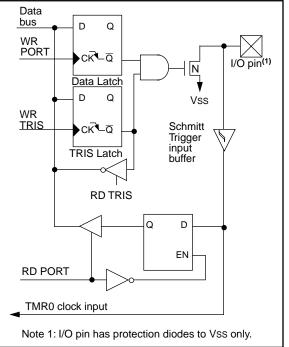

#### FIGURE 5-2: BLOCK DIAGRAM OF RA4/ T0CKI PIN

### TABLE 5-1: PORTA FUNCTIONS

| Name         | Bit# | Buffer | Function                                                                       |

|--------------|------|--------|--------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF                                           |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0                                |

|              |      |        | Output is open drain type                                                      |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input |

Legend: TTL = TTL input, ST = Schmitt Trigger input

# TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5     | Bit 4      | Bit 3 | Bit 2   | Bit 1   | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|--------|-------|-------|-----------|------------|-------|---------|---------|-------|--------------------------|---------------------------|

| 05h     | PORTA  | —     | _     | RA5       | RA4        | RA3   | RA2     | RA1     | RA0   | 0x 0000                  | 0u 0000                   |

| 85h     | TRISA  | —     | —     | PORTA Dat | a Directio | -     | 11 1111 | 11 1111 |       |                          |                           |

| 9Fh     | ADCON1 | —     |       | —         | _          | _     | PCFG2   | PCFG1   | PCFG0 | 000                      | 000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

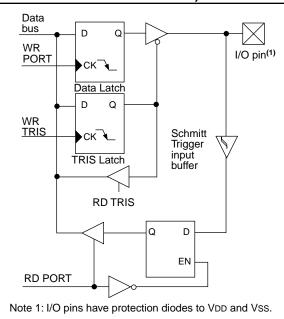

#### 5.4 PORTD and TRISD Registers

# Applicable Devices 72 73 73A 74 74A 76 77

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

PORTD can be configured as an 8-bit wide microprocessor port (parallel slave port) by setting control bit PSPMODE (TRISE<4>). In this mode, the input buffers are TTL.

# FIGURE 5-7: PORTD BLOCK DIAGRAM (IN I/O PORT MODE)

| Name     | Bit# | Buffer Type           | Function                                          |

|----------|------|-----------------------|---------------------------------------------------|

| RD0/PSP0 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit0 |

| RD1/PSP1 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit1 |

| RD2/PSP2 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit2 |

| RD3/PSP3 | bit3 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit3 |

| RD4/PSP4 | bit4 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit4 |

| RD5/PSP5 | bit5 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit5 |

| RD6/PSP6 | bit6 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit6 |

| RD7/PSP7 | bit7 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit7 |

#### TABLE 5-7:PORTD FUNCTIONS

Legend: ST = Schmitt Trigger input TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffer when in Parallel Slave Port Mode.

#### TABLE 5-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Address | Name  | Bit 7 | Bit 6  | Bit 5     | Bit 4     | Bit 3 | Value on:<br>POR,<br>BOR                                      | Value on all other resets |     |           |           |  |

|---------|-------|-------|--------|-----------|-----------|-------|---------------------------------------------------------------|---------------------------|-----|-----------|-----------|--|

| 08h     | PORTD | RD7   | RD6    | RD5       | RD4       | RD3   | RD2                                                           | RD1                       | RD0 | xxxx xxxx | uuuu uuuu |  |

| 88h     | TRISD | PORT  | D Data | 1111 1111 | 1111 1111 |       |                                                               |                           |     |           |           |  |

| 89h     | TRISE | IBF   | OBF    | IBOV      | PSPMODE   | —     | PORTE Data Direction Bits         0000 -111         0000 -111 |                           |     |           |           |  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTD.

|  | TABLE 10-5: | <b>REGISTERS ASSOCIATED WITH PWM AND TIMER2</b> |

|--|-------------|-------------------------------------------------|

|--|-------------|-------------------------------------------------|

| Address               | Name    | Bit 7                  | Bit 6          | Bit 5               | Bit 4               | Bit 3     | Bit 2  | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|-----------------------|---------|------------------------|----------------|---------------------|---------------------|-----------|--------|---------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                    | PEIE           | TOIE                | INTE                | RBIE      | TOIF   | INTF    | RBIF    | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1    | PSPIF <sup>(1,2)</sup> | ADIF           | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | SSPIF     | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000                | 0000 0000                       |

| 0Dh <sup>(2)</sup>    | PIR2    | —                      | _              | _                   |                     | _         | _      | _       | CCP2IF  | 0                        | 0                               |

| 8Ch                   | PIE1    | PSPIE <sup>(1,2)</sup> | ADIE           | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup> | SSPIE     | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000                | 0000 0000                       |

| 8Dh <sup>(2)</sup>    | PIE2    | —                      | _              | —                   | _                   | —         | —      | —       | CCP2IE  | 0                        | 0                               |

| 87h                   | TRISC   | PORTC Da               | ata Directio   | n Register          |                     |           |        |         |         | 1111 1111                | 1111 1111                       |

| 11h                   | TMR2    | Timer2 mod             | dule's registe | ər                  |                     |           |        |         |         | 0000 0000                | 0000 0000                       |

| 92h                   | PR2     | Timer2 mod             | dule's perioc  | l register          |                     |           |        |         |         | 1111 1111                | 1111 1111                       |

| 12h                   | T2CON   | —                      | TOUTPS3        | TOUTPS2             | TOUTPS1             | TOUTPS0   | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000                | -000 0000                       |

| 15h                   | CCPR1L  | Capture/Co             | mpare/PWN      | / register1 (       | LSB)                |           |        |         |         | xxxx xxxx                | uuuu uuuu                       |

| 16h                   | CCPR1H  | Capture/Co             | mpare/PWN      | / register1 (       | (MSB)               |           |        |         |         | xxxx xxxx                | uuuu uuuu                       |

| 17h                   | CCP1CON | —                      | —              | CCP1X               | CCP1Y               | CCP1M3    | CCP1M2 | CCP1M1  | CCP1M0  | 00 0000                  | 00 0000                         |

| 1Bh <b>(2)</b>        | CCPR2L  | Capture/Co             | mpare/PWN      |                     | xxxx xxxx           | uuuu uuuu |        |         |         |                          |                                 |

| 1Ch <sup>(2)</sup>    | CCPR2H  | Capture/Co             | mpare/PWN      |                     | xxxx xxxx           | uuuu uuuu |        |         |         |                          |                                 |

| 1Dh <sup>(2)</sup>    | CCP2CON | —                      | —              | CCP2X               | CCP2Y               | CCP2M3    | CCP2M2 | CCP2M1  | CCP2M0  | 00 0000                  | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PWM and Timer2.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

2: The PIC16C72 does not have a Parallel Slave Port, USART or CCP2 module, these bits are unimplemented, read as '0'.

٦

# FIGURE 11-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)

| R/W-0    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0                                                                   | R/W-0                                                                            | R/W-0                                                                        | R/W-0                                    | R/W-0        | R/W-0                        |                                                   |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------|--------------|------------------------------|---------------------------------------------------|--|--|--|--|

| WCOL     | SSPOV                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SSPEN                                                                   | CKP                                                                              | SSPM3                                                                        | SSPM2                                    | SSPM1        | SSPM0                        | R = Readable bit                                  |  |  |  |  |

| bit7     | bit0 W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset                                                                                                                                                                                                                                                                                                                                                                              |                                                                         |                                                                                  |                                                                              |                                          |              |                              |                                                   |  |  |  |  |

| bit 7:   | WCOL: W                                                                                                                                                                                                                                                                                                                                                                                                                                                                | rite Collisio                                                           | n Detect l                                                                       | oit                                                                          |                                          |              |                              |                                                   |  |  |  |  |

|          | 1 = The S                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SPBUF reg                                                               | jister is wr                                                                     |                                                                              | it is still tr                           | ansmitting   | the previou                  | us word                                           |  |  |  |  |

| bit 6:   | SSPOV: Receive Overflow Detect bit                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                         |                                                                                  |                                                                              |                                          |              |                              |                                                   |  |  |  |  |

|          | $\frac{\text{In SPI mode}}{1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR register is lost. Overflow can only occur in slave mode. The user must read the SSP-BUF, even if only transmitting data, to avoid setting overflow. In master mode the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPBUF register. 0 = No overflow$ |                                                                         |                                                                                  |                                                                              |                                          |              |                              |                                                   |  |  |  |  |

|          | In I <sup>2</sup> C mod                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u>de</u>                                                               |                                                                                  |                                                                              |                                          |              |                              |                                                   |  |  |  |  |

|          | 1 = A byte<br>in transmit<br>0 = No ove                                                                                                                                                                                                                                                                                                                                                                                                                                | mode. SS                                                                |                                                                                  |                                                                              |                                          |              |                              | us byte. SSPOV is a "don't care                   |  |  |  |  |

| bit 5:   | SSPEN: S                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ynchronou                                                               | s Serial P                                                                       | ort Enable                                                                   | bit                                      |              |                              |                                                   |  |  |  |  |

|          | In SPI mode<br>1 = Enables serial port and configures SCK, SDO, and SDI as serial port pins<br>0 = Disables serial port and configures these pins as I/O port pins                                                                                                                                                                                                                                                                                                     |                                                                         |                                                                                  |                                                                              |                                          |              |                              |                                                   |  |  |  |  |

|          | 0 = Disabl                                                                                                                                                                                                                                                                                                                                                                                                                                                             | es the seria                                                            | ort and co                                                                       | nfigures th                                                                  | nese pins a                              | as I/O port  | pins                         | ial port pins<br>s input or output.               |  |  |  |  |

| bit 4:   | CKP: Cloc                                                                                                                                                                                                                                                                                                                                                                                                                                                              | k Polarity                                                              | Select bit                                                                       |                                                                              |                                          |              |                              |                                                   |  |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ate for cloc                                                            |                                                                                  |                                                                              |                                          |              |                              | receive on rising edge.<br>ceive on falling edge. |  |  |  |  |

|          | $\frac{\ln l^2 C \mod SCK \text{ relea}}{1 = \text{Enable}}$                                                                                                                                                                                                                                                                                                                                                                                                           | se control<br>e clock                                                   | -11                                                                              |                                                                              | 4                                        |              | . (: )                       |                                                   |  |  |  |  |

|          | 0 = Holds                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                         |                                                                                  | , ,                                                                          |                                          |              | o time)                      |                                                   |  |  |  |  |

| bit 3-0: | 0001 = SF<br>0010 = SF<br>0011 = SF<br>0100 = SF<br>0101 = SF                                                                                                                                                                                                                                                                                                                                                                                                          | PI master n<br>PI master n<br>PI master n<br>PI master n<br>PI slave mo | node, cloc<br>node, cloc<br>node, cloc<br>node, cloc<br>ode, clock<br>ode, clock | k = Fosc/4<br>k = Fosc/1<br>k = Fosc/6<br>k = TMR2<br>= SCK pir<br>= SCK pir | l<br>6<br>64<br>output/2<br>1. SS pin co | ontrol enal  |                              | n be used as I/O pin.                             |  |  |  |  |

|          | $0111 = I^{2}(0)$<br>$1011 = I^{2}(0)$<br>$1110 = I^{2}(0)$                                                                                                                                                                                                                                                                                                                                                                                                            | C slave mo<br>C firmware<br>C slave mo                                  | de, 10-bit<br>controlled<br>de, 7-bit a                                          | address<br>I Master M<br>ddress wi                                           | th start an                              | d stop bit i | nterrupts er<br>interrupts o |                                                   |  |  |  |  |

Г

Г

# FIGURE 11-8: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)(PIC16C76/77)

| R/W-0<br>WCOL | R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         SSPOV       SSPEN       CKP       SSPM3       SSPM2       SSPM1       SSPM0       R = Readable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| bit7          | bit0<br>bit0<br>bit0<br>bit0<br>bit0<br>bit0<br>bit0<br>bit0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| bit 7:        | <ul> <li>WCOL: Write Collision Detect bit</li> <li>1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)</li> <li>0 = No collision</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| bit 6:        | SSPOV: Receive Overflow Indicator bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

|               | In SPI mode<br>1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow,<br>the data in SSPSR is lost. Overflow can only occur in slave mode. The user must read the SSPBUF, even<br>if only transmitting data, to avoid setting overflow. In master mode the overflow bit is not set since each<br>new reception (and transmission) is initiated by writing to the SSPBUF register.<br>0 = No overflow                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

|               | <u>In I<sup>2</sup>C mode</u><br>1 = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't call in transmit mode. SSPOV must be cleared in software in either mode.<br>0 = No overflow                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| bit 5:        | SSPEN: Synchronous Serial Port Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

|               | In SPI mode         1 = Enables serial port and configures SCK, SDO, and SDI as serial port pins         0 = Disables serial port and configures these pins as I/O port pins         In I <sup>2</sup> C mode         1 = Enables the serial port and configures the SDA and SCL pins as serial port pins         0 = Disables serial port and configures these pins as I/O port pins         In both modes, when enabled, these pins must be properly configured as input or output.                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| bit 4:        | <b>CKP</b> : Clock Polarity Select bit<br>In SPI mode<br>1 = Idle state for clock is a high level<br>0 = Idle state for clock is a low level<br>In $I^2C$ mode<br>SCK release control<br>1 = Enable clock<br>0 = Holds clock low (clock stretch) (Used to ensure data setup time)                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| bit 3-0:      | <b>SSPM3:SSPM0</b> : Synchronous Serial Port Mode Select bits<br>0000 = SPI master mode, clock = Fosc/4<br>0011 = SPI master mode, clock = Fosc/64<br>0011 = SPI master mode, clock = TMR2 output/2<br>$0100 = SPI$ slave mode, clock = SCK pin. $\overline{SS}$ pin control enabled.<br>$0101 = SPI$ slave mode, clock = SCK pin. $\overline{SS}$ pin control disabled. $\overline{SS}$ can be used as I/O pin<br>$0110 = I^2C$ slave mode, 7-bit address<br>$1011 = I^2C$ slave mode, 10-bit address<br>$1011 = I^2C$ slave mode, 7-bit address with start and stop bit interrupts enabled<br>$1111 = I^2C$ slave mode, 10-bit address with start and stop bit interrupts enabled |  |  |  |  |  |  |  |  |  |

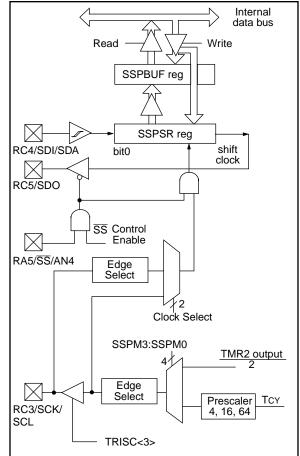

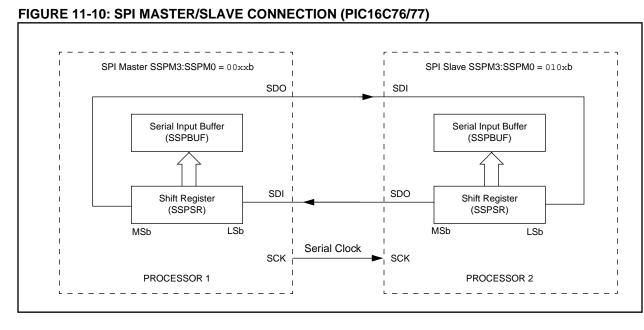

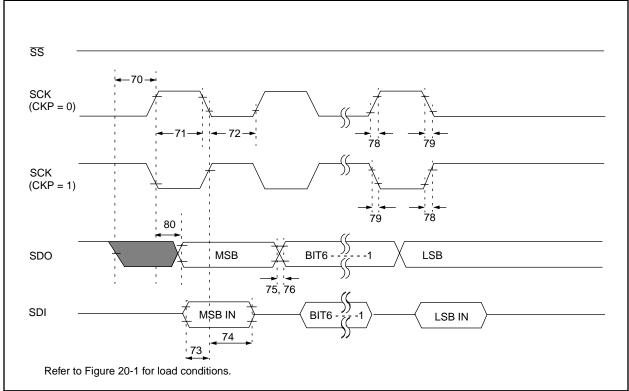

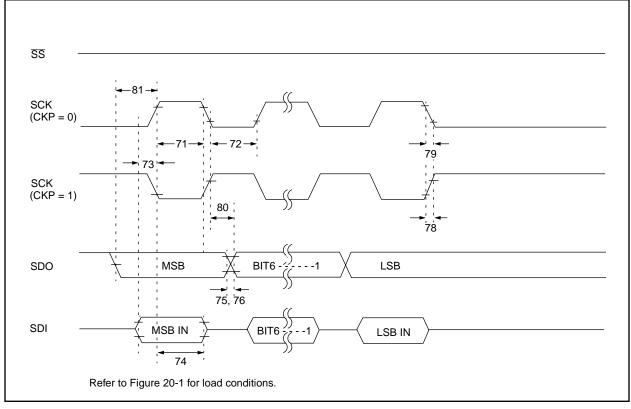

#### 11.3.1 SPI MODE FOR PIC16C76/77

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally a fourth pin may be used when in a slave mode of operation:

Slave Select (SS) RA5/SS/AN4

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master Mode (SCK is the clock output)

- Slave Mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select Mode (Slave mode only)

The SSP consists of a transmit/receive Shift Register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the 8-bits of data have been received, that byte is moved to the SSPBUF register. Then the buffer full detect bit BF (SSPSTAT<0>) and interrupt flag bit SSPIF (PIR1<3>) are set. This double buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored, and the write collision detect bit WCOL (SSPCON<7>) will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully. When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer full bit BF (SSPSTAT<0>) indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, bit BF is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally the SSP Interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 11-2 shows the loading of the SSPBUF (SSPSR) for data transmission. The shaded instruction is only required if the received data is meaningful.

#### EXAMPLE 11-2: LOADING THE SSPBUF (SSPSR) REGISTER (PIC16C76/77)

| LOOP | BCF<br>BSF<br>BTFSS | STATUS ,<br>STATUS ,<br>SSPSTAT , | RP0 | ;Specify Bank 1<br>;<br>;Has data been              |

|------|---------------------|-----------------------------------|-----|-----------------------------------------------------|

|      | GOTO                | LOOP                              |     | <pre>;received ;(transmit ;complete)? ;No</pre>     |

|      | BCF<br>MOVF         | STATUS ,<br>SSPBUF ,              |     | ;Specify Bank 0<br>;W reg = contents<br>; of SSPBUF |

|      | MOVWF               | RXDATA                            |     | ;Save in user RAM                                   |

|      |                     | TXDATA,                           | W   | ;W reg = contents<br>; of TXDATA                    |

|      | MOVWF               | SSPBUF                            |     | ;New data to xmit                                   |

The block diagram of the SSP module, when in SPI mode (Figure 11-9), shows that the SSPSR is not directly readable or writable, and can only be accessed from addressing the SSPBUF register. Additionally, the SSP status register (SSPSTAT) indicates the various status conditions.

#### FIGURE 11-9: SSP BLOCK DIAGRAM (SPI MODE)(PIC16C76/77)

To enable the serial port, SSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON register, and then set bit SSPEN. This configures the SDI, SDO, SCK, and SS pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRISC register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value. An example would be in master mode where you are only sending data (to a display driver), then both SDI and SS could be used as general purpose outputs by clearing their corresponding TRIS register bits.

Figure 11-10 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge, and latched on the opposite edge of the clock. Both processors should be programmed to same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application firmware. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- Master sends dummy data Slave sends data

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2) is to broadcast data by the firmware protocol.

In master mode the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SCK output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "line activity monitor" mode.

In slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched the interrupt flag bit SSPIF (PIR1<3>) is set.

The clock polarity is selected by appropriately programming bit CKP (SSPCON<4>). This then would give waveforms for SPI communication as shown in Figure 11-11, Figure 11-12, and Figure 11-13 where the MSB is transmitted first. In master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

This allows a maximum bit clock frequency (at 20 MHz) of 5 MHz. When in slave mode the external clock must meet the minimum high and low times.

In sleep mode, the slave can transmit and receive data and wake the device from sleep.

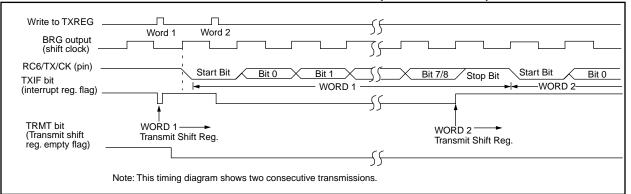

Steps to follow when setting up an Asynchronous Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH. (Section 12.1)

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

# FIGURE 12-8: ASYNCHRONOUS MASTER TRANSMISSION

# FIGURE 12-9: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

# TABLE 12-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address | Name  | Bit 7                              | Bit 6                   | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|------------------------------------|-------------------------|-------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup>               | ADIF                    | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h     | RCSTA | SPEN                               | RX9                     | SREN  | CREN  | —     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 19h     | TXREG | USART Trar                         | JSART Transmit Register |       |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup>               | ADIE                    | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h     | TXSTA | CSRC                               | TX9                     | TXEN  | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h     | SPBRG | SPBRG Baud Rate Generator Register |                         |       |       |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

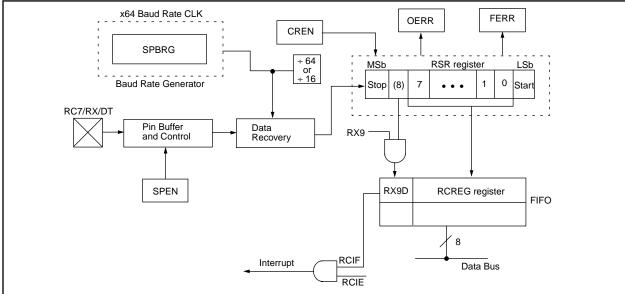

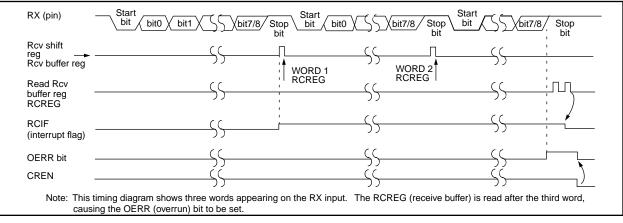

#### 12.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 12-10. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the receive (serial) shift register (RSR). After sampling the STOP bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a

#### FIGURE 12-10: USART RECEIVE BLOCK DIAGRAM

double buffered register, i.e. it is a two deep FIFO. It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte begin shifting to the RSR register. On the detection of the STOP bit of the third byte, if the RCREG register is still full then overrun error bit OERR (RCSTA<1>) will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited, so it is essential to clear error bit OERR if it is set. Framing error bit FERR (RCSTA<2>) is set if a stop bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG, will load bits RX9D and FERR with new values, therefore it is essential for the user to read the RCSTA register before reading RCREG register in order not to lose the old FERR and RX9D information.

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH. (Section 12.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC, and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

# TABLE 12-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address | Name  | Bit 7                             | Bit 6                  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1     | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|-----------------------------------|------------------------|-------|-------|-------|--------|-----------|-----------|--------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup>              | ADIF                   | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF    | TMR1IF    | 0000 0000                | 0000 0000                       |

| 18h     | RCSTA | SPEN                              | RX9                    | SREN  | CREN  |       | FERR   | OERR      | RX9D      | 0000 -00x                | 0000 -00x                       |

| 1Ah     | RCREG | USART Rec                         | JSART Receive Register |       |       |       |        |           |           | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup>              | ADIE                   | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE    | TMR1IE    | 0000 0000                | 0000 0000                       |

| 98h     | TXSTA | CSRC                              | TX9                    | TXEN  | SYNC  | _     | BRGH   | TRMT      | TX9D      | 0000 -010                | 0000 -010                       |

| 99h     | SPBRG | PBRG Baud Rate Generator Register |                        |       |       |       |        | 0000 0000 | 0000 0000 |                          |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

| SUBWF             | Subtract                                                                                                                                                                        | W from f                   |                             |                      |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------|----------------------|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                       | SUBWF                      | f,d                         |                      |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$                                                                                                                | 7                          |                             |                      |  |  |  |

| Operation:        | (f) - (W) –                                                                                                                                                                     | → (destina                 | tion)                       |                      |  |  |  |

| Status Affected:  | C, DC, Z                                                                                                                                                                        |                            |                             |                      |  |  |  |

| Encoding:         | 00                                                                                                                                                                              | 0010                       | dfff                        | ffff                 |  |  |  |

| Description:      | Subtract (2's complement method) W re<br>ister from register 'f'. If 'd' is 0 the result<br>stored in the W register. If 'd' is 1 the<br>result is stored back in register 'f'. |                            |                             |                      |  |  |  |

| Words:            | 1                                                                                                                                                                               |                            |                             |                      |  |  |  |

| Cycles:           | 1                                                                                                                                                                               |                            |                             |                      |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                              | Q2                         | Q3                          | Q4                   |  |  |  |

|                   | Decode                                                                                                                                                                          | Read<br>register 'f'       | Process<br>data             | Write to destination |  |  |  |

| Example 1:        | SUBWF<br>Before Ins<br>REG1                                                                                                                                                     | REG1 , 1<br>struction<br>= | 3                           |                      |  |  |  |

|                   | W                                                                                                                                                                               | =                          | 2                           |                      |  |  |  |

|                   | C<br>Z                                                                                                                                                                          | =                          | ?<br>?                      |                      |  |  |  |

|                   | After Instruction                                                                                                                                                               |                            |                             |                      |  |  |  |

|                   | REG1<br>W<br>C<br>7                                                                                                                                                             | =<br>=<br>=                | 1<br>2<br>1; result is<br>0 | positive             |  |  |  |

| Example 2:        | Before Ins                                                                                                                                                                      | struction                  | C C                         |                      |  |  |  |

|                   | REG1 = 2<br>W = 2<br>C = ?<br>Z = ?                                                                                                                                             |                            | 2<br>?                      |                      |  |  |  |

|                   | After Instr                                                                                                                                                                     |                            |                             |                      |  |  |  |

|                   | W<br>C                                                                                                                                                                          | =<br>=<br>=                | 0<br>2<br>1; result is      | zero                 |  |  |  |

| Example 3:        | Z<br>Before Ins                                                                                                                                                                 | =<br>struction             | 1                           |                      |  |  |  |

| Example 0.        | REG1                                                                                                                                                                            | =                          | 1                           |                      |  |  |  |

|                   | W                                                                                                                                                                               | =                          | 2                           |                      |  |  |  |

|                   | C                                                                                                                                                                               | =                          | ?                           |                      |  |  |  |

|                   | Z<br>After Instr                                                                                                                                                                | =<br>uction                | ?                           |                      |  |  |  |

|                   | REG1                                                                                                                                                                            | =                          | 0xFF                        |                      |  |  |  |

|                   | W                                                                                                                                                                               | =                          | 2                           |                      |  |  |  |

|                   | C<br>Z                                                                                                                                                                          | =<br>=                     | 0; result is<br>0           | negative             |  |  |  |

| SWAPF             | Swap Ni                                                                                                                                                                          | bbles in                                                                                | f               |                      |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------|----------------------|--|--|--|

| Syntax:           | [label]                                                                                                                                                                          | SWAPF                                                                                   | i,d             |                      |  |  |  |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$                                                                                                                                                   | 27                                                                                      |                 |                      |  |  |  |

| Operation:        | ,                                                                                                                                                                                | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$ |                 |                      |  |  |  |

| Status Affected:  | None                                                                                                                                                                             |                                                                                         |                 |                      |  |  |  |

| Encoding:         | 00                                                                                                                                                                               | 1110                                                                                    | dfff            | ffff                 |  |  |  |

| Description:      | Description: The upper and lower nibbles of registe<br>'f' are exchanged. If 'd' is 0 the result is<br>placed in W register. If 'd' is 1 the resul<br>is placed in register 'f'. |                                                                                         |                 |                      |  |  |  |

| Words:            | 1                                                                                                                                                                                |                                                                                         |                 |                      |  |  |  |

| Cycles:           | 1                                                                                                                                                                                |                                                                                         |                 |                      |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                               | Q2                                                                                      | Q3              | Q4                   |  |  |  |

|                   | Decode                                                                                                                                                                           | Read<br>register 'f'                                                                    | Process<br>data | Write to destination |  |  |  |

| Example           | SWAPF                                                                                                                                                                            | REG,                                                                                    | 0               |                      |  |  |  |

|                   | Before In                                                                                                                                                                        | struction                                                                               |                 |                      |  |  |  |

|                   |                                                                                                                                                                                  | REG1                                                                                    | = 0x            | :A5                  |  |  |  |

|                   | After Inst                                                                                                                                                                       | ruction                                                                                 |                 |                      |  |  |  |

|                   |                                                                                                                                                                                  | REG1<br>W                                                                               | •••             | :A5<br>:5A           |  |  |  |

| TRIS             | Load TRIS Register                                                                                                                                                                  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] TRIS f                                                                                                                                                             |

| Operands:        | $5 \le f \le 7$                                                                                                                                                                     |

| Operation:       | (W) $\rightarrow$ TRIS register f;                                                                                                                                                  |

| Status Affected: | None                                                                                                                                                                                |

| Encoding:        | 00 0000 0110 0fff                                                                                                                                                                   |

| Description:     | The instruction is supported for code<br>compatibility with the PIC16C5X prod-<br>ucts. Since TRIS registers are read-<br>able and writable, the user can directly<br>address them. |

| Words:           | 1                                                                                                                                                                                   |

| Cycles:          | 1                                                                                                                                                                                   |

| Example          |                                                                                                                                                                                     |

|                  | To maintain upward compatibility<br>with future PIC16CXX products, do<br>not use this instruction.                                                                                  |

|                  |                                                                                                                                                                                     |

MPASM has the following features to assist in developing software for specific use applications.

- Provides translation of Assembler source code to object code for all Microchip microcontrollers.

- Macro assembly capability.

- Produces all the files (Object, Listing, Symbol, and special) required for symbolic debug with Microchip's emulator systems.

- Supports Hex (default), Decimal and Octal source and listing formats.

MPASM provides a rich directive language to support programming of the PIC16/17. Directives are helpful in making the development of your assemble source code shorter and more maintainable.

# 16.11 Software Simulator (MPLAB-SIM)

The MPLAB-SIM Software Simulator allows code development in a PC host environment. It allows the user to simulate the PIC16/17 series microcontrollers on an instruction level. On any given instruction, the user may examine or modify any of the data areas or provide external stimulus to any of the pins. The input/ output radix can be set by the user and the execution can be performed in; single step, execute until break, or in a trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C and MPASM. The Software Simulator offers the low cost flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

# 16.12 <u>C Compiler (MPLAB-C)</u>

The MPLAB-C Code Development System is a complete 'C' compiler and integrated development environment for Microchip's PIC16/17 family of micro-controllers. The compiler provides powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compiler provides symbol information that is compatible with the MPLAB IDE memory display (PICMASTER emulator software versions 1.13 and later).

#### 16.13 <u>Fuzzy Logic Development System</u> (fuzzyTECH-MP)

*fuzzy*TECH-MP fuzzy logic development tool is available in two versions - a low cost introductory version, MP Explorer, for designers to gain a comprehensive working knowledge of fuzzy logic system design; and a full-featured version, *fuzzy*TECH-MP, edition for implementing more complex systems.

Both versions include Microchip's *fuzzy*LAB<sup>™</sup> demonstration board for hands-on experience with fuzzy logic systems implementation.

# 16.14 <u>MP-DriveWay™ – Application Code</u> <u>Generator</u>

MP-DriveWay is an easy-to-use Windows-based Application Code Generator. With MP-DriveWay you can visually configure all the peripherals in a PIC16/17 device and, with a click of the mouse, generate all the initialization and many functional code modules in C language. The output is fully compatible with Microchip's MPLAB-C C compiler. The code produced is highly modular and allows easy integration of your own code. MP-DriveWay is intelligent enough to maintain your code through subsequent code generation.

# 16.15 <u>SEEVAL<sup>®</sup> Evaluation and</u> <u>Programming System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

# 16.16 <u>TrueGauge<sup>®</sup> Intelligent Battery</u> <u>Management</u>

The TrueGauge development tool supports system development with the MTA11200B TrueGauge Intelligent Battery Management IC. System design verification can be accomplished before hardware prototypes are built. User interface is graphically-oriented and measured data can be saved in a file for exporting to Microsoft Excel.

# 16.17 <u>KEELOQ<sup>®</sup> Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

Applicable Devices

72

73

73A

74

76

77

# 20.5 <u>Timing Diagrams and Specifications</u>

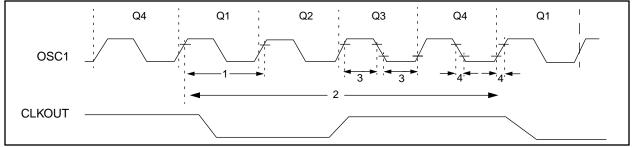

# FIGURE 20-2: EXTERNAL CLOCK TIMING

# TABLE 20-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                   | Min | Тур† | Мах    | Units | Conditions                             |