Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | A/D 8x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LCC (J-Lead)                                                           |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c74a-20i-l |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0 General Description                                              | 5     |

|----------------------------------------------------------------------|-------|

| 2.0 PIC16C7X Device Varieties                                        | 7     |

| 3.0 Architectural Overview                                           | 9     |

| 4.0 Memory Organization                                              | 19    |

| 5.0 I/O Ports                                                        | 43    |

| 6.0 Overview of Timer Modules                                        | 57    |

| 7.0 Timer0 Module                                                    | 59    |

| 8.0 Timer1 Module                                                    | 65    |

| 9.0 Timer2 Module                                                    | 69    |

| 10.0 Capture/Compare/PWM Module(s)                                   |       |

| 11.0 Synchronous Serial Port (SSP) Module                            |       |

| 12.0 Universal Synchronous Asynchronous Receiver Transmitter (USART) | 99    |

| 13.0 Analog-to-Digital Converter (A/D) Module                        | . 117 |

| 14.0 Special Features of the CPU                                     |       |

| 15.0 Instruction Set Summary                                         | . 147 |

| 16.0 Development Support                                             |       |

| 17.0 Electrical Characteristics for PIC16C72                         |       |

| 18.0 Electrical Characteristics for PIC16C73/74                      |       |

| 19.0 Electrical Characteristics for PIC16C73A/74A                    |       |

| 20.0 Electrical Characteristics for PIC16C76/77                      | . 219 |

| 21.0 DC and AC Characteristics Graphs and Tables                     |       |

| 22.0 Packaging Information                                           | . 251 |

| Appendix A:                                                          |       |

| Appendix B: Compatibility                                            | . 263 |

| Appendix C: What's New                                               | . 264 |

| Appendix D: What's Changed                                           |       |

| Appendix E: PIC16/17 Microcontrollers                                | . 265 |

| Pin Compatibility                                                    |       |

| Index                                                                | . 273 |

| List of Examples                                                     | . 279 |

| List of Figures                                                      |       |

| List of Tables                                                       |       |

| Reader Response                                                      |       |

| PIC16C7X Product Identification System                               | . 287 |

For register and module descriptions in this data sheet, device legends show which devices apply to those sections. As an example, the legend below would mean that the following section applies only to the PIC16C72, PIC16C73A and PIC16C74A devices.

## Applicable Devices 72 73 73A 74 74A 76 77

12|13|13A|14|14A|16|11

## To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent an exceptional amount of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

|            |                                                 | PIC16C710                           | PIC16C71            | PIC16C711                           | PIC16C715                           | PIC16C72                   | PIC16CR72 <sup>(1)</sup>   |  |  |  |

|------------|-------------------------------------------------|-------------------------------------|---------------------|-------------------------------------|-------------------------------------|----------------------------|----------------------------|--|--|--|

| Clock      | Maximum Frequency<br>of Operation (MHz)         | 20                                  | 20                  | 20                                  | 20                                  | 20                         | 20                         |  |  |  |

|            | EPROM Program Memory<br>(x14 words)             | 512                                 | 1K                  | 1K                                  | 2К                                  | 2К                         | —                          |  |  |  |

| lemory     | ROM Program Memory<br>(14K words)               | _                                   | _                   | _                                   | _                                   | _                          | 2К                         |  |  |  |

|            | Data Memory (bytes)                             | 36                                  | 36                  | 68                                  | 128                                 | 128                        | 128                        |  |  |  |

|            | Timer Module(s)                                 | TMR0                                | TMR0                | TMR0                                | TMR0                                | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2     |  |  |  |

| eripherals | Capture/Compare/<br>PWM Module(s)               | —                                   | _                   | —                                   | —                                   | 1                          | 1                          |  |  |  |

|            | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | _                                   | _                   | —                                   | —                                   | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C       |  |  |  |

|            | Parallel Slave Port                             | _                                   | —                   | —                                   | _                                   | _                          | —                          |  |  |  |

|            | A/D Converter (8-bit) Channels                  | 4                                   | 4                   | 4                                   | 4                                   | 5                          | 5                          |  |  |  |

|            | Interrupt Sources                               | 4                                   | 4                   | 4                                   | 4                                   | 8                          | 8                          |  |  |  |

|            | I/O Pins                                        | 13                                  | 13                  | 13                                  | 13                                  | 22                         | 22                         |  |  |  |

|            | Voltage Range (Volts)                           | 3.0-6.0                             | 3.0-6.0             | 3.0-6.0                             | 3.0-5.5                             | 2.5-6.0                    | 3.0-5.5                    |  |  |  |

| atures     | In-Circuit Serial Programming                   | Yes                                 | Yes                 | Yes                                 | Yes                                 | Yes                        | Yes                        |  |  |  |

|            | Brown-out Reset                                 | Yes                                 | —                   | Yes                                 | Yes                                 | Yes                        | Yes                        |  |  |  |

|            | Packages                                        | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC, SSOP |  |  |  |

## TABLE 1-1: PIC16C7XX FAMILY OF DEVCES

|             |                                                   | PIC16C73A                   | PIC16C74A                                 | PIC16C76                    | PIC16C77                                  |

|-------------|---------------------------------------------------|-----------------------------|-------------------------------------------|-----------------------------|-------------------------------------------|

| Clock       | Maximum Frequency of Oper-<br>ation (MHz)         | 20                          | 20                                        | 20                          | 20                                        |

| Memory      | EPROM Program Memory<br>(x14 words)               | 4K                          | 4K                                        | 8K                          | 8K                                        |

|             | Data Memory (bytes)                               | 192                         | 192                                       | 368                         | 368                                       |

|             | Timer Module(s)                                   | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    |

| Peripherals | Capture/Compare/PWM Mod-<br>ule(s)                | 2                           | 2                                         | 2                           | 2                                         |

|             | Serial Port(s) (SPI/I <sup>2</sup> C, US-<br>ART) | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               |

|             | Parallel Slave Port                               | —                           | Yes                                       | —                           | Yes                                       |

|             | A/D Converter (8-bit) Channels                    | 5                           | 8                                         | 5                           | 8                                         |

|             | Interrupt Sources                                 | 11                          | 12                                        | 11                          | 12                                        |

|             | I/O Pins                                          | 22                          | 33                                        | 22                          | 33                                        |

|             | Voltage Range (Volts)                             | 2.5-6.0                     | 2.5-6.0                                   | 2.5-6.0                     | 2.5-6.0                                   |

| eatures     | In-Circuit Serial Programming                     | Yes                         | Yes                                       | Yes                         | Yes                                       |

|             | Brown-out Reset                                   | Yes                         | Yes                                       | Yes                         | Yes                                       |

|             | Packages                                          | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C7XX Family devices use serial programming with clock pin RB6 and data pin RB7.

Note 1: Please contact your local Microchip sales office for availability of these devices.

NOTES:

## FIGURE 10-1: CCP1CON REGISTER (ADDRESS 17h)/CCP2CON REGISTER (ADDRESS 1Dh)

| U-0      | U-0                                                                                                                                                                                                                               | R/W-0                                                                                             | R/W-0                                                                                                                                                                 | R/W-0                                                                                                                              | R/W-0                                                                                            | R/W-0                                                       | R/W-0                                   |                                                                                      |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------|--|--|--|

|          | —                                                                                                                                                                                                                                 | CCPxX                                                                                             | CCPxY                                                                                                                                                                 | CCPxM3                                                                                                                             | CCPxM2                                                                                           | CCPxM1                                                      | CCPxM0                                  | R = Readable bit                                                                     |  |  |  |

| bit7     |                                                                                                                                                                                                                                   |                                                                                                   |                                                                                                                                                                       |                                                                                                                                    |                                                                                                  |                                                             | bit0                                    | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset |  |  |  |

| bit 7-6: | Unim                                                                                                                                                                                                                              | plemente                                                                                          | d: Read a                                                                                                                                                             | s '0'                                                                                                                              |                                                                                                  |                                                             |                                         |                                                                                      |  |  |  |

| bit 5-4: | <ul> <li>CCPxX:CCPxY: PWM Least Significant bits</li> <li>Capture Mode: Unused</li> <li>Compare Mode: Unused</li> <li>PWM Mode: These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.</li> </ul> |                                                                                                   |                                                                                                                                                                       |                                                                                                                                    |                                                                                                  |                                                             |                                         |                                                                                      |  |  |  |

| bit 3-0: | 0000<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001<br>1010<br>1011                                                                                                                                                              | = Capture<br>= Capture<br>= Capture<br>= Capture<br>= Capture<br>= Compai<br>= Compai<br>= Compai | A/Compare<br>e mode, ev<br>e mode, ev<br>e mode, ev<br>e mode, ev<br>re mode, ev<br>re mode, ev<br>re mode, g<br>re mode, t<br>re mode, t<br>re mode, t<br>re mode, t | very falling e<br>very rising e<br>very 4th risin<br>very 16th ris<br>set output o<br>clear output<br>generate sof<br>rigger speci | resets CCP:<br>edge<br>dge<br>ng edge<br>ning edge<br>n match (CC<br>on match (C<br>tware intern | CPxIF bit is<br>CCPxIF bit i<br>upt on matc<br>CPxIF bit is | is set)<br>h (CCPxIF bi<br>set; CCP1 re | it is set, CCPx pin is unaffected)<br>sets TMR1; CCP2 resets TMR1                    |  |  |  |

## 10.1 <u>Capture Mode</u>

Applicable Devices

72 73 73A 74 74A 76 77

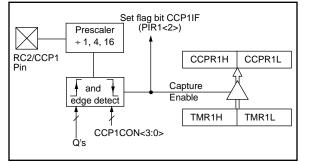

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as:

- · Every falling edge

- · Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

### 10.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 is configured as an out-     |

|-------|----------------------------------------------|

|       | put, a write to the port can cause a capture |

|       | condition.                                   |

### FIGURE 10-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

### 10.1.2 TIMER1 MODE SELECTION

Timer1 must be running in timer mode or synchronized counter mode for the CCP module to use the capture feature. In asynchronous counter mode, the capture operation may not work.

#### 10.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in operating mode.

## 12.2 USART Asynchronous Mode

| Ap | Applicable Devices |     |    |     |    |    |  |  |  |  |

|----|--------------------|-----|----|-----|----|----|--|--|--|--|

| 72 | 73                 | 73A | 74 | 74A | 76 | 77 |  |  |  |  |

In this mode, the USART uses standard nonreturn-tozero (NRZ) format (one start bit, eight or nine data bits and one stop bit). The most common data format is 8-bits. An on-chip dedicated 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The USART's transmitter and receiver are functionally independent but use the same data format and baud rate. The baud rate generator produces a clock either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- · Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

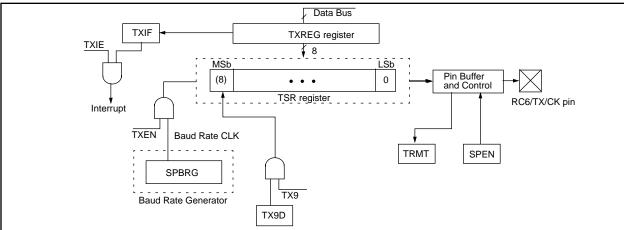

#### 12.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 12-7. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG register is empty and

flag bit TXIF (PIR1<4>) is set. This interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicated the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

| Note 1: | The TSR register is not mapped in data memory so it is not available to the user. |

|---------|-----------------------------------------------------------------------------------|

| Note 2: | Flag bit TXIF is set when enable bit TXEN is set.                                 |

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 12-7). The transmission can also be started by first loading the TXREG register and then setting enable bit TXEN. Normally when transmission is first started, the TSR register is empty, so a transfer to the TXREG register will result in an immediate transfer to TSR resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 12-9). Clearing enable bit TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result the RC6/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG register can result in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a case, an incorrect ninth data bit maybe loaded in the TSR register.

### FIGURE 12-7: USART TRANSMIT BLOCK DIAGRAM

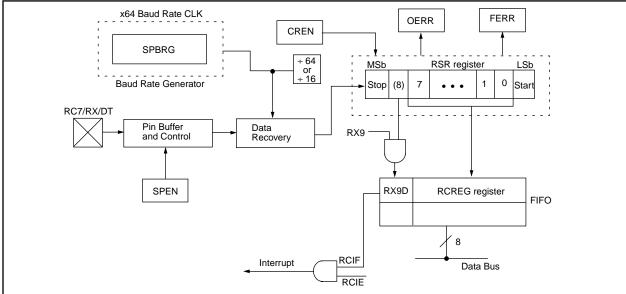

#### 12.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 12-10. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

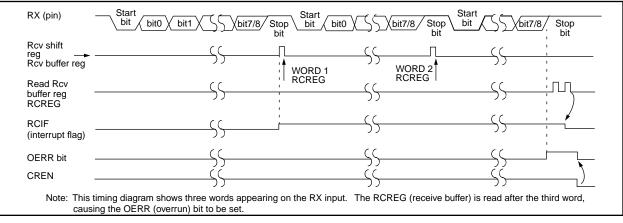

The heart of the receiver is the receive (serial) shift register (RSR). After sampling the STOP bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a

#### FIGURE 12-10: USART RECEIVE BLOCK DIAGRAM

double buffered register, i.e. it is a two deep FIFO. It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte begin shifting to the RSR register. On the detection of the STOP bit of the third byte, if the RCREG register is still full then overrun error bit OERR (RCSTA<1>) will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited, so it is essential to clear error bit OERR if it is set. Framing error bit FERR (RCSTA<2>) is set if a stop bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG, will load bits RX9D and FERR with new values, therefore it is essential for the user to read the RCSTA register before reading RCREG register in order not to lose the old FERR and RX9D information.

## Applicable Devices 72 73 73A 74 74A 76 77

### 17.1 DC Characteristics: PIC16C72-04 (Commercial, Industrial, Extended) PIC16C72-10 (Commercial, Industrial, Extended) PIC16C72-20 (Commercial, Industrial, Extended)

| DC CHA                         | RACTERISTICS                                                      | <b>Standa</b><br>Operati |                  |                           | ure -4<br>-4         | Itions (unless otherwise stated) $40^{\circ}C \leq TA \leq +125^{\circ}C$ for extended, $40^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial and $40^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------|-------------------------------------------------------------------|--------------------------|------------------|---------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                   | Characteristic                                                    | Sym                      | Min              | Тур†                      | Max                  | Units                                                                                                                                                                                                     | Conditions                                                                                                                                                                                                                                                                                                                                                                          |

| D001<br>D001A                  | Supply Voltage                                                    | Vdd                      | 4.0<br>4.5       |                           | 6.0<br>5.5           | V<br>V                                                                                                                                                                                                    | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                                                                                                                                                                                                             |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                            | Vdr                      | -                | 1.5                       | -                    | V                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                     |

| D003                           | VDD start voltage to<br>ensure internal Power-<br>on Reset Signal | VPOR                     | -                | Vss                       | -                    | V                                                                                                                                                                                                         | See section on Power-on Reset for details                                                                                                                                                                                                                                                                                                                                           |

| D004*                          | VDD rise rate to ensure<br>internal Power-on Reset<br>Signal      | SVDD                     | 0.05             | -                         | -                    | V/ms                                                                                                                                                                                                      | See section on Power-on Reset for details                                                                                                                                                                                                                                                                                                                                           |

| D005                           | Brown-out Reset Voltage                                           | Bvdd                     | 3.7              | 4.0                       | 4.3                  | V                                                                                                                                                                                                         | BODEN bit in configuration word enabled                                                                                                                                                                                                                                                                                                                                             |

|                                |                                                                   |                          | 3.7              | 4.0                       | 4.4                  | V                                                                                                                                                                                                         | Extended Only                                                                                                                                                                                                                                                                                                                                                                       |

| D010                           | Supply Current<br>(Note 2,5)                                      | IDD                      | -                | 2.7                       | 5.0                  | mA                                                                                                                                                                                                        | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                                                                                                                                                                                                                                                                                       |

| D013                           |                                                                   |                          | -                | 10                        | 20                   | mA                                                                                                                                                                                                        | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                                                                                                                                                                                                                                   |

| D015                           | Brown-out Reset Current<br>(Note 6)                               | ΔIBOR                    | -                | 350                       | 425                  | μA                                                                                                                                                                                                        | BOR enabled VDD = 5.0V                                                                                                                                                                                                                                                                                                                                                              |

| D020<br>D021<br>D021A<br>D021B | Power-down Current<br>(Note 3,5)                                  | IPD                      | -<br>-<br>-<br>- | 10.5<br>1.5<br>1.5<br>2.5 | 42<br>16<br>19<br>19 | μΑ<br>μΑ<br>μΑ<br>μΑ                                                                                                                                                                                      | $ \begin{array}{l} \mbox{VDD} = 4.0\mbox{V, WDT enabled, -40^{\circ}\mbox{C to +85^{\circ}\mbox{C}} \\ \mbox{VDD} = 4.0\mbox{V, WDT disabled, -0^{\circ}\mbox{C to +70^{\circ}\mbox{C}} \\ \mbox{VDD} = 4.0\mbox{V, WDT disabled, -40^{\circ}\mbox{C to +85^{\circ}\mbox{C}} \\ \mbox{VDD} = 4.0\mbox{V, WDT disabled, -40^{\circ}\mbox{C to +125^{\circ}\mbox{C}} \\ \end{array} $ |

| D023                           | Brown-out Reset Current<br>(Note 6)                               | ΔIBOR                    | -                | 350                       | 425                  | μA                                                                                                                                                                                                        | BOR enabled VDD = 5.0V                                                                                                                                                                                                                                                                                                                                                              |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD  $\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VbD and Vss.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

## Applicable Devices 72 73 73A 74 74A 76 77

#### 17.4 **Timing Parameter Symbology**

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2p             | pS                                      | 3. TCC:ST | (I <sup>2</sup> C specifications only) |

|-----------------------|-----------------------------------------|-----------|----------------------------------------|

| 2. TppS               |                                         | 4. Ts     | (I <sup>2</sup> C specifications only) |

| т                     |                                         |           |                                        |

| F                     | Frequency                               | Т         | Time                                   |

| Lowerca               | ase letters (pp) and their meanings:    |           |                                        |

| рр                    |                                         |           |                                        |

| CC                    | CCP1                                    | OSC       | OSC1                                   |

| ck                    | CLKOUT                                  | rd        | RD                                     |

| CS                    | CS                                      | rw        | $\overline{RD}$ or $\overline{WR}$     |

| di                    | SDI                                     | SC        | SCK                                    |

| do                    | SDO                                     | SS        | SS                                     |

| dt                    | Data in                                 | tO        | TOCKI                                  |

| io                    | I/O port                                | t1        | T1CKI                                  |

| mc                    | MCLR                                    | wr        | WR                                     |

| Upperca               | ase letters and their meanings:         |           |                                        |

| S                     |                                         |           |                                        |

| F                     | Fall                                    | P         | Period                                 |

| Н                     | High                                    | R         | Rise                                   |

| I                     | Invalid (Hi-impedance)                  | V         | Valid                                  |

| L                     | Low                                     | Z         | Hi-impedance                           |

| I <sup>2</sup> C only |                                         |           |                                        |

| AA                    | output access                           | High      | High                                   |

| BUF                   | Bus free                                | Low       | Low                                    |

| Tcc:st (              | (I <sup>2</sup> C specifications only)  | I         |                                        |

| CC                    |                                         |           |                                        |

| HD                    | Hold                                    | SU        | Setup                                  |

| ST                    |                                         |           | Comp                                   |

| DAT                   | DATA input hold                         | STO       | STOP condition                         |

| STA                   | START condition                         |           |                                        |

|                       |                                         |           |                                        |

| FIGURE 1              | 17-1: LOAD CONDITIONS                   |           |                                        |

|                       | Load condition 1                        |           | Load condition 2                       |

|                       | N = = /0                                |           |                                        |

|                       |                                         |           |                                        |

|                       | J                                       |           |                                        |

|                       | $\leq$ RL                               |           |                                        |

|                       | $ \leq $                                | N         |                                        |

|                       | I → I                                   |           | X                                      |

|                       |                                         | F         |                                        |

|                       | • • • • • • • • • • • • • • • • • • • • | ,         | ··· ↓                                  |

|                       | Vss                                     |           | Vss                                    |

|                       | $RL$ = 464 $\Omega$                     |           |                                        |

|                       |                                         |           |                                        |

|                       | $C_L = 50 \text{ pF}$ for all pins ex   | cept 0502 |                                        |

15 pF for OSC2 output

Applicable Devices 72 73 73A 74 74A 76 77

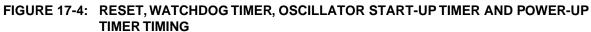

### FIGURE 17-5: BROWN-OUT RESET TIMING

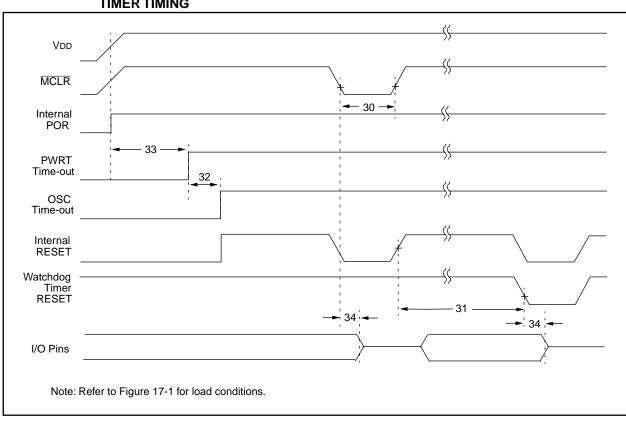

## TABLE 17-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†     | Max | Units | Conditions                |

|------------------|-------|--------------------------------------------------------|-----|----------|-----|-------|---------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                 | 2   | _        | _   | μs    | VDD = 5V, -40°C to +125°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +125°C |

| 32               | Tost  | Oscillation Start-up Timer Period                      | _   | 1024Tosc | _   | —     | Tosc = OSC1 period        |

| 33*              | Tpwrt | Power-up Timer Period                                  | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +125°C |

| 34               | Tioz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | _   | _        | 2.1 | μs    |                           |

| 35               | TBOR  | Brown-out Reset pulse width                            | 100 |          | _   | μs    | $VDD \le BVDD$ (D005)     |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16C7X

Applicable Devices 72 73 73A 74 74A 76 77

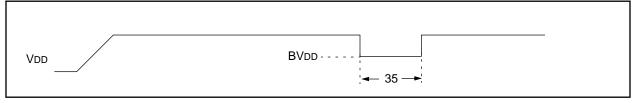

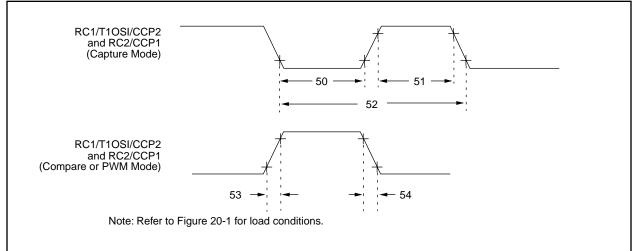

## TABLE 17-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1)

| Param<br>No. | Sym  | Characteristic        | Min            | Тур†               | Max                   | Units | Conditions |    |                                   |

|--------------|------|-----------------------|----------------|--------------------|-----------------------|-------|------------|----|-----------------------------------|

| 50*          | TccL | CCP1 input low time   | No Prescaler   |                    | 0.5Tcy + 20           | —     |            | ns |                                   |

|              |      |                       | With Prescaler | PIC16 <b>C</b> 72  | 10                    | —     | _          | ns |                                   |

|              |      |                       |                | PIC16 <b>LC</b> 72 | 20                    | —     | _          | ns |                                   |

| 51*          | TccH | CCP1 input high time  | No Prescaler   |                    | 0.5Tcy + 20           | —     | —          | ns |                                   |

|              |      |                       | With Prescaler | PIC16 <b>C</b> 72  | 10                    | —     | _          | ns |                                   |

|              |      |                       |                | PIC16 <b>LC</b> 72 | 20                    | —     | _          | ns |                                   |

| 52*          | TccP | CCP1 input period     |                |                    | <u>3Tcy + 40</u><br>N | —     | —          | ns | N = prescale<br>value (1,4 or 16) |

| 53*          | TccR | CCP1 output rise time |                | PIC16 <b>C</b> 72  | _                     | 10    | 25         | ns |                                   |

|              |      |                       |                | PIC16 <b>LC</b> 72 | —                     | 25    | 45         | ns |                                   |

| 54*          | TccF | CCP1 output fall time |                | PIC16 <b>C</b> 72  | _                     | 10    | 25         | ns |                                   |

|              |      |                       |                | PIC16 <b>LC</b> 72 | _                     | 25    | 45         | ns |                                   |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| Applic       | able Devices 72 73 73A 74             | 74A 76 | 6 77                 |            |                                                    |                  |                                                                                                                      |

|--------------|---------------------------------------|--------|----------------------|------------|----------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------|

| 18.3         | PIC16<br>PIC16                        | 6C73/7 | 4-10 (Co<br>4-20 (Co | omr<br>omr | mercial,  <br>mercial,  <br>mercial,  <br>mercial, | Indust<br>Indust | rial)<br>rial)                                                                                                       |

|              |                                       |        |                      |            |                                                    |                  | less otherwise stated)                                                                                               |

| DC CH4       | ARACTERISTICS                         |        |                      |            | 0°C                                                | ; ≤              | $TA \le +85^{\circ}C$ for industrial and<br>$TA \le +70^{\circ}C$ for commercial<br>ibed in DC spec Section 18.1 and |

| Param<br>No. | Characteristic                        | Sym    | Min                  | Тур        | Max                                                | Units            | Conditions                                                                                                           |

| INO.         |                                       |        |                      | 1          |                                                    |                  |                                                                                                                      |

|              | Input Low Voltage                     | VIL    |                      |            |                                                    |                  |                                                                                                                      |

| D030         | with TTL buffer                       |        | Vss                  | -          | 0.15VDD                                            | v                | For entire VDD range                                                                                                 |

| D030A        |                                       |        | VSS                  | _          | 0.10VDD                                            | v                | $4.5V \le VDD \le 5.5V$                                                                                              |

| D031         | with Schmitt Trigger buffer           |        | VSS                  | -          | 0.2VDD                                             | v                |                                                                                                                      |

| D032         | MCLR, OSC1 (in RC mode)               |        | Vss                  | -          | 0.2VDD                                             | v                |                                                                                                                      |

| D033         | OSC1 (in XT, HS and LP)               |        | Vss                  | -          | 0.3VDD                                             | V                | Note1                                                                                                                |

|              | Input High Voltage                    |        |                      |            |                                                    |                  |                                                                                                                      |

|              | I/O ports                             | Vih    |                      | -          |                                                    |                  |                                                                                                                      |

| D040         | with TTL buffer                       |        | 2.0                  | -          | Vdd                                                | V                | $4.5V \le VDD \le 5.5V$                                                                                              |

| D040A        |                                       |        | 0.25VDD<br>+ 0.8V    | -          | Vdd                                                | V                | For entire VDD range                                                                                                 |

| D041         | with Schmitt Trigger buffer           |        | 0.8Vdd               | -          | Vdd                                                | v                | For entire VDD range                                                                                                 |

| D041         | MCLR                                  |        | 0.8VDD               | _          | VDD                                                | v                | Tor entire VDD range                                                                                                 |

| D042A        | OSC1 (XT, HS and LP)                  |        | 0.7VDD               | -          | VDD                                                | v                | Note1                                                                                                                |

| D043         | OSC1 (in RC mode)                     |        | 0.9VDD               | -          | VDD                                                | v                |                                                                                                                      |

| D070         | PORTB weak pull-up current            | IPURB  | 50                   | 250        |                                                    | μA               | VDD = 5V, VPIN = VSS                                                                                                 |

|              | Input Leakage Current<br>(Notes 2, 3) |        |                      |            |                                                    | Pr. 1            |                                                                                                                      |

| D060         | I/O ports                             | lı∟    | -                    | -          | ±1                                                 | μA               | Vss $\leq$ VPIN $\leq$ VDD, Pin at hi-impedance                                                                      |

| D061         | MCLR, RA4/T0CKI                       |        | -                    | -          | ±5                                                 | μA               | $Vss \le VPIN \le VDD$                                                                                               |

| D063         | OSC1                                  |        | -                    | -          | ±5                                                 | μA               | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration                                                          |

|              | Output Low Voltage                    |        |                      |            |                                                    |                  |                                                                                                                      |

| D080         | I/O ports                             | Vol    | -                    | -          | 0.6                                                | V                | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                                                                          |

| D083         | OSC2/CLKOUT (RC osc config)           |        | -                    | -          | 0.6                                                | V                | lOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                                                                          |

|              | Output High Voltage                   |        |                      |            |                                                    |                  |                                                                                                                      |

| D090         | I/O ports (Note 3)                    | Vон    | Vdd - 0.7            | -          | -                                                  | V                | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                                                                         |

| D092         | OSC2/CLKOUT (RC osc config)           |        | Vdd - 0.7            | -          | -                                                  | V                | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                                                                         |

| D150*        | Open-Drain High Voltage               | Vod    | -                    | -          | 14                                                 | V                | RA4 pin                                                                                                              |

| L            |                                       | L      | L                    | L          | I                                                  | I                | · ·                                                                                                                  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C7X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

19.1 DC Characteristics: PIC16C73A/74A-04 (Commercial, Industrial, Extended) PIC16C73A/74A-10 (Commercial, Industrial, Extended) PIC16C73A/74A-20 (Commercial, Industrial, Extended)

| DC CHA                         | ARACTERISTICS                                                    |               | <b>Standa</b><br>Operati |                           |                      | ure -4<br>-4         | litions (unless otherwise stated) $0^{\circ}C \leq TA \leq +125^{\circ}C$ for extended, $0^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial and $C \leq TA \leq +70^{\circ}C$ for commercial                                                                                                                                        |

|--------------------------------|------------------------------------------------------------------|---------------|--------------------------|---------------------------|----------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                   | Characteristic                                                   | Sym           | Min                      | Тур†                      | Max                  | Units                | Conditions                                                                                                                                                                                                                                                                                                                            |

| D001<br>D001A                  | Supply Voltage                                                   | Vdd           | 4.0<br>4.5               | -                         | 6.0<br>5.5           | V<br>V               | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                                                                                                                                                               |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                           | Vdr           | -                        | 1.5                       | -                    | V                    |                                                                                                                                                                                                                                                                                                                                       |

| D003                           | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR          | -                        | Vss                       | -                    | V                    | See section on Power-on Reset for details                                                                                                                                                                                                                                                                                             |

| D004*                          | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | Svdd          | 0.05                     | -                         | -                    | V/ms                 | See section on Power-on Reset for details                                                                                                                                                                                                                                                                                             |

| D005                           | Brown-out Reset Voltage                                          | Bvdd          | 3.7                      | 4.0                       | 4.3                  | V                    | BODEN bit in configuration word enabled                                                                                                                                                                                                                                                                                               |

|                                |                                                                  |               | 3.7                      | 4.0                       | 4.4                  | V                    | Extended Range Only                                                                                                                                                                                                                                                                                                                   |

| D010                           | Supply Current (Note 2,5)                                        | IDD           | -                        | 2.7                       | 5                    | mA                   | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                                                                                                                                                                                                                                         |

| D013                           |                                                                  |               | -                        | 10                        | 20                   | mA                   | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                                                                                                                                                                                     |

| D015*                          | Brown-out Reset Current<br>(Note 6)                              | $\Delta$ Ibor | -                        | 350                       | 425                  | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                                                                                                                                |

| D020<br>D021<br>D021A<br>D021B | Power-down Current<br>(Note 3,5)                                 | IPD           | -<br>-<br>-<br>-         | 10.5<br>1.5<br>1.5<br>2.5 | 42<br>16<br>19<br>19 | μΑ<br>μΑ<br>μΑ<br>μΑ | $\label{eq:VDD} \begin{array}{l} VDD = 4.0V, WDT \text{ enabled}, -40^\circC \text{ to } +85^\circC \\ VDD = 4.0V, WDT \text{ disabled}, -0^\circC \text{ to } +70^\circC \\ VDD = 4.0V, WDT \text{ disabled}, -40^\circC \text{ to } +85^\circC \\ VDD = 4.0V, WDT \text{ disabled}, -40^\circC \text{ to } +125^\circC \end{array}$ |

| D023*                          | Brown-out Reset Current<br>(Note 6)                              | $\Delta$ Ibor | -                        | 350                       | 425                  | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                                                                                                                                |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

$\overline{\text{MCLR}}$  = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

## 19.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2p             | pS                                                | 3. Tcc:st       | (I <sup>2</sup> C specifications only) |

|-----------------------|---------------------------------------------------|-----------------|----------------------------------------|

| 2. TppS               |                                                   | 4. Ts           | (I <sup>2</sup> C specifications only) |

| Т                     |                                                   |                 |                                        |

| F                     | Frequency                                         | Т               | Time                                   |

| Lowerca               | ase letters (pp) and their meanings:              |                 |                                        |

| рр                    |                                                   |                 |                                        |

| сс                    | CCP1                                              | osc             | OSC1                                   |

| ck                    | CLKOUT                                            | rd              | RD                                     |

| CS                    | <u>CS</u>                                         | rw              | RD or WR                               |

| di                    | SDI                                               | sc              | SCK                                    |

| do                    | SDO                                               | SS              | SS                                     |

| dt                    | Data in                                           | tO              | ТОСКІ                                  |

| io                    | I/O port                                          | t1              | T1CKI                                  |

| mc                    | MCLR                                              | wr              | WR                                     |

| Upperca               | ase letters and their meanings:                   |                 |                                        |

| S                     |                                                   |                 |                                        |

| F                     | Fall                                              | Р               | Period                                 |

| н                     | High                                              | R               | Rise                                   |

| 1                     | Invalid (Hi-impedance)                            | V               | Valid                                  |

| L                     | Low                                               | Z               | Hi-impedance                           |

| I <sup>2</sup> C only |                                                   |                 |                                        |

| AA                    | output access                                     | High            | High                                   |

| BUF                   | Bus free                                          | Low             | Low                                    |

| Tcc:st (              | (I <sup>2</sup> C specifications only)            |                 |                                        |

| CC                    |                                                   |                 |                                        |

| HD                    | Hold                                              | SU              | Setup                                  |

| ST                    |                                                   |                 |                                        |

| DAT                   | DATA input hold                                   | STO             | STOP condition                         |

| STA                   | START condition                                   |                 |                                        |

| L                     | 9-1: LOAD CONDITIONS                              |                 |                                        |

|                       | Load condition 1                                  |                 | Load condition 2                       |

|                       |                                                   |                 |                                        |

|                       | VDD/2                                             |                 |                                        |

|                       | ✓ →                                               |                 |                                        |

|                       |                                                   |                 |                                        |

|                       | • • • • • • • • • • • • • • • • • • • •           | ſ               | "' ↓                                   |

|                       | Vss                                               |                 | Vss                                    |

|                       | $RL = 464\Omega$                                  |                 | -                                      |

|                       |                                                   |                 |                                        |

|                       | CL = 50 pF for all pins except OSC2, but in ports | ncluaing PORT   | D and FORTE outputs as                 |

|                       | 15 pF for OSC2 output                             |                 |                                        |

|                       | Note: PORTD and PORTE are not implement           | ted on the PIC1 | 6C73A.                                 |

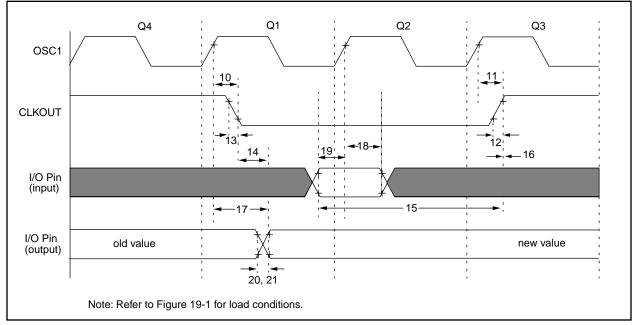

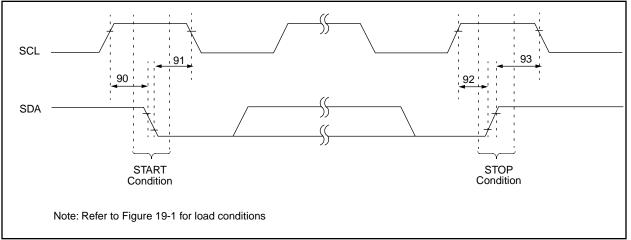

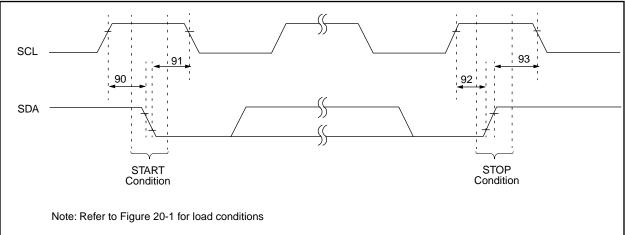

## FIGURE 19-3: CLKOUT AND I/O TIMING

## TABLE 19-3: CLKOUT AND I/O TIMING REQUIREMENTS

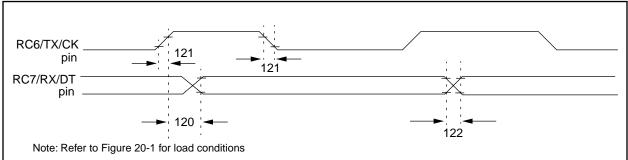

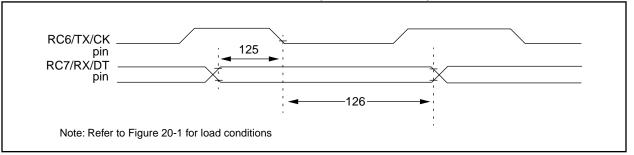

| Param<br>No. | Sym      | Characteristic                                    |                         | Min        | Тур† | Max         | Units  | Conditions |