Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | A/D 5x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c76-04-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. The special function registers can be classified into two sets (core and peripheral). Those registers associated with the "core" functions are described in this section, and those related to the operation of the peripheral features are described in the section of that peripheral feature.

TABLE 4-1: PIC16C72 SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name    | Bit 7                                                                                          | Bit 6              | Bit 5              | Bit 4          | Bit 3         | Bit 2            | Bit 1       | Bit 0   | Value on:<br>POR,<br>BOR | Value on all other resets (3) |

|----------------------|---------|------------------------------------------------------------------------------------------------|--------------------|--------------------|----------------|---------------|------------------|-------------|---------|--------------------------|-------------------------------|

| Bank 0               | Bank 0  |                                                                                                |                    |                    |                |               |                  |             |         |                          |                               |

| 00h <sup>(1)</sup>   | INDF    | Addressing this location uses contents of FSR to address data memory (not a physical register) |                    |                    |                |               |                  |             |         | 0000 0000                | 0000 0000                     |

| 01h                  | TMR0    | Timer0 mod                                                                                     | dule's registe     | r                  |                |               |                  |             |         | xxxx xxxx                | uuuu uuuu                     |

| 02h <sup>(1)</sup>   | PCL     | Program Co                                                                                     | ounter's (PC)      | Least Signif       | icant Byte     |               |                  |             |         | 0000 0000                | 0000 0000                     |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(4)</sup>                                                                             | RP1 <sup>(4)</sup> | RP0                | TO             | PD            | Z                | DC          | С       | 0001 1xxx                | 000q quuu                     |

| 04h <sup>(1)</sup>   | FSR     | Indirect dat                                                                                   | a memory ac        | dress pointe       | r              |               |                  |             |         | xxxx xxxx                | uuuu uuuu                     |

| 05h                  | PORTA   | _                                                                                              | _                  | PORTA Dat          | a Latch whe    | n written: PO | RTA pins wh      | en read     |         | 0x 0000                  | 0u 0000                       |

| 06h                  | PORTB   | PORTB Da                                                                                       | ta Latch whe       | n written: PC      | RTB pins wl    | nen read      |                  |             |         | xxxx xxxx                | uuuu uuuu                     |

| 07h                  | PORTC   | PORTC Da                                                                                       | ta Latch whe       | n written: PC      | RTC pins w     | hen read      |                  |             |         | xxxx xxxx                | uuuu uuuu                     |

| 08h                  | _       | Unimpleme                                                                                      | nted               |                    |                |               |                  |             |         | _                        | _                             |

| 09h                  | _       | Unimpleme                                                                                      | nted               |                    |                |               |                  |             |         | _                        | _                             |

| 0Ah <sup>(1,2)</sup> | PCLATH  | _                                                                                              | _                  | _                  | Write Buffer   | for the uppe  | er 5 bits of the | e Program C | ounter  | 0 0000                   | 0 0000                        |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                                                                                            | PEIE               | TOIE               | INTE           | RBIE          | TOIF             | INTF        | RBIF    | 0000 000x                | 0000 000u                     |

| 0Ch                  | PIR1    | _                                                                                              | ADIF               | _                  | _              | SSPIF         | CCP1IF           | TMR2IF      | TMR1IF  | -0 0000                  | -0 0000                       |

| 0Dh                  | _       | Unimpleme                                                                                      | nted               |                    |                |               |                  |             |         | _                        | _                             |

| 0Eh                  | TMR1L   | Holding register for the Least Significant Byte of the 16-bit TMR1 register                    |                    |                    |                |               |                  |             |         | xxxx xxxx                | uuuu uuuu                     |

| 0Fh                  | TMR1H   | Holding reg                                                                                    | ister for the N    | Most Signification | ant Byte of th | ne 16-bit TMF | R1 register      |             |         | xxxx xxxx                | uuuu uuuu                     |

| 10h                  | T1CON   | _                                                                                              | _                  | T1CKPS1            | T1CKPS0        | T10SCEN       | T1SYNC           | TMR1CS      | TMR10N  | 00 0000                  | uu uuuu                       |

| 11h                  | TMR2    | Timer2 mod                                                                                     | dule's registe     | r                  |                |               |                  |             |         | 0000 0000                | 0000 0000                     |

| 12h                  | T2CON   | _                                                                                              | TOUTPS3            | TOUTPS2            | TOUTPS1        | TOUTPS0       | TMR2ON           | T2CKPS1     | T2CKPS0 | -000 0000                | -000 0000                     |

| 13h                  | SSPBUF  | Synchronou                                                                                     | us Serial Port     | Receive Bu         | ffer/Transmit  | Register      |                  |             |         | xxxx xxxx                | uuuu uuuu                     |

| 14h                  | SSPCON  | WCOL                                                                                           | SSPOV              | SSPEN              | CKP            | SSPM3         | SSPM2            | SSPM1       | SSPM0   | 0000 0000                | 0000 0000                     |

| 15h                  | CCPR1L  | Capture/Co                                                                                     | mpare/PWM          | Register (LS       | SB)            |               |                  |             |         | xxxx xxxx                | uuuu uuuu                     |

| 16h                  | CCPR1H  | Capture/Co                                                                                     | mpare/PWM          | Register (M        | SB)            |               |                  |             |         | xxxx xxxx                | uuuu uuuu                     |

| 17h                  | CCP1CON | _                                                                                              | _                  | CCP1X              | CCP1Y          | CCP1M3        | CCP1M2           | CCP1M1      | CCP1M0  | 00 0000                  | 00 0000                       |

| 18h                  | _       | Unimpleme                                                                                      | nted               |                    |                |               |                  |             |         | _                        | _                             |

| 19h                  | _       | Unimpleme                                                                                      | nted               |                    |                |               |                  |             |         | _                        | _                             |

| 1Ah                  | _       | Unimpleme                                                                                      | nted               |                    |                |               |                  |             |         | _                        | _                             |

| 1Bh                  | _       | Unimpleme                                                                                      | Unimplemented      |                    |                |               |                  |             |         |                          | _                             |

| 1Ch                  | _       | Unimpleme                                                                                      | nted               |                    |                |               |                  |             |         | _                        | _                             |

| 1Dh                  | _       | Unimpleme                                                                                      | nted               |                    |                |               |                  |             |         | _                        | _                             |

| 1Eh                  | ADRES   | A/D Result                                                                                     | Register           |                    |                |               |                  |             |         | xxxx xxxx                | uuuu uuuu                     |

| 1Fh                  | ADCON0  | ADCS1                                                                                          | ADCS0              | CHS2               | CHS1           | CHS0          | GO/DONE          | _           | ADON    | 0000 00-0                | 0000 00-0                     |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

- Note 1: These registers can be addressed from either bank.

- 2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

- 3: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

- 4: The IRP and RP1 bits are reserved on the PIC16C72, always maintain these bits clear.

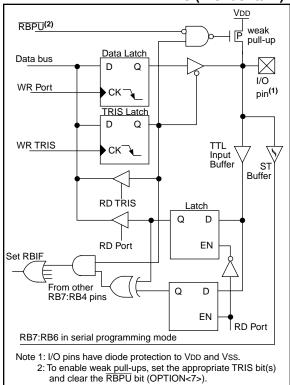

FIGURE 5-4: **BLOCK DIAGRAM OF RB7:RB4 PINS (PIC16C73/74)**

FIGURE 5-5: **BLOCK DIAGRAM OF** RB7:RB4 PINS (PIC16C72/ 73A/74A/76/77)

2: To enable weak pull-ups, set the appropriate TRIS bit(s) and clear the RBPU bit (OPTION<7>).

**TABLE 5-3:** PORTB FUNCTIONS

| Name    | Bit# | Buffer                | Function                                                                                                            |

|---------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                          |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming data.  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

#### 8.3 <u>Timer1 Operation in Asynchronous</u> Counter Mode

Applicable Devices 72 73 73A 74 74A 76 77

If control bit T1SYNC (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt on overflow which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 8.3.2).

In asynchronous counter mode, Timer1 can not be used as a time-base for capture or compare operations.

## 8.3.1 EXTERNAL CLOCK INPUT TIMING WITH UNSYNCHRONIZED CLOCK

If control bit T1SYNC is set, the timer will increment completely asynchronously. The input clock must meet certain minimum high time and low time requirements. Refer to the appropriate Electrical Specifications Section, timing parameters 45, 46, and 47.

## 8.3.2 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running, from an external asynchronous clock, will guarantee a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself poses certain problems since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Example 8-1 is an example routine to read the 16-bit timer value. This is useful if the timer cannot be stopped.

#### EXAMPLE 8-1: READING A 16-BIT FREE-RUNNING TIMER

```

; All interrupts are disabled

MOVF

TMR1H, W ; Read high byte

MOVWF TMPH

MOVF

TMR1L, W ; Read low byte

MOVWE TMPL

MOVF

TMR1H, W ; Read high byte

TMPH, W ;Sub 1st read

SUBWF

; with 2nd read

BTFSC STATUS, Z ; Is result = 0

CONTINUE ; Good 16-bit read

GOTO

; TMR1L may have rolled over between the read

of the high and low bytes. Reading the high

and low bytes now will read a good value.

MOVF

TMR1H, W ; Read high byte

MOVWF

TMPH

TMR1L, W ; Read low byte

MOVF

MOVWF TMPL

; Re-enable the Interrupt (if required)

;Continue with your code

CONTINUE

```

#### 8.4 Timer1 Oscillator

Applicable Devices 72 73 73 A 74 74 A 76 77

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 8-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

TABLE 8-1: CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR

| Osc Type                                   | Freq        | C1                             | C2       |  |  |  |  |

|--------------------------------------------|-------------|--------------------------------|----------|--|--|--|--|

| LP                                         | 32 kHz      | 33 pF                          | 33 pF    |  |  |  |  |

|                                            | 100 kHz     | 15 pF                          |          |  |  |  |  |

|                                            | 200 kHz     | 15 pF                          |          |  |  |  |  |

| These values are for design guidance only. |             |                                |          |  |  |  |  |

| Crystals Tes                               | ted:        |                                |          |  |  |  |  |

| 32.768 kHz                                 | Epson C-00  | 1R32.768K-A                    | ± 20 PPM |  |  |  |  |

| 100 kHz                                    | Epson C-2 1 | Epson C-2 100.00 KC-P ± 20 PPM |          |  |  |  |  |

| 200 kHz                                    | STD XTL 20  | STD XTL 200.000 kHz ± 20 PPM   |          |  |  |  |  |

|                                            | • •         |                                |          |  |  |  |  |

- Note 1: Higher capacitance increases the stability of oscillator but also increases the start-up time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

## FIGURE 12-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS 18h)

|               |                                                         |                          |                     |             |             |              | _            |                                                                              |

|---------------|---------------------------------------------------------|--------------------------|---------------------|-------------|-------------|--------------|--------------|------------------------------------------------------------------------------|

| R/W-0<br>SPEN | R/W-0                                                   | R/W-0<br>SREN            | R/W-0<br>CREN       | U-0         | R-0<br>FERR | R-0<br>OERR  | R-x<br>RX9D  | R = Readable bit                                                             |

| bit7          | I KVA                                                   | JREN                     | OREN                |             | FERR        | OERR         | bit0         | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset |

| bit 7:        | SPEN: Ser<br>1 = Serial p<br>0 = Serial p               | ort enable               | ed (Configur        | es RC7/R    | X/DT and    | RC6/TX/CI    | K pins as se | rial port pins)                                                              |

| bit 6:        | <b>RX9</b> : 9-bit I 1 = Selects 0 = Selects            | 9-bit rece               | ption               |             |             |              |              |                                                                              |

| bit 5:        | SREN: Sing                                              | gle Receive              | e Enable bi         | t           |             |              |              |                                                                              |

|               | Asynchrone<br>Don't care                                | ous mode                 |                     |             |             |              |              |                                                                              |

|               | Synchrono<br>1 = Enable<br>0 = Disable<br>This bit is o | s single reess single re | ceive               | is comple   | ete.        |              |              |                                                                              |

|               | Synchrono<br>Unused in                                  |                          | <u>slave</u>        |             |             |              |              |                                                                              |

| bit 4:        | CREN: Cor                                               | ntinuous R               | eceive Enal         | ble bit     |             |              |              |                                                                              |

|               | Asynchrono<br>1 = Enable<br>0 = Disable                 | s continuo               |                     |             |             |              |              |                                                                              |

|               | Synchrono<br>1 = Enable<br>0 = Disable                  | s continuo               |                     | until enabl | e bit CREN  | I is cleared | (CREN ove    | errides SREN)                                                                |

| bit 3:        | Unimplem                                                | ented: Rea               | ad as '0'           |             |             |              |              |                                                                              |

| bit 2:        | FERR: Fran<br>1 = Framing<br>0 = No fran                | g error (Ca              |                     | ed by reac  | ding RCRE   | G register   | and receive  | next valid byte)                                                             |

| bit 1:        | OERR: Over 1 = Overrui 0 = No ove                       | n error (Ca              | bit<br>In be cleare | d by clear  | ing bit CRI | ΞN)          |              |                                                                              |

bit 0: **RX9D**: 9th bit of received data (Can be parity bit)

#### 13.5 A/D Operation During Sleep

**Applicable Devices** 72 | 73 | 73 | 74 | 74 | 76 | 77 |

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed the  $GO/\overline{DONE}$  bit will be cleared, and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the A/D module will then be turned off, although the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

#### Note:

For the A/D module to operate in SLEEP, the A/D clock source must be set to RC (ADCS1:ADCS0 = 11). To perform an A/D conversion in SLEEP, ensure the SLEEP instruction immediately follows the instruction that sets the  $GO/\overline{DONE}$  bit.

#### 13.6 A/D Accuracy/Error

**Applicable Devices** 72 | 73 | 73 | 74 | 74 | 76 | 77 |

The absolute accuracy specified for the A/D converter includes the sum of all contributions for quantization error, integral error, differential error, full scale error, offset error, and monotonicity. It is defined as the maximum deviation from an actual transition versus an ideal transition for any code. The absolute error of the A/D converter is specified at  $<\pm 1$  LSb for VDD = VREF (over the device's specified operating range). However, the accuracy of the A/D converter will degrade as VDD diverges from VREF.

For a given range of analog inputs, the output digital code will be the same. This is due to the quantization of the analog input to a digital code. Quantization error is typically  $\pm$  1/2 LSb and is inherent in the analog to digital conversion process. The only way to reduce quantization error is to increase the resolution of the A/D converter.

Offset error measures the first actual transition of a code versus the first ideal transition of a code. Offset error shifts the entire transfer function. Offset error can be calibrated out of a system or introduced into a system through the interaction of the total leakage current and source impedance at the analog input.

Gain error measures the maximum deviation of the last actual transition and the last ideal transition adjusted for offset error. This error appears as a change in slope of the transfer function. The difference in gain error to full scale error is that full scale does not take offset error into account. Gain error can be calibrated out in software.

Linearity error refers to the uniformity of the code changes. Linearity errors cannot be calibrated out of the system. Integral non-linearity error measures the actual code transition versus the ideal code transition adjusted by the gain error for each code.

Differential non-linearity measures the maximum actual code width versus the ideal code width. This measure is unadjusted.

The maximum pin leakage current is  $\pm$  1  $\mu$ A.

In systems where the device frequency is low, use of the A/D RC clock is preferred. At moderate to high frequencies, TAD should be derived from the device oscillator. TAD must not violate the minimum and should be  $\leq 8~\mu s$  for preferred operation. This is because TAD, when derived from Tosc, is kept away from on-chip phase clock transitions. This reduces, to a large extent, the effects of digital switching noise. This is not possible with the RC derived clock. The loss of accuracy due to digital switching noise can be significant if many I/O pins are active.

In systems where the device will enter SLEEP mode after the start of the A/D conversion, the RC clock source selection is required. In this mode, the digital noise from the modules in SLEEP are stopped. This method gives high accuracy.

#### 13.7 Effects of a RESET

Applicable Devices 72|73|73A|74|74A|76|77

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted.

The value that is in the ADRES register is not modified for a Power-on Reset. The ADRES register will contain unknown data after a Power-on Reset.

TABLE 14-8: INITIALIZATION CONDITIONS FOR ALL REGISTERS (Cont.'d)

| Register | Applicable Devices |    |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT<br>or<br>Interrupt |    |           |           |              |

|----------|--------------------|----|-----|------------------------------------|--------------------------|------------------------------------|----|-----------|-----------|--------------|

| INTCON   | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 0000 000x | 0000 000u | uuuu uuuu(1) |

|          | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | -0 0000   | -0 0000   | -u uuuu(1)   |

| PIR1     | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | -000 0000 | -000 0000 | -uuu uuuu(1) |

|          | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 0000 0000 | 0000 0000 | uuuu uuuu(1) |

| PIR2     | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 0         | 0         | (1)          |

| TMR1L    | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | xxxx xxxx | uuuu uuuu | uuuu uuuu    |

| TMR1H    | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | xxxx xxxx | uuuu uuuu | uuuu uuuu    |

| T1CON    | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 00 0000   | uu uuuu   | uu uuuu      |

| TMR2     | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 0000 0000 | 0000 0000 | uuuu uuuu    |

| T2CON    | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | -000 0000 | -000 0000 | -uuu uuuu    |

| SSPBUF   | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | xxxx xxxx | uuuu uuuu | uuuu uuuu    |

| SSPCON   | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 0000 0000 | 0000 0000 | uuuu uuuu    |

| CCPR1L   | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | xxxx xxxx | uuuu uuuu | uuuu uuuu    |

| CCPR1H   | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | xxxx xxxx | uuuu uuuu | uuuu uuuu    |

| CCP1CON  | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 00 0000   | 00 0000   | uu uuuu      |

| RCSTA    | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 0000 -00x | 0000 -00x | uuuu -uuu    |

| TXREG    | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 0000 0000 | 0000 0000 | uuuu uuuu    |

| RCREG    | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 0000 0000 | 0000 0000 | uuuu uuuu    |

| CCPR2L   | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | xxxx xxxx | uuuu uuuu | uuuu uuuu    |

| CCPR2H   | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | xxxx xxxx | uuuu uuuu | uuuu uuuu    |

| CCP2CON  | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 0000 0000 | 0000 0000 | uuuu uuuu    |

| ADRES    | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | xxxx xxxx | uuuu uuuu | uuuu uuuu    |

| ADCON0   | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 0000 00-0 | 0000 00-0 | uuuu uu-u    |

| OPTION   | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 1111 1111 | 1111 1111 | uuuu uuuu    |

| TRISA    | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 11 1111   | 11 1111   | uu uuuu      |

| TRISB    | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 1111 1111 | 1111 1111 | uuuu uuuu    |

| TRISC    | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 1111 1111 | 1111 1111 | uuuu uuuu    |

| TRISD    | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 1111 1111 | 1111 1111 | uuuu uuuu    |

| TRISE    | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 0000 -111 | 0000 -111 | uuuu -uuu    |

|          | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | -0 0000   | -0 0000   | -u uuuu      |

| PIE1     | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | -000 0000 | -000 0000 | -uuu uuuu    |

|          | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 0000 0000 | 0000 0000 | uuuu uuuu    |

| PIE2     | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 0         | 0         | u            |

| DCON     | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 0-        | u-        | u-           |

| PCON     | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 0u        | uu        | uu           |

| PR2      | 72                 | 73 | 73A | 74                                 | 74A                      | 76                                 | 77 | 1111 1111 | 1111 1111 | 1111 1111    |

Legend: u = unchanged, x = unknown, -= unimplemented bit, read as '0', <math>q = value depends on condition Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

<sup>2:</sup> When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h)

<sup>3:</sup> See Table 14-7 for reset value for specific condition.

# PIC16C7X

| CLRF              | Clear f                                                        |                         |                 |                       |  |  |  |  |  |

|-------------------|----------------------------------------------------------------|-------------------------|-----------------|-----------------------|--|--|--|--|--|

| Syntax:           | [label] C                                                      | [label] CLRF f          |                 |                       |  |  |  |  |  |

| Operands:         | $0 \le f \le 12$                                               | $0 \le f \le 127$       |                 |                       |  |  |  |  |  |

| Operation:        | $00h \to (f)$ $1 \to Z$                                        |                         |                 |                       |  |  |  |  |  |

| Status Affected:  | Z                                                              |                         |                 |                       |  |  |  |  |  |

| Encoding:         | 00 0001 1fff ffff                                              |                         |                 |                       |  |  |  |  |  |

| Description:      | The contents of register 'f' are cleared and the Z bit is set. |                         |                 |                       |  |  |  |  |  |

| Words:            | 1                                                              |                         |                 |                       |  |  |  |  |  |

| Cycles:           | 1                                                              |                         |                 |                       |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                             | Q2                      | Q3              | Q4                    |  |  |  |  |  |

|                   | Decode                                                         | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |  |  |  |  |

| Example           | CLRF                                                           | FLAG                    | G_REG           |                       |  |  |  |  |  |

|                   | Before Instruction<br>FLAG_REG = 0x5A                          |                         |                 |                       |  |  |  |  |  |

|                   | After Instruction                                              |                         |                 |                       |  |  |  |  |  |

$FLAG_REG = 0x00$

| CLRW              | Clear W                                     |                  |                 |               |  |  |  |  |  |

|-------------------|---------------------------------------------|------------------|-----------------|---------------|--|--|--|--|--|

| Syntax:           | [ label ]                                   | CLRW             |                 |               |  |  |  |  |  |

| Operands:         | None                                        |                  |                 |               |  |  |  |  |  |

| Operation:        | $00h \rightarrow (W)$ $1 \rightarrow Z$     |                  |                 |               |  |  |  |  |  |

| Status Affected:  | Z                                           |                  |                 |               |  |  |  |  |  |

| Encoding:         | 00                                          | 0001             | 0xxx            | xxxx          |  |  |  |  |  |

| Description:      | W register is cleared. Zero bit (Z) is set. |                  |                 |               |  |  |  |  |  |

| Words:            | 1                                           |                  |                 |               |  |  |  |  |  |

| Cycles:           | 1                                           |                  |                 |               |  |  |  |  |  |

| Q Cycle Activity: | Q1                                          | Q2               | Q3              | Q4            |  |  |  |  |  |

|                   | Decode                                      | No-<br>Operation | Process<br>data | Write to<br>W |  |  |  |  |  |

| Example           | CLRW                                        |                  |                 |               |  |  |  |  |  |

|                   | Before In                                   | struction        |                 |               |  |  |  |  |  |

|                   |                                             | • •              | 0x5A            |               |  |  |  |  |  |

|                   | After Inst                                  |                  | 0x00            |               |  |  |  |  |  |

|                   |                                             | • •              | 1               |               |  |  |  |  |  |

| CLRWDT            | Clear Wa                                                                                                              | tchdog 1              | Timer           |                         |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|-------------------------|--|--|--|--|

| Syntax:           | [ label ]                                                                                                             | CLRWD1                | Г               |                         |  |  |  |  |

| Operands:         | None                                                                                                                  |                       |                 |                         |  |  |  |  |

| Operation:        | 00h → WDT<br>0 → WDT prescaler,<br>1 → $\overline{\text{TO}}$<br>1 → $\overline{\text{PD}}$                           |                       |                 |                         |  |  |  |  |

| Status Affected:  | $\overline{TO}$ , $\overline{PD}$                                                                                     |                       |                 |                         |  |  |  |  |

| Encoding:         | 00 0000 0110 0100                                                                                                     |                       |                 |                         |  |  |  |  |

| Description:      | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits TO and PD are set. |                       |                 |                         |  |  |  |  |

| Words:            | 1                                                                                                                     |                       |                 |                         |  |  |  |  |

| Cycles:           | 1                                                                                                                     |                       |                 |                         |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                    | Q2                    | Q3              | Q4                      |  |  |  |  |

|                   | Decode                                                                                                                | No-<br>Operation      | Process<br>data | Clear<br>WDT<br>Counter |  |  |  |  |

| Example           | CLRWDT                                                                                                                |                       |                 |                         |  |  |  |  |

|                   | Before In                                                                                                             | struction<br>WDT cour | nter =          | ?                       |  |  |  |  |

|                   | After Instruction  WDT counter = 0x00  WDT prescaler = 0  TO = 1  PD = 1                                              |                       |                 |                         |  |  |  |  |

#### 16.6 <u>PICDEM-1 Low-Cost PIC16/17</u> Demonstration Board

The PICDEM-1 is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The users can program the sample microcontrollers provided with the PICDEM-1 board, on a PRO MATE II or PICSTART-16B programmer, and easily test firmware. The user can also connect the PICDEM-1 board to the PICMASTER emulator and download the firmware to the emulator for testing. Additional prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push-button switches and eight LEDs connected to PORTB.

## 16.7 PICDEM-2 Low-Cost PIC16CXX Demonstration Board

The PICDEM-2 is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-2 board, on a PRO MATE II programmer or PICSTART-16C, and easily test firmware. The PICMASTER emulator may also be used with the PICDEM-2 board to test firmware. Additional prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push-button switches, a potentiometer for simulated analog input, a Serial EEPROM to demonstrate usage of the I<sup>2</sup>C bus and separate headers for connection to an LCD module and a keypad.

## 16.8 PICDEM-3 Low-Cost PIC16CXXX Demonstration Board

The PICDEM-3 is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with a LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-3 board, on a PRO MATE II programmer or PICSTART Plus with an adapter socket, and easily test firmware. The PICMASTER emulator may also be used with the PICDEM-3 board to test firmware. Additional prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include

an RS-232 interface, push-button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM-3 board is an LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM-3 provides an additional RS-232 interface and Windows 3.1 software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

### 16.9 MPLAB Integrated Development Environment Software

The MPLAB IDE Software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a windows based application which contains:

- · A full featured editor

- · Three operating modes

- editor

- emulator

- simulator

- · A project manager

- · Customizable tool bar and key mapping

- · A status bar with project information

- Extensive on-line help

MPLAB allows you to:

- · Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC16/17 tools (automatically updates all project information)

- · Debug using:

- source files

- absolute listing file

- Transfer data dynamically via DDE (soon to be replaced by OLE)

- · Run up to four emulators on the same PC

The ability to use MPLAB with Microchip's simulator allows a consistent platform and the ability to easily switch from the low cost simulator to the full featured emulator with minimal retraining due to development tools.

#### 16.10 Assembler (MPASM)

The MPASM Universal Macro Assembler is a PC-hosted symbolic assembler. It supports all microcontroller series including the PIC12C5XX, PIC14000, PIC16C5X, PIC16CXXX, and PIC17CXX families.

MPASM offers full featured Macro capabilities, conditional assembly, and several source and listing formats. It generates various object code formats to support Microchip's development tools as well as third party programmers.

MPASM allows full symbolic debugging from PICMASTER, Microchip's Universal Emulator System.

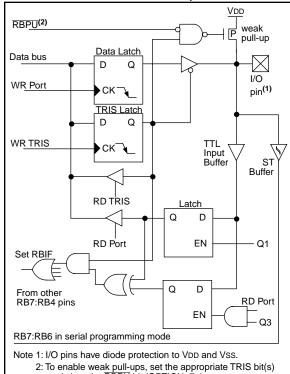

FIGURE 17-8: SPI MODE TIMING

TABLE 17-7: SPI MODE REQUIREMENTS

| Parameter<br>No. | Sym                   | Characteristic                           | Min      | Тур† | Max | Units | Conditions |

|------------------|-----------------------|------------------------------------------|----------|------|-----|-------|------------|

| 70               | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                | Tcy      | _    | _   | ns    |            |

| 71               | TscH                  | SCK input high time (slave mode)         | Tcy + 20 |      |     | ns    |            |

| 72               | TscL                  | SCK input low time (slave mode)          | Tcy + 20 | _    | _   | ns    |            |

| 73               | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge | 50       | _    | _   | ns    |            |

| 74               | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge  | 50       | _    | _   | ns    |            |

| 75               | TdoR                  | SDO data output rise time                | _        | 10   | 25  | ns    |            |

| 76               | TdoF                  | SDO data output fall time                | _        | 10   | 25  | ns    |            |

| 77               | TssH2doZ              | SS↑ to SDO output hi-impedance           | 10       | _    | 50  | ns    |            |

| 78               | TscR                  | SCK output rise time (master mode)       | _        | 10   | 25  | ns    |            |

| 79               | TscF                  | SCK output fall time (master mode)       | _        | 10   | 25  | ns    |            |

| 80               | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge     | _        | _    | 50  | ns    |            |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

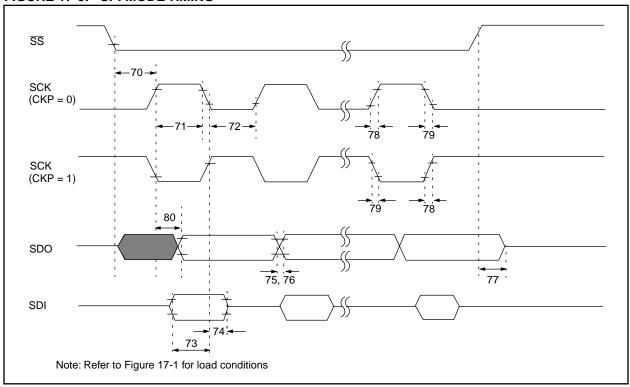

FIGURE 18-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

TABLE 18-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER REQUIREMENTS

| Parameter No. | Sym   | Characteristic                                         | Min | Тур†     | Max | Units | Conditions                                        |

|---------------|-------|--------------------------------------------------------|-----|----------|-----|-------|---------------------------------------------------|

| 30            | TmcL  | MCLR Pulse Width (low)                                 | 100 | _        | _   | ns    | $VDD = 5V, -40^{\circ}C \text{ to } +85^{\circ}C$ |

| 31*           | Twdt  | Watchdog Timer Time-out Period (No Prescaler)          | 7   | 18       | 33  | ms    | $VDD = 5V$ , $-40^{\circ}C$ to $+85^{\circ}C$     |

| 32            | Tost  | Oscillation Start-up Timer Period                      | _   | 1024Tosc | _   | _     | Tosc = OSC1 period                                |

| 33*           | Tpwrt | Power up Timer Period                                  | 28  | 72       | 132 | ms    | $VDD = 5V, -40^{\circ}C \text{ to } +85^{\circ}C$ |

| 34            | Tıoz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | _   | _        | 100 | ns    |                                                   |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

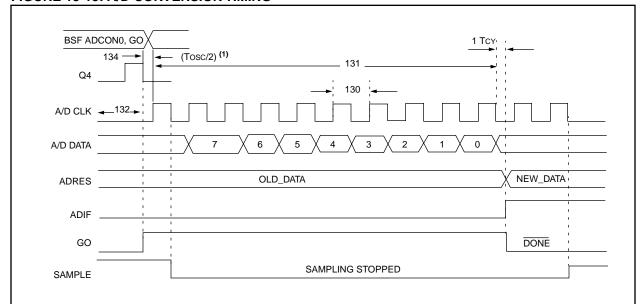

## FIGURE 18-13: A/D CONVERSION TIMING

Note 1: If the A/D clock source is selected as RC, a time of Tcy is added before the A/D clock starts. This allows the SLEEP instruction to be executed.

#### **TABLE 18-14: A/D CONVERSION REQUIREMENTS**

| Param<br>No. | Sym  | Characteristic                                    |                           | Min    | Тур†     | Max | Units | Conditions                                                                                                                                                                                                |

|--------------|------|---------------------------------------------------|---------------------------|--------|----------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D clock period                                  | PIC16 <b>C</b> 73/74      | 1.6    | _        | _   | μs    | Tosc based, VREF ≥ 3.0V                                                                                                                                                                                   |

|              |      |                                                   | PIC16 <b>LC</b> 73/74     | 2.0    | _        | _   | μs    | Tosc based, VREF full range                                                                                                                                                                               |

|              |      |                                                   | PIC16 <b>C</b> 73/74      | 2.0    | 4.0      | 6.0 | μs    | A/D RC Mode                                                                                                                                                                                               |

|              |      |                                                   | PIC16 <b>LC</b> 73/74     | 3.0    | 6.0      | 9.0 | μs    | A/D RC Mode                                                                                                                                                                                               |

| 131          | TCNV | Conversion time (not including S/H time) (Note 1) |                           | _      | 9.5      | _   | TAD   |                                                                                                                                                                                                           |

| 132          | TACQ | Acquisition time                                  |                           | Note 2 | 20       | _   | μs    |                                                                                                                                                                                                           |

|              |      |                                                   |                           | 5*     | _        | _   | μs    | The minimum time is the amplifier settling time. This may be used if the "new" input voltage has not changed by more than 1 LSb (i.e., 20 mV @ 5.12V) from the last sampled voltage (as stated on CHOLD). |

| 134          | TGO  | Q4 to A/D clock start                             |                           | _      | Tosc/2 § | _   | _     | If the A/D clock source is selected as RC, a time of Tcy is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                          |

| 135          | Tswc | Switching from convert                            | $\rightarrow$ sample time | 1.5 §  | _        | _   | TAD   |                                                                                                                                                                                                           |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>§</sup> This specification ensured by design.

Note 1: ADRES register may be read on the following TcY cycle.

<sup>2:</sup> See Section 13.1 for min conditions.

## 19.2 DC Characteristics: PIC16LC73A/74A-04 (Commercial, Industrial)

| DC CHA        |                                                                  |       | ard Ope | •    | •      | itions (unless otherwise stated)  °C ≤ TA ≤ +85°C for industrial and  C ≤ TA ≤ +70°C for commercial |                                                                 |

|---------------|------------------------------------------------------------------|-------|---------|------|--------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| Param<br>No.  | Characteristic                                                   | Sym   | Min     | Тур† | Max    | Units                                                                                               | Conditions                                                      |

| D001          | Supply Voltage                                                   | VDD   | 2.5     | -    | 6.0    | V                                                                                                   | LP, XT, RC osc configuration (DC - 4 MHz)                       |

| D002*         | RAM Data Retention<br>Voltage (Note 1)                           | VDR   | -       | 1.5  | -      | V                                                                                                   |                                                                 |

| D003          | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR  | -       | Vss  | -      | >                                                                                                   | See section on Power-on Reset for details                       |

| D004*         | VDD rise rate to ensure internal Power-on Reset signal           | SVDD  | 0.05    | -    | -      | V/ms                                                                                                | See section on Power-on Reset for details                       |

| D005          | Brown-out Reset Voltage                                          | BVDD  | 3.7     | 4.0  | 4.3    | V                                                                                                   | BODEN bit in configuration word enabled                         |

| D010          | Supply Current (Note 2,5)                                        | IDD   | -       | 2.0  | 3.8    | mA                                                                                                  | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)   |

| D010A         |                                                                  |       | -       | 22.5 | 48     | μΑ                                                                                                  | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled |

| D015*         | Brown-out Reset Current (Note 6)                                 | ΔIBOR | -       | 350  | 425    | μΑ                                                                                                  | BOR enabled VDD = 5.0V                                          |

| D020          | Power-down Current                                               | IPD   | -       | 7.5  | 30     | μΑ                                                                                                  | VDD = 3.0V, WDT enabled, -40°C to +85°C                         |

| D021<br>D021A | (Note 3,5)                                                       |       | -       | 0.9  | 5<br>5 | μΑ                                                                                                  | VDD = 3.0V, WDT disabled, 0°C to +70°C                          |

| 1             | Brown-out Reset Current                                          | Albor | _       | 0.9  | •      | μA<br>                                                                                              | VDD = 3.0V, WDT disabled, -40°C to +85°C                        |

| D023*         | (Note 6)                                                         | Δlbor | -       | 350  | 425    | μΑ                                                                                                  | BOR enabled VDD = 5.0V                                          |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

- The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

- MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

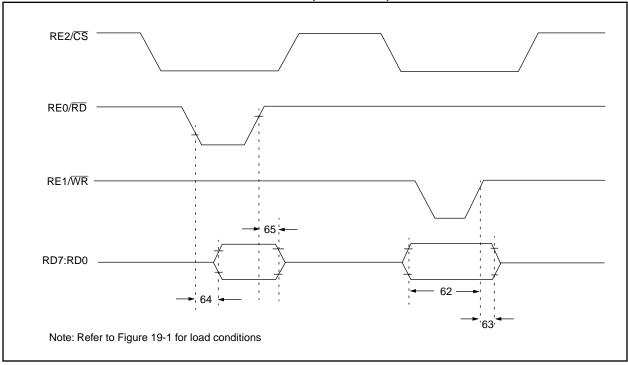

FIGURE 19-8: PARALLEL SLAVE PORT TIMING (PIC16C74A)

TABLE 19-7: PARALLEL SLAVE PORT REQUIREMENTS (PIC16C74A)

| Parameter No. | Sym      | Characteristic                                                    |                     | Min      | Тур† | Max      | Units    | Conditions             |

|---------------|----------|-------------------------------------------------------------------|---------------------|----------|------|----------|----------|------------------------|

| 62            | TdtV2wrH | Data in valid before WR↑ or CS↑ (setup time)                      |                     | 20<br>25 | _    | _        | ns<br>ns | Extended<br>Range Only |

| 63*           | TwrH2dtl | $\overline{WR}$ or $\overline{CS}$ to data–in invalid (hold time) | PIC16 <b>C</b> 74A  | 20       | _    | _        | ns       |                        |

|               |          |                                                                   | PIC16 <b>LC</b> 74A | 35       | _    | _        | ns       |                        |

| 64            | TrdL2dtV | RD↓ and CS↓ to data–out valid                                     |                     |          | _    | 80<br>90 | ns<br>ns | Extended<br>Range Only |

| 65            | TrdH2dtl | RD↑ or CS↓ to data–out invalid                                    |                     | 10       | _    | 30       | ns       |                        |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

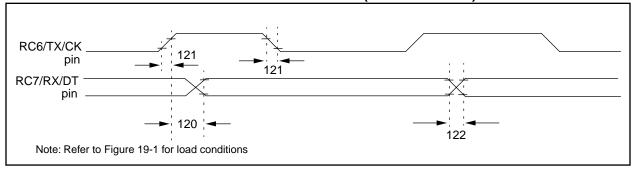

## FIGURE 19-12: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 19-11: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                                          | Min                                               | Тур†   | Max      | Units     | Conditions |  |

|--------------|----------|---------------------------------------------------------|---------------------------------------------------|--------|----------|-----------|------------|--|

| 120          | TckH2dtV | SYNC XMIT (MASTER & SLAVE) Clock high to data out valid | PIC16 <b>C</b> 73A/74A<br>PIC16 <b>LC</b> 73A/74A | _      | _        | 80<br>100 | ns<br>ns   |  |

| 121          | Tckrf    | Clock out rise time and fall time                       |                                                   | _      |          | 45        | ns         |  |

| 122          | Tdtrf    | (Master Mode)  Data out rise time and fall time         | PIC16 <b>LC</b> 73A/74A<br>PIC16 <b>C</b> 73A/74A | _<br>_ | <u> </u> | 50<br>45  | ns<br>ns   |  |

|              |          |                                                         | PIC16 <b>LC</b> 73A/74A                           | _      | _        | 50        | ns         |  |

<sup>†:</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

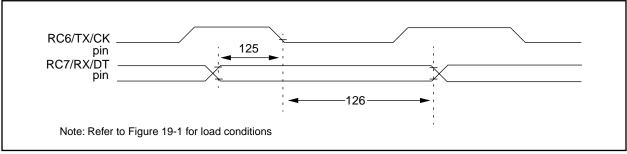

## FIGURE 19-13: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 19-12: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                   | Min | Тур† | Max | Units | Conditions |

|------------------|----------|------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE) Data setup before CK ↓ (DT setup time) | 15  |      |     | ns    |            |

| 126              | TckL2dtl | Data hold after CK ↓ (DT hold time)                              | 15  | _    | _   | ns    |            |

<sup>†:</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### 20.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

1. TppS2ppS 3. Tcc:st (I<sup>2</sup>C specifications only)

2. TppS 4. Ts (I<sup>2</sup>C specifications only)

T

F

Frequency

T

Time

Lowercase letters (pp) and their meanings:

| рр |          |     |          |

|----|----------|-----|----------|

| СС | CCP1     | osc | OSC1     |

| ck | CLKOUT   | rd  | RD       |

| cs | CS       | rw  | RD or WR |

| di | SDI      | sc  | SCK      |

| do | SDO      | SS  | SS       |

| dt | Data in  | t0  | T0CKI    |

| io | I/O port | t1  | T1CKI    |

| mc | MCLR     | wr  | WR       |

Uppercase letters and their meanings:

| S                     |                        |      |              |

|-----------------------|------------------------|------|--------------|

| F                     | Fall                   | Р    | Period       |

| Н                     | High                   | R    | Rise         |

| I                     | Invalid (Hi-impedance) | V    | Valid        |

| L                     | Low                    | Z    | Hi-impedance |

| I <sup>2</sup> C only |                        |      |              |

| AA                    | output access          | High | High         |

| BUF                   | Bus free               | Low  | Low          |

Tcc:st (I<sup>2</sup>C specifications only)

| CC  |                 |     |                |

|-----|-----------------|-----|----------------|

| HD  | Hold            | SU  | Setup          |

| ST  |                 |     |                |

| DAT | DATA input hold | STO | STOP condition |

| STA | START condition |     |                |

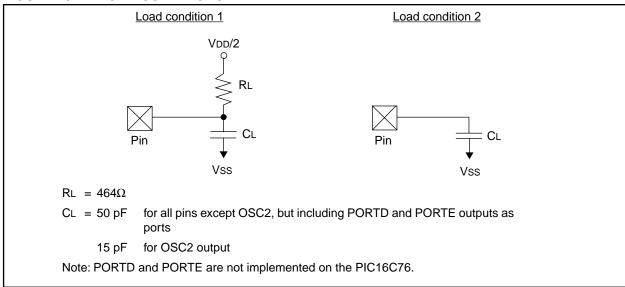

#### FIGURE 20-1: LOAD CONDITIONS

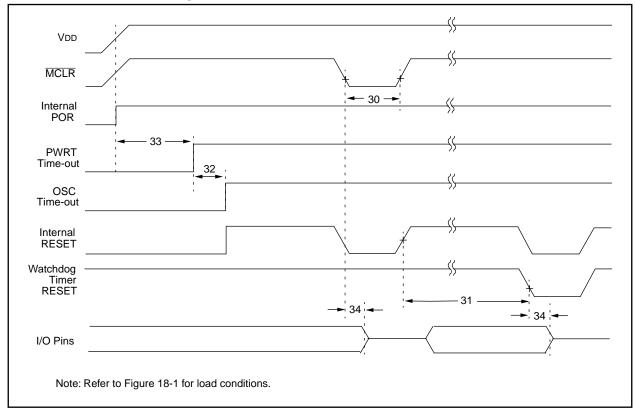

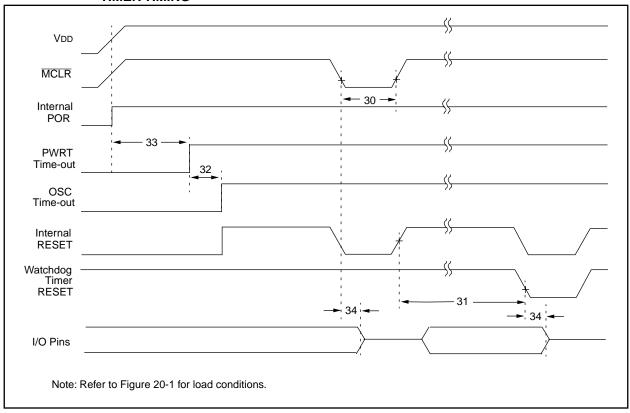

FIGURE 20-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

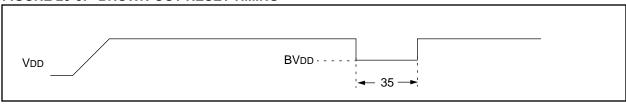

FIGURE 20-5: BROWN-OUT RESETTIMING

TABLE 20-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†     | Max | Units | Conditions                                         |

|------------------|-------|--------------------------------------------------------|-----|----------|-----|-------|----------------------------------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                 | 2   | _        | _   | μs    | $VDD = 5V, -40^{\circ}C \text{ to } +125^{\circ}C$ |

| 31*              | Twdt  | Watchdog Timer Time-out Period (No Prescaler)          | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +125°C                          |

| 32               | Tost  | Oscillation Start-up Timer Period                      | _   | 1024Tosc | _   | _     | Tosc = OSC1 period                                 |

| 33*              | Tpwrt | Power up Timer Period                                  | 28  | 72       | 132 | ms    | $VDD = 5V, -40^{\circ}C \text{ to } +125^{\circ}C$ |

| 34               | Tıoz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | _   | _        | 2.1 | μs    |                                                    |

| 35               | TBOR  | Brown-out Reset pulse width                            | 100 | _        | _   | μs    | VDD ≤ BVDD (D005)                                  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

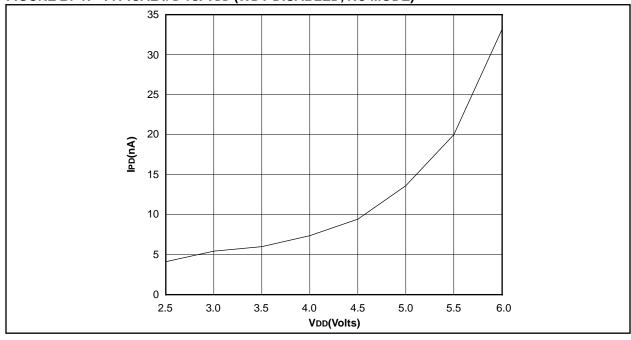

### 21.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed.

In some graphs or tables the data presented are outside specified operating range (i.e., outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

**Note:** The data presented in this section is a statistical summary of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at, 25°C, while 'max' or 'min' represents (mean +3σ) and (mean -3σ) respectively where σ is standard deviation.

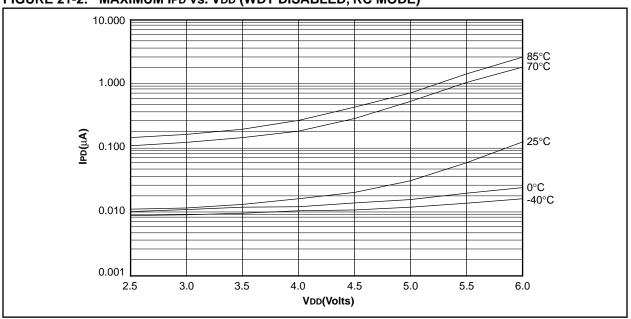

FIGURE 21-1: TYPICAL IPD vs. VDD (WDT DISABLED, RC MODE)

FIGURE 21-2: MAXIMUM IPD vs. VDD (WDT DISABLED, RC MODE)

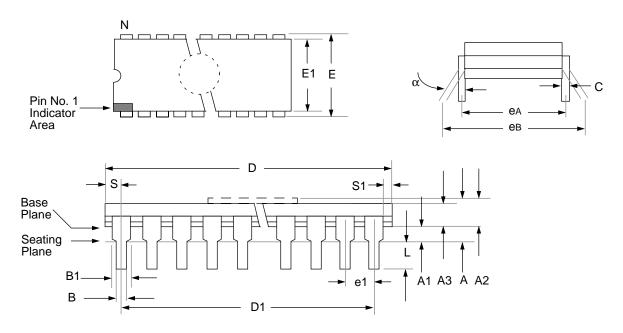

## 22.2 40-Lead Ceramic CERDIP Dual In-line with Window (600 mil) (JW)

|        | Package Group: Ceramic CERDIP Dual In-Line (CDP) |             |           |       |       |           |  |  |  |  |

|--------|--------------------------------------------------|-------------|-----------|-------|-------|-----------|--|--|--|--|

|        |                                                  | Millimeters | s I       |       |       |           |  |  |  |  |

| Symbol | Min                                              | Max         | Notes     | Min   | Max   | Notes     |  |  |  |  |

| α      | 0°                                               | 10°         |           | 0°    | 10°   |           |  |  |  |  |

| Α      | 4.318                                            | 5.715       |           | 0.170 | 0.225 |           |  |  |  |  |

| A1     | 0.381                                            | 1.778       |           | 0.015 | 0.070 |           |  |  |  |  |

| A2     | 3.810                                            | 4.699       |           | 0.150 | 0.185 |           |  |  |  |  |

| А3     | 3.810                                            | 4.445       |           | 0.150 | 0.175 |           |  |  |  |  |

| В      | 0.355                                            | 0.585       |           | 0.014 | 0.023 |           |  |  |  |  |

| B1     | 1.270                                            | 1.651       | Typical   | 0.050 | 0.065 | Typical   |  |  |  |  |

| С      | 0.203                                            | 0.381       | Typical   | 0.008 | 0.015 | Typical   |  |  |  |  |

| D      | 51.435                                           | 52.705      |           | 2.025 | 2.075 |           |  |  |  |  |

| D1     | 48.260                                           | 48.260      | Reference | 1.900 | 1.900 | Reference |  |  |  |  |

| E      | 15.240                                           | 15.875      |           | 0.600 | 0.625 |           |  |  |  |  |

| E1     | 12.954                                           | 15.240      |           | 0.510 | 0.600 |           |  |  |  |  |

| e1     | 2.540                                            | 2.540       | Reference | 0.100 | 0.100 | Reference |  |  |  |  |

| eA     | 14.986                                           | 16.002      | Typical   | 0.590 | 0.630 | Typical   |  |  |  |  |

| eВ     | 15.240                                           | 18.034      |           | 0.600 | 0.710 |           |  |  |  |  |

| L      | 3.175                                            | 3.810       |           | 0.125 | 0.150 |           |  |  |  |  |

| N      | 40                                               | 40          |           | 40    | 40    |           |  |  |  |  |

| S      | 1.016                                            | 2.286       |           | 0.040 | 0.090 |           |  |  |  |  |

| S1     | 0.381                                            | 1.778       |           | 0.015 | 0.070 |           |  |  |  |  |

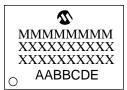

#### Package Marking Information (Cont'd)

44-Lead TQFP

### Example

| 0 | AABBCDE |

|---|---------|

|   |         |

| Legend: | MMM<br>XXX<br>AA<br>BB<br>C | Microchip part number information Customer specific information* Year code (last 2 digits of calender year) Week code (week of January 1 is week '01') Facility code of the plant at which wafer is manufactured. C = Chandler, Arizona, U.S.A. S = Tempe, Arizona, U.S.A. |

|---------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | D <sub>1</sub><br>E         | Mask revision number for microcontroller Assembly code of the plant or country of origin in which                                                                                                                                                                          |