Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | A/D 5x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

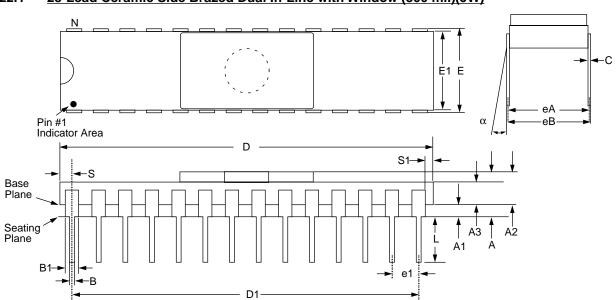

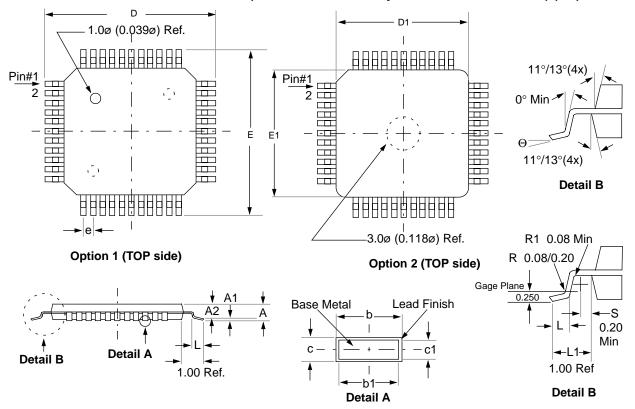

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c76-04e-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# FIGURE 4-4: PIC16C72 REGISTER FILE MAP

| File<br>Address   | 3                     |                     | File<br>Address |

|-------------------|-----------------------|---------------------|-----------------|

| 00h               | INDF <sup>(1)</sup>   | INDF <sup>(1)</sup> | 80h             |

| 01h               | TMR0                  | OPTION              | 81h             |

| 02h               | PCL                   | PCL                 |                 |

| 03h               | STATUS                | STATUS              |                 |

| 04h               | FSR                   | FSR                 |                 |

| 05h               | PORTA                 | TRISA               | 85h             |

| 06h               | PORTB                 | TRISB               | 86h             |

| 07h               | PORTC                 | TRISC               |                 |

| 08h               |                       |                     |                 |

| 09h               |                       |                     | 89h             |

| 0Ah               | PCLATH                | PCLATH              | 8Ah             |

| 0Bh               | INTCON                | INTCON              | 8Bh             |

| 0Ch               | PIR1                  | PIE1                | 8Ch             |

| 0Dh               |                       |                     | 8Dh             |

| 0Eh               | TMR1L                 | PCON                | 8Eh             |

| 0Fh               | TMR1H                 |                     | 8Fh             |

| 10h               | T1CON                 |                     | 90h             |

| 11h               | TMR2                  |                     | 91h             |

| 12h               | T2CON                 | PR2                 | 92h             |

| 13h               | SSPBUF                | SSPADD              | 93h             |

| 14h               | SSPCON                | SSPSTAT             |                 |

| 15h               | CCPR1L                |                     | 95h             |

| 16h               | CCPR1H                |                     | 96h             |

| 17h               | CCP1CON               |                     | 97h             |

| 18h               |                       |                     | 98h             |

| 19h               |                       |                     | 99h             |

| 1Ah               |                       |                     | 9Ah             |

| 1Bh               |                       |                     | 9Bh             |

| 1Ch               |                       |                     | 9Ch             |

| 1Dh               |                       |                     | 9Dh             |

| 1Eh               | ADRES                 |                     | 9Eh             |

| 1Fh               | ADCON0                | ADCON1              | 9Fh             |

| 20h               |                       |                     | A0h             |

|                   | General<br>Purpose    | General<br>Purpose  |                 |

|                   | Register              | Register            |                 |

|                   | U U                   |                     | BFh             |

|                   |                       |                     | C0h             |

|                   |                       |                     |                 |

|                   |                       |                     |                 |

|                   |                       |                     |                 |

| 7Fh               |                       |                     | FFh             |

|                   | Bank 0                | Bank 1              |                 |

|                   |                       |                     |                 |

|                   | nimplemented data     | a memory locations  | s, read as      |

| '0'.<br>Note 1: 1 | Not a physical regis  | stor                |                 |

|                   | tot a priysical regit | лот.                |                 |

|                   |                       |                     |                 |

#### FIGURE 4-5: PIC16C73/73A/74/74A REGISTER FILE MAP

|                | REGIST                                                        | ER FILE MA                     | F               |

|----------------|---------------------------------------------------------------|--------------------------------|-----------------|

| File<br>Addres | SS                                                            |                                | File<br>Address |

| 00h            | INDF <sup>(1)</sup>                                           | INDF <sup>(1)</sup>            | 80h             |

| 01h            | TMR0                                                          | OPTION                         |                 |

| 02h            | PCL                                                           | PCL                            | 82h             |

| 03h            | STATUS                                                        | STATUS                         | 83h             |

| 04h            | FSR                                                           | FSR                            |                 |

| 05h            | PORTA                                                         | TRISA                          | 85h             |

| 06h            | PORTB                                                         | TRISB                          | 86h             |

| 07h            | PORTC                                                         | TRISC                          |                 |

| 08h            | PORTD <sup>(2)</sup>                                          | TRISD <sup>(2)</sup>           |                 |

| 09h            | PORTE <sup>(2)</sup>                                          | TRISE <sup>(2)</sup>           | 89h             |

| 0Ah            | PCLATH                                                        | PCLATH                         | 8Ah             |

| 0Bh            | INTCON                                                        | INTCON                         | 8Bh             |

| 0Ch            | PIR1                                                          | PIE1                           | 8Ch             |

| 0Dh            | PIR2                                                          | PIE2                           | 8Dh             |

| 0Eh            | TMR1L                                                         | PCON                           | 8Eh             |

| 0Fh            | TMR1H                                                         |                                | 8Fh             |

| 10h            | T1CON                                                         |                                | 90h             |

| 11h            | TMR2                                                          |                                | 91h             |

| 12h            | T2CON                                                         | PR2                            |                 |

| 13h            | SSPBUF                                                        | SSPADD                         | 93h             |

| 14h            | SSPCON                                                        | SSPSTAT                        | 94h             |

| 15h            | CCPR1L                                                        |                                | 95h             |

| 16h            | CCPR1H                                                        |                                | 96h             |

| 17h            | CCP1CON                                                       |                                | 97h             |

| 18h            | RCSTA                                                         | TXSTA                          |                 |

| 19h            | TXREG                                                         | SPBRG                          | 99h             |

| 1Ah            | RCREG                                                         |                                | 9Ah             |

| 1Bh            | CCPR2L                                                        |                                | 9Bh             |

| 1Ch            | CCPR2H                                                        |                                | 9Ch             |

| 1Dh            | CCP2CON                                                       |                                | 9Dh             |

| 1Eh            | ADRES                                                         |                                | 9Eh             |

| 1Fh            | ADCON0                                                        | ADCON1                         | 9Fh             |

| 20h            |                                                               |                                | A0h             |

|                | General<br>Purpose<br>Register                                | General<br>Purpose<br>Register |                 |

| 7Fh            |                                                               |                                | FFh             |

|                | Bank 0                                                        | Bank 1                         |                 |

|                | Unimplemented da                                              | -                              | ons, read as    |

| Note 1:<br>2:  | Not a physical reg<br>These registers ar<br>mented on the PIC | e not physically               |                 |

|                |                                                               |                                |                 |

## 4.2.2.2 OPTION REGISTER

## Applicable Devices

72 73 73A 74 74A 76 77

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the External INT Interrupt, TMR0, and the weak pull-ups on PORTB.

## FIGURE 4-8: OPTION REGISTER (ADDRESS 81h, 181h)

| R/W-1    | R/W-1                                                | R/W-1                                                                                                                                                                          | R/W-1               | R/W-1     | R/W-1       | R/W-1       | R/W-1 |                                                                                       |  |  |  |  |

|----------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------|-------------|-------------|-------|---------------------------------------------------------------------------------------|--|--|--|--|

| RBPU     | INTEDG                                               | TOCS                                                                                                                                                                           | T0SE                | PSA       | PS2         | PS1         | PS0   | R = Readable bit                                                                      |  |  |  |  |

| bit7     |                                                      |                                                                                                                                                                                |                     |           |             |             | bitO  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |  |  |  |

| bit 7:   | <b>RBPU</b> : PO<br>1 = PORTE<br>0 = PORTE           | 3 pull-ups                                                                                                                                                                     | s are disat         | bled      | vidual port | latch value | es    |                                                                                       |  |  |  |  |

| bit 6:   | INTEDG: In<br>1 = Interru<br>0 = Interru             | pt on risir                                                                                                                                                                    | ng edge of          | f RB0/INT |             |             |       |                                                                                       |  |  |  |  |

| bit 5:   | 1 = Transit                                          | 0 = Interrupt on falling edge of RB0/INT pin<br><b>T0CS</b> : TMR0 Clock Source Select bit<br>1 = Transition on RA4/T0CKI pin<br>0 = Internal instruction cycle clock (CLKOUT) |                     |           |             |             |       |                                                                                       |  |  |  |  |

| bit 4:   | 1 = Increm                                           | <b>TOSE</b> : TMR0 Source Edge Select bit<br>1 = Increment on high-to-low transition on RA4/T0CKI pin<br>0 = Increment on low-to-high transition on RA4/T0CKI pin              |                     |           |             |             |       |                                                                                       |  |  |  |  |

| bit 3:   | 1 = Presca                                           | <ul> <li>PSA: Prescaler Assignment bit</li> <li>1 = Prescaler is assigned to the WDT</li> <li>0 = Prescaler is assigned to the Timer0 module</li> </ul>                        |                     |           |             |             |       |                                                                                       |  |  |  |  |

| bit 2-0: | PS2:PS0:                                             | Prescale                                                                                                                                                                       | r Rate Sel          | ect bits  |             |             |       |                                                                                       |  |  |  |  |

|          | Bit Value                                            | TMR0 R                                                                                                                                                                         | ate WD              | Γ Rate    |             |             |       |                                                                                       |  |  |  |  |

|          | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:12<br>1:25                                                                                                                      | 2 1:<br>1:<br>28 1: | 2<br>4    |             |             |       |                                                                                       |  |  |  |  |

## FIGURE 4-11: PIE1 REGISTER PIC16C73/73A/74/74A/76/77 (ADDRESS 8Ch)

| PSPIE <sup>(1)</sup> | ADIE      | RCIE                                     | TXIE        | SSPIE       | CCP1IE      | TMR2IE       | TMR1IE    | R      | = Readable bit                                                                                           |

|----------------------|-----------|------------------------------------------|-------------|-------------|-------------|--------------|-----------|--------|----------------------------------------------------------------------------------------------------------|

| bit7                 | 1         |                                          |             |             |             |              | bit0      | U      | <ul> <li>Writable bit</li> <li>Unimplemented bit,<br/>read as '0'</li> <li>Value at POR reset</li> </ul> |

| bit 7:               | 1 = Enabl | Parallel S<br>es the PS<br>les the PS    | P read/wr   | te interrup |             | Enable bit   |           |        |                                                                                                          |

| bit 6:               | 1 = Enabl | D Converte<br>les the A/E<br>les the A/I | ) interrupt |             | it          |              |           |        |                                                                                                          |

| bit 5:               | 1 = Enabl | ART Rece<br>es the US<br>les the US      | ART recei   | ve interrup | ot          |              |           |        |                                                                                                          |

| bit 4:               | 1 = Enabl | ART Trans<br>es the US<br>les the US     | ART trans   | mit interru | ıpt         |              |           |        |                                                                                                          |

| bit 3:               | 1 = Enabl | ynchronou<br>es the SS<br>les the SS     | P interrup  | t           | pt Enable b | bit          |           |        |                                                                                                          |

| bit 2:               | 1 = Enabl | CCP1 Inte<br>les the CC<br>les the CC    | P1 interru  | pt          |             |              |           |        |                                                                                                          |

| bit 1:               | 1 = Enabl | TMR2 to F<br>es the TM<br>les the TM     | R2 to PR2   | 2 match in  | •           |              |           |        |                                                                                                          |

| bit 0:               | 1 = Enabl | TMR1 Ove<br>es the TM<br>les the TM      | R1 overflo  | w interrup  | ot          |              |           |        |                                                                                                          |

| Note 1:              | PIC16C73  |                                          |             |             |             | Slave Port i | mplemente | ed, tl | his bit location is reserved                                                                             |

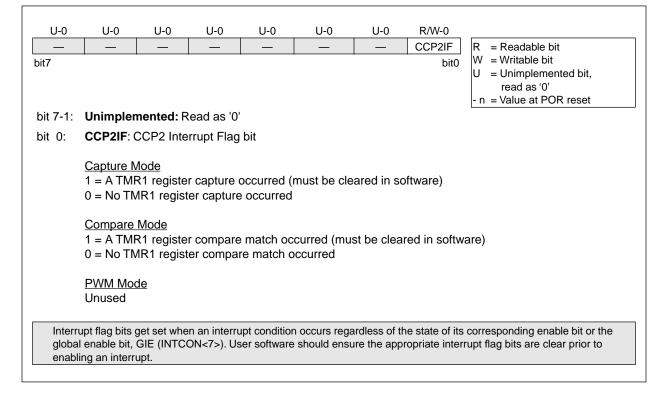

4.2.2.7 PIR2 REGISTER

Applicable Devices

72 73 73A 74 74A 76 77

This register contains the CCP2 interrupt flag bit.

Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## FIGURE 4-15: PIR2 REGISTER (ADDRESS 0Dh)

## 6.0 OVERVIEW OF TIMER MODULES

Applicable Devices

The PIC16C72, PIC16C73/73A, PIC16C74/74A, PIC16C76/77 each have three timer modules.

Each module can generate an interrupt to indicate that an event has occurred (i.e. timer overflow). Each of these modules is explained in full detail in the following sections. The timer modules are:

- Timer0 Module (Section 7.0)

- Timer1 Module (Section 8.0)

- Timer2 Module (Section 9.0)

### 6.1 <u>Timer0 Overview</u> Applicable Devices 72|73|73A|74|74A|76|77

The Timer0 module is a simple 8-bit overflow counter. The clock source can be either the internal system clock (Fosc/4) or an external clock. When the clock source is an external clock, the Timer0 module can be selected to increment on either the rising or falling edge.

The Timer0 module also has a programmable prescaler option. This prescaler can be assigned to either the Timer0 module or the Watchdog Timer. Bit PSA (OPTION<3>) assigns the prescaler, and bits PS2:PS0 (OPTION<2:0>) determine the prescaler value. Timer0 can increment at the following rates: 1:1 (when prescaler assigned to Watchdog timer), 1:2, 1:4, 1:8, 1:16, 1:32, 1:64, 1:128, and 1:256 (Timer0 only).

Synchronization of the external clock occurs after the prescaler. When the prescaler is used, the external clock frequency may be higher then the device's frequency. The maximum frequency is 50 MHz, given the high and low time requirements of the clock.

#### 6.2 <u>Timer1 Overview</u> Applicable Devices 72 73 73 74 74 76 77

Timer1 is a 16-bit timer/counter. The clock source can be either the internal system clock (Fosc/4), an external clock, or an external crystal. Timer1 can operate as either a timer or a counter. When operating as a counter (external clock source), the counter can either operate synchronized to the device or asynchronously to the device. Asynchronous operation allows Timer1 to operate during sleep, which is useful for applications that require a real-time clock as well as the power savings of SLEEP mode.

Timer1 also has a prescaler option which allows Timer1 to increment at the following rates: 1:1, 1:2, 1:4, and 1:8. Timer1 can be used in conjunction with the Capture/Compare/PWM module. When used with a CCP module, Timer1 is the time-base for 16-bit Capture or the 16-bit Compare and must be synchronized to the device.

## 6.3 <u>Timer2 Overview</u> Applicable Devices

|    |    |     |    | evic |    | _  |

|----|----|-----|----|------|----|----|

| 72 | 73 | 73A | 74 | 74A  | 76 | 77 |

Timer2 is an 8-bit timer with a programmable prescaler and postscaler, as well as an 8-bit period register (PR2). Timer2 can be used with the CCP1 module (in PWM mode) as well as the Baud Rate Generator for the Synchronous Serial Port (SSP). The prescaler option allows Timer2 to increment at the following rates: 1:1, 1:4, 1:16.

The postscaler allows the TMR2 register to match the period register (PR2) a programmable number of times before generating an interrupt. The postscaler can be programmed from 1:1 to 1:16 (inclusive).

#### 6.4 <u>CCP Overview</u>

Applicable Devices

72

73

73

74

74

76

77

The CCP module(s) can operate in one of these three modes: 16-bit capture, 16-bit compare, or up to 10-bit Pulse Width Modulation (PWM).

Capture mode captures the 16-bit value of TMR1 into the CCPRxH:CCPRxL register pair. The capture event can be programmed for either the falling edge, rising edge, fourth rising edge, or the sixteenth rising edge of the CCPx pin.

Compare mode compares the TMR1H:TMR1L register pair to the CCPRxH:CCPRxL register pair. When a match occurs an interrupt can be generated, and the output pin CCPx can be forced to given state (High or Low), TMR1 can be reset (CCP1), or TMR1 reset and start A/D conversion (CCP2). This depends on the control bits CCPxM3:CCPxM0.

PWM mode compares the TMR2 register to a 10-bit duty cycle register (CCPRxH:CCPRxL<5:4>) as well as to an 8-bit period register (PR2). When the TMR2 register = Duty Cycle register, the CCPx pin will be forced low. When TMR2 = PR2, TMR2 is cleared to 00h, an interrupt can be generated, and the CCPx pin (if an output) will be forced high.

NOTES:

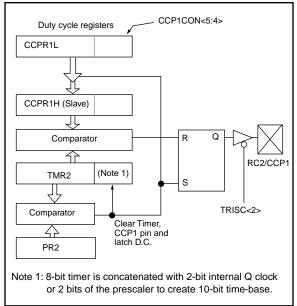

#### 10.3 PWM Mode

Applicable Devices

In Pulse Width Modulation (PWM) mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

Note: Clearing the CCP1CON register will force the CCP1 PWM output latch to the default low level. This is not the PORTC I/O data latch.

Figure 10-4 shows a simplified block diagram of the CCP module in PWM mode.

For a step by step procedure on how to set up the CCP module for PWM operation, see Section 10.3.3.

#### FIGURE 10-4: SIMPLIFIED PWM BLOCK DIAGRAM

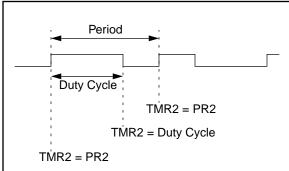

A PWM output (Figure 10-5) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### FIGURE 10-5: PWM OUTPUT

#### 10.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

PWM period = [(PR2) + 1] • 4 • TOSC • (TMR2 prescale value)

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

| Note: | The Timer2 postscaler (see Section 9.1) is   |

|-------|----------------------------------------------|

|       | not used in the determination of the PWM     |

|       | frequency. The postscaler could be used to   |

|       | have a servo update rate at a different fre- |

|       | quency than the PWM output.                  |

#### 10.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available: the CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

#### PWM duty cycle = (CCPR1L:CCP1CON<5:4>) • Tosc • (TMR2 prescale value)

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2 concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

Maximum PWM resolution (bits) for a given PWM frequency:

$$= \frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log(2)} \quad \text{bits}$$

Note: If the PWM duty cycle value is longer than the PWM period the CCP1 pin will not be cleared.

٦

## FIGURE 11-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)

| R/W-0    | R/W-0                                                                | R/W-0                                                                   | R/W-0                                                                            | R/W-0                                                                        | R/W-0                                    | R/W-0                    | R/W-0                        |                                                                                                                           |

|----------|----------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------|--------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| WCOL     | SSPOV                                                                | SSPEN                                                                   | CKP                                                                              | SSPM3                                                                        | SSPM2                                    | SSPM1                    | SSPM0                        | R = Readable bit                                                                                                          |

| bit7     |                                                                      |                                                                         |                                                                                  |                                                                              |                                          |                          | bit0                         | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset                                      |

| bit 7:   | WCOL: W                                                              | rite Collisio                                                           | n Detect l                                                                       | oit                                                                          |                                          |                          |                              |                                                                                                                           |

|          | 1 = The S                                                            | SPBUF reg                                                               | jister is wr                                                                     |                                                                              | it is still tr                           | ansmitting               | the previou                  | us word                                                                                                                   |

| bit 6:   | SSPOV: R                                                             | eceive Ove                                                              | erflow Det                                                                       | ect bit                                                                      |                                          |                          |                              |                                                                                                                           |

|          | the data ir<br>BUF, even                                             | byte is rece<br>SSPSR re<br>if only train<br>new rece                   | egister is I                                                                     | ost. Overfl<br>data, to av                                                   | ow can on<br>oid setting                 | ly occur in<br>overflow. | slave mod<br>In master       | revious data. In case of overflow<br>e. The user must read the SSP<br>mode the overflow bit is not se<br>SSPBUF register. |

|          | In I <sup>2</sup> C mod                                              | <u>de</u>                                                               |                                                                                  |                                                                              |                                          |                          |                              |                                                                                                                           |

|          | 1 = A byte<br>in transmit<br>0 = No ove                              | mode. SS                                                                |                                                                                  |                                                                              |                                          |                          |                              | us byte. SSPOV is a "don't care                                                                                           |

| bit 5:   | SSPEN: S                                                             | ynchronou                                                               | s Serial P                                                                       | ort Enable                                                                   | bit                                      |                          |                              |                                                                                                                           |

|          | $\frac{\text{In SPI model}}{1 = \text{Enable}}$ $0 = \text{Disable}$ | es serial po                                                            |                                                                                  |                                                                              |                                          |                          | s serial por<br>pins         | t pins                                                                                                                    |

|          | 0 = Disabl                                                           | es the seria                                                            | ort and co                                                                       | nfigures th                                                                  | nese pins a                              | as I/O port              | pins                         | ial port pins<br>s input or output.                                                                                       |

| bit 4:   | CKP: Cloc                                                            | k Polarity                                                              | Select bit                                                                       |                                                                              |                                          |                          |                              |                                                                                                                           |

|          |                                                                      | ate for cloc                                                            |                                                                                  |                                                                              |                                          |                          |                              | receive on rising edge.<br>ceive on falling edge.                                                                         |

|          | $\frac{\ln l^2 C \mod SCK \text{ relea}}{1 = \text{Enable}}$         | se control<br>e clock                                                   | -11                                                                              |                                                                              | 4                                        |                          | . (: )                       |                                                                                                                           |

|          | 0 = Holds                                                            |                                                                         |                                                                                  | , ,                                                                          |                                          |                          | o time)                      |                                                                                                                           |

| bit 3-0: | 0001 = SF<br>0010 = SF<br>0011 = SF<br>0100 = SF<br>0101 = SF        | PI master n<br>PI master n<br>PI master n<br>PI master n<br>PI slave mo | node, cloc<br>node, cloc<br>node, cloc<br>node, cloc<br>ode, clock<br>ode, clock | k = Fosc/4<br>k = Fosc/1<br>k = Fosc/6<br>k = TMR2<br>= SCK pir<br>= SCK pir | l<br>6<br>64<br>output/2<br>1. SS pin co | ontrol enal              |                              | n be used as I/O pin.                                                                                                     |

|          | $0111 = I^{2}(0)$<br>$1011 = I^{2}(0)$<br>$1110 = I^{2}(0)$          | C slave mo<br>C firmware<br>C slave mo                                  | de, 10-bit<br>controlled<br>de, 7-bit a                                          | address<br>I Master M<br>ddress wi                                           | th start an                              | d stop bit i             | nterrupts er<br>interrupts o |                                                                                                                           |

Г

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH. (Section 12.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC, and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

### TABLE 12-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address | Name  | Bit 7                | Bit 6    | Bit 5     | Bit 4     | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|----------------------|----------|-----------|-----------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF     | RCIF      | TXIF      | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h     | RCSTA | SPEN                 | RX9      | SREN      | CREN      |       | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 1Ah     | RCREG | USART Rec            | eive Reg | 0000 0000 | 0000 0000 |       |        |        |        |                          |                                 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE     | RCIE      | TXIE      | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h     | TXSTA | CSRC                 | TX9      | TXEN      | SYNC      |       | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h     | SPBRG | Baud Rate (          | Generato | 0000 0000 | 0000 0000 |       |        |        |        |                          |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

## 13.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

# Applicable Devices

The analog-to-digital (A/D) converter module has five inputs for the PIC16C72/73/73A/76, and eight for the PIC16C74/74A/77.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the RA3/AN3/VREF pin. The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

The ADCON0 register, shown in Figure 13-1, controls the operation of the A/D module. The ADCON1 register, shown in Figure 13-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/O.

| R/W-0    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0                                                                                                 | R/W-0                                                                            | R/W-0      | R/W-0         | U-0         | R/W-0     |                                                                                       |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------|---------------|-------------|-----------|---------------------------------------------------------------------------------------|--|--|

| ADCS1    | ADCS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CHS2                                                                                                  | CHS1                                                                             | CHS0       | GO/DONE       | _           | ADON      | R = Readable bit                                                                      |  |  |

| bit7     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |                                                                                  |            |               |             | bit0      | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |  |

| bit 7-6: | 00 = Fos<br>01 = Fos<br>10 = Fos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | c/2<br>c/8<br>c/32                                                                                    |                                                                                  |            | Select bits   | ·)          |           |                                                                                       |  |  |

| bit 5-3: | 000 = cha<br>001 = cha<br>010 = cha<br>011 = cha<br>100 = cha<br>101 = cha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | annel 0, (F<br>annel 1, (F<br>annel 2, (F<br>annel 3, (F<br>annel 4, (F<br>annel 5, (F<br>annel 6, (F | RĂO/ANO)<br>RA1/AN1)<br>RA2/AN2)<br>RA3/AN3)<br>RA5/AN4)<br>RE0/AN5)<br>RE0/AN5) | [1)        | ts            |             |           |                                                                                       |  |  |

| bit 2:   | GO/DON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | E: A/D Co                                                                                             | nversion S                                                                       | Status bit |               |             |           |                                                                                       |  |  |

|          | $\frac{\text{If ADON} = 1}{1 = A/D \text{ conversion in progress (setting this bit starts the A/D conversion)}} \\ 0 = A/D \text{ conversion not in progress (This bit is automatically cleared by hardware when the A/D conversion is complete)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                       |                                                                                  |            |               |             |           |                                                                                       |  |  |

| bit 1:   | Unimpler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | nented: F                                                                                             | Read as '0                                                                       | ,          |               |             |           |                                                                                       |  |  |

| bit 0:   | <b>ADON</b> : $A/A = A/D c $ | onverter n                                                                                            |                                                                                  |            | d consumes no | o operating | g current |                                                                                       |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |                                                                                  |            |               |             |           |                                                                                       |  |  |

### FIGURE 13-1: ADCON0 REGISTER (ADDRESS 1Fh)

#### 13.4 A/D Conversions

Applicable Devices

72

73

73

74

74

76

77

Example 13-2 shows how to perform an A/D conversion. The RA pins are configured as analog inputs. The analog reference (VREF) is the device VDD. The A/D interrupt is enabled, and the A/D conversion clock is FRC. The conversion is performed on the RA0 pin (channel 0).

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRES register will NOT be updated with the partially completed A/D conversion sample. That is, the ADRES register will continue to contain the value of the last completed conversion (or the last value written to the ADRES register). After the A/D conversion is aborted, a 2TAD wait is required before the next acquisition is started. After this 2TAD wait, an acquisition is automatically started on the selected channel.

## EXAMPLE 13-2: A/D CONVERSION

;

; ;

| BSF       | STATUS,  | RP0           | ;   | Select Bank 1                                       |

|-----------|----------|---------------|-----|-----------------------------------------------------|

| BCF       | STATUS,  | RP1           | ;   | PIC16C76/77 only                                    |

| CLRF      | ADCON1   |               | ;   | Configure A/D inputs                                |

| BSF       | PIE1,    | ADIE          | ;   | Enable A/D interrupts                               |

| BCF       | STATUS,  | RP0           | ;   | Select Bank 0                                       |

| MOVLW     | 0xC1     |               | ;   | RC Clock, A/D is on, Channel 0 is selected          |

| MOVWF     | ADCON0   |               | ;   |                                                     |

| BCF       | PIR1,    | ADIF          | ;   | Clear A/D interrupt flag bit                        |

| BSF       | INTCON,  | PEIE          | ;   | Enable peripheral interrupts                        |

| BSF       | INTCON,  | GIE           | ;   | Enable all interrupts                               |

| Enguro th | at the m | oquirod gamp  | 14. | ng time for the selected input channel has elapsed. |

|           |          | on may be sta |     |                                                     |

| BSF | ADCON0, | GO | ; | ; Start A/D Conversion                              |  |

|-----|---------|----|---|-----------------------------------------------------|--|

| :   |         |    | ; | ; The ADIF bit will be set and the GO/DONE bit      |  |

| :   |         |    | ; | ; is cleared upon completion of the A/D Conversion. |  |

# PIC16C7X

| Register | Applicable Devices |    |     |    | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT<br>or<br>Interrupt |           |           |           |

|----------|--------------------|----|-----|----|------------------------------------|--------------------------|------------------------------------|-----------|-----------|-----------|

| SSPADD   | 72                 | 73 | 73A | 74 | 74A                                | 76                       | 77                                 | 0000 0000 | 0000 0000 | uuuu uuuu |

| SSPSTAT  | 72                 | 73 | 73A | 74 | 74A                                | 76                       | 77                                 | 00 0000   | 00 0000   | uu uuuu   |

| TXSTA    | 72                 | 73 | 73A | 74 | 74A                                | 76                       | 77                                 | 0000 -010 | 0000 -010 | uuuu -uuu |

| SPBRG    | 72                 | 73 | 73A | 74 | 74A                                | 76                       | 77                                 | 0000 0000 | 0000 0000 | uuuu uuuu |

| ADCON1   | 72                 | 73 | 73A | 74 | 74A                                | 76                       | 77                                 | 000       | 000       | uuu       |

#### TABLE 14-8: INITIALIZATION CONDITIONS FOR ALL REGISTERS (Cont.'d)

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 14-7 for reset value for specific condition.

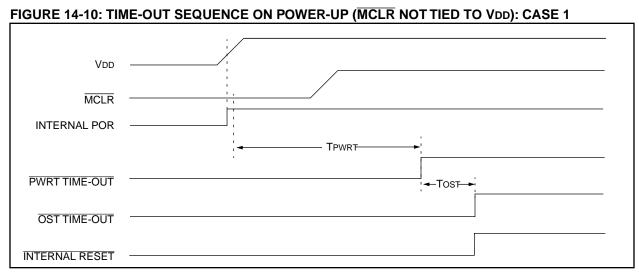

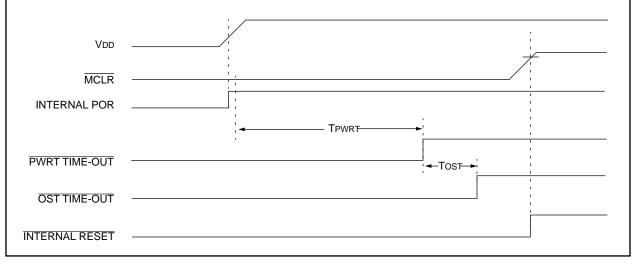

FIGURE 14-11: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

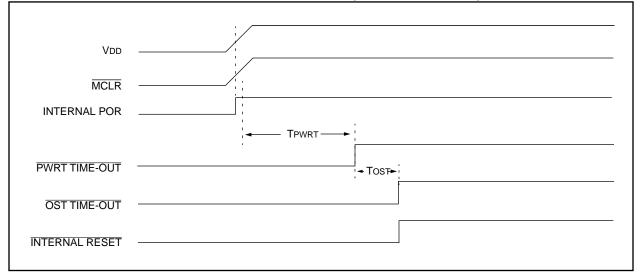

#### FIGURE 14-12: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

| GOTO              | Uncondi                                                            | tional Br                           | anch                                 |                  | INCF              | Increment f                                                                   |                             |                      |                      |

|-------------------|--------------------------------------------------------------------|-------------------------------------|--------------------------------------|------------------|-------------------|-------------------------------------------------------------------------------|-----------------------------|----------------------|----------------------|

| Syntax:           | [ label ]                                                          | GOTO                                | k                                    |                  | Syntax:           | [label] INC                                                                   | f,d                         |                      |                      |

| Operands:         | $0 \le k \le 20$                                                   | 047                                 |                                      |                  | Operands:         | $0 \leq f \leq 127$                                                           |                             |                      |                      |

| Operation:        | $k \rightarrow PC <$                                               | 10:0>                               |                                      |                  |                   | d ∈ [0,1]                                                                     |                             |                      |                      |

|                   | PCLATH-                                                            | <4:3> →                             | PC<12:11                             | >                | Operation:        | (f) + 1 $\rightarrow$ (des                                                    | inatio                      | n)                   |                      |

| Status Affected:  | None                                                               |                                     |                                      |                  | Status Affected:  | Z                                                                             |                             |                      |                      |

| Encoding:         | 10                                                                 | 1kkk                                | kkkk                                 | kkkk             | Encoding:         | 00 101                                                                        | 0 d                         | lfff                 | ffff                 |

| Description:      | GOTO is an<br>eleven bit<br>into PC bit<br>PC are loa<br>GOTO is a | immediate<br>s <10:0>.<br>ided from | value is lo<br>The upper<br>PCLATH<4 | bits of<br>1:3>. | Description:      | The contents of<br>mented. If 'd' is<br>the W register. I<br>placed back in r | ) the re<br>'d' is <i>'</i> | esult is<br>1 the re | placed in            |

| Words:            | 1                                                                  |                                     |                                      |                  | Words:            | 1                                                                             |                             |                      |                      |

| Cycles:           | 2                                                                  |                                     |                                      |                  | Cycles:           | 1                                                                             |                             |                      |                      |

| Q Cycle Activity: | Q1                                                                 | Q2                                  | Q3                                   | Q4               | Q Cycle Activity: | Q1 Q1                                                                         | 2                           | Q3                   | Q4                   |

| 1st Cycle         | Decode                                                             | Read<br>literal 'k'                 | Process<br>data                      | Write to<br>PC   |                   | Decode Rea<br>regis                                                           |                             | rocess<br>data       | Write to destination |

| 2nd Cycle         | No-<br>Operation                                                   | No-<br>Operation                    | No-<br>Operation                     | No-<br>Operation |                   |                                                                               |                             |                      |                      |

|                   |                                                                    |                                     |                                      |                  | Example           | INCF CN                                                                       | , 1                         |                      |                      |