Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuns                     |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | A/D 5x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c76-04i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## FIGURE 4-4: PIC16C72 REGISTER FILE MAP

| File<br>Address   | 3                     |                     | File<br>Address |

|-------------------|-----------------------|---------------------|-----------------|

| 00h               | INDF <sup>(1)</sup>   | INDF <sup>(1)</sup> | 80h             |

| 01h               | TMR0                  | OPTION              | 81h             |

| 02h               | PCL                   | PCL                 |                 |

| 03h               | STATUS                | STATUS              |                 |

| 04h               | FSR                   | FSR                 |                 |

| 05h               | PORTA                 | TRISA               | 85h             |

| 06h               | PORTB                 | TRISB               | 86h             |

| 07h               | PORTC                 | TRISC               |                 |

| 08h               |                       |                     |                 |

| 09h               |                       |                     | 89h             |

| 0Ah               | PCLATH                | PCLATH              | 8Ah             |

| 0Bh               | INTCON                | INTCON              | 8Bh             |

| 0Ch               | PIR1                  | PIE1                | 8Ch             |

| 0Dh               |                       |                     | 8Dh             |

| 0Eh               | TMR1L                 | PCON                | 8Eh             |

| 0Fh               | TMR1H                 |                     | 8Fh             |

| 10h               | T1CON                 |                     | 90h             |

| 11h               | TMR2                  |                     | 91h             |

| 12h               | T2CON                 | PR2                 | 92h             |

| 13h               | SSPBUF                | SSPADD              | 93h             |

| 14h               | SSPCON                | SSPSTAT             |                 |

| 15h               | CCPR1L                |                     | 95h             |

| 16h               | CCPR1H                |                     | 96h             |

| 17h               | CCP1CON               |                     | 97h             |

| 18h               |                       |                     | 98h             |

| 19h               |                       |                     | 99h             |

| 1Ah               |                       |                     | 9Ah             |

| 1Bh               |                       |                     | 9Bh             |

| 1Ch               |                       |                     | 9Ch             |

| 1Dh               |                       |                     | 9Dh             |

| 1Eh               | ADRES                 |                     | 9Eh             |

| 1Fh               | ADCON0                | ADCON1              | 9Fh             |

| 20h               |                       |                     | A0h             |

|                   | General<br>Purpose    | General<br>Purpose  |                 |

|                   | Register              | Register            |                 |

|                   | U U                   |                     | BFh             |

|                   |                       |                     | C0h             |

|                   |                       |                     |                 |

|                   |                       |                     |                 |

|                   |                       |                     |                 |

| 7Fh               |                       |                     | FFh             |

|                   | Bank 0                | Bank 1              |                 |

|                   |                       |                     |                 |

|                   | nimplemented data     | a memory locations  | s, read as      |

| '0'.<br>Note 1: 1 | Not a physical regis  | stor                |                 |

|                   | tot a priysical regit | лот.                |                 |

|                   |                       |                     |                 |

#### FIGURE 4-5: PIC16C73/73A/74/74A REGISTER FILE MAP

| File<br>Addres | SS                                                            | _                              | File<br>Address |  |  |  |

|----------------|---------------------------------------------------------------|--------------------------------|-----------------|--|--|--|

| 00h            | INDF <sup>(1)</sup>                                           | INDF <sup>(1)</sup>            | 80h             |  |  |  |

| 01h            | TMR0                                                          | OPTION                         |                 |  |  |  |

| 02h            | PCL                                                           | PCL                            | 82h             |  |  |  |

| 03h            | STATUS                                                        | STATUS                         | 83h             |  |  |  |

| 04h            | FSR                                                           | FSR                            |                 |  |  |  |

| 05h            | PORTA                                                         | TRISA                          | 85h             |  |  |  |

| 06h            | PORTB                                                         | TRISB                          | 86h             |  |  |  |

| 07h            | PORTC                                                         | TRISC                          |                 |  |  |  |

| 08h            | PORTD <sup>(2)</sup>                                          | TRISD <sup>(2)</sup>           |                 |  |  |  |

| 09h            | PORTE <sup>(2)</sup>                                          | TRISE <sup>(2)</sup>           | 89h             |  |  |  |

| 0Ah            | PCLATH                                                        | PCLATH                         | 8Ah             |  |  |  |

| 0Bh            | INTCON                                                        | INTCON                         | 8Bh             |  |  |  |

| 0Ch            | PIR1                                                          | PIE1                           | 8Ch             |  |  |  |

| 0Dh            | PIR2                                                          | PIE2                           | 8Dh             |  |  |  |

| 0Eh            | TMR1L                                                         | PCON                           | 8Eh             |  |  |  |

| 0Fh            | TMR1H                                                         |                                | 8Fh             |  |  |  |

| 10h            | T1CON                                                         |                                | 90h             |  |  |  |

| 11h            | TMR2                                                          |                                | 91h             |  |  |  |

| 12h            | T2CON                                                         | PR2                            |                 |  |  |  |

| 13h            | SSPBUF                                                        | SSPADD                         | 93h             |  |  |  |

| 14h            | SSPCON                                                        | SSPSTAT                        | 94h             |  |  |  |

| 15h            | CCPR1L                                                        |                                | 95h             |  |  |  |

| 16h            | CCPR1H                                                        |                                | 96h             |  |  |  |

| 17h            | CCP1CON                                                       |                                | 97h             |  |  |  |

| 18h            | RCSTA                                                         | TXSTA                          |                 |  |  |  |

| 19h            | TXREG                                                         | SPBRG                          | 99h             |  |  |  |

| 1Ah            | RCREG                                                         |                                | 9Ah             |  |  |  |

| 1Bh            | CCPR2L                                                        |                                | 9Bh             |  |  |  |

| 1Ch            | CCPR2H                                                        |                                | 9Ch             |  |  |  |

| 1Dh            | CCP2CON                                                       |                                | 9Dh             |  |  |  |

| 1Eh            | ADRES                                                         |                                | 9Eh             |  |  |  |

| 1Fh            | ADCON0                                                        | ADCON1                         | 9Fh             |  |  |  |

| 20h            |                                                               |                                | A0h             |  |  |  |

|                | General<br>Purpose<br>Register                                | General<br>Purpose<br>Register |                 |  |  |  |

| 7Fh            |                                                               |                                | FFh             |  |  |  |

|                | Bank 0                                                        | Bank 1                         |                 |  |  |  |

|                | Unimplemented da                                              | -                              | ons, read as    |  |  |  |

| Note 1:<br>2:  | Not a physical reg<br>These registers ar<br>mented on the PIC | e not physically               |                 |  |  |  |

|                |                                                               |                                |                 |  |  |  |

| Address                   | Name    | Bit 7                | Bit 6              | Bit 5          | Bit 4           | Bit 3          | Bit 2           | Bit 1         | Bit 0    | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(2) |

|---------------------------|---------|----------------------|--------------------|----------------|-----------------|----------------|-----------------|---------------|----------|--------------------------|-------------------------------------|

| Bank 0                    |         |                      |                    |                |                 |                |                 |               |          |                          |                                     |

| 00h <sup>(4)</sup>        | INDF    | Addressing           | this location      | uses conten    | ts of FSR to a  | ddress data r  | nemory (not     | a physical re | egister) | 0000 0000                | 0000 0000                           |

| 01h                       | TMR0    | Timer0 mod           | lule's registe     | r              |                 |                |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 02h <sup>(4)</sup>        | PCL     | Program Co           | ounter's (PC)      | Least Signif   | icant Byte      |                |                 |               |          | 0000 0000                | 0000 0000                           |

| 03h <sup>(4)</sup>        | STATUS  | IRP <sup>(7)</sup>   | RP1 <sup>(7)</sup> | RP0            | TO              | PD             | Z               | DC            | С        | 0001 1xxx                | 000q quuu                           |

| 04h <b>(4)</b>            | FSR     | Indirect data        | a memory ad        | dress pointe   | er              |                |                 |               | •        | XXXX XXXX                | uuuu uuuu                           |

| 05h                       | PORTA   | _                    | _                  | PORTA Dat      | a Latch when    | written: POR   | TA pins wher    | read          |          | 0x 0000                  | 0u 0000                             |

| 06h                       | PORTB   | PORTB Dat            | a Latch whe        | n written: PC  | ORTB pins whe   | n read         |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 07h                       | PORTC   | PORTC Dat            | ta Latch whe       | n written: PC  | DRTC pins whe   | en read        |                 |               |          | XXXX XXXX                | uuuu uuuu                           |

| 08h <sup>(5)</sup>        | PORTD   | PORTD Dat            | a Latch whe        | n written: PC  | ORTD pins whe   | en read        |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 09h <b>(5)</b>            | PORTE   | _                    | _                  | _              | _               | _              | RE2             | RE1           | RE0      | xxx                      | uuu                                 |

| 0Ah <b>(1,4)</b>          | PCLATH  | _                    | _                  | _              | Write Buffer fo | or the upper t | 5 bits of the I | Program Cou   | unter    | 0 0000                   | 0 0000                              |

| 0Bh <b><sup>(4)</sup></b> | INTCON  | GIE                  | PEIE               | TOIE           | INTE            | RBIE           | T0IF            | INTF          | RBIF     | 0000 000x                | 0000 000u                           |

| 0Ch                       | PIR1    | PSPIF <sup>(3)</sup> | ADIF               | RCIF           | TXIF            | SSPIF          | CCP1IF          | TMR2IF        | TMR1IF   | 0000 0000                | 0000 0000                           |

| 0Dh                       | PIR2    | —                    | —                  | -              | -               | -              | —               | —             | CCP2IF   | 0                        | 0                                   |

| 0Eh                       | TMR1L   | Holding reg          | ister for the L    | east Signific  | ant Byte of the | e 16-bit TMR1  | l register      |               |          | xxxx xxxx                | uuuu uuuu                           |

| 0Fh                       | TMR1H   | Holding reg          | ister for the N    | lost Significa | ant Byte of the | 16-bit TMR1    | register        |               |          | XXXX XXXX                | uuuu uuuu                           |

| 10h                       | T1CON   | —                    | —                  | T1CKPS1        | T1CKPS0         | T1OSCEN        | <b>T1SYNC</b>   | TMR1CS        | TMR10N   | 00 0000                  | uu uuuu                             |

| 11h                       | TMR2    | Timer2 mod           | lule's registe     | r              |                 |                |                 |               |          | 0000 0000                | 0000 0000                           |

| 12h                       | T2CON   | —                    | TOUTPS3            | TOUTPS2        | TOUTPS1         | TOUTPS0        | TMR2ON          | T2CKPS1       | T2CKPS0  | -000 0000                | -000 0000                           |

| 13h                       | SSPBUF  | Synchronou           | is Serial Port     | Receive Bu     | ffer/Transmit R | egister        |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 14h                       | SSPCON  | WCOL                 | SSPOV              | SSPEN          | СКР             | SSPM3          | SSPM2           | SSPM1         | SSPM0    | 0000 0000                | 0000 0000                           |

| 15h                       | CCPR1L  | Capture/Co           | mpare/PWM          | Register1 (L   | _SB)            |                |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 16h                       | CCPR1H  | Capture/Co           | mpare/PWM          | Register1 (N   | MSB)            |                |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 17h                       | CCP1CON | —                    | —                  | CCP1X          | CCP1Y           | CCP1M3         | CCP1M2          | CCP1M1        | CCP1M0   | 00 0000                  | 00 0000                             |

| 18h                       | RCSTA   | SPEN                 | RX9                | SREN           | CREN            | —              | FERR            | OERR          | RX9D     | 0000 -00x                | 0000 -00x                           |

| 19h                       | TXREG   | USART Trar           | nsmit Data R       | egister        |                 |                |                 |               |          | 0000 0000                | 0000 0000                           |

| 1Ah                       | RCREG   | USART Red            | ceive Data R       | egister        |                 |                |                 |               |          | 0000 0000                | 0000 0000                           |

| 1Bh                       | CCPR2L  | Capture/Co           | mpare/PWM          | Register2 (L   | _SB)            |                |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 1Ch                       | CCPR2H  | Capture/Co           | mpare/PWM          | Register2 (N   | MSB)            |                |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 1Dh                       | CCP2CON | —                    | —                  | CCP2X          | CCP2Y           | CCP2M3         | CCP2M2          | CCP2M1        | CCP2M0   | 00 0000                  | 00 0000                             |

| 1Eh                       | ADRES   | A/D Result           | Register           |                |                 |                |                 |               |          | XXXX XXXX                | uuuu uuuu                           |

| 1Fh                       | ADCON0  | ADCS1                | ADCS0              | CHS2           | CHS1            | CHS0           | GO/DONE         | —             | ADON     | 0000 00-0                | 0000 00-0                           |

TABLE 4-2:

PIC16C73/73A/74/74A SPECIAL FUNCTION REGISTER SUMMARY

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A, always maintain these bits clear.

4: These registers can be addressed from either bank.

5: PORTD and PORTE are not physically implemented on the PIC16C73/73A, read as '0'.

6: Brown-out Reset is not implemented on the PIC16C73 or the PIC16C74, read as '0'.

7: The IRP and RP1 bits are reserved on the PIC16C73/73A/74/74A, always maintain these bits clear.

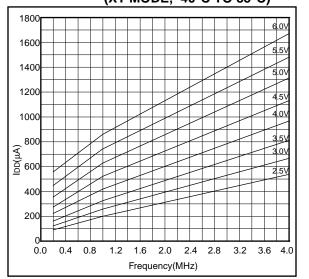

4.2.2.6 PIE2 REGISTER Applicable Devices 72 73 73 74 74 76 77

This register contains the individual enable bit for the CCP2 peripheral interrupt.

#### FIGURE 4-14: PIE2 REGISTER (ADDRESS 8Dh)

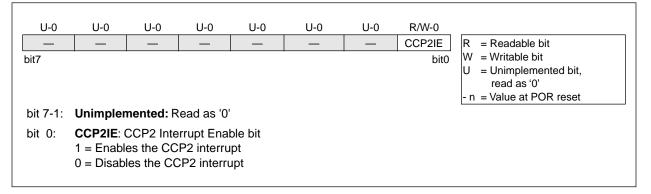

4.2.2.7 PIR2 REGISTER

Applicable Devices

72 73 73A 74 74A 76 77

This register contains the CCP2 interrupt flag bit.

Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 4-15: PIR2 REGISTER (ADDRESS 0Dh)

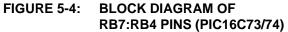

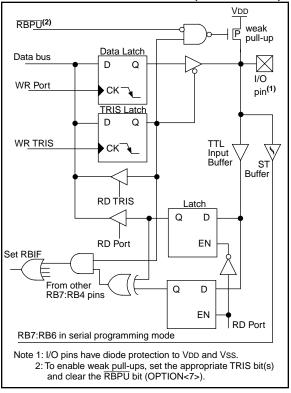

#### TABLE 5-3: PORTB FUNCTIONS

#### FIGURE 5-5: BLOCK DIAGRAM OF RB7:RB4 PINS (PIC16C72/ 73A/74A/76/77)

| Name    | Bit# | Buffer                | Function                                                                                                            |

|---------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                          |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming data.  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

|  | TABLE 5-4: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTB |

|--|------------|--------------------------------------------|

|--|------------|--------------------------------------------|

| Address   | Name                                          | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------|-----------------------------------------------|-------|--------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 06h, 106h | PORTB                                         | RB7   | RB6    | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | xxxx xxxx                | uuuu uuuu                 |

| 86h, 186h | 86h, 186h TRISB PORTB Data Direction Register |       |        |       |       |       |       |       |       | 1111 1111                | 1111 1111                 |

| 81h, 181h | OPTION                                        | RBPU  | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                 |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

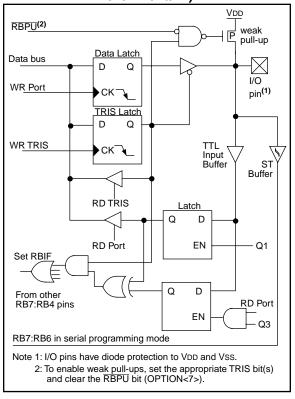

#### 5.4 PORTD and TRISD Registers

## Applicable Devices 72 73 73A 74 74A 76 77

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

PORTD can be configured as an 8-bit wide microprocessor port (parallel slave port) by setting control bit PSPMODE (TRISE<4>). In this mode, the input buffers are TTL.

## FIGURE 5-7: PORTD BLOCK DIAGRAM (IN I/O PORT MODE)

| Name     | Bit# | Buffer Type           | Function                                          |  |  |  |  |

|----------|------|-----------------------|---------------------------------------------------|--|--|--|--|

| RD0/PSP0 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit0 |  |  |  |  |

| RD1/PSP1 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit1 |  |  |  |  |

| RD2/PSP2 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit2 |  |  |  |  |

| RD3/PSP3 | bit3 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit3 |  |  |  |  |

| RD4/PSP4 | bit4 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit4 |  |  |  |  |

| RD5/PSP5 | bit5 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit5 |  |  |  |  |

| RD6/PSP6 | bit6 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit6 |  |  |  |  |

| RD7/PSP7 | bit7 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit7 |  |  |  |  |

#### TABLE 5-7:PORTD FUNCTIONS

Legend: ST = Schmitt Trigger input TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffer when in Parallel Slave Port Mode.

#### TABLE 5-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Address | Name                                | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3                            | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------------------------------------|-------|-------|-------|---------|----------------------------------|-------|-------|-------|--------------------------|---------------------------|

| 08h     | PORTD                               | RD7   | RD6   | RD5   | RD4     | RD3                              | RD2   | RD1   | RD0   | xxxx xxxx                | uuuu uuuu                 |

| 88h     | TRISD PORTD Data Direction Register |       |       |       |         |                                  |       |       |       | 1111 1111                | 1111 1111                 |

| 89h     | TRISE                               | IBF   | OBF   | IBOV  | PSPMODE | MODE — PORTE Data Direction Bits |       |       |       | 0000 -111                | 0000 -111                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTD.

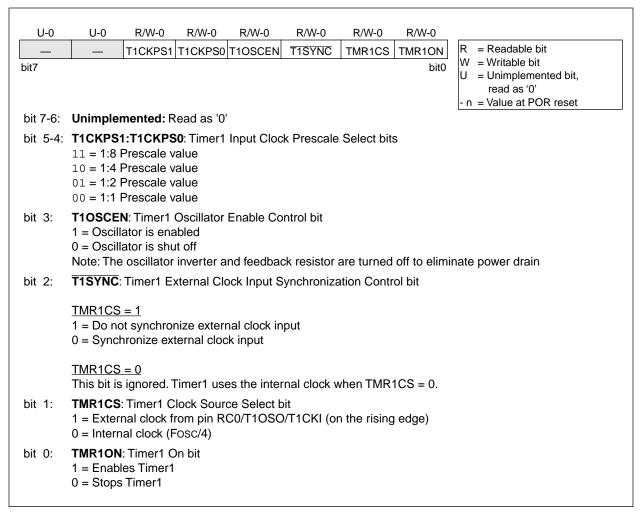

#### 8.0 TIMER1 MODULE Applicable Devices

72 73 73A 74 74A 76 77

The Timer1 module is a 16-bit timer/counter consisting of two 8-bit registers (TMR1H and TMR1L) which are readable and writable. The TMR1 Register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR1 Interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit TMR1IF (PIR1<0>). This interrupt can be enabled/disabled by setting/clearing TMR1 interrupt enable bit TMR1IE (PIE1<0>).

Timer1 can operate in one of two modes:

- As a timer

- · As a counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

In timer mode, Timer1 increments every instruction cycle. In counter mode, it increments on every rising edge of the external clock input.

Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Timer1 also has an internal "reset input". This reset can be generated by either of the two CCP modules (Section 10.0). Figure 8-1 shows the Timer1 control register.

For the PIC16C72/73A/74A/76/77, when the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI/CCP2 and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored.

For the PIC16C73/74, when the Timer1 oscillator is enabled (T1OSCEN is set), RC1/T1OSI/CCP2 pin becomes an input, however the RC0/T1OSO/T1CKI pin will have to be configured as an input by setting the TRISC<0> bit.

#### FIGURE 8-1: T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h)

#### 12.1.1 SAMPLING

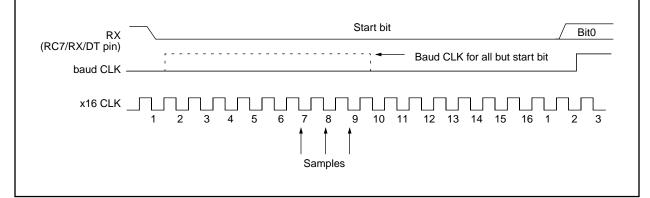

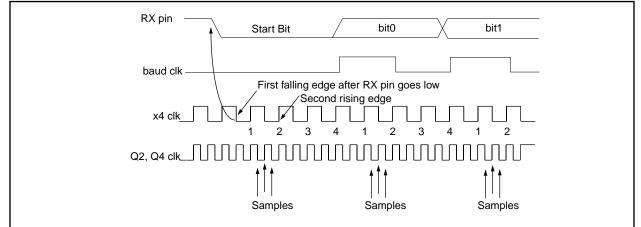

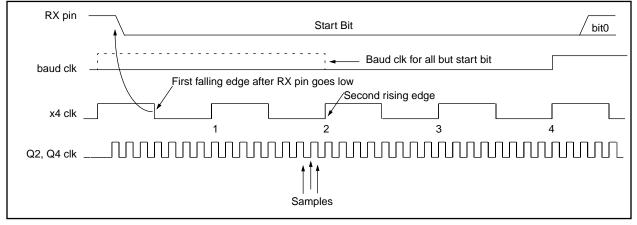

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin. If bit BRGH (TXSTA<2>) is clear (i.e., at the low baud rates), the sampling is done on the seventh, eighth and ninth falling edges of a x16 clock (Figure 12-3). If bit BRGH is set (i.e., at the high baud rates), the sampling is done on the 3 clock edges preceding the second rising edge after the first falling edge of a x4 clock (Figure 12-4 and Figure 12-5).

#### FIGURE 12-3: RX PIN SAMPLING SCHEME. BRGH = 0 (PIC16C73/73A/74/74A)

#### FIGURE 12-4: RX PIN SAMPLING SCHEME, BRGH = 1 (PIC16C73/73A/74/74A)

#### FIGURE 14-20: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| ; a1   a2   a3   a4 ; a1   a2   a<br>osc1/^_/_/_/_//                               | 23 Q4 Q1              | Q1  Q2  Q3  Q4 | ; q1   q2   q3   q4 ;<br>//////////////////////////////////// | Q1   Q2   Q3   Q4 ; | Q1   Q2   Q3   Q4;<br>∕──∕──∕─ |

|------------------------------------------------------------------------------------|-----------------------|----------------|---------------------------------------------------------------|---------------------|--------------------------------|

| CLKOUT(4) ,//                                                                      | Tost(2)               |                |                                                               | \'                  | '                              |

| INT pin                                                                            |                       |                |                                                               | 1<br>1<br>1         |                                |

| INTF flag<br>(INTCON<1>)                                                           | <b>`</b>              | 1              | Interrupt Latency<br>(Note 2)                                 |                     |                                |

| GIE bit<br>(INTCON<7>)                                                             | Processor in<br>SLEEP |                |                                                               | ו<br>ו<br>ו<br>ו    | 1<br>1<br>1                    |

| INSTRUCTION FLOW                                                                   |                       |                |                                                               | 1                   | 1                              |

| PC X PC X PC+1                                                                     | X PC+2                | PC+2           | PC + 2                                                        | X 0004h             | 0005h                          |

| Instruction $\begin{cases} \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $ | + 1)                  | Inst(PC + 2)   |                                                               | Inst(0004h)         | Inst(0005h)                    |

| Instruction<br>executed I Inst(PC - 1) SLEEP                                       |                       | Inst(PC + 1)   | Dummy cycle                                                   | Dummy cycle         | Inst(0004h)                    |

| Note 1. XT US or Descillator mode on                                               |                       |                |                                                               |                     |                                |

Note 1: XT, HS or LP oscillator mode assumed.

2: TOST = 1024TOSC (drawing not to scale) This delay will not be there for RC osc mode.

3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

### 14.9 <u>Program Verification/Code Protection</u>

Applicable Devices

72 73 73A 74 74A 76 77

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting windowed devices.              |

#### 14.10 ID Locations

Applicable Devices

72 73 73A 74 74A 76 77

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

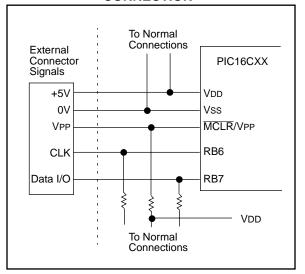

# 14.11 In-Circuit Serial Programming Applicable Devices 72/73/73A/74/74A/76/77

PIC16CXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed. The device is placed into a program/verify mode by holding the RB6 and RB7 pins low while raising the  $\overline{\text{MCLR}}$  (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After reset, to place the device into programming/verify mode, the program counter (PC) is at location 00h. A 6bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X Programming Specifications (Literature #DS30228).

#### FIGURE 14-21: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

# PIC16C7X

| BCF               | Bit Clear f                                                         | BTFSC             | Bit Test, Skip if Clear                                                      |  |  |

|-------------------|---------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------|--|--|

| Syntax:           | [ <i>label</i> ] BCF f,b                                            | Syntax:           | [ <i>label</i> ] BTFSC f,b                                                   |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ | Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$          |  |  |

| Operation:        | $0 \rightarrow (f < b >)$                                           | Operation:        | skip if (f <b>) = 0</b>                                                      |  |  |

| Status Affected:  | None                                                                | Status Affected:  | None                                                                         |  |  |

| Encoding:         | 01 00bb bfff ffff                                                   | Encoding:         | 01 10bb bfff ffff                                                            |  |  |

| Description:      | Bit 'b' in register 'f' is cleared.                                 | Description:      | If bit 'b' in register 'f' is '1' then the next                              |  |  |

| Words:            | 1                                                                   |                   | instruction is executed.<br>If bit 'b', in register 'f', is '0' then the nex |  |  |

| Cycles:           | 1                                                                   |                   | instruction is discarded, and a NOP is                                       |  |  |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                         |                   | executed instead, making this a 2Tch instruction.                            |  |  |

|                   | Decode Read Process Write register 'f'                              | Words:            | 1                                                                            |  |  |

|                   |                                                                     | Cycles:           | 1(2)<br>Q1 Q2 Q3 Q4                                                          |  |  |

| Example           | BCF FLAG_REG, 7                                                     | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                  |  |  |

|                   | Before Instruction                                                  |                   | register 'f' data Operat                                                     |  |  |

|                   | FLAG_REG = 0xC7<br>After Instruction                                | If Skip:          | (2nd Cycle)                                                                  |  |  |

|                   | FLAG_REG = 0x47                                                     |                   | Q1 Q2 Q3 Q4                                                                  |  |  |

|                   |                                                                     |                   | No-<br>OperationNo-<br>OperationNo-<br>OperationNo-<br>Operation             |  |  |

|                   |                                                                     | Example           | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•                  |  |  |

| BSF               | Bit Set f                                                           |                                  |           |      |  |  |  |  |

|-------------------|---------------------------------------------------------------------|----------------------------------|-----------|------|--|--|--|--|

| Syntax:           | [ <i>label</i> ] BSF f,b                                            |                                  |           |      |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |                                  |           |      |  |  |  |  |

| Operation:        | $1 \rightarrow (f < b;$                                             | >)                               |           |      |  |  |  |  |

| Status Affected:  | None                                                                |                                  |           |      |  |  |  |  |

| Encoding:         | 01                                                                  | 01bb                             | bfff      | ffff |  |  |  |  |

| Description:      | Bit 'b' in register 'f' is set.                                     |                                  |           |      |  |  |  |  |

| Words:            | 1                                                                   |                                  |           |      |  |  |  |  |

| Cycles:           | 1                                                                   |                                  |           |      |  |  |  |  |

| Q Cycle Activity: | Q1                                                                  | Q2                               | Q3        | Q4   |  |  |  |  |

|                   | Decode                                                              | Decode Read register data regist |           |      |  |  |  |  |

| Example           | BSF FLAG_REG, 7                                                     |                                  |           |      |  |  |  |  |

|                   | Before Instruction                                                  |                                  |           |      |  |  |  |  |

|                   | FLAG_REG = 0x0A<br>After Instruction                                |                                  |           |      |  |  |  |  |

|                   |                                                                     | FLAG_RE                          | EG = 0x8A | 4    |  |  |  |  |

• Before Instruction

PC =

After Instruction

PC = address HERE

address TRUE

address FALSE

if FLAG < 1 > = 0,

if FLAG<1>=1, PC = addre MPASM has the following features to assist in developing software for specific use applications.

- Provides translation of Assembler source code to object code for all Microchip microcontrollers.

- Macro assembly capability.

- Produces all the files (Object, Listing, Symbol, and special) required for symbolic debug with Microchip's emulator systems.

- Supports Hex (default), Decimal and Octal source and listing formats.

MPASM provides a rich directive language to support programming of the PIC16/17. Directives are helpful in making the development of your assemble source code shorter and more maintainable.

#### 16.11 Software Simulator (MPLAB-SIM)

The MPLAB-SIM Software Simulator allows code development in a PC host environment. It allows the user to simulate the PIC16/17 series microcontrollers on an instruction level. On any given instruction, the user may examine or modify any of the data areas or provide external stimulus to any of the pins. The input/ output radix can be set by the user and the execution can be performed in; single step, execute until break, or in a trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C and MPASM. The Software Simulator offers the low cost flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

#### 16.12 <u>C Compiler (MPLAB-C)</u>

The MPLAB-C Code Development System is a complete 'C' compiler and integrated development environment for Microchip's PIC16/17 family of micro-controllers. The compiler provides powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compiler provides symbol information that is compatible with the MPLAB IDE memory display (PICMASTER emulator software versions 1.13 and later).

#### 16.13 <u>Fuzzy Logic Development System</u> (fuzzyTECH-MP)

*fuzzy*TECH-MP fuzzy logic development tool is available in two versions - a low cost introductory version, MP Explorer, for designers to gain a comprehensive working knowledge of fuzzy logic system design; and a full-featured version, *fuzzy*TECH-MP, edition for implementing more complex systems.

Both versions include Microchip's *fuzzy*LAB<sup>™</sup> demonstration board for hands-on experience with fuzzy logic systems implementation.

#### 16.14 <u>MP-DriveWay™ – Application Code</u> <u>Generator</u>

MP-DriveWay is an easy-to-use Windows-based Application Code Generator. With MP-DriveWay you can visually configure all the peripherals in a PIC16/17 device and, with a click of the mouse, generate all the initialization and many functional code modules in C language. The output is fully compatible with Microchip's MPLAB-C C compiler. The code produced is highly modular and allows easy integration of your own code. MP-DriveWay is intelligent enough to maintain your code through subsequent code generation.

#### 16.15 <u>SEEVAL<sup>®</sup> Evaluation and</u> <u>Programming System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

#### 16.16 <u>TrueGauge<sup>®</sup> Intelligent Battery</u> <u>Management</u>

The TrueGauge development tool supports system development with the MTA11200B TrueGauge Intelligent Battery Management IC. System design verification can be accomplished before hardware prototypes are built. User interface is graphically-oriented and measured data can be saved in a file for exporting to Microsoft Excel.

#### 16.17 <u>KEELOQ<sup>®</sup> Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

### Applicable Devices 72 73 73A 74 74A 76 77

#### 17.1 DC Characteristics: PIC16C72-04 (Commercial, Industrial, Extended) PIC16C72-10 (Commercial, Industrial, Extended) PIC16C72-20 (Commercial, Industrial, Extended)

| DC CHAI                        | RACTERISTICS                                                      |       | <b>Standa</b><br>Operati |                           |                      | ure -4<br>-4         | litions (unless otherwise stated) $10^{\circ}C \leq TA \leq +125^{\circ}C$ for extended, $10^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial and $2C \leq TA \leq +70^{\circ}C$ for commercial |

|--------------------------------|-------------------------------------------------------------------|-------|--------------------------|---------------------------|----------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                   | Characteristic                                                    | Sym   | Min                      | Тур†                      | Max                  | Units                | Conditions                                                                                                                                                                                        |

| D001<br>D001A                  | Supply Voltage                                                    | Vdd   | 4.0<br>4.5               | -                         | 6.0<br>5.5           | V<br>V               | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                           |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                            | Vdr   | -                        | 1.5                       | -                    | V                    |                                                                                                                                                                                                   |

| D003                           | VDD start voltage to<br>ensure internal Power-<br>on Reset Signal | VPOR  | -                        | Vss                       | -                    | V                    | See section on Power-on Reset for details                                                                                                                                                         |

| D004*                          | VDD rise rate to ensure<br>internal Power-on Reset<br>Signal      | SVDD  | 0.05                     | -                         | -                    | V/ms                 | See section on Power-on Reset for details                                                                                                                                                         |

| D005                           | Brown-out Reset Voltage                                           | Bvdd  | 3.7                      | 4.0                       | 4.3                  | V                    | BODEN bit in configuration word enabled                                                                                                                                                           |

|                                |                                                                   |       | 3.7                      | 4.0                       | 4.4                  | V                    | Extended Only                                                                                                                                                                                     |

| D010                           | Supply Current<br>(Note 2,5)                                      | IDD   | -                        | 2.7                       | 5.0                  | mA                   | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                                                                                                     |

| D013                           |                                                                   |       | -                        | 10                        | 20                   | mA                   | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                                                 |

| D015                           | Brown-out Reset Current<br>(Note 6)                               | ΔIBOR | -                        | 350                       | 425                  | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                            |

| D020<br>D021<br>D021A<br>D021B | Power-down Current<br>(Note 3,5)                                  | IPD   | -<br>-<br>-<br>-         | 10.5<br>1.5<br>1.5<br>2.5 | 42<br>16<br>19<br>19 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 4.0V, WDT enabled, -40°C to +85°C<br>VDD = 4.0V, WDT disabled, -0°C to +70°C<br>VDD = 4.0V, WDT disabled, -40°C to +85°C<br>VDD = 4.0V, WDT disabled, -40°C to +125°C                       |

| D023                           | Brown-out Reset Current<br>(Note 6)                               | ΔIBOR | -                        | 350                       | 425                  | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD  $\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VbD and Vss.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

# PIC16C7X

Applicable Devices 72 73 73A 74 74A 76 77

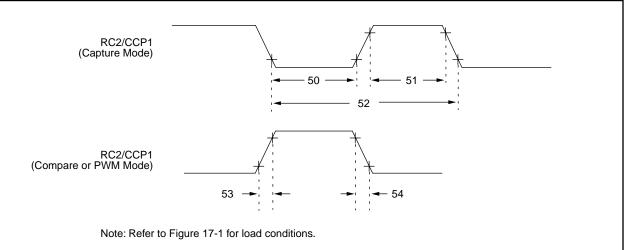

### TABLE 17-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1)

| Param<br>No. | Sym  | Characteristic        | Min            | Тур†               | Max                   | Units | Conditions |    |                                   |

|--------------|------|-----------------------|----------------|--------------------|-----------------------|-------|------------|----|-----------------------------------|

| 50*          | TccL | CCP1 input low time   | No Prescaler   |                    | 0.5Tcy + 20           | —     |            | ns |                                   |

|              |      |                       | With Prescaler | PIC16 <b>C</b> 72  | 10                    | —     | _          | ns |                                   |

|              |      |                       |                | PIC16 <b>LC</b> 72 | 20                    | —     | _          | ns |                                   |

| 51*          | TccH | CCP1 input high time  | No Prescaler   |                    | 0.5Tcy + 20           | —     | —          | ns |                                   |

|              |      |                       | With Prescaler | PIC16 <b>C</b> 72  | 10                    | —     | _          | ns |                                   |

|              |      |                       |                | PIC16 <b>LC</b> 72 | 20                    | —     | _          | ns |                                   |

| 52*          | TccP | CCP1 input period     |                |                    | <u>3Tcy + 40</u><br>N | —     | —          | ns | N = prescale<br>value (1,4 or 16) |

| 53*          | TccR | CCP1 output rise time |                | PIC16 <b>C</b> 72  | _                     | 10    | 25         | ns |                                   |

|              |      |                       |                | PIC16 <b>LC</b> 72 | —                     | 25    | 45         | ns |                                   |

| 54*          | TccF | CCP1 output fall time |                | PIC16 <b>C</b> 72  | _                     | 10    | 25         | ns |                                   |

|              |      |                       |                | PIC16 <b>LC</b> 72 | _                     | 25    | 45         | ns |                                   |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## Applicable Devices 72 73 73A 74 76 77

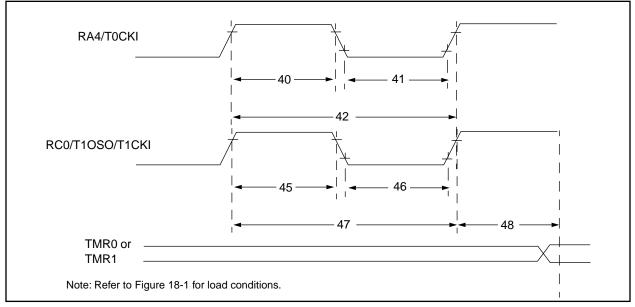

#### FIGURE 18-5: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

#### TABLE 18-5: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                                 |                      |                    | Min                                              | Тур† | Max   | Units | Conditions                         |

|--------------|----------|------------------------------------------------|----------------------|--------------------|--------------------------------------------------|------|-------|-------|------------------------------------|

| 40*          | Tt0H     | T0CKI High Pulse V                             | Vidth                | No Prescaler       | 0.5Tcy + 20                                      | -    | —     | ns    | Must also meet                     |

|              |          |                                                |                      | With Prescaler     | 10                                               | _    | _     | ns    | parameter 42                       |

| 41*          | Tt0L     | T0CKI Low Pulse W                              | /idth                | No Prescaler       | 0.5TCY + 20                                      | -    | —     | ns    | Must also meet                     |

|              |          |                                                |                      | With Prescaler     | 10                                               | —    | —     | ns    | parameter 42                       |

| 42*          | Tt0P     | T0CKI Period                                   |                      | No Prescaler       | Tcy + 40                                         | —    | —     | ns    |                                    |

|              |          |                                                |                      | With Prescaler     | Greater of:<br>20 or <u>Tcy + 40</u><br>N        | -    | _     | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Tt1H     | T1CKI High Time                                | Synchronous, F       | Prescaler = 1      | 0.5TCY + 20                                      | -    | —     | ns    | Must also meet                     |

|              |          |                                                | Synchronous,         | PIC16 <b>C</b> 7X  | 15                                               | -    | —     | ns    | parameter 47                       |

|              |          |                                                | Prescaler =<br>2,4,8 | PIC16 <b>LC</b> 7X | 25                                               | -    | —     | ns    |                                    |

|              |          |                                                | Asynchronous         | PIC16 <b>C</b> 7X  | 30                                               | —    | —     | ns    |                                    |

|              |          |                                                |                      | PIC16 <b>LC</b> 7X | 50                                               | —    | —     | ns    |                                    |

| 46*          | Tt1L     |                                                |                      |                    | 0.5Tcy + 20                                      | —    | —     | ns    | Must also meet                     |

|              |          |                                                | Synchronous,         | PIC16 <b>C</b> 7X  | 15                                               | —    | —     | ns    | parameter 47                       |

|              |          |                                                | Prescaler =<br>2,4,8 | PIC16 <b>LC</b> 7X | 25                                               | -    | -     | ns    |                                    |

|              |          |                                                | Asynchronous         | PIC16 <b>C</b> 7X  | 30                                               | —    | —     | ns    |                                    |

|              |          |                                                |                      | PIC16 <b>LC</b> 7X | 50                                               | —    | —     | ns    |                                    |

| 47*          | Tt1P     | T1CKI input period                             | Synchronous          | PIC16 <b>C</b> 7X  | <u>Greater of:</u><br>30 OR <u>TCY + 40</u><br>N | -    | _     | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |          |                                                |                      | PIC16 <b>LC</b> 7X | <u>Greater of:</u><br>50 OR <u>TCY + 40</u><br>N |      |       |       | N = prescale value<br>(1, 2, 4, 8) |

|              |          |                                                | Asynchronous         | PIC16 <b>C</b> 7X  | 60                                               | —    | —     | ns    |                                    |

|              |          |                                                |                      | PIC16 <b>LC</b> 7X | 100                                              | —    | —     | ns    |                                    |

|              | Ft1      | Timer1 oscillator inp<br>(oscillator enabled b | by setting bit T1C   | SCEN)              | DC                                               | -    | 200   | kHz   |                                    |

| 48           | TCKEZtmr | 1 Delay from external                          | clock edge to tir    | ner increment      | 2Tosc                                            | —    | 7Tosc | -     |                                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

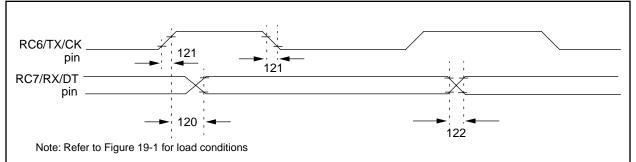

### Applicable Devices 72 73 73A 74 74A 76 77

#### FIGURE 19-12: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 19-11: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Sym                          | Characteristic                                  |                         | Min | Тур† | Мах | Units | Conditions |

|--------------|------------------------------|-------------------------------------------------|-------------------------|-----|------|-----|-------|------------|

| 120          | TckH2dtV                     | SYNC XMIT (MASTER &<br>SLAVE)                   | PIC16 <b>C</b> 73A/74A  | _   | _    | 80  | ns    |            |

|              | Clock high to data out valid | PIC16 <b>LC</b> 73A/74A                         | _                       | —   | 100  | ns  |       |            |

| 121 Tckrf    |                              | Clock out rise time and fall time (Master Mode) | PIC16 <b>C</b> 73A/74A  | -   | —    | 45  | ns    |            |

|              | PIC16 <b>LC</b> 73A/74A      |                                                 | -                       | —   | 50   | ns  |       |            |

| 122          | Tdtrf                        | Data out rise time and fall time                | PIC16 <b>C</b> 73A/74A  | - 1 | -    | 45  | ns    |            |

|              |                              |                                                 | PIC16 <b>LC</b> 73A/74A | -   | —    | 50  | ns    |            |

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

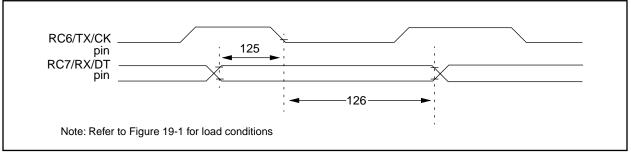

#### FIGURE 19-13: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 19-12: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                                                            | Min | Тур† | Мах | Units | Conditions |

|------------------|----------|-----------------------------------------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | $\frac{\text{SYNC RCV (MASTER \& SLAVE)}}{\text{Data setup before CK} \downarrow (\text{DT setup time})}$ | 15  | _    | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                                            | 15  | —    | —   | ns    |            |

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16C7X

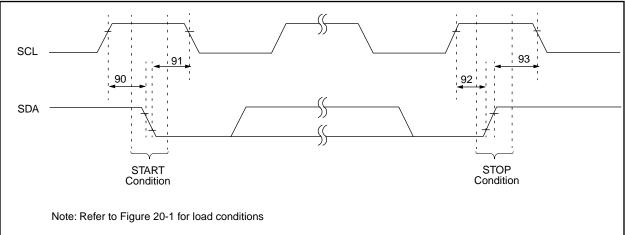

## Applicable Devices 72 73 73A 74 74A 76 77

## TABLE 20-9: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Parameter<br>No. | Sym     | Characteristic  |              | Min  | Тур | Max | Units | Conditions                        |  |

|------------------|---------|-----------------|--------------|------|-----|-----|-------|-----------------------------------|--|

| 90               | TSU:STA | START condition | 100 kHz mode | 4700 | —   | —   | ns    | Only relevant for repeated START  |  |

|                  |         | Setup time      | 400 kHz mode | 600  | _   | -   |       | condition                         |  |

| 91               | THD:STA | START condition | 100 kHz mode | 4000 | —   | —   | ns    | After this period the first clock |  |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | 113   | pulse is generated                |  |

| 92               | Tsu:sto | STOP condition  | 100 kHz mode | 4700 | —   | —   | ns    |                                   |  |

|                  |         | Setup time      | 400 kHz mode | 600  | —   | —   |       |                                   |  |

| 93               | THD:STO | STOP condition  | 100 kHz mode | 4000 | —   | -   | ns    |                                   |  |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | 113   |                                   |  |

#### Applicable Devices 72 73 73A 74 74A 76 77

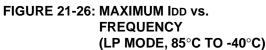

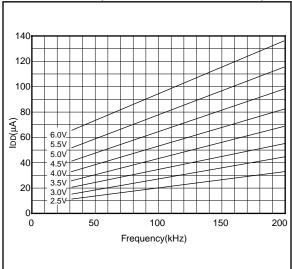

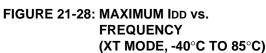

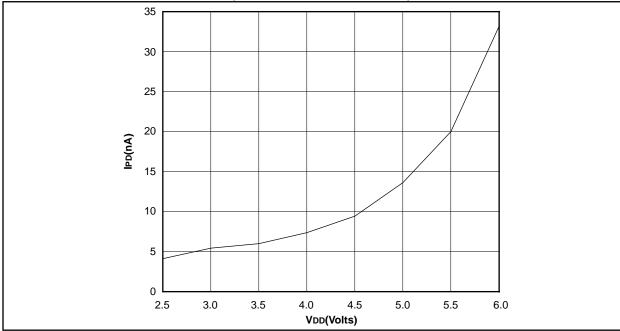

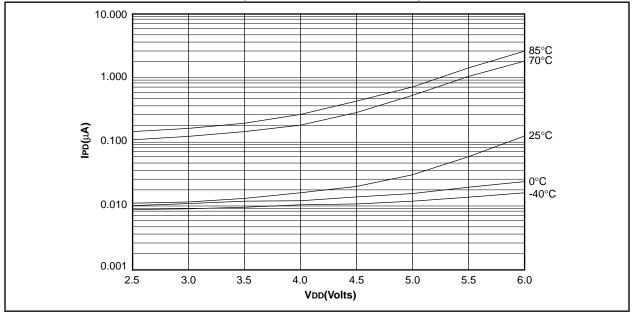

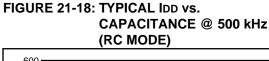

## 21.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for design guidance and are not tested or guaranteed.

In some graphs or tables the data presented are outside specified operating range (i.e., outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

**Note:** The data presented in this section is a statistical summary of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at, 25°C, while 'max' or 'min' represents (mean +3σ) and (mean -3σ) respectively where σ is standard deviation.

FIGURE 21-1: TYPICAL IPD vs. VDD (WDT DISABLED, RC MODE)

FIGURE 21-2: MAXIMUM IPD vs. VDD (WDT DISABLED, RC MODE)

#### TABLE 21-1: RC OSCILLATOR FREQUENCIES

| Cext   | Rext  | Average         |        |  |  |  |  |

|--------|-------|-----------------|--------|--|--|--|--|

| Cext   | T CAL | Fosc @ 5V, 25°C |        |  |  |  |  |

| 22 pF  | 5k    | 4.12 MHz        | ± 1.4% |  |  |  |  |

|        | 10k   | 2.35 MHz        | ± 1.4% |  |  |  |  |

|        | 100k  | 268 kHz         | ± 1.1% |  |  |  |  |

| 100 pF | 3.3k  | 1.80 MHz        | ± 1.0% |  |  |  |  |

|        | 5k    | 1.27 MHz        | ± 1.0% |  |  |  |  |

|        | 10k   | 688 kHz         | ± 1.2% |  |  |  |  |

|        | 100k  | 77.2 kHz        | ± 1.0% |  |  |  |  |

| 300 pF | 3.3k  | 707 kHz         | ± 1.4% |  |  |  |  |

|        | 5k    | 501 kHz         | ± 1.2% |  |  |  |  |

|        | 10k   | 269 kHz         | ± 1.6% |  |  |  |  |

|        | 100k  | 28.3 kHz        | ± 1.1% |  |  |  |  |

The percentage variation indicated here is part to part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviation from average value for VDD = 5V.

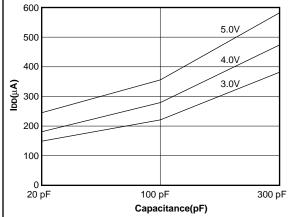

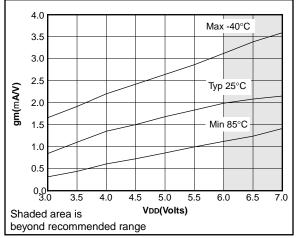

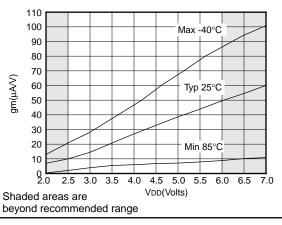

### Applicable Devices 72 73 73A 74 74A 76 77

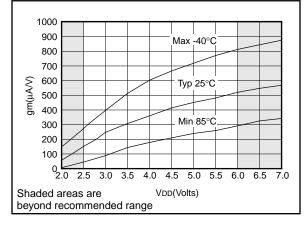

#### FIGURE 21-19: TRANSCONDUCTANCE(gm) OF HS OSCILLATOR vs. VDD

#### FIGURE 21-20: TRANSCONDUCTANCE(gm) OF LP OSCILLATOR vs. VDD

#### FIGURE 21-21: TRANSCONDUCTANCE(gm) OF XT OSCILLATOR vs. VDD

Data based on matrix samples. See first page of this section for details.

## © 1997 Microchip Technology Inc.

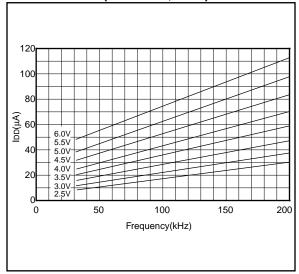

#### FIGURE 21-25: TYPICAL IDD vs. FREQUENCY (LP MODE, 25°C)