Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 10MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | A/D 5x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c76-10i-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 3-2:PIC16C73/73A/76 PINOUT DESCRIPTION

| Pin Name                | DIP<br>Pin# | SOIC<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                                  |

|-------------------------|-------------|--------------|---------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN              | 9           | 9            | I             | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                        |

| OSC2/CLKOUT             | 10          | 10           | 0             | -                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp                | 1           | 1            | I/P           | ST                     | Master clear (reset) input or programming voltage input. This pin is an active low reset to the device.                                                                                                      |

|                         |             |              |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                          |

| RA0/AN0                 | 2           | 2            | I/O           | TTL                    | RA0 can also be analog input0                                                                                                                                                                                |

| RA1/AN1                 | 3           | 3            | I/O           | TTL                    | RA1 can also be analog input1                                                                                                                                                                                |

| RA2/AN2                 | 4           | 4            | I/O           | TTL                    | RA2 can also be analog input2                                                                                                                                                                                |

| RA3/AN3/VREF            | 5           | 5            | I/O           | TTL                    | RA3 can also be analog input3 or analog reference voltage                                                                                                                                                    |

| RA4/T0CKI               | 6           | 6            | I/O           | ST                     | RA4 can also be the clock input to the Timer0 module.<br>Output is open drain type.                                                                                                                          |

| RA5/ <del>SS</del> /AN4 | 7           | 7            | I/O           | TTL                    | RA5 can also be analog input4 or the slave select for the<br>synchronous serial port.                                                                                                                        |

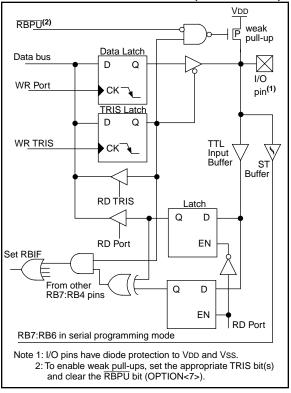

|                         |             |              |               |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                                |

| RB0/INT                 | 21          | 21           | I/O           | TTL/ST(1)              | RB0 can also be the external interrupt pin.                                                                                                                                                                  |

| RB1                     | 22          | 22           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB2                     | 23          | 23           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB3                     | 24          | 24           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB4                     | 25          | 25           | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |

| RB5                     | 26          | 26           | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |

| RB6                     | 27          | 27           | I/O           | TTL/ST(2)              | Interrupt on change pin. Serial programming clock.                                                                                                                                                           |

| RB7                     | 28          | 28           | I/O           | TTL/ST(2)              | Interrupt on change pin. Serial programming data.                                                                                                                                                            |

|                         |             |              |               |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                          |

| RC0/T1OSO/T1CKI         | 11          | 11           | I/O           | ST                     | RC0 can also be the Timer1 oscillator output or Timer1 clock input.                                                                                                                                          |

| RC1/T1OSI/CCP2          | 12          | 12           | I/O           | ST                     | RC1 can also be the Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output.                                                                                                                   |

| RC2/CCP1                | 13          | 13           | I/O           | ST                     | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                                                                                                                          |

| RC3/SCK/SCL             | 14          | 14           | I/O           | ST                     | RC3 can also be the synchronous serial clock input/output for both SPI and I <sup>2</sup> C modes.                                                                                                           |

| RC4/SDI/SDA             | 15          | 15           | I/O           | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                                                                                              |

| RC5/SDO                 | 16          | 16           | I/O           | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                 |

| RC6/TX/CK               | 17          | 17           | I/O           | ST                     | RC6 can also be the USART Asynchronous Transmit of<br>Synchronous Clock.                                                                                                                                     |

| RC7/RX/DT               | 18          | 18           | I/O           | ST                     | RC7 can also be the USART Asynchronous Receive of<br>Synchronous Data.                                                                                                                                       |

| Vss                     | 8, 19       | 8, 19        | Р             | <u> </u>               | Ground reference for logic and I/O pins.                                                                                                                                                                     |

| VDD                     | 20          | 20           | P             | <u> </u>               | Positive supply for logic and I/O pins.                                                                                                                                                                      |

| Legend: I = input       | O = outp    |              |               | input/output           | P = power                                                                                                                                                                                                    |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

4.2.2.4 PIE1 REGISTER

Applicable Devices

72 73 73A 74 74A 76 77

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

This register contains the individual enable bits for the peripheral interrupts.

# FIGURE 4-10: PIE1 REGISTER PIC16C72 (ADDRESS 8Ch)

| U-0      | R/W-0                                                                                                                                                 | U-0                                                                                                                            | U-0                                       | R/W-0      | R/W-0  | R/W-0  | R/W-0  |                  |  |  |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------|--------|--------|--------|------------------|--|--|--|--|--|--|

|          | ADIE                                                                                                                                                  | _                                                                                                                              | —                                         | SSPIE      | CCP1IE | TMR2IE | TMR1IE | R = Readable bit |  |  |  |  |  |  |

| bit7     | bit0<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset                                                         |                                                                                                                                |                                           |            |        |        |        |                  |  |  |  |  |  |  |

| bit 7:   | Unimplemented: Read as '0'                                                                                                                            |                                                                                                                                |                                           |            |        |        |        |                  |  |  |  |  |  |  |

| bit 6:   |                                                                                                                                                       | es the A/D                                                                                                                     | er Interrup<br>D interrupt<br>D interrupt |            | it     |        |        |                  |  |  |  |  |  |  |

| bit 5-4: | Unimpler                                                                                                                                              | Jnimplemented: Read as '0'                                                                                                     |                                           |            |        |        |        |                  |  |  |  |  |  |  |

| bit 3:   | 1 = Enabl                                                                                                                                             | <b>SSPIE</b> : Synchronous Serial Port Interrupt Enable bit<br>1 = Enables the SSP interrupt<br>0 = Disables the SSP interrupt |                                           |            |        |        |        |                  |  |  |  |  |  |  |

| bit 2:   | <b>CCP1IE</b> : CCP1 Interrupt Enable bit<br>1 = Enables the CCP1 interrupt<br>0 = Disables the CCP1 interrupt                                        |                                                                                                                                |                                           |            |        |        |        |                  |  |  |  |  |  |  |

| bit 1:   | <b>TMR2IE</b> : TMR2 to PR2 Match Interrupt Enable bit<br>1 = Enables the TMR2 to PR2 match interrupt<br>0 = Disables the TMR2 to PR2 match interrupt |                                                                                                                                |                                           |            |        |        |        |                  |  |  |  |  |  |  |

| bit 0:   | 1 = Enabl                                                                                                                                             | es the TM                                                                                                                      | erflow Inte<br>R1 overflo<br>IR1 overflo  | w interrup | ot     |        |        |                  |  |  |  |  |  |  |

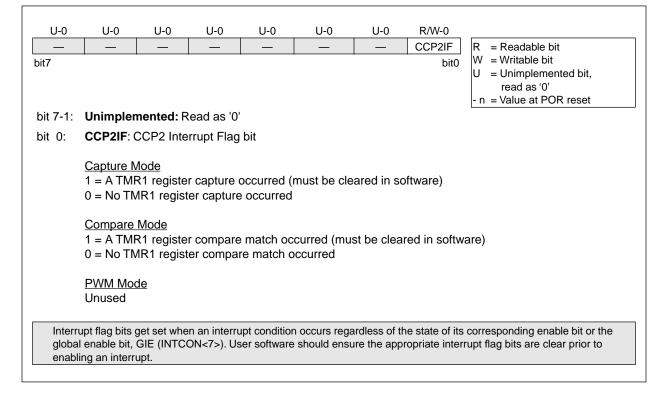

4.2.2.7 PIR2 REGISTER

Applicable Devices

72 73 73A 74 74A 76 77

This register contains the CCP2 interrupt flag bit.

Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# FIGURE 4-15: PIR2 REGISTER (ADDRESS 0Dh)

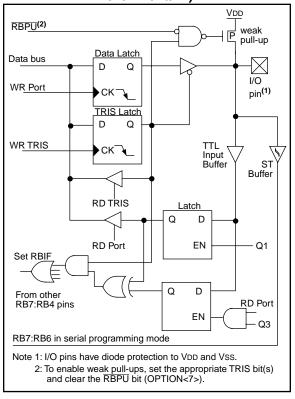

# TABLE 5-3: PORTB FUNCTIONS

## FIGURE 5-5: BLOCK DIAGRAM OF RB7:RB4 PINS (PIC16C72/ 73A/74A/76/77)

| Name    | Bit# | Buffer                | Function                                                                                                            |

|---------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                          |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming data.  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

|  | TABLE 5-4: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTB |

|--|------------|--------------------------------------------|

|--|------------|--------------------------------------------|

| Address   | Name   | Bit 7 | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------|--------|-------|-------------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 06h, 106h | PORTB  | RB7   | RB6                           | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   | xxxx xxxx                | uuuu uuuu                 |

| 86h, 186h | TRISB  | PORTB | PORTB Data Direction Register |       |       |       |       |       |       |                          | 1111 1111                 |

| 81h, 181h | OPTION | RBPU  | INTEDG                        | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                 |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

# 6.0 OVERVIEW OF TIMER MODULES

Applicable Devices

The PIC16C72, PIC16C73/73A, PIC16C74/74A, PIC16C76/77 each have three timer modules.

Each module can generate an interrupt to indicate that an event has occurred (i.e. timer overflow). Each of these modules is explained in full detail in the following sections. The timer modules are:

- Timer0 Module (Section 7.0)

- Timer1 Module (Section 8.0)

- Timer2 Module (Section 9.0)

# 6.1 <u>Timer0 Overview</u> Applicable Devices 72|73|73A|74|74A|76|77

The Timer0 module is a simple 8-bit overflow counter. The clock source can be either the internal system clock (Fosc/4) or an external clock. When the clock source is an external clock, the Timer0 module can be selected to increment on either the rising or falling edge.

The Timer0 module also has a programmable prescaler option. This prescaler can be assigned to either the Timer0 module or the Watchdog Timer. Bit PSA (OPTION<3>) assigns the prescaler, and bits PS2:PS0 (OPTION<2:0>) determine the prescaler value. Timer0 can increment at the following rates: 1:1 (when prescaler assigned to Watchdog timer), 1:2, 1:4, 1:8, 1:16, 1:32, 1:64, 1:128, and 1:256 (Timer0 only).

Synchronization of the external clock occurs after the prescaler. When the prescaler is used, the external clock frequency may be higher then the device's frequency. The maximum frequency is 50 MHz, given the high and low time requirements of the clock.

## 6.2 <u>Timer1 Overview</u> Applicable Devices 72 73 73 74 74 76 77

Timer1 is a 16-bit timer/counter. The clock source can be either the internal system clock (Fosc/4), an external clock, or an external crystal. Timer1 can operate as either a timer or a counter. When operating as a counter (external clock source), the counter can either operate synchronized to the device or asynchronously to the device. Asynchronous operation allows Timer1 to operate during sleep, which is useful for applications that require a real-time clock as well as the power savings of SLEEP mode.

Timer1 also has a prescaler option which allows Timer1 to increment at the following rates: 1:1, 1:2, 1:4, and 1:8. Timer1 can be used in conjunction with the Capture/Compare/PWM module. When used with a CCP module, Timer1 is the time-base for 16-bit Capture or the 16-bit Compare and must be synchronized to the device.

# 6.3 <u>Timer2 Overview</u> Applicable Devices

|    | Applicable Devices |     |    |     |    |    |  |  |  |  |  |

|----|--------------------|-----|----|-----|----|----|--|--|--|--|--|

| 72 | 73                 | 73A | 74 | 74A | 76 | 77 |  |  |  |  |  |

Timer2 is an 8-bit timer with a programmable prescaler and postscaler, as well as an 8-bit period register (PR2). Timer2 can be used with the CCP1 module (in PWM mode) as well as the Baud Rate Generator for the Synchronous Serial Port (SSP). The prescaler option allows Timer2 to increment at the following rates: 1:1, 1:4, 1:16.

The postscaler allows the TMR2 register to match the period register (PR2) a programmable number of times before generating an interrupt. The postscaler can be programmed from 1:1 to 1:16 (inclusive).

## 6.4 <u>CCP Overview</u>

Applicable Devices

72

73

73

74

74

76

77

The CCP module(s) can operate in one of these three modes: 16-bit capture, 16-bit compare, or up to 10-bit Pulse Width Modulation (PWM).

Capture mode captures the 16-bit value of TMR1 into the CCPRxH:CCPRxL register pair. The capture event can be programmed for either the falling edge, rising edge, fourth rising edge, or the sixteenth rising edge of the CCPx pin.

Compare mode compares the TMR1H:TMR1L register pair to the CCPRxH:CCPRxL register pair. When a match occurs an interrupt can be generated, and the output pin CCPx can be forced to given state (High or Low), TMR1 can be reset (CCP1), or TMR1 reset and start A/D conversion (CCP2). This depends on the control bits CCPxM3:CCPxM0.

PWM mode compares the TMR2 register to a 10-bit duty cycle register (CCPRxH:CCPRxL<5:4>) as well as to an 8-bit period register (PR2). When the TMR2 register = Duty Cycle register, the CCPx pin will be forced low. When TMR2 = PR2, TMR2 is cleared to 00h, an interrupt can be generated, and the CCPx pin (if an output) will be forced high.

٦

# FIGURE 11-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)

| R/W-0    | R/W-0                                                                | R/W-0                                                                   | R/W-0                                                                            | R/W-0                                                                        | R/W-0                                    | R/W-0                    | R/W-0                        |                                                                                                                           |

|----------|----------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------|--------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| WCOL     | SSPOV                                                                | SSPEN                                                                   | CKP                                                                              | SSPM3                                                                        | SSPM2                                    | SSPM1                    | SSPM0                        | R = Readable bit                                                                                                          |

| bit7     |                                                                      |                                                                         |                                                                                  |                                                                              |                                          |                          | bit0                         | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset                                      |

| bit 7:   | WCOL: W                                                              | rite Collisio                                                           | n Detect l                                                                       | oit                                                                          |                                          |                          |                              |                                                                                                                           |

|          | 1 = The S                                                            | SPBUF reg                                                               | jister is wr                                                                     |                                                                              | it is still tr                           | ansmitting               | the previou                  | us word                                                                                                                   |

| bit 6:   | SSPOV: R                                                             | eceive Ove                                                              | erflow Det                                                                       | ect bit                                                                      |                                          |                          |                              |                                                                                                                           |

|          | the data ir<br>BUF, even                                             | byte is rece<br>SSPSR re<br>if only train<br>new rece                   | egister is I                                                                     | ost. Overfl<br>data, to av                                                   | ow can on<br>oid setting                 | ly occur in<br>overflow. | slave mod<br>In master       | revious data. In case of overflow<br>e. The user must read the SSP<br>mode the overflow bit is not se<br>SSPBUF register. |

|          | In I <sup>2</sup> C mod                                              | <u>de</u>                                                               |                                                                                  |                                                                              |                                          |                          |                              |                                                                                                                           |

|          | 1 = A byte<br>in transmit<br>0 = No ove                              | mode. SS                                                                |                                                                                  |                                                                              |                                          |                          |                              | us byte. SSPOV is a "don't care                                                                                           |

| bit 5:   | SSPEN: S                                                             | ynchronou                                                               | s Serial P                                                                       | ort Enable                                                                   | bit                                      |                          |                              |                                                                                                                           |

|          | $\frac{\text{In SPI model}}{1 = \text{Enable}}$ $0 = \text{Disable}$ | es serial po                                                            |                                                                                  |                                                                              |                                          |                          | s serial por<br>pins         | t pins                                                                                                                    |

|          | 0 = Disabl                                                           | es the seria                                                            | ort and co                                                                       | nfigures th                                                                  | nese pins a                              | as I/O port              | pins                         | ial port pins<br>s input or output.                                                                                       |

| bit 4:   | CKP: Cloc                                                            | k Polarity                                                              | Select bit                                                                       |                                                                              |                                          |                          |                              |                                                                                                                           |

|          |                                                                      | ate for cloc                                                            |                                                                                  |                                                                              |                                          |                          |                              | receive on rising edge.<br>ceive on falling edge.                                                                         |

|          | $\frac{\ln l^2 C \mod SCK \text{ relea}}{1 = \text{Enable}}$         | se control<br>e clock                                                   | -11                                                                              |                                                                              | 4                                        |                          | . (: )                       |                                                                                                                           |

|          | 0 = Holds                                                            |                                                                         |                                                                                  | , ,                                                                          |                                          |                          | o time)                      |                                                                                                                           |

| bit 3-0: | 0001 = SF<br>0010 = SF<br>0011 = SF<br>0100 = SF<br>0101 = SF        | PI master n<br>PI master n<br>PI master n<br>PI master n<br>PI slave mo | node, cloc<br>node, cloc<br>node, cloc<br>node, cloc<br>ode, clock<br>ode, clock | k = Fosc/4<br>k = Fosc/1<br>k = Fosc/6<br>k = TMR2<br>= SCK pir<br>= SCK pir | l<br>6<br>64<br>output/2<br>1. SS pin co | ontrol enal              |                              | n be used as I/O pin.                                                                                                     |

|          | $0111 = I^{2}(0)$<br>$1011 = I^{2}(0)$<br>$1110 = I^{2}(0)$          | C slave mo<br>C firmware<br>C slave mo                                  | de, 10-bit<br>controlled<br>de, 7-bit a                                          | address<br>I Master M<br>ddress wi                                           | th start an                              | d stop bit i             | nterrupts er<br>interrupts o |                                                                                                                           |

Г

## 11.5.1 SLAVE MODE

In slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The SSP module will override the input state with the output data when required (slave-transmitter).

When an address is matched or the data transfer after an address match is received, the hardware automatically will generate the acknowledge ( $\overline{ACK}$ ) pulse, and then load the SSPBUF register with the received value currently in the SSPSR register.

There are certain conditions that will cause the SSP module not to give this  $\overline{ACK}$  pulse. These are if either (or both):

- a) The buffer full bit BF (SSPSTAT<0>) was set before the transfer was received.

- b) The overflow bit SSPOV (SSPCON<6>) was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. Table 11-4 shows what happens when a data transfer byte is received, given the status of bits BF and SSPOV. The shaded cells show the condition where user software did not properly clear the overflow condition. Flag bit BF is cleared by reading the SSPBUF register while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification as well as the requirement of the SSP module is shown in timing parameter #100 and parameter #101.

### 11.5.1.1 ADDRESSING

Once the SSP module has been enabled, it waits for a START condition to occur. Following the START condition, the 8-bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The

address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and SSPOV bits are clear, the following events occur:

- a) The SSPSR register value is loaded into the SSPBUF register.

- b) The buffer full bit, BF is set.

- c) An ACK pulse is generated.

- d) SSP interrupt flag bit, SSPIF (PIR1<3>) is set (interrupt is generated if enabled) - on the falling edge of the ninth SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave (Figure 11-16). The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address the first byte would equal '1111 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7- 9 for slave-transmitter:

- 1. Receive first (high) byte of Address (bits SSPIF, BF, and bit UA (SSPSTAT<1>) are set).

- Update the SSPADD register with second (low) byte of Address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of Address (bits SSPIF, BF, and UA are set).

- 5. Update the SSPADD register with the first (high) byte of Address, if match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive repeated START condition.

- 8. Receive first (high) byte of Address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

|    | ts as Data<br>s Received |                     |                       | Set bit SSPIF                        |  |

|----|--------------------------|---------------------|-----------------------|--------------------------------------|--|

| BF | SSPOV                    | $SSPSR \to  SSPBUF$ | Generate ACK<br>Pulse | (SSP Interrupt occurs<br>if enabled) |  |

| 0  | 0                        | Yes                 | Yes                   | Yes                                  |  |

| 1  | 0                        | No                  | No                    | Yes                                  |  |

| 1  | 1                        | No                  | No                    | Yes                                  |  |

| 0  | 1                        | No                  | No                    | Yes                                  |  |

# TABLE 11-4: DATA TRANSFER RECEIVED BYTE ACTIONS

# 12.1 USART Baud Rate Generator (BRG) Applicable Devices 72 73 73A 74 74A 76 77

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In asynchronous mode bit BRGH (TXSTA<2>) also controls the baud rate. In synchronous mode bit BRGH is ignored. Table 12-1 shows the formula for computation of the baud rate for different USART modes which only apply in master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 12-1. From this, the error in baud rate can be determined.

Example 12-1 shows the calculation of the baud rate error for the following conditions:

Fosc = 16 MHz Desired Baud Rate = 9600 BRGH = 0 SYNC = 0

# EXAMPLE 12-1: CALCULATING BAUD RATE ERROR

Desired Baud rate = Fosc / (64 (X + 1))

$9600 = \frac{16000000}{(64 (X + 1))}$

$X = \lfloor 25.042 \rfloor = 25$

Calculated Baud Rate=16000000 / (64 (25 + 1))

= 9615

- Error = (Calculated Baud Rate Desired Baud Rate) Desired Baud Rate

- = (9615 9600) / 9600

= 0.16%

It may be advantageous to use the high baud rate (BRGH = 1) even for slower baud clocks. This is because the Fosc/(16(X + 1)) equation can reduce the baud rate error in some cases.

| Note: | For the PIC16C73/73A/74/74A, the asyn-<br>chronous high speed mode (BRGH = 1)<br>may experience a high rate of receive<br>errors. It is recommended that BRGH = 0.<br>If you desire a higher baud rate than<br>BRGH = 0 can support, refer to the device<br>errata for additional information, or use the<br>PIC16C76/77. |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Writing a new value to the SPBRG register, causes the BRG timer to be reset (or cleared), this ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

# TABLE 12-1: BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)     |

|------|-------------------------------------------|---------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate= Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X+1))   | NA                        |

X = value in SPBRG (0 to 255)

## TABLE 12-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name  | Bit 7 | Bit 6     | Bit 5     | Bit 4 | Bit 3     | Bit 2     | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|-------|-----------|-----------|-------|-----------|-----------|-------|-------|--------------------------|---------------------------|

| 98h     | TXSTA | CSRC  | TX9       | TXEN      | SYNC  | —         | BRGH      | TRMT  | TX9D  | 0000 -010                | 0000 -010                 |

| 18h     | RCSTA | SPEN  | RX9       | SREN      | CREN  | 0000 -00x | 0000 -00x |       |       |                          |                           |

| 99h     | SPBRG |       | 0000 0000 | 0000 0000 |       |           |           |       |       |                          |                           |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used by the BRG.

#### 14.5.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered: either rising if bit INTEDG (OPTION<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 14.8 for details on SLEEP mode.

#### 14.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>). (Section 7.0)

#### 14.5.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>). (Section 5.2)

| Note: | For the PIC16C73/74, if a change on the      |

|-------|----------------------------------------------|

|       | I/O pin should occur when the read opera-    |

|       | tion is being executed (start of the Q2      |

|       | cycle), then the RBIF interrupt flag may not |

|       | get set.                                     |

## 14.6 <u>Context Saving During Interrupts</u> Applicable Devices

# 72 73 73A 74 74A 76 77

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt i.e., W register and STATUS register. This will have to be implemented in software.

Example 14-1 stores and restores the STATUS, W, and PCLATH registers. The register, W\_TEMP, must be defined in each bank and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1).

The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Stores the PCLATH register.

- d) Executes the ISR code.

- e) Restores the STATUS register (and bank select bit).

- f) Restores the W and PCLATH registers.

### EXAMPLE 14-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

| MOVWF<br>SWAPF<br>CLRF | W_TEMP<br>STATUS,W<br>STATUS | ;Copy W to TEMP register, could be bank one or zero<br>;Swap status to be saved into W<br>;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

|------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVWF                  | STATUS_TEMP                  | ;Save status to bank zero STATUS_TEMP register                                                                                                    |

| MOVF                   | PCLATH, W                    | ;Only required if using pages 1, 2 and/or 3                                                                                                       |

| MOVWF                  | PCLATH_TEMP                  | ;Save PCLATH into W                                                                                                                               |

| CLRF                   | PCLATH                       | ;Page zero, regardless of current page                                                                                                            |

| BCF                    | STATUS, IRP                  | ;Return to Bank 0                                                                                                                                 |

| MOVF                   | FSR, W                       | ;Copy FSR to W                                                                                                                                    |

| MOVWF                  | FSR_TEMP                     | ;Copy FSR from W to FSR_TEMP                                                                                                                      |

| :                      |                              |                                                                                                                                                   |

| :(ISR)                 |                              |                                                                                                                                                   |

| :                      |                              |                                                                                                                                                   |

| MOVF                   | PCLATH_TEMP, W               | ;Restore PCLATH                                                                                                                                   |

| MOVWF                  | PCLATH                       | ;Move W into PCLATH                                                                                                                               |

| SWAPF                  | STATUS_TEMP,W                | ;Swap STATUS_TEMP register into W                                                                                                                 |

|                        |                              | ;(sets bank to original state)                                                                                                                    |

| MOVWF                  | STATUS                       | ;Move W into STATUS register                                                                                                                      |

| SWAPF                  | W_TEMP,F                     | ;Swap W_TEMP                                                                                                                                      |

| SWAPF                  | W_TEMP,W                     | ;Swap W_TEMP into W                                                                                                                               |

|                        |                              |                                                                                                                                                   |

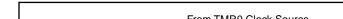

#### 14.7 Watchdog Timer (WDT) **Applicable Devices** 72 73 73A 74 74A 76 77

The Watchdog Timer is as a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLKOUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset). If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer Wake-up). The WDT can be permanently disabled by clearing configuration bit WDTE (Section 14.1).

### 14.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a

FIGURE 14-18: WATCHDOG TIMER BLOCK DIAGRAM

prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET condition.

The TO bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

14.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken into account that under worst case conditions (VDD = Min., Temperature = Max., and max. WDT prescaler) it may take several seconds before a WDT time-out occurs.

Note: When a CLRWDT instruction is executed and the prescaler is assigned to the WDT, the prescaler count will be cleared, but the prescaler assignment is not changed.

# FIGURE 14-19: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address  | Name         | Bit 7 | Bit 6                | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 |

|----------|--------------|-------|----------------------|-------|-------|----------------------|-------|-------|-------|

| 2007h    | Config. bits | (1)   | BODEN <sup>(1)</sup> | CP1   | CP0   | PWRTE <sup>(1)</sup> | WDTE  | FOSC1 | FOSC0 |

| 81h,181h | OPTION       | RBPU  | INTEDG               | TOCS  | TOSE  | PSA                  | PS2   | PS1   | PS0   |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Figure 14-1, and Figure 14-2 for operation of these bits.

| INCFSZ            | Increment f, Skip if 0                                                                                                                                                                                                    | IORLW             | Inclusive OR Literal with W                                                 |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------|

| Syntax:           | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                               | Syntax:           | [ <i>label</i> ] IORLW k                                                    |

| Operands:         | $0 \le f \le 127$                                                                                                                                                                                                         | Operands:         | $0 \le k \le 255$                                                           |

|                   | d ∈ [0,1]                                                                                                                                                                                                                 | Operation:        | (W) .OR. $k \rightarrow$ (W)                                                |

| Operation:        | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                | Status Affected:  | Z                                                                           |

| Status Affected:  | None                                                                                                                                                                                                                      | Encoding:         | 11 1000 kkkk kkkk                                                           |

| Encoding:         | 00 1111 dfff fff                                                                                                                                                                                                          | Description:      | The contents of the W register is OR'ed with the eight bit literal 'k'. The |

| Description:      | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed in                                                                                                                                    |                   | result is placed in the W register.                                         |

|                   | the W register. If 'd' is 1 the result is                                                                                                                                                                                 | Words:            | 1                                                                           |

|                   | placed back in register 'f'.<br>If the result is 1, the next instruction is                                                                                                                                               | Cycles:           | 1                                                                           |

|                   | executed. If the result is 0, a NOP is executed instead making it a 2Tcy                                                                                                                                                  | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                 |

| Words:            | instruction.                                                                                                                                                                                                              |                   | Decode Read Process Write to literal 'k' data W                             |

| Cycles:           | 1(2)                                                                                                                                                                                                                      | <b>F</b> ormula   |                                                                             |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                               | Example           | IORLW 0x35                                                                  |

|                   | Decode Read register 'f' Process Write to destination                                                                                                                                                                     |                   | Before Instruction<br>W = 0x9A<br>After Instruction                         |

| If Skip:          | (2nd Cycle)                                                                                                                                                                                                               |                   | W = 0xBF                                                                    |

|                   | Q1 Q2 Q3 Q4                                                                                                                                                                                                               |                   | Z = 1                                                                       |

|                   | No-<br>OperationNo-<br>OperationNo-<br>Operation                                                                                                                                                                          |                   |                                                                             |

| Example           | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE<br>•<br>•<br>Before Instruction<br>PC = address HERE<br>After Instruction<br>CNT = CNT + 1<br>if CNT= 0,<br>PC = address CONTINUE<br>if CNT $\neq$ 0,<br>PC = address HERE +1 |                   |                                                                             |

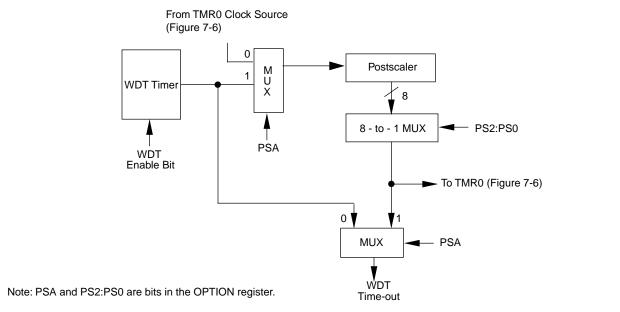

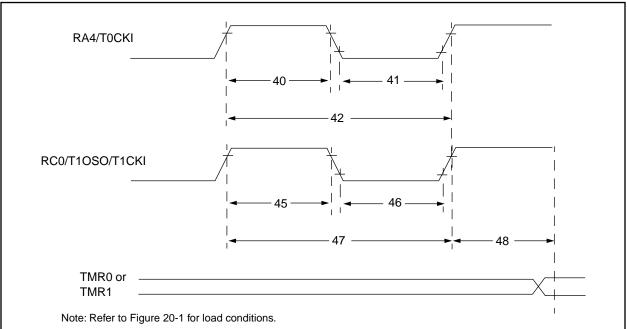

# Applicable Devices 72 73 73A 74 74A 76 77

| TABLE 17-5: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|-------------|-----------------------------------------------|

|-------------|-----------------------------------------------|

| Param<br>No. | Sym      | Characteristic                                 |                      |                    | Min                                              | Тур† | Max   | Units | Conditions                         |

|--------------|----------|------------------------------------------------|----------------------|--------------------|--------------------------------------------------|------|-------|-------|------------------------------------|

| 40*          | Tt0H     | T0CKI High Pulse V                             | Vidth                | No Prescaler       | 0.5Tcy + 20                                      | —    | —     | ns    | Must also meet                     |

|              |          |                                                |                      | With Prescaler     | 10                                               | _    | _     | ns    | parameter 42                       |

| 41*          | Tt0L     | T0CKI Low Pulse W                              | /idth                | No Prescaler       | 0.5TCY + 20                                      | -    | —     | ns    | Must also meet                     |

|              |          | -                                              |                      | With Prescaler     | 10                                               | —    | —     | ns    | parameter 42                       |

| 42*          | Tt0P     | T0CKI Period                                   |                      |                    | Tcy + 40                                         | _    | —     | ns    |                                    |

|              |          | V                                              |                      | With Prescaler     | Greater of:<br>20 or <u>Tcy + 40</u><br>N        | -    | _     | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Tt1H     | T1CKI High Time                                | Synchronous, F       | Prescaler = 1      | 0.5TCY + 20                                      | - 1  | _     | ns    | Must also meet                     |

|              |          |                                                | Synchronous,         | PIC16 <b>C</b> 7X  | 15                                               | - 1  | —     | ns    | parameter 47                       |

|              |          |                                                | Prescaler =<br>2,4,8 | PIC16 <b>LC</b> 7X | 25                                               | -    | —     | ns    | -                                  |

|              |          |                                                | Asynchronous         | PIC16 <b>C</b> 7X  | 30                                               | —    | —     | ns    |                                    |

|              |          |                                                |                      | PIC16 <b>LC</b> 7X | 50                                               | —    | —     | ns    |                                    |

| 46*          | Tt1L T   | T1CKI Low Time                                 | Synchronous, F       |                    | 0.5Tcy + 20                                      | -    | —     | ns    | Must also meet                     |

|              |          |                                                | Synchronous,         | PIC16 <b>C</b> 7X  | 15                                               | —    | —     | ns    | parameter 47                       |

|              |          |                                                | Prescaler =<br>2,4,8 | PIC16 <b>LC</b> 7X | 25                                               | -    | -     | ns    |                                    |

|              |          |                                                | Asynchronous         | PIC16 <b>C</b> 7X  | 30                                               | —    | —     | ns    |                                    |

|              |          |                                                |                      | PIC16 <b>LC</b> 7X | 50                                               | —    | —     | ns    |                                    |

| 47*          | Tt1P     | T1CKI input period                             | Synchronous          | PIC16 <b>C</b> 7X  | <u>Greater of:</u><br>30 OR <u>TCY + 40</u><br>N | -    | —     | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |          |                                                |                      | PIC16 <b>LC</b> 7X | <u>Greater of:</u><br>50 OR <u>TCY + 40</u><br>N |      |       |       | N = prescale value<br>(1, 2, 4, 8) |

|              |          |                                                |                      | PIC16 <b>C</b> 7X  | 60                                               | -    | —     | ns    |                                    |

|              |          |                                                |                      | PIC16 <b>LC</b> 7X | 100                                              | —    | —     | ns    |                                    |

|              | Ft1      | Timer1 oscillator inp<br>(oscillator enabled b |                      |                    | DC                                               | -    | 200   | kHz   |                                    |

| 48           | TCKEZtmr | 1 Delay from external                          | clock edge to tir    | ner increment      | 2Tosc                                            | _    | 7Tosc | —     |                                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Applicable Devices 72 73 73A 74 74A 76 77

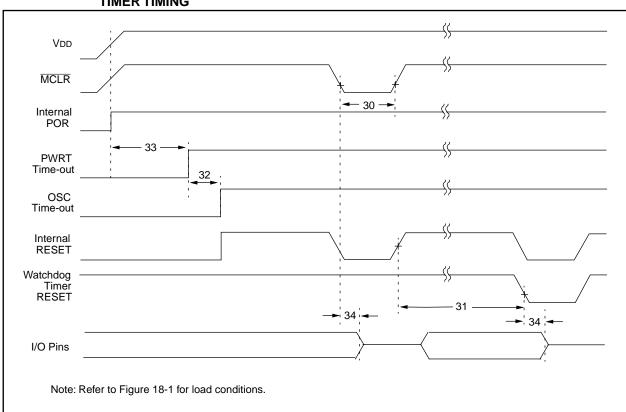

# FIGURE 18-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

# TABLE 18-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP<br/>TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†     | Max | Units | Conditions               |

|------------------|-------|--------------------------------------------------------|-----|----------|-----|-------|--------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                 | 100 | —        | —   | ns    | VDD = 5V, -40°C to +85°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +85°C |

| 32               | Tost  | Oscillation Start-up Timer Period                      | _   | 1024Tosc | —   | _     | Tosc = OSC1 period       |

| 33*              | Tpwrt | Power up Timer Period                                  | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +85°C |

| 34               | Tıoz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | —   | _        | 100 | ns    |                          |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16C7X

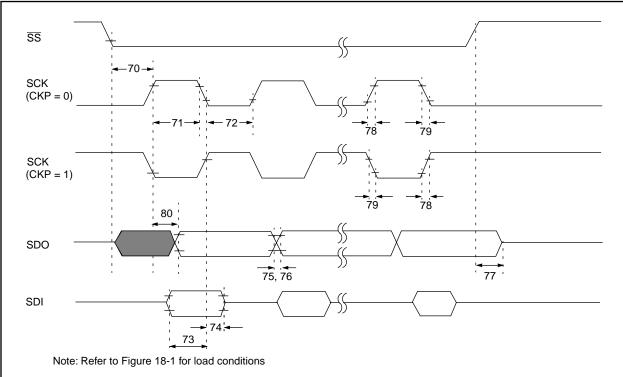

# Applicable Devices 72 73 73A 74 74A 76 77

# TABLE 18-8: SPI MODE REQUIREMENTS

| Parameter<br>No. | Sym                   | Characteristic                                                        | Min      | Тур† | Max | Units | Conditions |

|------------------|-----------------------|-----------------------------------------------------------------------|----------|------|-----|-------|------------|

| 70               | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input | Тсү      | —    | -   | ns    |            |

| 71               | TscH                  | SCK input high time (slave mode)                                      | TCY + 20 | _    | _   | ns    |            |

| 72               | TscL                  | SCK input low time (slave mode)                                       | TCY + 20 | _    | _   | ns    |            |

| 73               | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge                              | 50       | _    | _   | ns    |            |

| 74               | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                               | 50       | _    | -   | ns    |            |

| 75               | TdoR                  | SDO data output rise time                                             | _        | 10   | 25  | ns    |            |

| 76               | TdoF                  | SDO data output fall time                                             | _        | 10   | 25  | ns    |            |

| 77               | TssH2doZ              | SS↑ to SDO output hi-impedance                                        | 10       | _    | 50  | ns    |            |

| 78               | TscR                  | SCK output rise time (master mode)                                    | _        | 10   | 25  | ns    |            |

| 79               | TscF                  | SCK output fall time (master mode)                                    | _        | 10   | 25  | ns    |            |

| 80               | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge                                  | _        | _    | 50  | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

|       | Applicable Devices 72 73 73A 74 74A 76 77     |                                                                                                                                                                                         |                   |       |                  |       |                                                                           |  |  |  |

|-------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|------------------|-------|---------------------------------------------------------------------------|--|--|--|

| 20.3  | PIC10<br>PIC10                                | 6C76/77-04 (Commercial, Industrial, Extended)<br>6C76/77-10 (Commercial, Industrial, Extended)<br>6C76/77-20 (Commercial, Industrial, Extended)<br>6LC76/77-04 (Commercial, Industrial) |                   |       |                  |       |                                                                           |  |  |  |

|       |                                               |                                                                                                                                                                                         | ird Opera         |       |                  |       | less otherwise stated)<br>TA $\leq$ +125°C for extended,                  |  |  |  |

|       | ARACTERISTICS                                 | operati                                                                                                                                                                                 | ing tempe         | latai | -40              |       | $TA \leq +85^{\circ}C$ for industrial and                                 |  |  |  |

|       |                                               | Operati<br>Section                                                                                                                                                                      |                   | e Vd  | 0°C<br>D range a |       | $TA \le +70^{\circ}C$ for commercial<br>ribed in DC spec Section 20.1 and |  |  |  |

| Param | Characteristic                                | Sym                                                                                                                                                                                     | Min               | Тур   | Мах              | Units | Conditions                                                                |  |  |  |

| No.   |                                               |                                                                                                                                                                                         |                   | †     |                  |       |                                                                           |  |  |  |

|       | Input Low Voltage                             |                                                                                                                                                                                         |                   |       |                  |       |                                                                           |  |  |  |

|       | I/O ports                                     | VIL                                                                                                                                                                                     |                   |       |                  |       |                                                                           |  |  |  |

| D030  | with TTL buffer                               |                                                                                                                                                                                         | Vss               | -     | 0.15Vdd          |       | For entire VDD range                                                      |  |  |  |

| D030A |                                               |                                                                                                                                                                                         | Vss               | -     | 0.8V             | V     | $4.5V \le VDD \le 5.5V$                                                   |  |  |  |

| D031  | with Schmitt Trigger buffer                   |                                                                                                                                                                                         | Vss               | -     | 0.2VDD           | V     |                                                                           |  |  |  |

| D032  | MCLR, OSC1 (in RC mode)                       |                                                                                                                                                                                         | Vss               | -     | 0.2VDD           | V     | NI-4-4                                                                    |  |  |  |

| D033  | OSC1 (in XT, HS and LP)<br>Input High Voltage |                                                                                                                                                                                         | Vss               | -     | 0.3Vdd           | V     | Note1                                                                     |  |  |  |

|       | I/O ports                                     | ViH                                                                                                                                                                                     |                   | -     |                  |       |                                                                           |  |  |  |

| D040  | with TTL buffer                               | VIII                                                                                                                                                                                    | 2.0               | _     | VDD              | v     | $4.5V \leq VDD \leq 5.5V$                                                 |  |  |  |

| D040A |                                               |                                                                                                                                                                                         | 0.25VDD<br>+ 0.8V | -     | VDD              | V     | For entire VDD range                                                      |  |  |  |

| D041  | with Schmitt Trigger buffer                   |                                                                                                                                                                                         | 0.8VDD            | -     | Vdd              | v     | For entire VDD range                                                      |  |  |  |