Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                              |

| Data Converters            | A/D 5x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c76-20i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

4.2.2.5 PIR1 REGISTER

Applicable Devices

This register contains the individual flag bits for the Peripheral interrupts.

FIGURE 4-12: PIR1 REGISTER PIC16C72 (ADDRESS 0Ch)

# Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### U-0 R/W-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 ADIF SSPIF CCP1IF TMR2IF TMR1IF = Readable bit R = Writable bit W bit0 bit7 = Unimplemented bit, U read as '0' n = Value at POR reset bit 7: Unimplemented: Read as '0' bit 6: ADIF: A/D Converter Interrupt Flag bit 1 = An A/D conversion completed (must be cleared in software) 0 = The A/D conversion is not complete bit 5-4: Unimplemented: Read as '0' bit 3: SSPIF: Synchronous Serial Port Interrupt Flag bit 1 = The transmission/reception is complete (must be cleared in software) 0 = Waiting to transmit/receive bit 2: CCP1IF: CCP1 Interrupt Flag bit Capture Mode 1 = A TMR1 register capture occurred (must be cleared in software) 0 = No TMR1 register capture occurred Compare Mode 1 = A TMR1 register compare match occurred (must be cleared in software) 0 = No TMR1 register compare match occurred PWM Mode Unused in this mode TMR2IF: TMR2 to PR2 Match Interrupt Flag bit bit 1: 1 = TMR2 to PR2 match occurred (must be cleared in software) 0 = No TMR2 to PR2 match occurred bit 0: TMR1IF: TMR1 Overflow Interrupt Flag bit 1 = TMR1 register overflowed (must be cleared in software) 0 = TMR1 register did not overflow Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# 8.3 <u>Timer1 Operation in Asynchronous</u> <u>Counter Mode</u> Applicable Devices 72 73 73A 74 74A 76 77

If control bit T1SYNC (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt on overflow which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 8.3.2).

In asynchronous counter mode, Timer1 can not be used as a time-base for capture or compare operations.

# 8.3.1 EXTERNAL CLOCK INPUT TIMING WITH UNSYNCHRONIZED CLOCK

If control bit T1SYNC is set, the timer will increment completely asynchronously. The input clock must meet certain minimum high time and low time requirements. Refer to the appropriate Electrical Specifications Section, timing parameters 45, 46, and 47.

# 8.3.2 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running, from an external asynchronous clock, will guarantee a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself poses certain problems since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Example 8-1 is an example routine to read the 16-bit timer value. This is useful if the timer cannot be stopped.

#### EXAMPLE 8-1: READING A 16-BIT FREE-RUNNING TIMER

```

; All interrupts are disabled

MOVE

TMR1H, W ;Read high byte

MOVWF TMPH

;

TMR1L, W ;Read low byte

MOVF

MOVWE TMPL

;

MOVF

TMR1H, W ;Read high byte

TMPH, W ;Sub 1st read

SUBWF

; with 2nd read

BTFSC STATUS,Z ;Is result = 0

CONTINUE ;Good 16-bit read

GOTO

;

; TMR1L may have rolled over between the read

of the high and low bytes. Reading the high

;

and low bytes now will read a good value.

MOVF

TMR1H, W ;Read high byte

MOVWF

TMPH

TMR1L, W ;Read low byte

MOVE

MOVWE TMPL

;

; Re-enable the Interrupt (if required)

;Continue with your code

CONTINUE

```

# 8.4 <u>Timer1 Oscillator</u> Applicable Devices 72 73 73 74 74 76 77

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 8-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

## TABLE 8-1: CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR

| Osc Type                                                                                                                                                                                                                                                                                                                                                 | Freq                           | C1                    | C2    |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------|-------|--|--|--|--|

| LP                                                                                                                                                                                                                                                                                                                                                       | 32 kHz                         | 33 pF                 | 33 pF |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                          | 100 kHz                        | 15 pF                 |       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                          | 200 kHz                        | 15 pF                 | 15 pF |  |  |  |  |

| These values are for design guidance only.                                                                                                                                                                                                                                                                                                               |                                |                       |       |  |  |  |  |

| <b>Crystals Tes</b>                                                                                                                                                                                                                                                                                                                                      | ted:                           |                       |       |  |  |  |  |

| 32.768 kHz                                                                                                                                                                                                                                                                                                                                               | Epson C-001R32.768K-A ± 20 PPM |                       |       |  |  |  |  |

| 100 kHz                                                                                                                                                                                                                                                                                                                                                  | Epson C-2 1                    | Epson C-2 100.00 KC-P |       |  |  |  |  |

| 200 kHz                                                                                                                                                                                                                                                                                                                                                  | STD XTL 20                     | STD XTL 200.000 kHz : |       |  |  |  |  |

| <ul> <li>200 kHz STD XTL 200.000 kHz ± 20 PPM</li> <li>Note 1: Higher capacitance increases the stability of oscillator but also increases the start-up time.</li> <li>2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.</li> </ul> |                                |                       |       |  |  |  |  |

# 10.0 CAPTURE/COMPARE/PWM MODULE(s)

Applicable Devices

72

73

73A

74

74A

76

77

CCP1

72

73

73A

74

74A

76

77

CCP2

Each CCP (Capture/Compare/PWM) module contains a 16-bit register which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave Duty Cycle register. Both the CCP1 and CCP2 modules are identical in operation, with the exception of the operation of the special event trigger. Table 10-1 and Table 10-2 show the resources and interactions of the CCP module(s). In the following sections, the operation of a CCP module is described with respect to CCP1. CCP2 operates the same as CCP1, except where noted.

## CCP1 module:

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

## CCP2 module:

Capture/Compare/PWM Register2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. All are readable and writable.

For use of the CCP modules, refer to the Embedded Control Handbook, "Using the CCP Modules" (AN594).

## TABLE 10-1: CCP MODE - TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

# TABLE 10-2: INTERACTION OF TWO CCP MODULES

| CCPx Mode | CCPy Mode | Interaction                                                                           |

|-----------|-----------|---------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time-base.                                                                  |

| Capture   | Compare   | The compare should be configured for the special event trigger, which clears TMR1.    |

| Compare   | Compare   | The compare(s) should be configured for the special event trigger, which clears TMR1. |

| PWM       | PWM       | The PWMs will have the same frequency, and update rate (TMR2 interrupt).              |

| PWM       | Capture   | None                                                                                  |

| PWM       | Compare   | None                                                                                  |

## 11.5.1.3 TRANSMISSION

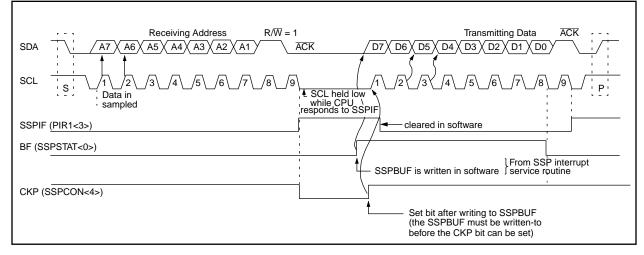

When the  $R\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The  $\overline{ACK}$  pulse will be sent on the ninth bit, and pin RC3/SCK/SCL is held low. The transmit data must be loaded into the SSP-BUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 11-26). An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software, and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP.

## FIGURE 11-26: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

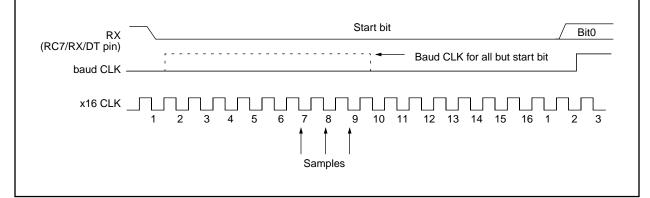

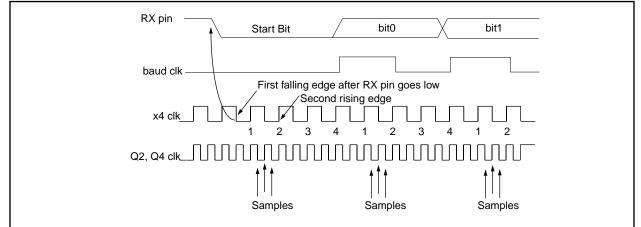

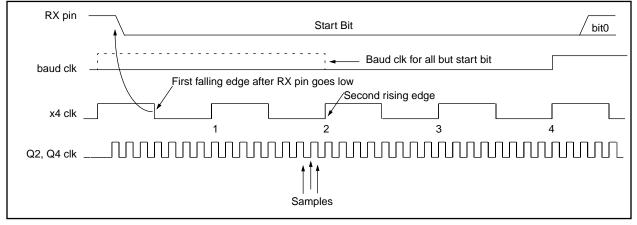

#### 12.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin. If bit BRGH (TXSTA<2>) is clear (i.e., at the low baud rates), the sampling is done on the seventh, eighth and ninth falling edges of a x16 clock (Figure 12-3). If bit BRGH is set (i.e., at the high baud rates), the sampling is done on the 3 clock edges preceding the second rising edge after the first falling edge of a x4 clock (Figure 12-4 and Figure 12-5).

## FIGURE 12-3: RX PIN SAMPLING SCHEME. BRGH = 0 (PIC16C73/73A/74/74A)

#### FIGURE 12-4: RX PIN SAMPLING SCHEME, BRGH = 1 (PIC16C73/73A/74/74A)

## 12.3 USART Synchronous Master Mode

# Applicable Devices 72 73 73A 74 74A 76 77

In Synchronous Master mode, the data is transmitted in a half-duplex manner i.e. transmission and reception do not occur at the same time. When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition enable bit SPEN (RCSTA<7>) is set in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

#### 12.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 12-7. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer register TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one Tcycle), the TXREG is empty and interrupt bit, TXIF (PIR1<4>) is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the CK line. Data out is stable around the falling edge of the synchronous clock (Figure 12-12). The transmission can also be started by first loading the TXREG register and then setting bit TXEN (Figure 12-13). This is advantageous when slow baud rates are selected, since the BRG is kept in reset when bits TXEN, CREN, and SREN are clear. Setting enable bit TXEN will start the BRG, creating a shift clock immediately. Normally when transmission is first started, the TSR register is empty, so a transfer to the TXREG register will result in an immediate transfer to TSR resulting in an empty TXREG. Back-to-back transfers are possible.

Clearing enable bit TXEN, during a transmission, will cause the transmission to be aborted and will reset the transmitter. The DT and CK pins will revert to hi-impedance. If either bit CREN or bit SREN is set, during a transmission, the transmission is aborted and the DT pin reverts to a hi-impedance state (for a reception). The CK pin will remain an output if bit CSRC is set (internal clock). The transmitter logic however is not reset although it is disconnected from the pins. In order to reset the transmitter, the user has to clear bit TXEN. If bit SREN is set (to interrupt an on-going transmission and receive a single word), then after the single word is received, bit SREN will be cleared and the serial port will revert back to transmitting since bit TXEN is still set. The DT line will immediately switch from hi-impedance receive mode to transmit and start driving. To avoid this, bit TXEN should be cleared.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG can result in an immediate transfer of the data to the TSR register (if the TSR is empty). If the TSR was empty and the TXREG was written before writing the "new" TX9D, the "present" value of bit TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 12.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

# 13.5 A/D Operation During Sleep

Applicable Devices

72

73

73

74

74

76

77

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed the GO/DONE bit will be cleared, and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

Note: For the A/D module to operate in SLEEP, the A/D clock source must be set to RC (ADCS1:ADCS0 = 11). To perform an A/D conversion in SLEEP, ensure the SLEEP instruction immediately follows the instruction that sets the GO/DONE bit.

# 13.6 <u>A/D Accuracy/Error</u> Applicable Devices 72 73 73A 74 74A 76 77

The absolute accuracy specified for the A/D converter includes the sum of all contributions for quantization error, integral error, differential error, full scale error, offset error, and monotonicity. It is defined as the maximum deviation from an actual transition versus an ideal transition for any code. The absolute error of the A/D converter is specified at < $\pm$ 1 LSb for VDD = VREF (over the device's specified operating range). However, the accuracy of the A/D converter will degrade as VDD diverges from VREF.

For a given range of analog inputs, the output digital code will be the same. This is due to the quantization of the analog input to a digital code. Quantization error is typically  $\pm$  1/2 LSb and is inherent in the analog to digital conversion process. The only way to reduce quantization error is to increase the resolution of the A/D converter.

Offset error measures the first actual transition of a code versus the first ideal transition of a code. Offset error shifts the entire transfer function. Offset error can be calibrated out of a system or introduced into a system through the interaction of the total leakage current and source impedance at the analog input.

Gain error measures the maximum deviation of the last actual transition and the last ideal transition adjusted for offset error. This error appears as a change in slope of the transfer function. The difference in gain error to full scale error is that full scale does not take offset error into account. Gain error can be calibrated out in software.

Linearity error refers to the uniformity of the code changes. Linearity errors cannot be calibrated out of the system. Integral non-linearity error measures the actual code transition versus the ideal code transition adjusted by the gain error for each code.

Differential non-linearity measures the maximum actual code width versus the ideal code width. This measure is unadjusted.

The maximum pin leakage current is  $\pm$  1  $\mu$ A.

In systems where the device frequency is low, use of the A/D RC clock is preferred. At moderate to high frequencies, TAD should be derived from the device oscillator. TAD must not violate the minimum and should be  $\leq 8 \ \mu s$  for preferred operation. This is because TAD, when derived from TOSC, is kept away from on-chip phase clock transitions. This reduces, to a large extent, the effects of digital switching noise. This is not possible with the RC derived clock. The loss of accuracy due to digital switching noise can be significant if many I/O pins are active.

In systems where the device will enter SLEEP mode after the start of the A/D conversion, the RC clock source selection is required. In this mode, the digital noise from the modules in SLEEP are stopped. This method gives high accuracy.

# 13.7 Effects of a RESET

Applicable Devices

72

73

73A

74

74A

76

77

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted.

The value that is in the ADRES register is not modified for a Power-on Reset. The ADRES register will contain unknown data after a Power-on Reset.

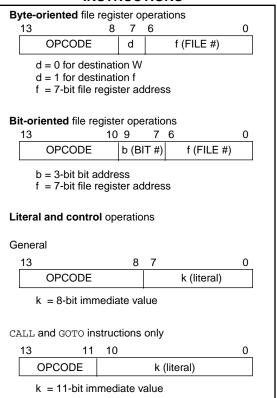

# 15.0 INSTRUCTION SET SUMMARY

Each PIC16CXX instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXX instruction set summary in Table 15-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 15-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

# TABLE 15-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| x             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                   |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| PCLATH        | Program Counter High Latch                                                                                                                                                     |

| GIE           | Global Interrupt Enable bit                                                                                                                                                    |

| WDT           | Watchdog Timer/Counter                                                                                                                                                         |

| TO            | Time-out bit                                                                                                                                                                   |

| PD            | Power-down bit                                                                                                                                                                 |

| dest          | Destination either the W register or the specified register file location                                                                                                      |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| <>            | Register bit field                                                                                                                                                             |

| ∈             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 15-2 lists the instructions recognized by the MPASM assembler.

Figure 15-1 shows the general formats that the instructions can have.

**Note:** To maintain upward compatibility with future PIC16CXX products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

# FIGURE 15-1: GENERAL FORMAT FOR INSTRUCTIONS

| GOTO              | Unconditional                                                                                     | Branch                                         |                           | INCF              | Increme                                           | nt f                         |                            |                      |  |

|-------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------|-------------------|---------------------------------------------------|------------------------------|----------------------------|----------------------|--|

| Syntax:           | [label] GOT                                                                                       | ) k                                            |                           | Syntax:           | [ label ]                                         | INCF                         | f,d                        |                      |  |

| Operands:         | $0 \leq k \leq 2047$                                                                              |                                                |                           | Operands:         | $0 \le f \le 12$                                  | 27                           |                            |                      |  |

| Operation:        | $k \rightarrow PC < 10:0 >$                                                                       |                                                |                           |                   | d ∈ [0,1]                                         |                              |                            |                      |  |

|                   | PCLATH<4:3>                                                                                       | $\rightarrow$ PC<12:1                          | 1>                        | Operation:        | (f) + 1 $\rightarrow$ (destination)               |                              |                            |                      |  |

| Status Affected:  | None                                                                                              |                                                |                           | Status Affected:  | Z                                                 |                              |                            |                      |  |

| Encoding:         | 10 1kkł                                                                                           | kkkk                                           | kkkk                      | Encoding:         | 00                                                | 1010                         | dfff                       | ffff                 |  |

| Description:      | GOTO is an uncon<br>eleven bit immed<br>into PC bits <10:<br>PC are loaded fr<br>GOTO is a two cy | ate value is lo<br>)>. The upper<br>om PCLATH< | oaded<br>bits of<br>4:3>. | Description:      | The conte<br>mented. If<br>the W reg<br>placed ba | 'd' is 0 th<br>ister. If 'd' | e result is<br>is 1 the re | placed in            |  |

| Words:            | 1                                                                                                 |                                                |                           | Words:            | 1                                                 |                              |                            |                      |  |

| Cycles:           | 2                                                                                                 |                                                |                           | Cycles:           | 1                                                 |                              |                            |                      |  |

| Q Cycle Activity: | Q1 Q2                                                                                             | Q3                                             | Q4                        | Q Cycle Activity: | Q1                                                | Q2                           | Q3                         | Q4                   |  |

| 1st Cycle         | Decode Rea<br>literal                                                                             |                                                | Write to<br>PC            |                   | Decode                                            | Read<br>register<br>'f'      | Process<br>data            | Write to destination |  |

| 2nd Cycle         | No- No<br>Operation Opera                                                                         | ion Operation                                  | No-<br>Operation          |                   |                                                   |                              |                            |                      |  |

|                   |                                                                                                   |                                                |                           | Example           | INCF                                              | CNT,                         | 1                          |                      |  |

| Example           | GOTO THERE                                                                                        |                                                |                           |                   | Before Ir                                         |                              | -                          | -                    |  |

|                   | After Instruction                                                                                 | n                                              |                           |                   |                                                   | CNT<br>7                     | = 0xF<br>= 0               | F                    |  |

|                   | PC =                                                                                              | Address                                        | THERE                     |                   | After Inst                                        | _                            | - 0                        |                      |  |

|                   |                                                                                                   |                                                |                           |                   |                                                   | CNT                          | = 0x0                      | 0                    |  |

|                   |                                                                                                   |                                                |                           |                   |                                                   | Z                            | = 1                        |                      |  |

| INCFSZ            | Increment f, Skip if 0                                                                                                                                                                                                    | IORLW             | Inclusive OR Literal with W                                                 |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------|

| Syntax:           | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                               | Syntax:           | [ <i>label</i> ] IORLW k                                                    |

| Operands:         | $0 \le f \le 127$                                                                                                                                                                                                         | Operands:         | $0 \le k \le 255$                                                           |

|                   | d ∈ [0,1]                                                                                                                                                                                                                 | Operation:        | (W) .OR. $k \rightarrow$ (W)                                                |

| Operation:        | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                | Status Affected:  | Z                                                                           |

| Status Affected:  | None                                                                                                                                                                                                                      | Encoding:         | 11 1000 kkkk kkkk                                                           |

| Encoding:         | 00 1111 dfff fff                                                                                                                                                                                                          | Description:      | The contents of the W register is OR'ed with the eight bit literal 'k'. The |

| Description:      | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed in                                                                                                                                    |                   | result is placed in the W register.                                         |

|                   | the W register. If 'd' is 1 the result is                                                                                                                                                                                 | Words:            | 1                                                                           |

|                   | placed back in register 'f'.<br>If the result is 1, the next instruction is                                                                                                                                               | Cycles:           | 1                                                                           |

|                   | executed. If the result is 0, a NOP is executed instead making it a 2Tcy                                                                                                                                                  | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                 |

| Words:            | instruction.                                                                                                                                                                                                              |                   | Decode Read Process Write to literal 'k' data W                             |

| Cycles:           | 1(2)                                                                                                                                                                                                                      | <b>F</b> ormula   |                                                                             |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                               | Example           | IORLW 0x35                                                                  |

|                   | Decode Read register 'f' Process Write to destination                                                                                                                                                                     |                   | Before Instruction<br>W = 0x9A<br>After Instruction                         |

| If Skip:          | (2nd Cycle)                                                                                                                                                                                                               |                   | W = 0xBF                                                                    |

|                   | Q1 Q2 Q3 Q4                                                                                                                                                                                                               |                   | Z = 1                                                                       |

|                   | No-<br>OperationNo-<br>OperationNo-<br>Operation                                                                                                                                                                          |                   |                                                                             |

| Example           | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE<br>•<br>•<br>Before Instruction<br>PC = address HERE<br>After Instruction<br>CNT = CNT + 1<br>if CNT= 0,<br>PC = address CONTINUE<br>if CNT $\neq$ 0,<br>PC = address HERE +1 |                   |                                                                             |

# PIC16C7X

| IORWF             | Inclusive                                                                                                                                                            | Inclusive OR W with f                                             |                  |                      |  |  |  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------|----------------------|--|--|--|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                            | IORWF                                                             | f,d              |                      |  |  |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$                                                                                                     | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$ |                  |                      |  |  |  |  |  |  |

| Operation:        | (W) .OR.                                                                                                                                                             | (W) .OR. (f) $\rightarrow$ (destination)                          |                  |                      |  |  |  |  |  |  |

| Status Affected:  | Z                                                                                                                                                                    |                                                                   |                  |                      |  |  |  |  |  |  |

| Encoding:         | 00                                                                                                                                                                   | 0100                                                              | dfff             | ffff                 |  |  |  |  |  |  |

| Description:      | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'. |                                                                   |                  |                      |  |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                    |                                                                   |                  |                      |  |  |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                    |                                                                   |                  |                      |  |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                   | Q2                                                                | Q3               | Q4                   |  |  |  |  |  |  |

|                   | Decode                                                                                                                                                               | Read<br>register<br>'f'                                           | Process<br>data  | Write to destination |  |  |  |  |  |  |

| Example           | IORWF                                                                                                                                                                |                                                                   | RESULT,          | 0                    |  |  |  |  |  |  |

|                   | Before In                                                                                                                                                            |                                                                   |                  |                      |  |  |  |  |  |  |

|                   |                                                                                                                                                                      | RESULT<br>W                                                       | = 0x13<br>= 0x91 | -                    |  |  |  |  |  |  |

|                   | After Inst                                                                                                                                                           |                                                                   |                  | 3                    |  |  |  |  |  |  |

| MOVLW             | Move Literal to W                                                                          |  |  |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:           | [ <i>label</i> ] MOVLW k                                                                   |  |  |  |  |  |  |

| Operands:         | $0 \le k \le 255$                                                                          |  |  |  |  |  |  |

| Operation:        | $k \rightarrow (W)$                                                                        |  |  |  |  |  |  |

| Status Affected:  | None                                                                                       |  |  |  |  |  |  |

| Encoding:         | 11 00xx kkkk kkkk                                                                          |  |  |  |  |  |  |

| Description:      | The eight bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |  |  |  |  |  |  |

| Words:            | 1                                                                                          |  |  |  |  |  |  |

| Cycles:           | 1                                                                                          |  |  |  |  |  |  |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                |  |  |  |  |  |  |

|                   | Decode Read literal 'k' Process Write to W                                                 |  |  |  |  |  |  |

| Example           | MOVLW $0x5A$<br>After Instruction<br>W = 0x5A                                              |  |  |  |  |  |  |

| MOVF              | Move f                                                                                                                                                                                                                                                          |                                                                   |                 |                      |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------|----------------------|--|--|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                                                                                       | MOVF                                                              | f,d             |                      |  |  |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                                | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$ |                 |                      |  |  |  |  |  |

| Operation:        | (f) $\rightarrow$ (de                                                                                                                                                                                                                                           | (f) $\rightarrow$ (destination)                                   |                 |                      |  |  |  |  |  |

| Status Affected:  | Z                                                                                                                                                                                                                                                               |                                                                   |                 |                      |  |  |  |  |  |

| Encoding:         | 00                                                                                                                                                                                                                                                              | 1000                                                              | dfff            | ffff                 |  |  |  |  |  |

| Description:      | The contents of register f is moved to a destination dependant upon the status of d. If $d = 0$ , destination is W register. If $d = 1$ , the destination is file register f itself. $d = 1$ is useful to test a file register since status flag Z is affected. |                                                                   |                 |                      |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                               |                                                                   |                 |                      |  |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                               |                                                                   |                 |                      |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                                                              | Q2                                                                | Q3              | Q4                   |  |  |  |  |  |

|                   | Decode                                                                                                                                                                                                                                                          | Read<br>register<br>'f'                                           | Process<br>data | Write to destination |  |  |  |  |  |

| Example           | MOVF                                                                                                                                                                                                                                                            | ,                                                                 | 0               |                      |  |  |  |  |  |

|                   | After Instruction<br>W = value in FSR register<br>Z = 1                                                                                                                                                                                                         |                                                                   |                 |                      |  |  |  |  |  |

| MOVWF             | Move W                                                           | to f                    | Move W to f     |                       |  |  |  |  |  |  |

|-------------------|------------------------------------------------------------------|-------------------------|-----------------|-----------------------|--|--|--|--|--|--|

| Syntax:           | [ label ]                                                        | MOVW                    | = f             |                       |  |  |  |  |  |  |

| Operands:         | $0 \le f \le 12$                                                 | 27                      |                 |                       |  |  |  |  |  |  |

| Operation:        | $(W) \rightarrow (f)$                                            |                         |                 |                       |  |  |  |  |  |  |

| Status Affected:  | None                                                             | None                    |                 |                       |  |  |  |  |  |  |

| Encoding:         | 00                                                               | 0000                    | lfff            | ffff                  |  |  |  |  |  |  |

| Description:      | Move data<br>'f'.                                                | from W r                | egister to      | register              |  |  |  |  |  |  |

| Words:            | 1                                                                |                         |                 |                       |  |  |  |  |  |  |

| Cycles:           | 1                                                                |                         |                 |                       |  |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                               | Q2                      | Q3              | Q4                    |  |  |  |  |  |  |

|                   | Decode                                                           | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |  |  |  |  |  |

| Example           | MOVWF                                                            | OPTIC                   | DN_REG          |                       |  |  |  |  |  |  |

|                   | Before In                                                        |                         |                 | -                     |  |  |  |  |  |  |

|                   | $\begin{array}{rcl} OPTION &= & 0xFF \\ W &= & 0x4F \end{array}$ |                         |                 |                       |  |  |  |  |  |  |

|                   | After Inst                                                       | ruction                 |                 |                       |  |  |  |  |  |  |

|                   |                                                                  | OPTION                  |                 |                       |  |  |  |  |  |  |

|                   |                                                                  | W                       | = 0x4           | F                     |  |  |  |  |  |  |

| <u> 8</u> 8 5              |                                                    |                                       |                                                    |                      |                                                                  |                                                |                                    |                                              |                                                     |                                         |                                   |                                      |          |          |          |                                       |

|----------------------------|----------------------------------------------------|---------------------------------------|----------------------------------------------------|----------------------|------------------------------------------------------------------|------------------------------------------------|------------------------------------|----------------------------------------------|-----------------------------------------------------|-----------------------------------------|-----------------------------------|--------------------------------------|----------|----------|----------|---------------------------------------|

| HCS200<br>HCS300<br>HCS301 |                                                    |                                       |                                                    |                      |                                                                  |                                                |                                    |                                              |                                                     | 7                                       | 7                                 |                                      |          |          |          | 7                                     |

| 24CXX<br>25CXX<br>93CXX    |                                                    |                                       |                                                    |                      |                                                                  |                                                | 7                                  |                                              |                                                     | 7                                       |                                   | 7                                    |          |          |          |                                       |

| PIC17C75X                  | Available<br>3Q97                                  |                                       | 7                                                  | 7                    |                                                                  |                                                |                                    |                                              | 7                                                   | 7                                       |                                   |                                      |          |          |          |                                       |

| PIC17C4X                   | 2                                                  |                                       | 7                                                  | 7                    | 7                                                                | 7                                              |                                    |                                              | 7                                                   | 7                                       |                                   |                                      | 7        |          |          |                                       |

| PIC16C9XX                  | 2                                                  |                                       | 7                                                  | 7                    | 7                                                                |                                                |                                    |                                              | 7                                                   | 7                                       |                                   |                                      |          |          | 7        |                                       |

| PIC16C8X                   | 2                                                  | 7                                     | 7                                                  | 7                    | 7                                                                | 7                                              |                                    | 7                                            | 7                                                   | 7                                       |                                   |                                      | 7        |          |          |                                       |

| PIC16C7XX                  | 7                                                  | 7                                     | 7                                                  | 7                    | 7                                                                | 7                                              |                                    | 7                                            | 7                                                   | 7                                       |                                   |                                      |          | 7        |          |                                       |

| PIC16C6X                   | 7                                                  | 7                                     | 7                                                  | 7                    | 7                                                                | 7                                              |                                    | 7                                            | 7                                                   | 7                                       |                                   |                                      |          | 7        |          |                                       |

| PIC16CXXX                  | 7                                                  | 7                                     | 7                                                  | 7                    | 7                                                                | 7                                              |                                    |                                              | 7                                                   | 7                                       |                                   |                                      | 7        |          |          |                                       |

| PIC16C5X                   | 7                                                  | 7                                     | 7                                                  | 2                    | 7                                                                | 7                                              |                                    | 7                                            | 7                                                   | 7                                       |                                   |                                      | 7        |          |          |                                       |

| PIC14000                   | 7                                                  |                                       | 7                                                  | 7                    | 7                                                                |                                                |                                    |                                              | 7                                                   | 7                                       |                                   |                                      |          |          |          |                                       |

| PIC12C5XX                  | 2                                                  | 7                                     | 7                                                  | 2                    | 7                                                                |                                                |                                    |                                              | 7                                                   | 7                                       |                                   |                                      |          |          |          |                                       |

|                            | PICMASTER®/<br>PICMASTER-CE<br>In-Circuit Emulator | CEPIC Low-Cost<br>In-Circuit Emulator | MPLAB™<br>Integrated<br>Development<br>Environment | MPLAB™ C<br>Compiler | Lo fuzzyTECH®-MP<br>Explorer/Edition<br>Fuzzy Logic<br>Dev. Tool | MP-DriveWay™<br>Applications<br>Code Generator | Total Endurance™<br>Software Model | PICSTART®<br>Lite Ultra Low-Cost<br>Dev. Kit | 0. PICSTART®<br>Plus Low-Cost<br>Universal Dev. Kit | PRO MATE® II<br>Universal<br>Programmer | KEELOQ <sup>®</sup><br>Programmer | SEEVAL <sup>®</sup><br>Designers Kit | PICDEM-1 | PICDEM-2 | BICDEM-3 | KEELOQ <sup>®</sup><br>Evaluation Kit |

# TABLE 16-1: DEVELOPMENT TOOLS FROM MICROCHIP

Applicable Devices 72 73 73A 74 74A 76 77

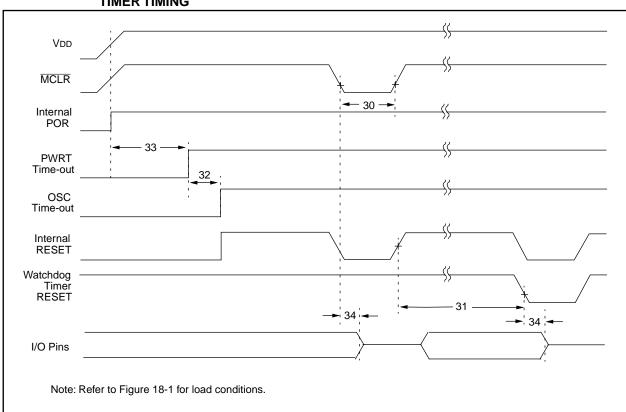

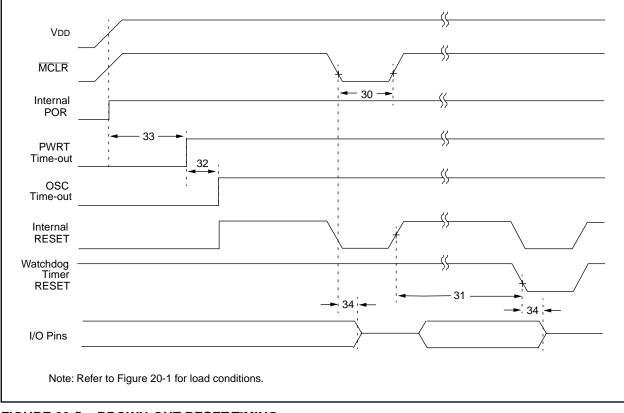

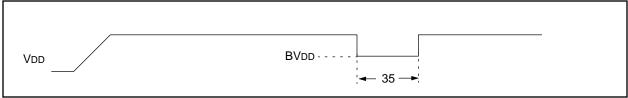

# FIGURE 18-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

# TABLE 18-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP<br/>TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†     | Max | Units | Conditions               |

|------------------|-------|--------------------------------------------------------|-----|----------|-----|-------|--------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                 | 100 | —        | _   | ns    | VDD = 5V, -40°C to +85°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +85°C |

| 32               | Tost  | Oscillation Start-up Timer Period                      | _   | 1024Tosc | —   | _     | Tosc = OSC1 period       |

| 33*              | Tpwrt | Power up Timer Period                                  | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +85°C |

| 34               | Tıoz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | —   | _        | 100 | ns    |                          |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

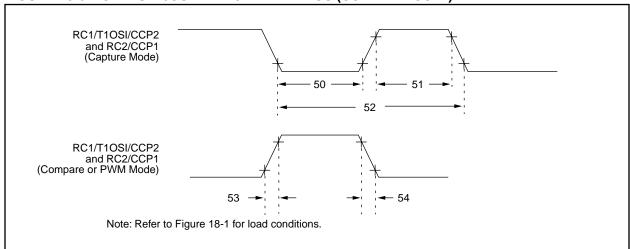

# Applicable Devices 72 73 73A 74 74A 76 77

# FIGURE 18-6: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

## TABLE 18-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Parameter<br>No. | Sym  | Characteristic             |                                 |                       | Min                   | Тур† | Max | Units | Conditions                        |

|------------------|------|----------------------------|---------------------------------|-----------------------|-----------------------|------|-----|-------|-----------------------------------|

| 50*              | TccL | CCP1 and CCP2              | No Prescaler                    |                       | 0.5Tcy + 20           | —    | _   | ns    |                                   |

|                  |      | input low time             |                                 | PIC16 <b>C</b> 73/74  | 10                    | _    | _   | ns    |                                   |

|                  |      |                            | With Prescaler                  | PIC16 <b>LC</b> 73/74 | 20                    | —    | _   | ns    |                                   |

| 51*              | TccH | CCP1 and CCP2 No Prescaler |                                 |                       | 0.5Tcy + 20           | —    | —   | ns    |                                   |

|                  |      | input high time            |                                 | PIC16 <b>C</b> 73/74  | 10                    |      | -   | ns    |                                   |

|                  |      |                            | With Prescaler                  | PIC16 <b>LC</b> 73/74 | 20                    | —    | _   | ns    |                                   |

| 52*              | TccP | CCP1 and CCP2 in           | nput period                     |                       | <u>3Tcy + 40</u><br>N | _    | _   | ns    | N = prescale value<br>(1,4 or 16) |

| 53*              | TccR | CCP1 and CCP2 of           | output fall time                | PIC16 <b>C</b> 73/74  | _                     | 10   | 25  | ns    |                                   |

|                  |      |                            |                                 | PIC16 <b>LC</b> 73/74 | _                     | 25   | 45  | ns    |                                   |

| 54*              | TccF | CCP1 and CCP2 of           | and CCP2 output fall time PIC16 |                       | _                     | 10   | 25  | ns    |                                   |

|                  |      |                            |                                 | PIC16 <b>LC</b> 73/74 | _                     | 25   | 45  | ns    |                                   |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested. Applicable Devices 72 73 73A 74 74A 76 77

# TABLE 20-1:CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS<br/>AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)