Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | A/D 5x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c76-20i-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0 General Description                                              | 5   |

|----------------------------------------------------------------------|-----|

| 2.0 PIC16C7X Device Varieties                                        | 7   |

| 3.0 Architectural Overview                                           | 9   |

| 4.0 Memory Organization                                              | 19  |

| 5.0 I/O Ports                                                        | 43  |

| 6.0 Overview of Timer Modules                                        | 57  |

| 7.0 Timer0 Module                                                    | 59  |

| 8.0 Timer1 Module                                                    | 65  |

| 9.0 Timer2 Module                                                    | 69  |

| 10.0 Capture/Compare/PWM Module(s)                                   | 71  |

| 11.0 Synchronous Serial Port (SSP) Module                            | 77  |

| 12.0 Universal Synchronous Asynchronous Receiver Transmitter (USART) | 99  |

| 13.0 Analog-to-Digital Converter (A/D) Module                        | 117 |

| 14.0 Special Features of the CPU                                     | 129 |

| 15.0 Instruction Set Summary                                         | 147 |

| 16.0 Development Support                                             | 163 |

| 17.0 Electrical Characteristics for PIC16C72                         | 167 |

| 18.0 Electrical Characteristics for PIC16C73/74                      |     |

| 19.0 Electrical Characteristics for PIC16C73A/74A                    | 201 |

| 20.0 Electrical Characteristics for PIC16C76/77                      |     |

| 21.0 DC and AC Characteristics Graphs and Tables                     | 241 |

| 22.0 Packaging Information                                           | 251 |

| Appendix A:                                                          | 263 |

| Appendix B: Compatibility                                            | 263 |

| Appendix C: What's New                                               | 264 |

| Appendix D: What's Changed                                           | 264 |

| Appendix E: PIC16/17 Microcontrollers                                |     |

| Pin Compatibility                                                    | 271 |

| Index                                                                | 273 |

| List of Examples                                                     | 279 |

| List of Figures                                                      | 280 |

| List of Tables                                                       | 283 |

| Reader Response                                                      | 286 |

| PIC16C7X Product Identification System                               | 287 |

For register and module descriptions in this data sheet, device legends show which devices apply to those sections. As an example, the legend below would mean that the following section applies only to the PIC16C72, PIC16C73A and PIC16C74A devices.

Applicable Devices

72 73 73A 74 74A 76 77

# To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent an exceptional amount of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

NOTES:

FIGURE 4-4: PIC16C72 REGISTER FILE MAP

| File<br>Address   | 3                     |                     | File<br>Address |

|-------------------|-----------------------|---------------------|-----------------|

| 00h               | INDF <sup>(1)</sup>   | INDF <sup>(1)</sup> | 80h             |

| 01h               | TMR0                  | OPTION              | 81h             |

| 02h               | PCL                   | PCL                 | 82h             |

| 03h               | STATUS                | STATUS              | 83h             |

| 04h               | FSR                   | FSR                 | 84h             |

| 05h               | PORTA                 | TRISA               | 85h             |

| 06h               | PORTB                 | TRISB               | 86h             |

| 07h               | PORTC                 | TRISC               | 87h             |

| 08h               |                       |                     | 88h             |

| 09h               |                       |                     | 89h             |

| 0Ah               | PCLATH                | PCLATH              | - 8Ah           |

| 0Bh               | INTCON                | INTCON              | 8Bh             |

| 0Ch               | PIR1                  | PIE1                | 8Ch             |

| 0Dh               | 1 11 11               | 1121                | 8Dh             |

| 0Eh               | TMR1L                 | PCON                | 8Eh             |

| 0En               | TMR1H                 | 1 0014              | 8Fh             |

| 10h               | T1CON                 |                     | 90h             |

| 11h               | TMR2                  |                     | 91h             |

| 12h               | T2CON                 | PR2                 | 92h             |

| 1211<br>13h       | SSPBUF                |                     | 93h             |

| 13h<br>14h        |                       | SSPADD<br>SSPSTAT   | 9311<br>94h     |

| 140<br>15h        | SSPCON                | SSPSTAI             | 94n<br>95h      |

|                   | CCPR1L                |                     | _               |

| 16h               | CCPR1H                |                     | 96h             |

| 17h               | CCP1CON               |                     | 97h             |

| 18h               |                       |                     | 98h             |

| 19h               |                       |                     | 99h             |

| 1Ah               |                       |                     | 9Ah             |

| 1Bh               |                       |                     | 9Bh             |

| 1Ch               |                       |                     | 9Ch             |

| 1Dh               | 10050                 |                     | 9Dh             |

| 1Eh               | ADRES                 |                     | 9Eh             |

| 1Fh               | ADCON0                | ADCON1              | 9Fh             |

| 20h               | Canaral               | Conorol             | A0h             |

|                   | General<br>Purpose    | General<br>Purpose  |                 |

|                   | Register              | Register            | DEL             |

|                   |                       |                     | BFh             |

|                   |                       |                     | C0h             |

|                   |                       |                     |                 |

| ,                 |                       |                     |                 |

|                   |                       |                     |                 |

| 7Fh               | D- 1.0                | D 1.1               | ᆜ FFh           |

|                   | Bank 0                | Bank 1              |                 |

|                   |                       |                     |                 |

|                   | nimplemented data     | a memory location   | s, read as      |

| '0'.<br>Note 1: I | Not a physical regis  | ster                |                 |

| '**** '           | ioi a priyotoat regit | J.01.               |                 |

|                   |                       |                     |                 |

FIGURE 4-5: PIC16C73/73A/74/74A REGISTER FILE MAP

| REGISTER FILE WAP |                                      |                      |                  |  |  |  |  |  |

|-------------------|--------------------------------------|----------------------|------------------|--|--|--|--|--|

| File<br>Addres    | ss                                   |                      | File<br>Address  |  |  |  |  |  |

| 00h               | INDF <sup>(1)</sup>                  | INDF <sup>(1)</sup>  | 80h              |  |  |  |  |  |

| 01h               | TMR0                                 | OPTION               | 81h              |  |  |  |  |  |

| 02h               | PCL                                  | PCL                  | 82h              |  |  |  |  |  |

| 03h               | STATUS                               | STATUS               | 83h              |  |  |  |  |  |

| 04h               | FSR                                  | FSR                  | 84h              |  |  |  |  |  |

| 05h               | PORTA                                | TRISA                | 85h              |  |  |  |  |  |

| 06h               | PORTB                                | TRISB                | 86h              |  |  |  |  |  |

| 07h               | PORTC                                | TRISC                | 87h              |  |  |  |  |  |

| 08h               | PORTD <sup>(2)</sup>                 | TRISD <sup>(2)</sup> | -<br>88h         |  |  |  |  |  |

| 09h               | PORTE <sup>(2)</sup>                 | TRISE <sup>(2)</sup> | 89h              |  |  |  |  |  |

| 0Ah               | PCLATH                               | PCLATH               | -<br>8Ah         |  |  |  |  |  |

| 0Bh               | INTCON                               | INTCON               | -<br>8Bh         |  |  |  |  |  |

| 0Ch               | PIR1                                 | PIE1                 | 8Ch              |  |  |  |  |  |

| 0Dh               | PIR2                                 | PIE2                 | <sup>-</sup> 8Dh |  |  |  |  |  |

| 0Eh               | TMR1L                                | PCON                 | 8Eh              |  |  |  |  |  |

| 0Fh               | TMR1H                                |                      | 8Fh              |  |  |  |  |  |

| 10h               | T1CON                                |                      | 90h              |  |  |  |  |  |

| 11h               | TMR2                                 |                      | 91h              |  |  |  |  |  |

| 12h               | T2CON                                | PR2                  | 92h              |  |  |  |  |  |

| 13h               | SSPBUF                               | SSPADD               | 93h              |  |  |  |  |  |

| 14h               | SSPCON                               | SSPSTAT              | 94h              |  |  |  |  |  |

| 15h               | CCPR1L                               | 00.0                 | 95h              |  |  |  |  |  |

| 16h               | CCPR1H                               |                      | 96h              |  |  |  |  |  |

| 17h               | CCP1CON                              |                      | 97h              |  |  |  |  |  |

| 18h               | RCSTA                                | TXSTA                | 98h              |  |  |  |  |  |

| 19h               | TXREG                                | SPBRG                | 99h              |  |  |  |  |  |

| 1Ah               | RCREG                                | 0. 5.0               | 9Ah              |  |  |  |  |  |

| 17(i)<br>1Bh      | CCPR2L                               |                      | 9Bh              |  |  |  |  |  |

| 1Ch               | CCPR2H                               |                      | 9Ch              |  |  |  |  |  |

| 1Dh               | CCP2CON                              |                      | 9Dh              |  |  |  |  |  |

| 1Eh               | ADRES                                |                      | 9Eh              |  |  |  |  |  |

| 1Fh               | ADCON0                               | ADCON1               | 9Fh              |  |  |  |  |  |

| 20h               | 71000140                             | ABOON                | - A0h            |  |  |  |  |  |

| 2011              |                                      |                      | AUII             |  |  |  |  |  |

|                   |                                      |                      |                  |  |  |  |  |  |

|                   | General<br>Purpose                   | General<br>Purpose   |                  |  |  |  |  |  |

|                   | Register                             | Register             |                  |  |  |  |  |  |

|                   | -                                    |                      |                  |  |  |  |  |  |

|                   |                                      |                      |                  |  |  |  |  |  |

| 7Fh               |                                      |                      | FFh              |  |  |  |  |  |

| '                 | Bank 0                               | Bank 1               |                  |  |  |  |  |  |

|                   | Barin                                | Bank 1               |                  |  |  |  |  |  |

|                   | Unimplemented da                     | ta memory location   | ns, read as      |  |  |  |  |  |

|                   | )'.                                  |                      |                  |  |  |  |  |  |

| Note 1:           | Not a physical reg                   |                      | anla             |  |  |  |  |  |

| 2:                | These registers ar mented on the PIC |                      |                  |  |  |  |  |  |

|                   | ontog on the Fit                     |                      | . 40 0.          |  |  |  |  |  |

#### 4.3 PCL and PCLATH

Applicable Devices 72 73 73 A 74 74 A 76 77

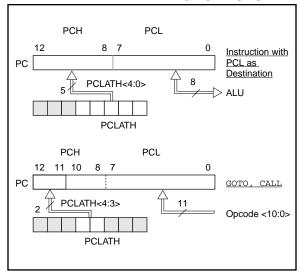

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any reset, the upper bits of the PC will be cleared. Figure 4-17 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 4-17: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note "Implementing a Table Read" (AN556).

#### 4.3.2 STACK

The PIC16CXX family has an 8 level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- **Note 1:** There are no status bits to indicate stack overflow or stack underflow conditions.

- Note 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address.

#### 4.4 Program Memory Paging

Applicable Devices 72 73 73 A 74 74 A 76 77

PIC16C7X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<4:3> bits are not required for the return instructions (which POPs the address from the stack).

Note: PIC16C7X devices with 4K or less of program memory ignore paging bit PCLATH<4>. The use of PCLATH<4> as a general purpose read/write bit is not recommended since this may affect upward compatibility with future products.

TABLE 5-1: PORTA FUNCTIONS

| Name         | Bit# | Buffer | Function                                                                       |

|--------------|------|--------|--------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF                                           |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0                                |

|              |      |        | Output is open drain type                                                      |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input |

Legend: TTL = TTL input, ST = Schmitt Trigger input

### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5                         | Bit 4 | Bit 3 | Bit 2   | Bit 1   | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|--------|-------|-------|-------------------------------|-------|-------|---------|---------|-------|--------------------------|---------------------------|

| 05h     | PORTA  | _     | _     | RA5                           | RA4   | RA3   | RA2     | RA1     | RA0   | 0x 0000                  | 0u 0000                   |

| 85h     | TRISA  | _     | _     | PORTA Data Direction Register |       |       | 11 1111 | 11 1111 |       |                          |                           |

| 9Fh     | ADCON1 | _     | _     | _                             | _     | _     | PCFG2   | PCFG1   | PCFG0 | 000                      | 000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

#### 5.2 PORTB and TRISB Registers

**Applicable Devices** 72 | 73 | 73 | 74 | 74 | 76 | 77

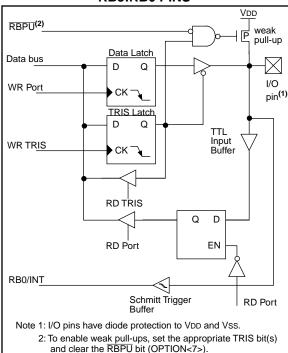

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a bit in the TRISB register puts the corresponding output driver in a hi-impedance input mode. Clearing a bit in the TRISB register puts the contents of the output latch on the selected pin(s).

#### **EXAMPLE 5-2: INITIALIZING PORTB**

```

BCF

STATUS, RPO

CLRF

; Initialize PORTB by

PORTR

; clearing output

; data latches

BSF

STATUS, RPO ; Select Bank 1

M.TVOM

OxCF

; Value used to

; initialize data

; direction

MOVWF

; Set RB<3:0> as inputs

TRISB

; RB<5:4> as outputs

; RB<7:6> as inputs

```

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

FIGURE 5-3: BLOCK DIAGRAM OF RB3:RB0 PINS

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition, and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a keypad and make it possible for wake-up on key-depression. Refer to the Embedded Control Handbook, "Implementing Wake-Up on Key Stroke" (AN552).

Note: For the PIC16C73/74, if a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then interrupt flag bit RBIF may not get set.

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

Note: To avoid an unintended device RESET, the following instruction sequence (shown in Example 7-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

#### **EXAMPLE 7-1: CHANGING PRESCALER (TIMER0→WDT)**

Lines 2 and 3 do NOT have to be included if the final desired prescale value is other than 1:1. If 1:1 is final desired value, then a temporary prescale value is set in lines 2 and 3 and the final prescale value will be set in lines 10 and 11.

```

STATUS, RPO

1) BSF

2) MOVLW b'xx0x0xxx'

;Select clock source and prescale value of

3) MOVWF OPTION_REG

;other than 1:1

BCF

STATUS, RPO

;Bank 0

5) CLRF

TMR0

;Clear TMR0 and prescaler

6)

BSF

STATUS, RP1

;Bank 1

MOVLW b'xxxx1xxx'

;Select WDT, do not change prescale value

7)

MOVWF OPTION_REG

8)

9)

CLRWDT

;Clears WDT and prescaler

10) MOVLW b'xxxx1xxx'

;Select new prescale value and WDT

11) MOVWF OPTION_REG

12) BCF

STATUS, RPO

;Bank 0

```

To change prescaler from the WDT to the Timer0 module use the sequence shown in Example 7-2.

### **EXAMPLE 7-2: CHANGING PRESCALER (WDT→TIMER0)**

```

CLRWDT ;Clear WDT and prescaler

BSF STATUS, RP0 ;Bank 1

MOVLW b'xxxx0xxx' ;Select TMR0, new prescale value and

MOVWF OPTION_REG ;clock source

BCF STATUS, RP0 ;Bank 0

```

#### TABLE 7-1: REGISTERS ASSOCIATED WITH TIMERO

| Address               | Name   | Bit 7  | Bit 6       | Bit 5    | Bit 4        | Bit 3     | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------------------|--------|--------|-------------|----------|--------------|-----------|-------|-------|-------|--------------------------|---------------------------|

| 01h,101h              | TMR0   | Timer0 | module's re | egister  |              |           |       |       |       | xxxx xxxx                | uuuu uuuu                 |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE    | PEIE        | TOIE     | INTE         | RBIE      | T0IF  | INTF  | RBIF  | 0000 000x                | 0000 000u                 |

| 81h,181h              | OPTION | RBPU   | INTEDG      | T0CS     | T0SE         | PSA       | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                 |

| 85h                   | TRISA  | _      | _           | PORTA Da | ta Direction | on Regist | ər    | •     |       | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

**TABLE 10-5**: **REGISTERS ASSOCIATED WITH PWM AND TIMER2**

| Address               | Name    | Bit 7                  | Bit 6          | Bit 5               | Bit 4               | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>PO<br>BO | R,   |      | e on<br>ther<br>ets |

|-----------------------|---------|------------------------|----------------|---------------------|---------------------|---------|--------|---------|---------|-------------------|------|------|---------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                    | PEIE           | TOIE                | INTE                | RBIE    | TOIF   | INTF    | RBIF    | 0000              | 000x | 0000 | 000u                |

| 0Ch                   | PIR1    | PSPIF <sup>(1,2)</sup> | ADIF           | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000              | 0000 | 0000 | 0000                |

| 0Dh <sup>(2)</sup>    | PIR2    | _                      | _              | _                   | _                   | _       | _      | _       | CCP2IF  |                   | 0    |      | 0                   |

| 8Ch                   | PIE1    | PSPIE <sup>(1,2)</sup> | ADIE           | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup> | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000              | 0000 | 0000 | 0000                |

| 8Dh <sup>(2)</sup>    | PIE2    | _                      | _              | _                   | _                   | _       | _      | _       | CCP2IE  |                   | 0    |      | 0                   |

| 87h                   | TRISC   | PORTC D                | ata Directio   | n Register          |                     |         |        |         |         | 1111              | 1111 | 1111 | 1111                |

| 11h                   | TMR2    | Timer2 mod             | dule's registe | er                  |                     |         |        |         |         | 0000              | 0000 | 0000 | 0000                |

| 92h                   | PR2     | Timer2 mod             | dule's period  | l register          |                     |         |        |         |         | 1111              | 1111 | 1111 | 1111                |

| 12h                   | T2CON   | _                      | TOUTPS3        | TOUTPS2             | TOUTPS1             | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000              | 0000 | -000 | 0000                |

| 15h                   | CCPR1L  | Capture/Co             | mpare/PWN      | Л register1 (       | LSB)                |         |        |         |         | xxxx              | xxxx | uuuu | uuuu                |

| 16h                   | CCPR1H  | Capture/Co             | mpare/PWN      | // register1 (      | (MSB)               |         |        |         |         | xxxx              | xxxx | uuuu | uuuu                |

| 17h                   | CCP1CON | _                      | _              | CCP1X               | CCP1Y               | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00                | 0000 | 00   | 0000                |

| 1Bh <sup>(2)</sup>    | CCPR2L  | Capture/Co             | mpare/PWN      | Л register2 (       | LSB)                |         |        |         |         | xxxx              | xxxx | uuuu | uuuu                |

| 1Ch <sup>(2)</sup>    | CCPR2H  | Capture/Co             | mpare/PWN      | // register2 (      | (MSB)               |         |        |         |         | xxxx              | xxxx | uuuu | uuuu                |

| 1Dh <sup>(2)</sup>    | CCP2CON | _                      | _              | CCP2X               | CCP2Y               | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00                | 0000 | 00   | 0000                |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PWM and Timer2. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

<sup>2:</sup> The PIC16C72 does not have a Parallel Slave Port, USART or CCP2 module, these bits are unimplemented, read as '0'.

#### 12.3 <u>USART Synchronous Master Mode</u>

**Applicable Devices** 72 73 73 A 74 74 A 76 77

In Synchronous Master mode, the data is transmitted in a half-duplex manner i.e. transmission and reception do not occur at the same time. When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition enable bit SPEN (RCSTA<7>) is set in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

# 12.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 12-7. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer register TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one Tcycle), the TXREG is empty and interrupt bit, TXIF (PIR1<4>) is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

Transmission is enabled by setting enable bit TXEN (TXSTA<5>). The actual transmission will not occur until the TXREG register has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the CK line. Data out is stable around the falling edge of the synchronous clock (Figure 12-12). The transmission can also be started by first loading the TXREG register and then setting bit TXEN (Figure 12-13). This is advantageous when slow baud rates are selected, since the BRG is kept in reset when bits TXEN, CREN, and SREN are clear. Setting enable bit TXEN will start the BRG, creating a shift clock immediately. Normally when transmission is first started, the TSR register is empty, so a transfer to the TXREG register will result in an immediate transfer to TSR resulting in an empty TXREG. Back-to-back transfers are possible.

Clearing enable bit TXEN, during a transmission, will cause the transmission to be aborted and will reset the transmitter. The DT and CK pins will revert to hi-impedance. If either bit CREN or bit SREN is set, during a transmission, the transmission is aborted and the DT pin reverts to a hi-impedance state (for a reception). The CK pin will remain an output if bit CSRC is set (internal clock). The transmitter logic however is not reset although it is disconnected from the pins. In order to reset the transmitter, the user has to clear bit TXEN. If bit SREN is set (to interrupt an on-going transmission and receive a single word), then after the single word is received, bit SREN will be cleared and the serial port will revert back to transmitting since bit TXEN is still set. The DT line will immediately switch from hi-impedance receive mode to transmit and start driving. To avoid this, bit TXEN should be cleared.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to bit TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG register. This is because a data write to the TXREG can result in an immediate transfer of the data to the TSR register (if the TSR is empty). If the TSR was empty and the TXREG was written before writing the "new" TX9D, the "present" value of bit TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 12.1).

- Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- Enable the transmission by setting bit TXEN.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- Start transmission by loading data to the TXREG register.

#### 13.5 A/D Operation During Sleep

**Applicable Devices** 72 | 73 | 73 | 74 | 74 | 76 | 77 |

The A/D module can operate during SLEEP mode. This requires that the A/D clock source be set to RC (ADCS1:ADCS0 = 11). When the RC clock source is selected, the A/D module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is completed the  $GO/\overline{DONE}$  bit will be cleared, and the result loaded into the ADRES register. If the A/D interrupt is enabled, the device will wake-up from SLEEP. If the A/D interrupt is not enabled, the A/D module will then be turned off, although the ADON bit will remain set.

When the A/D clock source is another clock option (not RC), a SLEEP instruction will cause the present conversion to be aborted and the A/D module to be turned off, though the ADON bit will remain set.

Turning off the A/D places the A/D module in its lowest current consumption state.

#### Note:

For the A/D module to operate in SLEEP, the A/D clock source must be set to RC (ADCS1:ADCS0 = 11). To perform an A/D conversion in SLEEP, ensure the SLEEP instruction immediately follows the instruction that sets the  $GO/\overline{DONE}$  bit.

#### 13.6 A/D Accuracy/Error

**Applicable Devices** 72 73 73 A 74 74 A 76 77

The absolute accuracy specified for the A/D converter includes the sum of all contributions for quantization error, integral error, differential error, full scale error, offset error, and monotonicity. It is defined as the maximum deviation from an actual transition versus an ideal transition for any code. The absolute error of the A/D converter is specified at  $<\pm 1$  LSb for VDD = VREF (over the device's specified operating range). However, the accuracy of the A/D converter will degrade as VDD diverges from VREF.

For a given range of analog inputs, the output digital code will be the same. This is due to the quantization of the analog input to a digital code. Quantization error is typically  $\pm$  1/2 LSb and is inherent in the analog to digital conversion process. The only way to reduce quantization error is to increase the resolution of the A/D converter.

Offset error measures the first actual transition of a code versus the first ideal transition of a code. Offset error shifts the entire transfer function. Offset error can be calibrated out of a system or introduced into a system through the interaction of the total leakage current and source impedance at the analog input.

Gain error measures the maximum deviation of the last actual transition and the last ideal transition adjusted for offset error. This error appears as a change in slope of the transfer function. The difference in gain error to full scale error is that full scale does not take offset error into account. Gain error can be calibrated out in software.

Linearity error refers to the uniformity of the code changes. Linearity errors cannot be calibrated out of the system. Integral non-linearity error measures the actual code transition versus the ideal code transition adjusted by the gain error for each code.

Differential non-linearity measures the maximum actual code width versus the ideal code width. This measure is unadjusted.

The maximum pin leakage current is  $\pm$  1  $\mu$ A.

In systems where the device frequency is low, use of the A/D RC clock is preferred. At moderate to high frequencies, TAD should be derived from the device oscillator. TAD must not violate the minimum and should be  $\leq 8~\mu s$  for preferred operation. This is because TAD, when derived from Tosc, is kept away from on-chip phase clock transitions. This reduces, to a large extent, the effects of digital switching noise. This is not possible with the RC derived clock. The loss of accuracy due to digital switching noise can be significant if many I/O pins are active.

In systems where the device will enter SLEEP mode after the start of the A/D conversion, the RC clock source selection is required. In this mode, the digital noise from the modules in SLEEP are stopped. This method gives high accuracy.

#### 13.7 Effects of a RESET

Applicable Devices 72|73|73A|74|74A|76|77

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted.

The value that is in the ADRES register is not modified for a Power-on Reset. The ADRES register will contain unknown data after a Power-on Reset.

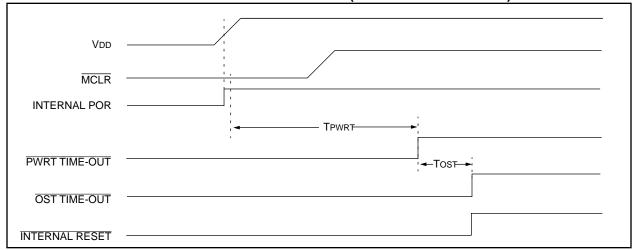

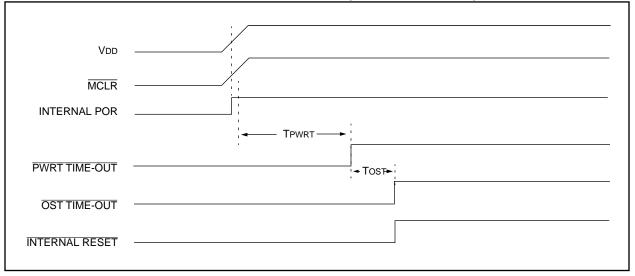

FIGURE 14-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

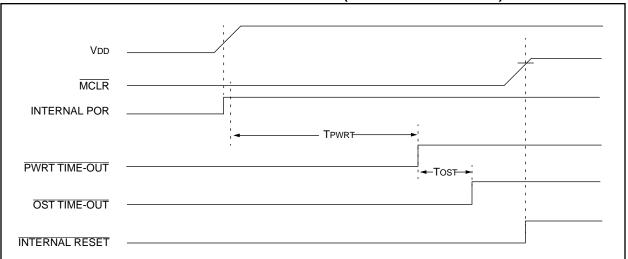

FIGURE 14-11: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

FIGURE 14-12: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

NOP No Operation Syntax: [label] NOP Operands: None Operation: No operation Status Affected: None Encoding: 0000 00 0xx00000 Description: No operation. Words: 1 1 Cycles: Q Cycle Activity: Q3 Q1 Q2 Q4 Decode No-No-No-Operation Operation Operation Example NOP

| OPTION           | Load Op                                                                                                                                                                                      | Load Option Register |  |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|--|--|--|

| Syntax:          | [ label ] OPTION                                                                                                                                                                             |                      |  |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                         |                      |  |  |  |  |  |  |  |

| Operation:       | $(W) \rightarrow OPTION$                                                                                                                                                                     |                      |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                         |                      |  |  |  |  |  |  |  |

| Encoding:        | 00 0000 0110 0010                                                                                                                                                                            |                      |  |  |  |  |  |  |  |

|                  | loaded in the OPTION register. This instruction is supported for code compatibility with PIC16C5X products.  Since OPTION is a readable/writable register, the user can directly address it. |                      |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                            |                      |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                            |                      |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                              |                      |  |  |  |  |  |  |  |

| Example          | To maintain upward compatibility with future PIC16CXX products, do not use this instruction.                                                                                                 |                      |  |  |  |  |  |  |  |

| RETFIE            | Return from Interrupt                                                                                                                                                                              |                  |                    |                    |  |  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|--------------------|--|--|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                          | RETFIE           |                    |                    |  |  |  |  |  |

| Operands:         | None                                                                                                                                                                                               |                  |                    |                    |  |  |  |  |  |

| Operation:        | $\begin{aligned} & TOS \to PC, \\ & 1 \to GIE \end{aligned}$                                                                                                                                       |                  |                    |                    |  |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                                               |                  |                    |                    |  |  |  |  |  |

| Encoding:         | 00                                                                                                                                                                                                 | 0000             | 0000               | 1001               |  |  |  |  |  |

| Description:      | Return from Interrupt. Stack is POPed and Top of Stack (TOS) is loaded in the PC. Interrupts are enabled by setting Global Interrupt Enable bit, GIE (INTCON<7>). This is a two cycle instruction. |                  |                    |                    |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                  |                  |                    |                    |  |  |  |  |  |

| Cycles:           | 2                                                                                                                                                                                                  |                  |                    |                    |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                 | Q2               | Q3                 | Q4                 |  |  |  |  |  |

| 1st Cycle         | Decode                                                                                                                                                                                             | No-<br>Operation | Set the<br>GIE bit | Pop from the Stack |  |  |  |  |  |

| 2nd Cycle         | No-<br>Operation                                                                                                                                                                                   | No-<br>Operation | No-<br>Operation   | No-<br>Operation   |  |  |  |  |  |

Example RETFIE

After Interrupt PC =

PC = TOS GIE = 1

| XORLW                                 | Exclusive OR Literal with W                                                                                       | XORWF                          | Exclusive OR W with f                                                                                                        |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                               | [label] XORLW k                                                                                                   | Syntax:                        | [label] XORWF f,d                                                                                                            |

| Operands:                             | 0 ≤ k ≤ 255                                                                                                       | Operands:                      | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                           |

| Operation: Status Affected: Encoding: | (W) .XOR. $k \rightarrow (W)$ Z  11   1010   kkkk   kkkk                                                          | Operation:<br>Status Affected: | (W) .XOR. (f) $\rightarrow$ (destination) Z                                                                                  |

| Description:                          | The contents of the W register are XOR'ed with the eight bit literal 'k'. The result is placed in the W register. | Encoding:<br>Description:      | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is |

| Words:                                | 1                                                                                                                 | Words:                         | 1 the result is stored back in register 'f'. 1                                                                               |

| Cycles:<br>Q Cycle Activity:          | Q1 Q2 Q3 Q4  Decode Read Process Write to data W                                                                  | Cycles:<br>Q Cycle Activity:   | 1     Q1    Q2    Q3    Q4     Decode    Read    Process    Write to                                                         |

| Example:                              | XORLW 0xAF  Before Instruction                                                                                    | Evampla                        | register data destination  XORWF REG 1                                                                                       |

|                                       | W = 0xB5                                                                                                          | Example                        | Before Instruction                                                                                                           |

|                                       | After Instruction $W = 0x1A$                                                                                      |                                | $ \begin{array}{rcl} REG & = & 0xAF \\ W & = & 0xB5 \end{array} $                                                            |

|                                       |                                                                                                                   |                                | After Instruction                                                                                                            |

|                                       |                                                                                                                   |                                | $ REG = 0x1A \\ W = 0xB5 $                                                                                                   |

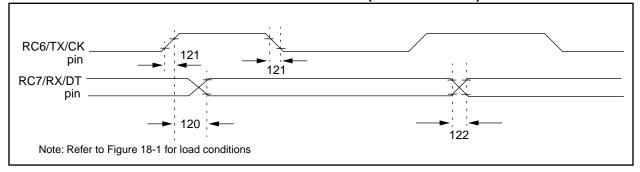

## FIGURE 18-11: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 18-11: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                    |                       | Min | Тур† | Max | Units | Conditions |

|------------------|----------|-----------------------------------|-----------------------|-----|------|-----|-------|------------|

| 120              | TckH2dtV | SYNC XMIT (MASTER & SLAVE)        | PIC16 <b>C</b> 73/74  | _   |      | 80  | ns    |            |

|                  |          | Clock high to data out valid      | PIC16 <b>LC</b> 73/74 | _   | -    | 100 | ns    |            |

| 121              | Tckrf    | Clock out rise time and fall time | PIC16 <b>C</b> 73/74  | _   | _    | 45  | ns    |            |

|                  |          | (Master Mode)                     | PIC16 <b>LC</b> 73/74 | _   | _    | 50  | ns    |            |

| 122              | Tdtrf    | Data out rise time and fall time  | PIC16 <b>C</b> 73/74  | _   | _    | 45  | ns    |            |

|                  |          |                                   | PIC16 <b>LC</b> 73/74 | _   | _    | 50  | ns    |            |

<sup>†:</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

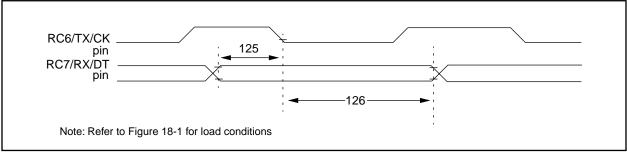

## FIGURE 18-12: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 18-12: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                   | Min | Тур† | Max | Units | Conditions |

|------------------|----------|------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE) Data setup before CK ↓ (DT setup time) | 15  |      |     | ns    |            |

| 126              | TckL2dtl | Data hold after CK ↓ (DT hold time)                              | 15  | _    | _   | ns    |            |

<sup>†:</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

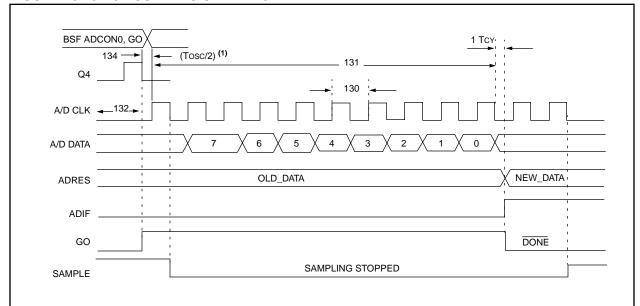

### FIGURE 18-13: A/D CONVERSION TIMING

Note 1: If the A/D clock source is selected as RC, a time of Tcy is added before the A/D clock starts. This allows the SLEEP instruction to be executed.

#### **TABLE 18-14: A/D CONVERSION REQUIREMENTS**

| Param<br>No. | Sym  | Characteristic                |                       | Min    | Тур†     | Max | Units | Conditions                                                                                                                                                                                                |

|--------------|------|-------------------------------|-----------------------|--------|----------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D clock period              | PIC16 <b>C</b> 73/74  | 1.6    | _        | _   | μs    | Tosc based, VREF ≥ 3.0V                                                                                                                                                                                   |

|              |      |                               | PIC16 <b>LC</b> 73/74 | 2.0    | _        | _   | μs    | Tosc based, VREF full range                                                                                                                                                                               |

|              |      |                               | PIC16 <b>C</b> 73/74  | 2.0    | 4.0      | 6.0 | μs    | A/D RC Mode                                                                                                                                                                                               |

|              |      |                               | PIC16 <b>LC</b> 73/74 | 3.0    | 6.0      | 9.0 | μs    | A/D RC Mode                                                                                                                                                                                               |

| 131          | TCNV | Conversion time (not (Note 1) | including S/H time)   | _      | 9.5      | _   | TAD   |                                                                                                                                                                                                           |

| 132          | TACQ | Acquisition time              |                       | Note 2 | 20       | _   | μs    |                                                                                                                                                                                                           |

|              |      |                               |                       | 5*     | _        | _   | μs    | The minimum time is the amplifier settling time. This may be used if the "new" input voltage has not changed by more than 1 LSb (i.e., 20 mV @ 5.12V) from the last sampled voltage (as stated on CHOLD). |

| 134          | Tgo  | Q4 to A/D clock start         |                       | _      | Tosc/2 § | _   | _     | If the A/D clock source is selected as RC, a time of Tcy is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                          |

| 135          | Tswc | Switching from conve          | rt → sample time      | 1.5 §  | _        | _   | TAD   |                                                                                                                                                                                                           |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>§</sup> This specification ensured by design.

Note 1: ADRES register may be read on the following TcY cycle.

<sup>2:</sup> See Section 13.1 for min conditions.

#### **TABLE 19-13: A/D CONVERTER CHARACTERISTICS:**

PIC16C73A/74A-04 (Commercial, Industrial, Extended) PIC16C73A/74A-10 (Commercial, Industrial, Extended) PIC16C73A/74A-20 (Commercial, Industrial, Extended) PIC16LC73A/74A-04 (Commercial, Industrial)

| Param<br>No. | Sym   | Characteristic                            |                         | Min       | Тур†       | Max        | Units                                    | Conditions                                                                                         |

|--------------|-------|-------------------------------------------|-------------------------|-----------|------------|------------|------------------------------------------|----------------------------------------------------------------------------------------------------|

| A01          | NR    | Resolution                                | _                       | _         | 8-bits     | bit        | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF |                                                                                                    |

| A02          | EABS  | Total Absolute error                      | _                       | _         | < ± 1      | LSb        | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF |                                                                                                    |

| A03          | EIL   | Integral linearity error                  |                         | _         | _          | < ± 1      | LSb                                      | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF                                                           |

| A04          | EDL   | Differential linearity error              | _                       | _         | < ± 1      | LSb        | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF |                                                                                                    |

| A05          | EFS   | Full scale error                          |                         | _         | _          | < ± 1      | LSb                                      | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF                                                           |

| A06          | Eoff  | Offset error                              |                         | _         | _          | < ± 1      | LSb                                      | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF                                                           |

| A10          | _     | Monotonicity                              |                         | _         | guaranteed | _          | _                                        | VSS ≤ VAIN ≤ VREF                                                                                  |

| A20          | VREF  | Reference voltage                         |                         | 3.0V      | _          | VDD + 0.3  | V                                        |                                                                                                    |

| A25          | VAIN  | Analog input voltage                      |                         | Vss - 0.3 | _          | VREF + 0.3 | V                                        |                                                                                                    |

| A30          | ZAIN  | Recommended impedar analog voltage source | ice of                  | _         | _          | 10.0       | kΩ                                       |                                                                                                    |

| A40          | IAD   | A/D conversion current                    | PIC16 <b>C</b> 73A/74A  | _         | 180        | _          | μΑ                                       | Average current consump-                                                                           |

|              | (VDD) |                                           | PIC16 <b>LC</b> 73A/74A | _         | 90         | _          | μΑ                                       | tion when A/D is on.<br>(Note 1)                                                                   |

| A50          | IREF  | F VREF input current (Note 2)             |                         | 10        | _          | 1000       | μА                                       | During VAIN acquisition. Based on differential of VHOLD to VAIN to charge CHOLD, see Section 13.1. |

|              |       |                                           |                         | _         | _          | 10         | μА                                       | During A/D Conversion cycle                                                                        |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current.

The power-down current spec includes any such leakage from the A/D module.

<sup>2:</sup> VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

DC CHARACTERISTICS

# **Applicable Devices** 72 73 73A 74 74A 76 77

#### Standard Operating Conditions (unless otherwise stated)

Operating temperature  $-40^{\circ}\text{C} \leq \text{TA} \leq +125^{\circ}\text{C}$  for extended,

-40°C ≤ TA ≤ +85°C for industrial and

$0^{\circ}$ C  $\leq TA \leq +70^{\circ}$ C for commercial

Operating voltage VDD range as described in DC spec Section 20.1 and

Section 20.2.

| Param | Characteristic                             | Sym               | Min       | Тур | Max | Units | Conditions                                                        |

|-------|--------------------------------------------|-------------------|-----------|-----|-----|-------|-------------------------------------------------------------------|

| No.   |                                            |                   |           | †   |     |       |                                                                   |

|       | Output High Voltage                        |                   |           |     |     |       |                                                                   |

| D090  | I/O ports (Note 3)                         | Voн               | VDD - 0.7 | -   | -   | V     | IOH = $-3.0$ mA, VDD = $4.5$ V, $-40$ °C to $+85$ °C              |

| D090A |                                            |                   | VDD - 0.7 | -   | -   | V     | IOH = $-2.5$ mA, VDD = $4.5$ V,<br>-40°C to $+125$ °C             |

| D092  | OSC2/CLKOUT (RC osc config)                |                   | VDD - 0.7 | -   | -   | V     | IOH = $-1.3$ mA, VDD = $4.5$ V, $-40$ °C to $+85$ °C              |

| D092A |                                            |                   | VDD - 0.7 | -   | -   | V     | IOH = -1.0 mA, VDD = $4.5V$ ,<br>-40°C to +125°C                  |

| D150* | Open-Drain High Voltage                    | Vod               | -         | -   | 14  | V     | RA4 pin                                                           |

|       | Capacitive Loading Specs on<br>Output Pins |                   |           |     |     |       |                                                                   |

| D100  | OSC2 pin                                   | Cosc <sub>2</sub> | -         | -   | 15  | pF    | In XT, HS and LP modes when external clock is used to drive OSC1. |

| D101  | All I/O pins and OSC2 (in RC               | Cio               | -         | -   | 50  | pF    |                                                                   |

| D102  | mode) SCL, SDA in I <sup>2</sup> C mode    | Св                | -         | -   | 400 | pF    |                                                                   |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C7X be driven with external clock in RC mode.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

## 20.5 <u>Timing Diagrams and Specifications</u>

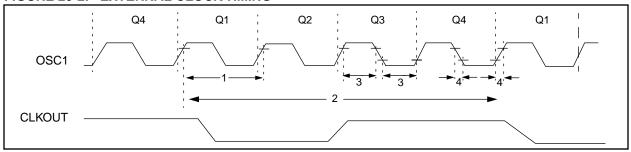

#### FIGURE 20-2: EXTERNAL CLOCK TIMING

#### TABLE 20-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter No. | Sym   | Characteristic                       | Min | Тур† | Max    | Units | Conditions         |

|---------------|-------|--------------------------------------|-----|------|--------|-------|--------------------|

|               | Fosc  | External CLKIN Frequency             | DC  |      | 4      | MHz   | XT and RC osc mode |

|               |       | (Note 1)                             | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|               |       |                                      | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|               |       |                                      | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|               |       |                                      | DC  | _    | 200    | kHz   | LP osc mode        |

|               |       | Oscillator Frequency                 | DC  | _    | 4      | MHz   | RC osc mode        |

|               |       | (Note 1)                             | 0.1 | _    | 4      | MHz   | XT osc mode        |

|               |       |                                      | 4   | _    | 20     | MHz   | HS osc mode        |

|               |       |                                      | 5   | 1    | 200    | kHz   | LP osc mode        |

| 1             | Tosc  | External CLKIN Period                | 250 | _    | _      | ns    | XT and RC osc mode |

|               |       | (Note 1)                             | 250 | _    | _      | ns    | HS osc mode (-04)  |

|               |       |                                      | 100 | _    | _      | ns    | HS osc mode (-10)  |

|               |       |                                      | 50  | _    | _      | ns    | HS osc mode (-20)  |

|               |       |                                      | 5   | _    | _      | μs    | LP osc mode        |

|               |       | Oscillator Period                    | 250 |      | _      | ns    | RC osc mode        |

|               |       | (Note 1)                             | 250 | _    | 10,000 | ns    | XT osc mode        |

|               |       |                                      | 250 | _    | 250    | ns    | HS osc mode (-04)  |

|               |       |                                      | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|               |       |                                      |     |      |        |       | HS osc mode (-20)  |

|               |       |                                      | 50  | _    | 250    | ns    |                    |

|               |       |                                      | 5   |      | _      | μs    | LP osc mode        |

| 2             | TCY   | Instruction Cycle Time (Note 1)      | 200 | Tcy  | DC     | ns    | Tcy = 4/Fosc       |

| 3             | TosL, | External Clock in (OSC1) High or     | 100 | _    | -      | ns    | XT oscillator      |

|               | TosH  | Low Time                             | 2.5 | _    | _      | μs    | LP oscillator      |

|               |       |                                      | 15  |      | _      | ns    | HS oscillator      |

| 4             | TosR, | External Clock in (OSC1) Rise or     | _   | _    | 25     | ns    | XT oscillator      |

|               | TosF  | Fall Time                            | _   | _    | 50     | ns    | LP oscillator      |

| + Dots        |       | column is at EV 25°C unless athemais |     |      | 15     | ns    | HS oscillator      |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

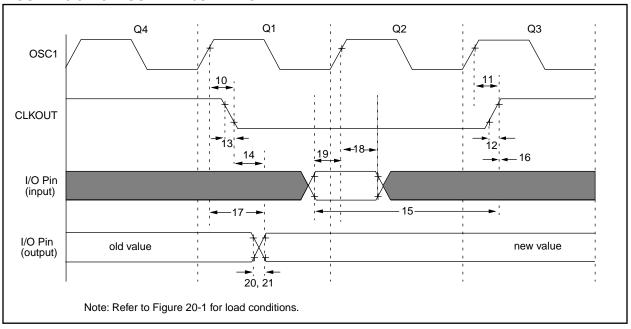

FIGURE 20-3: CLKOUT AND I/O TIMING

TABLE 20-3: CLKOUT AND I/O TIMING REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                             | Min                   | Тур† | Max         | Units | Conditions |        |

|--------------|----------|--------------------------------------------|-----------------------|------|-------------|-------|------------|--------|

| 10*          | TosH2ckL | OSC1↑ to CLKOUT↓                           | _                     | 75   | 200         | ns    | Note 1     |        |

| 11*          | TosH2ckH | OSC1↑ to CLKOUT↑                           |                       | _    | 75          | 200   | ns         | Note 1 |

| 12*          | TckR     | CLKOUT rise time                           |                       | _    | 35          | 100   | ns         | Note 1 |

| 13*          | TckF     | CLKOUT fall time                           |                       | _    | 35          | 100   | ns         | Note 1 |

| 14*          | TckL2ioV | CLKOUT ↓ to Port out valid                 | _                     | _    | 0.5Tcy + 20 | ns    | Note 1     |        |

| 15*          | TioV2ckH | Port in valid before CLKOL                 | Tosc + 200            | _    | _           | ns    | Note 1     |        |

| 16*          | TckH2iol | Port in hold after CLKOUT                  | 0                     | _    | _           | ns    | Note 1     |        |

| 17*          | TosH2ioV | OSC1↑ (Q1 cycle) to<br>Port out valid      |                       | _    | 50          | 150   | ns         |        |

| 18*          | TosH2ioI | OSC1↑ (Q2 cycle) to PIC16 <b>C</b> 76/77   |                       | 100  | _           | _     | ns         |        |

|              |          | Port input invalid (I/O in hold time)      | PIC16 <b>LC</b> 76/77 | 200  | _           | _     | ns         |        |

| 19*          | TioV2osH | Port input valid to OSC1                   | (I/O in setup time)   | 0    | _           | _     | ns         |        |

| 20*          | TioR     | Port output rise time                      | PIC16 <b>C</b> 76/77  | _    | 10          | 40    | ns         |        |

|              |          |                                            | PIC16 <b>LC</b> 76/77 | _    | _           | 80    | ns         |        |

| 21*          | TioF     | Port output fall time PIC16 <b>C</b> 76/77 |                       | _    | 10          | 40    | ns         |        |

|              |          |                                            | PIC16 <b>LC</b> 76/77 |      |             | 80    | ns         |        |

| 22††*        | Tinp     | INT pin high or low time                   |                       | Tcy  | _           | _     | ns         |        |

| 23††*        | Trbp     | RB7:RB4 change INT high                    | or low time           | Tcy  | _           | _     | ns         |        |

These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>††</sup> These parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

| CCP2IF bit38                                 | F                                         |           |

|----------------------------------------------|-------------------------------------------|-----------|

| CCPR1H Register25, 27, 29, 71                | Family of Devices                         |           |

| CCPR1L Register29, 71                        | PIC12CXXX                                 | 265       |

| CCPR2H Register25, 27, 29, 71                | PIC14C000                                 |           |

| CCPR2L Register25, 27, 29, 71                | PIC16C15X                                 |           |

| CCPxM0 bit                                   | PIC16C55X                                 |           |

| CCPxM1 bit72                                 | PIC16C5X                                  | 266       |

| CCPxM2 bit72                                 | PIC16C62X and PIC16C64X                   |           |

| CCPxM3 bit72                                 | PIC16C6X                                  |           |

| CCPxX bit72                                  | PIC16C7XX                                 | 6         |

| CCPxY bit72                                  | PIC16C8X                                  | 269       |

| CKE83                                        | PIC16C9XX                                 | 269       |

| CKP                                          | PIC17CXX                                  | 270       |

| Clock Polarity Select bit, CKP79, 84         | FERR bit                                  | 100       |

| Clock Polarity, SPI Mode81                   | FSR Register 23, 24, 25, 26, 27, 2        | 8, 29, 41 |

| Clocking Scheme17                            | Fuzzy Logic Dev. System (fuzzyTECH®-MP)   | 163, 165  |

| Code Examples                                |                                           |           |

| Call of a Subroutine in Page 1 from Page 041 | G                                         |           |

| Changing Between Capture Prescalers          | General Description                       | 5         |