## E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 014110                   |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | A/D 8x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-QFP                                                                   |

| Supplier Device Package    | 44-MQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c77-04-pq |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

### TABLE 3-3: PIC16C74/74A/77 PINOUT DESCRIPTION (Cont.'d)

| Pin Name          | DIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                            |

|-------------------|-------------|--------------|-------------|---------------|-----------------------|--------------------------------------------------------------------------------------------------------|

|                   |             |              |             |               |                       | PORTC is a bi-directional I/O port.                                                                    |

| RC0/T1OSO/T1CKI   | 15          | 16           | 32          | I/O           | ST                    | RC0 can also be the Timer1 oscillator output or a<br>Timer1 clock input.                               |

| RC1/T1OSI/CCP2    | 16          | 18           | 35          | I/O           | ST                    | RC1 can also be the Timer1 oscillator input or<br>Capture2 input/Compare2 output/PWM2 output.          |

| RC2/CCP1          | 17          | 19           | 36          | I/O           | ST                    | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                    |

| RC3/SCK/SCL       | 18          | 20           | 37          | I/O           | ST                    | RC3 can also be the synchronous serial clock input/<br>output for both SPI and I <sup>2</sup> C modes. |

| RC4/SDI/SDA       | 23          | 25           | 42          | I/O           | ST                    | RC4 can also be the SPI Data In (SPI mode) or data I/O ( $I^2$ C mode).                                |

| RC5/SDO           | 24          | 26           | 43          | I/O           | ST                    | RC5 can also be the SPI Data Out (SPI mode).                                                           |

| RC6/TX/CK         | 25          | 27           | 44          | I/O           | ST                    | RC6 can also be the USART Asynchronous Transmit or<br>Synchronous Clock.                               |

| RC7/RX/DT         | 26          | 29           | 1           | I/O           | ST                    | RC7 can also be the USART Asynchronous Receive or<br>Synchronous Data.                                 |

|                   |             |              |             |               |                       | PORTD is a bi-directional I/O port or parallel slave port when interfacing to a microprocessor bus.    |

| RD0/PSP0          | 19          | 21           | 38          | I/O           | ST/TTL <sup>(3)</sup> | when interfacing to a microprocessor bus.                                                              |

| RD1/PSP1          | 20          | 21           | 39          | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD2/PSP2          | 20          | 22           | 40          | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD3/PSP3          | 22          | 23           | 41          | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD4/PSP4          | 27          | 30           | 2           | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD5/PSP5          | 28          | 31           | 3           | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD6/PSP6          | 29          | 32           | 4           | 1/O           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD7/PSP7          | 30          | 33           | 5           | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

|                   |             |              |             | 1/0           | OI/ITE                | PORTE is a bi-directional I/O port.                                                                    |

| RE0/RD/AN5        | 8           | 9            | 25          | I/O           | ST/TTL <sup>(3)</sup> | RE0 can also be read control for the parallel slave port,<br>or analog input5.                         |

| RE1/WR/AN6        | 9           | 10           | 26          | I/O           | ST/TTL <sup>(3)</sup> | RE1 can also be write control for the parallel slave port, or analog input6.                           |

| RE2/CS/AN7        | 10          | 11           | 27          | I/O           | ST/TTL <sup>(3)</sup> | RE2 can also be select control for the parallel slave port, or analog input7.                          |

| Vss               | 12,31       | 13,34        | 6,29        | Р             |                       | Ground reference for logic and I/O pins.                                                               |

| Vdd               | 11,32       | 12,35        | 7,28        | Р             | _                     | Positive supply for logic and I/O pins.                                                                |

| NC                | —           | 1,17,28,     | 12,13,      |               |                       | These pins are not internally connected. These pins should                                             |

|                   |             | 40           | 33,34       |               |                       | be left unconnected.                                                                                   |

| Legend: I = input | 0 = oi      | •            |             |               | put/output            | P = power                                                                                              |

|                   |             | lot used     |             |               | TL input              | ST = Schmitt Trigger input<br>external interrupt.                                                      |

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

This buffer is a Schmitt Trigger input when used in serial programming mode.

This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel

Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

| Address                   | Name    | Bit 7                | Bit 6                        | Bit 5          | Bit 4           | Bit 3          | Bit 2           | Bit 1       | Bit 0   | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(2) |

|---------------------------|---------|----------------------|------------------------------|----------------|-----------------|----------------|-----------------|-------------|---------|--------------------------|-------------------------------------|

| Bank 0                    |         |                      |                              |                |                 |                |                 |             |         |                          |                                     |

| 00h <sup>(4)</sup>        | INDF    | Addressing           | this location                | egister)       | 0000 0000       | 0000 0000      |                 |             |         |                          |                                     |

| 01h                       | TMR0    | Timer0 mod           | lule's registe               |                | xxxx xxxx       | uuuu uuuu      |                 |             |         |                          |                                     |

| 02h <sup>(4)</sup>        | PCL     | Program Co           | ounter's (PC)                | Least Signif   | icant Byte      |                |                 |             |         | 0000 0000                | 0000 0000                           |

| 03h <b>(4)</b>            | STATUS  | IRP <sup>(7)</sup>   | RP1 <sup>(7)</sup>           | RP0            | TO              | PD             | Z               | DC          | С       | 0001 1xxx                | 000q quuu                           |

| 04h <b>(4)</b>            | FSR     | Indirect data        | a memory ad                  | dress pointe   | er              |                |                 |             | •       | XXXX XXXX                | uuuu uuuu                           |

| 05h                       | PORTA   | _                    | _                            | PORTA Dat      | a Latch when    | written: POR   | TA pins wher    | read        |         | 0x 0000                  | 0u 0000                             |

| 06h                       | PORTB   | PORTB Dat            | a Latch whe                  | n written: PC  | ORTB pins whe   | n read         |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 07h                       | PORTC   | PORTC Dat            | ta Latch whe                 | n written: PC  | DRTC pins whe   | en read        |                 |             |         | XXXX XXXX                | uuuu uuuu                           |

| 08h <sup>(5)</sup>        | PORTD   | PORTD Dat            | a Latch whe                  | n written: PC  | ORTD pins whe   | en read        |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 09h <b>(5)</b>            | PORTE   | _                    | _                            | _              | _               | _              | RE2             | RE1         | RE0     | xxx                      | uuu                                 |

| 0Ah <b>(1,4)</b>          | PCLATH  | _                    | _                            | _              | Write Buffer fo | or the upper t | 5 bits of the I | Program Cou | unter   | 0 0000                   | 0 0000                              |

| 0Bh <b><sup>(4)</sup></b> | INTCON  | GIE                  | PEIE                         | TOIE           | INTE            | RBIE           | T0IF            | INTF        | RBIF    | 0000 000x                | 0000 000u                           |

| 0Ch                       | PIR1    | PSPIF <sup>(3)</sup> | ADIF                         | RCIF           | TXIF            | SSPIF          | CCP1IF          | TMR2IF      | TMR1IF  | 0000 0000                | 0000 0000                           |

| 0Dh                       | PIR2    | —                    | —                            | -              | -               | -              | —               | —           | CCP2IF  | 0                        | 0                                   |

| 0Eh                       | TMR1L   | Holding reg          | ister for the L              | east Signific  | ant Byte of the | e 16-bit TMR1  | l register      |             |         | xxxx xxxx                | uuuu uuuu                           |

| 0Fh                       | TMR1H   | Holding reg          | ister for the N              | lost Significa | ant Byte of the | 16-bit TMR1    | register        |             |         | XXXX XXXX                | uuuu uuuu                           |

| 10h                       | T1CON   | —                    | —                            | T1CKPS1        | T1CKPS0         | T1OSCEN        | <b>T1SYNC</b>   | TMR1CS      | TMR10N  | 00 0000                  | uu uuuu                             |

| 11h                       | TMR2    | Timer2 mod           | lule's registe               | r              |                 |                |                 |             |         | 0000 0000                | 0000 0000                           |

| 12h                       | T2CON   | —                    | TOUTPS3                      | TOUTPS2        | TOUTPS1         | TOUTPS0        | TMR2ON          | T2CKPS1     | T2CKPS0 | -000 0000                | -000 0000                           |

| 13h                       | SSPBUF  | Synchronou           | is Serial Port               | Receive Bu     | ffer/Transmit R | egister        |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 14h                       | SSPCON  | WCOL                 | SSPOV                        | SSPEN          | СКР             | SSPM3          | SSPM2           | SSPM1       | SSPM0   | 0000 0000                | 0000 0000                           |

| 15h                       | CCPR1L  | Capture/Co           | mpare/PWM                    | Register1 (L   | _SB)            |                |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 16h                       | CCPR1H  | Capture/Co           | mpare/PWM                    | Register1 (N   | MSB)            |                |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 17h                       | CCP1CON | —                    | —                            | CCP1X          | CCP1Y           | CCP1M3         | CCP1M2          | CCP1M1      | CCP1M0  | 00 0000                  | 00 0000                             |

| 18h                       | RCSTA   | SPEN                 | RX9                          | SREN           | CREN            | —              | FERR            | OERR        | RX9D    | 0000 -00x                | 0000 -00x                           |

| 19h                       | TXREG   | USART Trar           | USART Transmit Data Register |                |                 |                |                 |             |         |                          | 0000 0000                           |

| 1Ah                       | RCREG   | USART Red            | ceive Data R                 |                | 0000 0000       | 0000 0000      |                 |             |         |                          |                                     |

| 1Bh                       | CCPR2L  | Capture/Co           | mpare/PWM                    | Register2 (L   | _SB)            |                |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 1Ch                       | CCPR2H  | Capture/Co           | mpare/PWM                    | Register2 (N   | MSB)            |                |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 1Dh                       | CCP2CON | —                    | —                            | CCP2X          | CCP2Y           | CCP2M3         | CCP2M2          | CCP2M1      | CCP2M0  | 00 0000                  | 00 0000                             |

| 1Eh                       | ADRES   | A/D Result           | Register                     |                |                 |                |                 |             |         | XXXX XXXX                | uuuu uuuu                           |

| 1Fh                       | ADCON0  | ADCS1                | ADCS0                        | CHS2           | CHS1            | CHS0           | GO/DONE         | —           | ADON    | 0000 00-0                | 0000 00-0                           |

TABLE 4-2:

PIC16C73/73A/74/74A SPECIAL FUNCTION REGISTER SUMMARY

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A, always maintain these bits clear.

4: These registers can be addressed from either bank.

5: PORTD and PORTE are not physically implemented on the PIC16C73/73A, read as '0'.

6: Brown-out Reset is not implemented on the PIC16C73 or the PIC16C74, read as '0'.

7: The IRP and RP1 bits are reserved on the PIC16C73/73A/74/74A, always maintain these bits clear.

| Address                    | Name   | Bit 7         | Bit 6          | Bit 5         | Bit 4            | Bit 3         | Bit 2           | Bit 1         | Bit 0    | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(2) |

|----------------------------|--------|---------------|----------------|---------------|------------------|---------------|-----------------|---------------|----------|--------------------------|-------------------------------------|

| Bank 2                     |        | •             |                |               |                  |               |                 |               |          |                          |                                     |

| 100h <sup>(4)</sup>        | INDF   | Addressing    | this location  | uses conter   | nts of FSR to a  | ddress data r | memory (not     | a physical re | egister) | 0000 0000                | 0000 0000                           |

| 101h                       | TMR0   | Timer0 mod    | lule's registe |               | xxxx xxxx        | uuuu uuuu     |                 |               |          |                          |                                     |

| 102h <sup>(4)</sup>        | PCL    | Program Co    | ounter's (PC)  |               | 0000 0000        | 0000 0000     |                 |               |          |                          |                                     |

| 103h <sup>(4)</sup>        | STATUS | IRP           | RP1            | RP0           | TO               | PD            | z               | DC            | с        | 0001 1xxx                | 000q quuu                           |

| 104h <sup>(4)</sup>        | FSR    | Indirect data | a memory ad    | ldress pointe | )<br>Pr          |               |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 105h                       | _      | Unimpleme     | nted           |               |                  |               |                 |               |          | _                        | —                                   |

| 106h                       | PORTB  | PORTB Dat     | a Latch whe    | n written: PC | ORTB pins whe    | n read        |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 107h                       | _      | Unimpleme     | nted           |               |                  |               |                 |               |          | _                        | —                                   |

| 108h                       | —      | Unimpleme     | nted           |               |                  |               |                 |               |          | _                        | _                                   |

| 109h                       | —      | Unimpleme     | nted           |               |                  |               |                 |               |          | —                        | —                                   |

| 10Ah <b>(1,4)</b>          | PCLATH | -             | —              | —             | Write Buffer fo  | or the upper  | 5 bits of the I | Program Cou   | Inter    | 0 0000                   | 0 0000                              |

| 10Bh <b><sup>(4)</sup></b> | INTCON | GIE           | PEIE           | TOIE          | INTE             | RBIE          | TOIF            | INTF          | RBIF     | 0000 000x                | 0000 000u                           |

| 10Ch-<br>10Fh              | _      | Unimpleme     | nted           |               |                  | •             |                 |               | •        | _                        | _                                   |

| Bank 3                     |        |               |                |               |                  |               |                 |               |          |                          |                                     |

| 180h <sup>(4)</sup>        | INDF   | Addressing    | this location  | uses conter   | nts of FSR to ad | ddress data r | nemory (not     | a physical re | egister) | 0000 0000                | 0000 0000                           |

| 181h                       | OPTION | RBPU          | INTEDG         | TOCS          | TOSE             | PSA           | PS2             | PS1           | PS0      | 1111 1111                | 1111 1111                           |

| 182h <sup>(4)</sup>        | PCL    | Program Co    | ounter's (PC)  | Least Sigr    | nificant Byte    | •             |                 |               | •        | 0000 0000                | 0000 0000                           |

| 183h <sup>(4)</sup>        | STATUS | IRP           | RP1            | RP0           | TO               | PD            | z               | DC            | с        | 0001 1xxx                | 000q quuu                           |

| 184h <sup>(4)</sup>        | FSR    | Indirect data | a memory ad    | ldress pointe | )<br>Pr          |               |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 185h                       | _      | Unimpleme     | nted           |               |                  |               |                 |               |          | _                        | —                                   |

| 186h                       | TRISB  | PORTB Dat     | a Direction F  | Register      |                  |               |                 |               |          | 1111 1111                | 1111 1111                           |

| 187h                       | _      | Unimpleme     | nted           |               |                  |               |                 |               |          | _                        | —                                   |

| 188h                       | —      | Unimpleme     | nted           |               | —                | —             |                 |               |          |                          |                                     |

| 189h                       | _      | Unimpleme     | nted           |               | —                | —             |                 |               |          |                          |                                     |

| 18Ah <b>(1,4)</b>          | PCLATH | -             | —              | Inter         | 0 0000           | 0 0000        |                 |               |          |                          |                                     |

| 18Bh <b><sup>(4)</sup></b> | INTCON | GIE           | PEIE           | TOIE          | RBIF             | 0000 000x     | 0000 000u       |               |          |                          |                                     |

| 18Ch-<br>18Fh              | _      | Unimpleme     | nted           |               |                  |               |                 |               |          | _                        | _                                   |

TABLE 4-3: PIC16C76/77 SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

$\label{eq:legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.$  Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the PIC16C76, always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD and PORTE are not physically implemented on the PIC16C76, read as '0'.

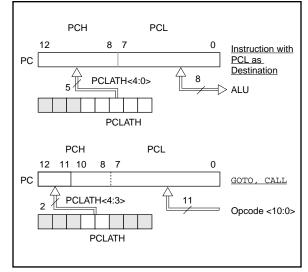

#### 4.3 PCL and PCLATH Applicable Devices 72/73/73A/74/74A/76/77

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any reset, the upper bits of the PC will be cleared. Figure 4-17 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 4-17: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note *"Implementing a Table Read"* (AN556).

#### 4.3.2 STACK

The PIC16CXX family has an 8 level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no status bits to indicate stack overflow or stack underflow conditions.

- Note 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address.

#### 4.4 Program Memory Paging Applicable Devices 72|73|73A|74|74A|76|77

PIC16C7X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<4:3> bits are not required for the return instructions (which POPs the address from the stack).

Note: PIC16C7X devices with 4K or less of program memory ignore paging bit PCLATH<4>. The use of PCLATH<4> as a general purpose read/write bit is not recommended since this may affect upward compatibility with future products.

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

| Note: | To avoid an unintended device RESET, the |

|-------|------------------------------------------|

|       | following instruction sequence (shown in |

|       | Example 7-1) must be executed when       |

|       | changing the prescaler assignment from   |

|       | Timer0 to the WDT. This sequence must    |

|       | be followed even if the WDT is disabled. |

#### EXAMPLE 7-1: CHANGING PRESCALER (TIMER0→WDT)

|                                                                   | 1)  | BSF    | STATUS, RPO | ;Bank 1                                    |

|-------------------------------------------------------------------|-----|--------|-------------|--------------------------------------------|

| Lines 2 and 3 do NOT have to                                      | 2)  | MOVLW  | b'xx0x0xxx' | ;Select clock source and prescale value of |

| be included if the final desired                                  | 3)  | MOVWF  | OPTION_REG  | ;other than 1:1                            |

| prescale value is other than 1:1.                                 | 4)  | BCF    | STATUS, RPO | ;Bank 0                                    |

| If 1:1 is final desired value, then a temporary prescale value is | 5)  | CLRF   | TMR0        | ;Clear TMR0 and prescaler                  |

| set in lines 2 and 3 and the final                                | 6)  | BSF    | STATUS, RP1 | ;Bank 1                                    |

| prescale value will be set in lines                               | 7)  | MOVLW  | b'xxxx1xxx' | ;Select WDT, do not change prescale value  |

| 10 and 11.                                                        | 8)  | MOVWF  | OPTION_REG  | ;                                          |

|                                                                   | 9)  | CLRWDT |             | ;Clears WDT and prescaler                  |

|                                                                   | 10) | MOVLW  | b'xxxx1xxx' | ;Select new prescale value and WDT         |

|                                                                   | 11) | MOVWF  | OPTION_REG  | ;                                          |

|                                                                   | 12) | BCF    | STATUS, RPO | ;Bank 0                                    |

To change prescaler from the WDT to the Timer0 module use the sequence shown in Example 7-2.

#### EXAMPLE 7-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and prescaler             |

|--------|-------------|--------------------------------------|

| BSF    | STATUS, RPO | ;Bank 1                              |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new prescale value and |

| MOVWF  | OPTION_REG  | ;clock source                        |

| BCF    | STATUS, RPO | ;Bank 0                              |

|        |             |                                      |

#### TABLE 7-1: **REGISTERS ASSOCIATED WITH TIMER0**

| Address               | Name   | Bit 7  | Bit 6       | Bit 5    | Bit 4       | Bit 3      | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------------------|--------|--------|-------------|----------|-------------|------------|-------|-------|-------|--------------------------|---------------------------|

| 01h,101h              | TMR0   | Timer0 | module's re | egister  | _           |            |       |       |       | xxxx xxxx                | uuuu uuuu                 |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE    | PEIE        | TOIE     | INTE        | RBIE       | TOIF  | INTF  | RBIF  | 0000 000x                | 0000 000u                 |

| 81h,181h              | OPTION | RBPU   | INTEDG      | TOCS     | TOSE        | PSA        | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                 |

| 85h                   | TRISA  | —      |             | PORTA Da | ta Directio | on Registe | er    |       |       | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

#### FIGURE 9-2: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

| U-0      | R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0                                                                                                     |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| <u> </u> | TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0 R = Readable bit                                                                 |  |

| bit7     | bit0<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset                                           |  |

| bit 7:   | Unimplemented: Read as '0'                                                                                                              |  |

| bit 6-3: | TOUTPS3:TOUTPS0: Timer2 Output Postscale Select bits<br>0000 = 1:1 Postscale<br>0001 = 1:2 Postscale<br>•<br>•<br>1111 = 1:16 Postscale |  |

| bit 2:   | TMR2ON: Timer2 On bit<br>1 = Timer2 is on<br>0 = Timer2 is off                                                                          |  |

| bit 1-0: | <b>T2CKPS1:T2CKPS0</b> : Timer2 Clock Prescale Select bits<br>00 = Prescaler is 1<br>01 = Prescaler is 4<br>1x = Prescaler is 16        |  |

#### **TABLE 9-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER**

| Address               | Name   | Bit 7                  | Bit 6          | Bit 5               | Bit 4               | Bit 3     | Bit 2     | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|-----------------------|--------|------------------------|----------------|---------------------|---------------------|-----------|-----------|---------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                    | PEIE           | TOIE                | INTE                | RBIE      | TOIF      | INTF    | RBIF    | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1   | PSPIF <sup>(1,2)</sup> | ADIF           | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | SSPIF     | CCP1IF    | TMR2IF  | TMR1IF  | 0000 0000                | 0000 0000                       |

| 8Ch                   | PIE1   | PSPIE <sup>(1,2)</sup> | ADIE           | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup> | SSPIE     | CCP1IE    | TMR2IE  | TMR1IE  | 0000 0000                | 0000 0000                       |

| 11h                   | TMR2   | Timer2 mod             | lule's registe | r                   |                     |           |           |         |         | 0000 0000                | 0000 0000                       |

| 12h                   | T2CON  | _                      | TOUTPS3        | TOUTPS2             | TOUTPS1             | TOUTPS0   | TMR2ON    | T2CKPS1 | T2CKPS0 | -000 0000                | -000 0000                       |

| 92h                   | PR2    | Timer2 Peri            | od Register    |                     |                     | 1111 1111 | 1111 1111 |         |         |                          |                                 |

Legend:

x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

Note

1:

Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

2:

The PIC16C72 does not have a Parallel Slave Port or a USART, these bits are unimplemented, read as '0'.

| BAUD<br>RATE<br>(K) | Fosc = 2<br>KBAUD | 20 MHz<br>%<br>ERROR | SPBRG<br>value<br>(decimal) | 16 MHz<br>KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) | 10 MHz<br>KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) | 7.16 MH | z<br>%<br>ERROR | SPBRG<br>value<br>(decimal) |

|---------------------|-------------------|----------------------|-----------------------------|-----------------|------------|-----------------------------|-----------------|------------|-----------------------------|---------|-----------------|-----------------------------|

| 9.6                 | 9.615             | +0.16                | 129                         | 9.615           | +0.16      | 103                         | 9.615           | +0.16      | 64                          | 9.520   | -0.83           | 46                          |

| 19.2                | 19.230            | +0.16                | 64                          | 19.230          | +0.16      | 51                          | 18.939          | -1.36      | 32                          | 19.454  | +1.32           | 22                          |

| 38.4                | 37.878            | -1.36                | 32                          | 38.461          | +0.16      | 25                          | 39.062          | +1.7       | 15                          | 37.286  | -2.90           | 11                          |

| 57.6                | 56.818            | -1.36                | 21                          | 58.823          | +2.12      | 16                          | 56.818          | -1.36      | 10                          | 55.930  | -2.90           | 7                           |

| 115.2               | 113.636           | -1.36                | 10                          | 111.111         | -3.55      | 8                           | 125             | +8.51      | 4                           | 111.860 | -2.90           | 3                           |

| 250                 | 250               | 0                    | 4                           | 250             | 0          | 3                           | NA              | -          | -                           | NA      | -               | -                           |

| 625                 | 625               | 0                    | 1                           | NA              | -          | -                           | 625             | 0          | 0                           | NA      | -               | -                           |

| 1250                | 1250              | 0                    | 0                           | NA              | -          | -                           | NA              | -          | -                           | NA      | -               | -                           |

### TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD        | Fosc = 5 | .068 MHz   | SPBRG              | 4 MHz  |            | SPBRG              | 3.579 Mł | Ηz         | SPBRG              | 1 MHz  |            | SPBRG              | 32.768 | κHz        | SPBRG              |

|-------------|----------|------------|--------------------|--------|------------|--------------------|----------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) |

| 9.6         | 9.6      | 0          | 32                 | NA     | -          | -                  | 9.727    | +1.32      | 22                 | 8.928  | -6.99      | 6                  | NA     | -          | -                  |

| 19.2        | 18.645   | -2.94      | 16                 | 1.202  | +0.17      | 207                | 18.643   | -2.90      | 11                 | 20.833 | +8.51      | 2                  | NA     | -          | -                  |

| 38.4        | 39.6     | +3.12      | 7                  | 2.403  | +0.13      | 103                | 37.286   | -2.90      | 5                  | 31.25  | -18.61     | 1                  | NA     | -          | -                  |

| 57.6        | 52.8     | -8.33      | 5                  | 9.615  | +0.16      | 25                 | 55.930   | -2.90      | 3                  | 62.5   | +8.51      | 0                  | NA     | -          | -                  |

| 115.2       | 105.6    | -8.33      | 2                  | 19.231 | +0.16      | 12                 | 111.860  | -2.90      | 1                  | NA     | -          | -                  | NA     | -          | -                  |

| 250         | NA       | -          | -                  | NA     | -          | -                  | 223.721  | -10.51     | 0                  | NA     | -          | -                  | NA     | -          | -                  |

| 625         | NA       | -          | -                  | NA     | -          | -                  | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| 1250        | NA       | -          | -                  | NA     | -          | -                  | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

**Note:** For the PIC16C73/73A/74/74A, the asynchronous high speed mode (BRGH = 1) may experience a high rate of receive errors. It is recommended that BRGH = 0. If you desire a higher baud rate than BRGH = 0 can support, refer to the device errata for additional information, or use the PIC16C76/77.

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH. (Section 12.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC, and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

#### TABLE 12-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address | Name  | Bit 7                           | Bit 6    | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|---------------------------------|----------|--------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup>            | ADIF     | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h     | RCSTA | SPEN                            | RX9      | SREN   | CREN  |       | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 1Ah     | RCREG | USART Rec                       | eive Reç | gister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup>            | ADIE     | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h     | TXSTA | CSRC                            | TX9      | TXEN   | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h     | SPBRG | RG Baud Rate Generator Register |          |        |       |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

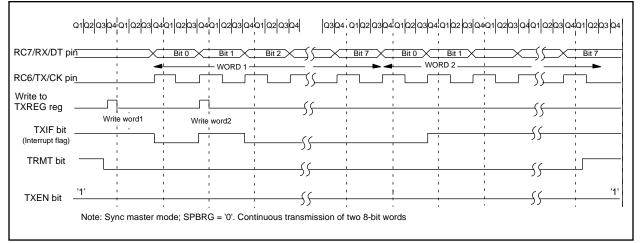

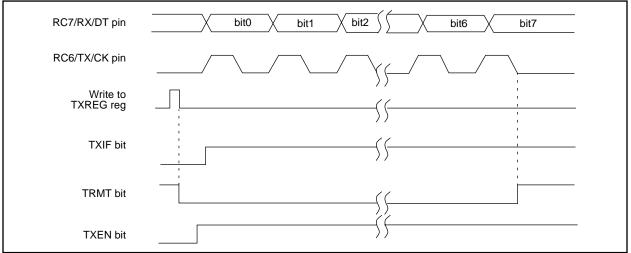

#### TABLE 12-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address | Name                                  | Bit 7                | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|---------------------------------------|----------------------|-----------|---------|-------|-------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1                                  | PSPIF <sup>(1)</sup> | ADIF      | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA                                 | SPEN                 | RX9       | SREN    | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                 |

| 19h     | TXREG                                 | USART Tra            | ansmit Re | egister |       |       |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1                                  | PSPIE <sup>(1)</sup> | ADIE      | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA                                 | CSRC                 | TX9       | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | 9h SPBRG Baud Rate Generator Register |                      |           |         |       |       |        |        |        | 0000 0000                | 0000 0000                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for Synchronous Master Transmission. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

#### FIGURE 12-12: SYNCHRONOUS TRANSMISSION

#### FIGURE 12-13: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

#### 13.4 A/D Conversions

Applicable Devices

72

73

73

74

74

76

77

Example 13-2 shows how to perform an A/D conversion. The RA pins are configured as analog inputs. The analog reference (VREF) is the device VDD. The A/D interrupt is enabled, and the A/D conversion clock is FRC. The conversion is performed on the RA0 pin (channel 0).

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRES register will NOT be updated with the partially completed A/D conversion sample. That is, the ADRES register will continue to contain the value of the last completed conversion (or the last value written to the ADRES register). After the A/D conversion is aborted, a 2TAD wait is required before the next acquisition is started. After this 2TAD wait, an acquisition is automatically started on the selected channel.

#### EXAMPLE 13-2: A/D CONVERSION

;

; ;

| BSF       | STATUS,  | RP0           | ;  | Select Bank 1                                       |

|-----------|----------|---------------|----|-----------------------------------------------------|

| BCF       | STATUS,  | RP1           | ;  | PIC16C76/77 only                                    |

| CLRF      | ADCON1   |               | ;  | Configure A/D inputs                                |

| BSF       | PIE1,    | ADIE          | ;  | Enable A/D interrupts                               |

| BCF       | STATUS,  | RP0           | ;  | Select Bank 0                                       |

| MOVLW     | 0xC1     |               | ;  | RC Clock, A/D is on, Channel 0 is selected          |

| MOVWF     | ADCON0   |               | ;  |                                                     |

| BCF       | PIR1,    | ADIF          | ;  | Clear A/D interrupt flag bit                        |

| BSF       | INTCON,  | PEIE          | ;  | Enable peripheral interrupts                        |

| BSF       | INTCON,  | GIE           | ;  | Enable all interrupts                               |

| Ensure th | at the r | equired samp  | li | ng time for the selected input channel has elapsed. |

|           |          | on may be sta |    |                                                     |

| BSF | ADCON0, | GO | ; | ; Start A/D Conversion                              |  |

|-----|---------|----|---|-----------------------------------------------------|--|

| :   |         |    | ; | ; The ADIF bit will be set and the GO/DONE bit      |  |

| :   |         |    | ; | ; is cleared upon completion of the A/D Conversion. |  |

NOTES:

#### 14.4.5 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 14-10, Figure 14-11, and Figure 14-12 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 14-11). This is useful for testing purposes or to synchronize more than one PIC16CXX device operating in parallel.

Table 14-7 shows the reset conditions for some special function registers, while Table 14-8 shows the reset conditions for all the registers.

#### 14.4.6 POWER CONTROL/STATUS REGISTER (PCON)

| Ар | pli | cabl | e D | evic | es |    |

|----|-----|------|-----|------|----|----|

| 72 | 73  | 73A  | 74  | 74A  | 76 | 77 |

The Power Control/Status Register, PCON has up to two bits, depending upon the device. Bit0 is not implemented on the PIC16C73 or PIC16C74.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent resets to see if bit BOR cleared, indicating a BOR occurred. The BOR bit is a "Don't Care" bit and is not necessarily predictable if the Brown-out Reset circuitry is disabled (by clearing bit BODEN in the Configuration Word).

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

#### TABLE 14-3: TIME-OUT IN VARIOUS SITUATIONS, PIC16C73/74

| Oscillator Configuration | Powe             | Wake-up from SLEEP |           |

|--------------------------|------------------|--------------------|-----------|

|                          | PWRTE = 1        | PWRTE = 0          |           |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc           | 1024 Tosc |

| RC                       | 72 ms            | _                  |           |

#### TABLE 14-4: TIME-OUT IN VARIOUS SITUATIONS, PIC16C72/73A/74A/76/77

| Oscillator Configuration | Power            | r-up      | Brown-out        | Wake-up from SLEEP |  |

|--------------------------|------------------|-----------|------------------|--------------------|--|

|                          | PWRTE = 0        | PWRTE = 1 | Brown-out        |                    |  |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc           |  |

| RC                       | 72 ms            |           | 72 ms            | _                  |  |

#### TABLE 14-5: STATUS BITS AND THEIR SIGNIFICANCE, PIC16C73/74

| POR | TO | PD |                                                         |  |  |  |

|-----|----|----|---------------------------------------------------------|--|--|--|

| 0   | 1  | 1  | Power-on Reset                                          |  |  |  |

| 0   | 0  | x  | Illegal, TO is set on POR                               |  |  |  |

| 0   | x  | 0  | Illegal, PD is set on POR                               |  |  |  |

| 1   | 0  | 1  | WDT Reset                                               |  |  |  |

| 1   | 0  | 0  | WDT Wake-up                                             |  |  |  |

| 1   | u  | u  | MCLR Reset during normal operation                      |  |  |  |

| 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |  |  |  |

Legend: u = unchanged, x = unknown

# 14.8 Power-down Mode (SLEEP) Applicable Devices 727373A7474A7677

Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD, or Vss, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D, disable external clocks. Pull all I/O pins, that are hi-impedance inputs, high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level (VIHMC).

#### 14.8.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change, or some Peripheral Interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. SSP (Start/Stop) bit detect interrupt.

- 3. SSP transmit or receive in slave mode (SPI/ $l^2$ C).

- 4. CCP capture mode interrupt.

- 5. Parallel Slave Port read or write.

- 6. A/D conversion (when A/D clock source is RC).

- 7. Special event trigger (Timer1 in asynchronous mode using an external clock).

- 8. USART TX or RX (synchronous slave mode).

Other peripherals cannot generate interrupts since during SLEEP, no on-chip Q clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 14.8.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

### Applicable Devices 72 73 73A 74 74A 76 77

#### 18.2 DC Characteristics: PIC16LC73/74-04 (Commercial, Industrial)

| DC CHA                | ARACTERISTICS                                                    |      | <b>Standa</b><br>Operat | itions (unless otherwise stated) $0^{\circ}C$ $\leq TA \leq +85^{\circ}C$ for industrial and $C$ $\leq TA \leq +70^{\circ}C$ for commercial |                  |                |                                                                                                                                                                                              |

|-----------------------|------------------------------------------------------------------|------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.          | Characteristic                                                   | Sym  | Min                     | Тур†                                                                                                                                        | Мах              | Units          | Conditions                                                                                                                                                                                   |

| D001                  | Supply Voltage                                                   | Vdd  | 3.0                     | -                                                                                                                                           | 6.0              | V              | LP, XT, RC osc configuration (DC - 4 MHz)                                                                                                                                                    |

| D002*                 | RAM Data Retention<br>Voltage (Note 1)                           | Vdr  | -                       | 1.5                                                                                                                                         | -                | V              |                                                                                                                                                                                              |

| D003                  | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR | -                       | Vss                                                                                                                                         | -                | V              | See section on Power-on Reset for details                                                                                                                                                    |

| D004*                 | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | Svdd | 0.05                    | -                                                                                                                                           | -                | V/ms           | See section on Power-on Reset for details                                                                                                                                                    |

| D010                  | Supply Current (Note 2,5)                                        | IDD  | -                       | 2.0                                                                                                                                         | 3.8              | mA             | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                                                                                |

| D010A                 |                                                                  |      | -                       | 22.5                                                                                                                                        | 48               | μA             | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                                                                                                              |

| D020<br>D021<br>D021A | Power-down Current<br>(Note 3,5)                                 | IPD  |                         | 7.5<br>0.9<br>0.9                                                                                                                           | 30<br>13.5<br>18 | μΑ<br>μΑ<br>μΑ | VDD = $3.0V$ , WDT enabled, $-40^{\circ}C$ to $+85^{\circ}C$<br>VDD = $3.0V$ , WDT disabled, $0^{\circ}C$ to $+70^{\circ}C$<br>VDD = $3.0V$ , WDT disabled, $-40^{\circ}C$ to $+85^{\circ}C$ |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

$\overline{\text{MCLR}}$  = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

Applicable Devices

72

73

73A

74

74A

76

77

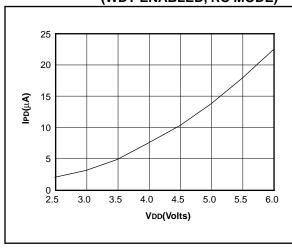

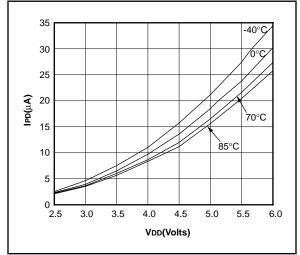

FIGURE 21-3: TYPICAL IPD vs. VDD @ 25°C (WDT ENABLED, RC MODE)

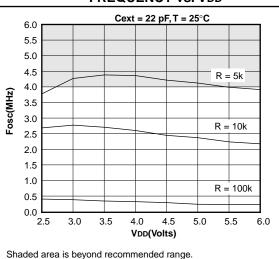

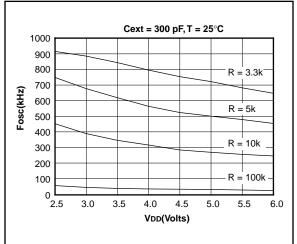

#### FIGURE 21-5: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

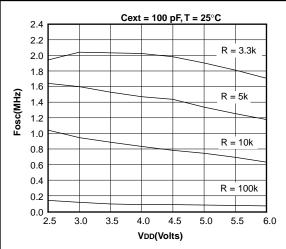

FIGURE 21-7: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

## PIC16C7X

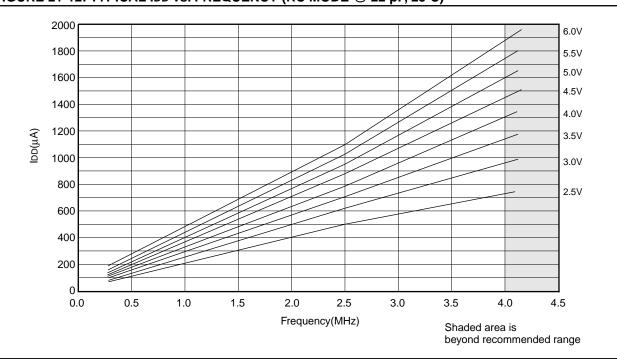

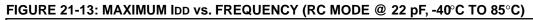

## Applicable Devices 72 73 73A 74 74A 76 77 FIGURE 21-12: TYPICAL IDD vs. FREQUENCY (RC MODE @ 22 pF, 25°C)

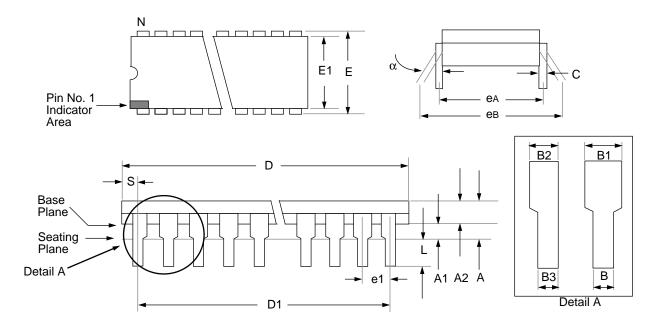

### 22.3 28-Lead Plastic Dual In-line (300 mil) (SP)

|        | Package Group: Plastic Dual In-Line (PLA) |             |           |        |       |           |  |  |  |  |

|--------|-------------------------------------------|-------------|-----------|--------|-------|-----------|--|--|--|--|

|        |                                           | Millimeters |           | Inches |       |           |  |  |  |  |

| Symbol | Min                                       | Мах         | Notes     | Min    | Max   | Notes     |  |  |  |  |

| α      | 0°                                        | 10°         |           | 0°     | 10°   |           |  |  |  |  |

| Α      | 3.632                                     | 4.572       |           | 0.143  | 0.180 |           |  |  |  |  |

| A1     | 0.381                                     | _           |           | 0.015  | _     |           |  |  |  |  |

| A2     | 3.175                                     | 3.556       |           | 0.125  | 0.140 |           |  |  |  |  |

| В      | 0.406                                     | 0.559       |           | 0.016  | 0.022 |           |  |  |  |  |

| B1     | 1.016                                     | 1.651       | Typical   | 0.040  | 0.065 | Typical   |  |  |  |  |

| B2     | 0.762                                     | 1.016       | 4 places  | 0.030  | 0.040 | 4 places  |  |  |  |  |

| B3     | 0.203                                     | 0.508       | 4 places  | 0.008  | 0.020 | 4 places  |  |  |  |  |

| С      | 0.203                                     | 0.331       | Typical   | 0.008  | 0.013 | Typical   |  |  |  |  |

| D      | 34.163                                    | 35.179      |           | 1.385  | 1.395 |           |  |  |  |  |

| D1     | 33.020                                    | 33.020      | Reference | 1.300  | 1.300 | Reference |  |  |  |  |

| E      | 7.874                                     | 8.382       |           | 0.310  | 0.330 |           |  |  |  |  |

| E1     | 7.112                                     | 7.493       |           | 0.280  | 0.295 |           |  |  |  |  |

| e1     | 2.540                                     | 2.540       | Typical   | 0.100  | 0.100 | Typical   |  |  |  |  |

| eA     | 7.874                                     | 7.874       | Reference | 0.310  | 0.310 | Reference |  |  |  |  |

| eB     | 8.128                                     | 9.652       |           | 0.320  | 0.380 |           |  |  |  |  |

| L      | 3.175                                     | 3.683       |           | 0.125  | 0.145 |           |  |  |  |  |

| Ν      | 28                                        | -           |           | 28     | -     |           |  |  |  |  |

| S      | 0.584                                     | 1.220       |           | 0.023  | 0.048 |           |  |  |  |  |

## PIC16C7X

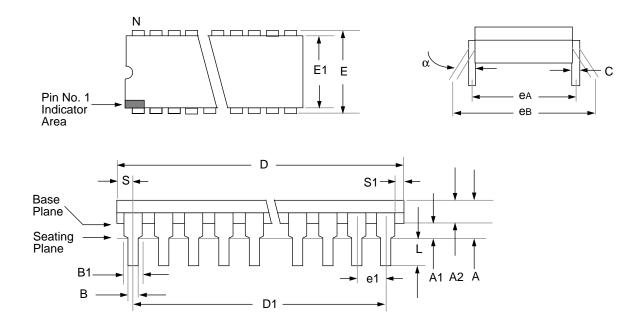

### 22.4 40-Lead Plastic Dual In-line (600 mil) (P)

|        | Package Group: Plastic Dual In-Line (PLA) |             |           |            |       |           |  |  |  |  |

|--------|-------------------------------------------|-------------|-----------|------------|-------|-----------|--|--|--|--|

|        |                                           | Millimeters |           | Inches     |       |           |  |  |  |  |

| Symbol | Min                                       | Мах         | Notes     | Min        | Max   | Notes     |  |  |  |  |

| α      | 0°                                        | 10°         |           | <b>0</b> ° | 10°   |           |  |  |  |  |

| А      | _                                         | 5.080       |           | _          | 0.200 |           |  |  |  |  |

| A1     | 0.381                                     | _           |           | 0.015      | -     |           |  |  |  |  |

| A2     | 3.175                                     | 4.064       |           | 0.125      | 0.160 |           |  |  |  |  |

| В      | 0.355                                     | 0.559       |           | 0.014      | 0.022 |           |  |  |  |  |

| B1     | 1.270                                     | 1.778       | Typical   | 0.050      | 0.070 | Typical   |  |  |  |  |

| С      | 0.203                                     | 0.381       | Typical   | 0.008      | 0.015 | Typical   |  |  |  |  |

| D      | 51.181                                    | 52.197      |           | 2.015      | 2.055 |           |  |  |  |  |

| D1     | 48.260                                    | 48.260      | Reference | 1.900      | 1.900 | Reference |  |  |  |  |

| E      | 15.240                                    | 15.875      |           | 0.600      | 0.625 |           |  |  |  |  |

| E1     | 13.462                                    | 13.970      |           | 0.530      | 0.550 |           |  |  |  |  |

| e1     | 2.489                                     | 2.591       | Typical   | 0.098      | 0.102 | Typical   |  |  |  |  |

| eA     | 15.240                                    | 15.240      | Reference | 0.600      | 0.600 | Reference |  |  |  |  |

| eB     | 15.240                                    | 17.272      |           | 0.600      | 0.680 |           |  |  |  |  |

| L      | 2.921                                     | 3.683       |           | 0.115      | 0.145 |           |  |  |  |  |

| N      | 40                                        | 40          |           | 40         | 40    |           |  |  |  |  |

| S      | 1.270                                     | _           |           | 0.050      | _     |           |  |  |  |  |

| S1     | 0.508                                     | _           |           | 0.020      | _     |           |  |  |  |  |

#### **ON-LINE SUPPORT**

Microchip provides two methods of on-line support. These are the Microchip BBS and the Microchip World Wide Web (WWW) site.

Use Microchip's Bulletin Board Service (BBS) to get current information and help about Microchip products. Microchip provides the BBS communication channel for you to use in extending your technical staff with microcontroller and memory experts.

To provide you with the most responsive service possible, the Microchip systems team monitors the BBS, posts the latest component data and software tool updates, provides technical help and embedded systems insights, and discusses how Microchip products provide project solutions.

The web site, like the BBS, is used by Microchip as a means to make files and information easily available to customers. To view the site, the user must have access to the Internet and a web browser, such as Netscape or Microsoft Explorer. Files are also available for FTP download from our FTP site.

#### Connecting to the Microchip Internet Web Site

The Microchip web site is available by using your favorite Internet browser to attach to:

#### www.microchip.com

The file transfer site is available by using an FTP service to connect to:

#### ftp://ftp.futureone.com/pub/microchip

The web site and file transfer site provide a variety of services. Users may download files for the latest Development Tools, Data Sheets, Application Notes, User's Guides, Articles and Sample Programs. A variety of Microchip specific business information is also available, including listings of Microchip sales offices, distributors and factory representatives. Other data available for consideration is:

- Latest Microchip Press Releases

- Technical Support Section with Frequently Asked

Questions

- Design Tips

- Device Errata

- Job Postings

- · Microchip Consultant Program Member Listing

- Links to other useful web sites related to Microchip Products

#### **Connecting to the Microchip BBS**

Connect worldwide to the Microchip BBS using either the Internet or the CompuServe<sup>®</sup> communications network.

#### Internet:

You can telnet or ftp to the Microchip BBS at the address: mchipbbs.microchip.com

#### CompuServe Communications Network:

When using the BBS via the Compuserve Network, in most cases, a local call is your only expense. The Microchip BBS connection does not use CompuServe membership services, therefore you do not need CompuServe membership to join Microchip's BBS. There is no charge for connecting to the Microchip BBS. The procedure to connect will vary slightly from country to country. Please check with your local CompuServe agent for details if you have a problem. CompuServe service allow multiple users various baud rates depending on the local point of access.

The following connect procedure applies in most locations.

- 1. Set your modem to 8-bit, No parity, and One stop (8N1). This is not the normal CompuServe setting which is 7E1.

- 2. Dial your local CompuServe access number.

- 3. Depress the **<Enter>** key and a garbage string will appear because CompuServe is expecting a 7E1 setting.

- Type +, depress the <Enter> key and "Host Name:" will appear.

- 5. Type MCHIPBBS, depress the **<Enter>** key and you will be connected to the Microchip BBS.

In the United States, to find the CompuServe phone number closest to you, set your modem to 7E1 and dial (800) 848-4480 for 300-2400 baud or (800) 331-7166 for 9600-14400 baud connection. After the system responds with "Host Name:", type NETWORK, depress the **<Enter>** key and follow CompuServe's directions.

For voice information (or calling from overseas), you may call (614) 723-1550 for your local CompuServe number.

Microchip regularly uses the Microchip BBS to distribute technical information, application notes, source code, errata sheets, bug reports, and interim patches for Microchip systems software products. For each SIG, a moderator monitors, scans, and approves or disapproves files submitted to the SIG. No executable files are accepted from the user community in general to limit the spread of computer viruses.

#### Systems Information and Upgrade Hot Line

The Systems Information and Upgrade Line provides system users a listing of the latest versions of all of Microchip's development systems software products. Plus, this line provides information on how customers can receive any currently available upgrade kits.The Hot Line Numbers are:

1-800-755-2345 for U.S. and most of Canada, and

1-602-786-7302 for the rest of the world.

970301

**Trademarks:** The Microchip name, logo, PIC, PICSTART, PICMASTER and PRO MATE are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. *Flex*ROM, MPLAB and *fuzzy*LAB, are trademarks and SQTP is a service mark of Microchip in the U.S.A.

*fuzzy*TECH is a registered trademark of Inform Software Corporation. IBM, IBM PC-AT are registered trademarks of International Business Machines Corp. Pentium is a trademark of Intel Corporation. Windows is a trademark and MS-DOS, Microsoft Windows are registered trademarks of Microsoft Corporation. CompuServe is a registered trademark of CompuServe Incorporated.

All other trademarks mentioned herein are the property of their respective companies.