Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Detuns                     |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | · ·                                                                      |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | A/D 8x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c77-04i-l |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# FIGURE 4-4: PIC16C72 REGISTER FILE MAP

| File<br>Address   | 3                     |                     | File<br>Address |

|-------------------|-----------------------|---------------------|-----------------|

| 00h               | INDF <sup>(1)</sup>   | INDF <sup>(1)</sup> | 80h             |

| 01h               | TMR0                  | OPTION              | 81h             |

| 02h               | PCL                   | PCL                 |                 |

| 03h               | STATUS                | STATUS              |                 |

| 04h               | FSR                   | FSR                 |                 |

| 05h               | PORTA                 | TRISA               | 85h             |

| 06h               | PORTB                 | TRISB               | 86h             |

| 07h               | PORTC                 | TRISC               |                 |

| 08h               |                       |                     |                 |

| 09h               |                       |                     | 89h             |

| 0Ah               | PCLATH                | PCLATH              | 8Ah             |

| 0Bh               | INTCON                | INTCON              | 8Bh             |

| 0Ch               | PIR1                  | PIE1                | 8Ch             |

| 0Dh               |                       |                     | 8Dh             |

| 0Eh               | TMR1L                 | PCON                | 8Eh             |

| 0Fh               | TMR1H                 |                     | 8Fh             |

| 10h               | T1CON                 |                     | 90h             |

| 11h               | TMR2                  |                     | 91h             |

| 12h               | T2CON                 | PR2                 | 92h             |

| 13h               | SSPBUF                | SSPADD              | 93h             |

| 14h               | SSPCON                | SSPSTAT             |                 |

| 15h               | CCPR1L                |                     | 95h             |

| 16h               | CCPR1H                |                     | 96h             |

| 17h               | CCP1CON               |                     | 97h             |

| 18h               |                       |                     | 98h             |

| 19h               |                       |                     | 99h             |

| 1Ah               |                       |                     | 9Ah             |

| 1Bh               |                       |                     | 9Bh             |

| 1Ch               |                       |                     | 9Ch             |

| 1Dh               |                       |                     | 9Dh             |

| 1Eh               | ADRES                 |                     | 9Eh             |

| 1Fh               | ADCON0                | ADCON1              | 9Fh             |

| 20h               |                       |                     | A0h             |

|                   | General<br>Purpose    | General<br>Purpose  |                 |

|                   | Register              | Register            |                 |

|                   | U U                   |                     | BFh             |

|                   |                       |                     | C0h             |

|                   |                       |                     |                 |

| 1                 |                       |                     |                 |

|                   |                       |                     |                 |

| 7Fh               |                       |                     | FFh             |

|                   | Bank 0                | Bank 1              |                 |

|                   |                       |                     |                 |

|                   | nimplemented data     | a memory locations  | s, read as      |

| '0'.<br>Note 1: 1 | Not a physical regis  | stor                |                 |

|                   | tot a priysical regit | лот.                |                 |

|                   |                       |                     |                 |

### FIGURE 4-5: PIC16C73/73A/74/74A REGISTER FILE MAP

|                | REGIST                                                        | ER FILE MA                     | F               |

|----------------|---------------------------------------------------------------|--------------------------------|-----------------|

| File<br>Addres | SS                                                            | _                              | File<br>Address |

| 00h            | INDF <sup>(1)</sup>                                           | INDF <sup>(1)</sup>            | 80h             |

| 01h            | TMR0                                                          | OPTION                         |                 |

| 02h            | PCL                                                           | PCL                            | 82h             |

| 03h            | STATUS                                                        | STATUS                         | 83h             |

| 04h            | FSR                                                           | FSR                            |                 |

| 05h            | PORTA                                                         | TRISA                          | 85h             |

| 06h            | PORTB                                                         | TRISB                          | 86h             |

| 07h            | PORTC                                                         | TRISC                          |                 |

| 08h            | PORTD <sup>(2)</sup>                                          | TRISD <sup>(2)</sup>           |                 |

| 09h            | PORTE <sup>(2)</sup>                                          | TRISE <sup>(2)</sup>           | 89h             |

| 0Ah            | PCLATH                                                        | PCLATH                         | 8Ah             |

| 0Bh            | INTCON                                                        | INTCON                         | 8Bh             |

| 0Ch            | PIR1                                                          | PIE1                           | 8Ch             |

| 0Dh            | PIR2                                                          | PIE2                           | 8Dh             |

| 0Eh            | TMR1L                                                         | PCON                           | 8Eh             |

| 0Fh            | TMR1H                                                         |                                | 8Fh             |

| 10h            | T1CON                                                         |                                | 90h             |

| 11h            | TMR2                                                          |                                | 91h             |

| 12h            | T2CON                                                         | PR2                            |                 |

| 13h            | SSPBUF                                                        | SSPADD                         | 93h             |

| 14h            | SSPCON                                                        | SSPSTAT                        | 94h             |

| 15h            | CCPR1L                                                        |                                | 95h             |

| 16h            | CCPR1H                                                        |                                | 96h             |

| 17h            | CCP1CON                                                       |                                | 97h             |

| 18h            | RCSTA                                                         | TXSTA                          |                 |

| 19h            | TXREG                                                         | SPBRG                          | 99h             |

| 1Ah            | RCREG                                                         |                                | 9Ah             |

| 1Bh            | CCPR2L                                                        |                                | 9Bh             |

| 1Ch            | CCPR2H                                                        |                                | 9Ch             |

| 1Dh            | CCP2CON                                                       |                                | 9Dh             |

| 1Eh            | ADRES                                                         |                                | 9Eh             |

| 1Fh            | ADCON0                                                        | ADCON1                         | 9Fh             |

| 20h            |                                                               |                                | A0h             |

|                | General<br>Purpose<br>Register                                | General<br>Purpose<br>Register |                 |

| 7Fh            |                                                               |                                | FFh             |

|                | Bank 0                                                        | Bank 1                         |                 |

|                | Unimplemented da                                              | -                              | ons, read as    |

| Note 1:<br>2:  | Not a physical reg<br>These registers ar<br>mented on the PIC | e not physically               |                 |

|                |                                                               |                                |                 |

| Address                   | Name    | Bit 7                | Bit 6              | Bit 5          | Bit 4           | Bit 3          | Bit 2           | Bit 1       | Bit 0   | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(2) |

|---------------------------|---------|----------------------|--------------------|----------------|-----------------|----------------|-----------------|-------------|---------|--------------------------|-------------------------------------|

| Bank 0                    |         |                      |                    |                |                 |                |                 |             |         |                          |                                     |

| 00h <sup>(4)</sup>        | INDF    | Addressing           | egister)           | 0000 0000      | 0000 0000       |                |                 |             |         |                          |                                     |

| 01h                       | TMR0    | Timer0 mod           | lule's registe     |                | xxxx xxxx       | uuuu uuuu      |                 |             |         |                          |                                     |

| 02h <sup>(4)</sup>        | PCL     | Program Co           | ounter's (PC)      | Least Signif   | icant Byte      |                |                 |             |         | 0000 0000                | 0000 0000                           |

| 03h <sup>(4)</sup>        | STATUS  | IRP <sup>(7)</sup>   | RP1 <sup>(7)</sup> | RP0            | TO              | PD             | Z               | DC          | С       | 0001 1xxx                | 000q quuu                           |

| 04h <b>(4)</b>            | FSR     | Indirect data        | a memory ad        | dress pointe   | er              |                |                 |             | •       | XXXX XXXX                | uuuu uuuu                           |

| 05h                       | PORTA   | _                    | _                  | PORTA Dat      | a Latch when    | written: POR   | TA pins wher    | read        |         | 0x 0000                  | 0u 0000                             |

| 06h                       | PORTB   | PORTB Dat            | a Latch whe        | n written: PC  | ORTB pins whe   | n read         |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 07h                       | PORTC   | PORTC Dat            | ta Latch whe       | n written: PC  | DRTC pins whe   | en read        |                 |             |         | XXXX XXXX                | uuuu uuuu                           |

| 08h <sup>(5)</sup>        | PORTD   | PORTD Dat            | a Latch whe        | n written: PC  | ORTD pins whe   | en read        |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 09h <b>(5)</b>            | PORTE   | _                    | _                  | _              | _               | _              | RE2             | RE1         | RE0     | xxx                      | uuu                                 |

| 0Ah <b>(1,4)</b>          | PCLATH  | _                    | _                  | _              | Write Buffer fo | or the upper t | 5 bits of the I | Program Cou | unter   | 0 0000                   | 0 0000                              |

| 0Bh <b><sup>(4)</sup></b> | INTCON  | GIE                  | PEIE               | TOIE           | INTE            | RBIE           | T0IF            | INTF        | RBIF    | 0000 000x                | 0000 000u                           |

| 0Ch                       | PIR1    | PSPIF <sup>(3)</sup> | ADIF               | RCIF           | TXIF            | SSPIF          | CCP1IF          | TMR2IF      | TMR1IF  | 0000 0000                | 0000 0000                           |

| 0Dh                       | PIR2    | —                    | —                  | -              | -               | -              | —               | —           | CCP2IF  | 0                        | 0                                   |

| 0Eh                       | TMR1L   | Holding reg          | ister for the L    | east Signific  | ant Byte of the | e 16-bit TMR1  | l register      |             |         | xxxx xxxx                | uuuu uuuu                           |

| 0Fh                       | TMR1H   | Holding reg          | ister for the N    | lost Significa | ant Byte of the | 16-bit TMR1    | register        |             |         | XXXX XXXX                | uuuu uuuu                           |

| 10h                       | T1CON   | —                    | —                  | T1CKPS1        | T1CKPS0         | T1OSCEN        | <b>T1SYNC</b>   | TMR1CS      | TMR10N  | 00 0000                  | uu uuuu                             |

| 11h                       | TMR2    | Timer2 mod           | lule's registe     | r              |                 |                |                 |             |         | 0000 0000                | 0000 0000                           |

| 12h                       | T2CON   | —                    | TOUTPS3            | TOUTPS2        | TOUTPS1         | TOUTPS0        | TMR2ON          | T2CKPS1     | T2CKPS0 | -000 0000                | -000 0000                           |

| 13h                       | SSPBUF  | Synchronou           | is Serial Port     | Receive Bu     | ffer/Transmit R | egister        |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 14h                       | SSPCON  | WCOL                 | SSPOV              | SSPEN          | СКР             | SSPM3          | SSPM2           | SSPM1       | SSPM0   | 0000 0000                | 0000 0000                           |

| 15h                       | CCPR1L  | Capture/Co           | mpare/PWM          | Register1 (L   | _SB)            |                |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 16h                       | CCPR1H  | Capture/Co           | mpare/PWM          | Register1 (N   | MSB)            |                |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 17h                       | CCP1CON | —                    | —                  | CCP1X          | CCP1Y           | CCP1M3         | CCP1M2          | CCP1M1      | CCP1M0  | 00 0000                  | 00 0000                             |

| 18h                       | RCSTA   | SPEN                 | RX9                | SREN           | CREN            | —              | FERR            | OERR        | RX9D    | 0000 -00x                | 0000 -00x                           |

| 19h                       | TXREG   | USART Trar           | nsmit Data R       | egister        |                 |                |                 |             |         | 0000 0000                | 0000 0000                           |

| 1Ah                       | RCREG   | USART Red            | ceive Data R       | egister        |                 |                |                 |             |         | 0000 0000                | 0000 0000                           |

| 1Bh                       | CCPR2L  | Capture/Co           | mpare/PWM          | Register2 (L   | _SB)            |                |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 1Ch                       | CCPR2H  | Capture/Co           | mpare/PWM          | Register2 (N   | MSB)            |                |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 1Dh                       | CCP2CON | —                    | —                  | CCP2X          | CCP2Y           | CCP2M3         | CCP2M2          | CCP2M1      | CCP2M0  | 00 0000                  | 00 0000                             |

| 1Eh                       | ADRES   | A/D Result           | Register           |                |                 |                |                 |             |         | XXXX XXXX                | uuuu uuuu                           |

| 1Fh                       | ADCON0  | ADCS1                | ADCS0              | CHS2           | CHS1            | CHS0           | GO/DONE         | —           | ADON    | 0000 00-0                | 0000 00-0                           |

TABLE 4-2:

PIC16C73/73A/74/74A SPECIAL FUNCTION REGISTER SUMMARY

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A, always maintain these bits clear.

4: These registers can be addressed from either bank.

5: PORTD and PORTE are not physically implemented on the PIC16C73/73A, read as '0'.

6: Brown-out Reset is not implemented on the PIC16C73 or the PIC16C74, read as '0'.

7: The IRP and RP1 bits are reserved on the PIC16C73/73A/74/74A, always maintain these bits clear.

## TABLE 5-1: PORTA FUNCTIONS

| Name         | Bit# | Buffer | Function                                                                       |

|--------------|------|--------|--------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF                                           |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0                                |

|              |      |        | Output is open drain type                                                      |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input |

Legend: TTL = TTL input, ST = Schmitt Trigger input

# TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5     | Bit 4      | Bit 3      | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|--------|-------|-------|-----------|------------|------------|-------|-------|-------|--------------------------|---------------------------|

| 05h     | PORTA  | —     | _     | RA5       | RA4        | RA3        | RA2   | RA1   | RA0   | 0x 0000                  | 0u 0000                   |

| 85h     | TRISA  | —     | —     | PORTA Dat | a Directio | n Register |       |       | -     | 11 1111                  | 11 1111                   |

| 9Fh     | ADCON1 | —     |       | —         | _          | _          | PCFG2 | PCFG1 | PCFG0 | 000                      | 000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

# 5.6 <u>I/O Programming Considerations</u> Applicable Devices 72 73 73A 74 74A 76 77

### 5.6.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched to an output, the content of the data latch may now be unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-4 shows the effect of two sequential readmodify-write instructions on an I/O port.

### EXAMPLE 5-4: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT settings: PORTB<7:4> Inputs

; PORTB<3:0> Outputs

;PORTB<7:6> have external pull-ups and are

;not connected to other circuitry

| i |     |         |     |   |      |       |           |  |

|---|-----|---------|-----|---|------|-------|-----------|--|

| ; |     |         |     |   | PORT | latch | PORT pins |  |

| ; |     |         |     |   |      |       |           |  |

|   | BCF | PORTB,  | 7   | ; | 01pp | pppp  | 11pp pppp |  |

|   | BCF | PORTB,  | 6   | ; | 10pp | pppp  | llpp pppp |  |

|   | BSF | STATUS, | RP0 | ; |      |       |           |  |

|   | BCF | TRISB,  | 7   | ; | 10pp | pppp  | 11pp pppp |  |

|   | BCF | TRISB,  | 6   | ; | 10pp | pppp  | 10pp pppp |  |

| ; |     |         |     |   |      |       |           |  |

|   |     |         |     |   |      |       |           |  |

;Note that the user may have expected the ;pin values to be 00pp ppp. The 2nd BCF ;caused RB7 to be latched as the pin value ;(high).

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

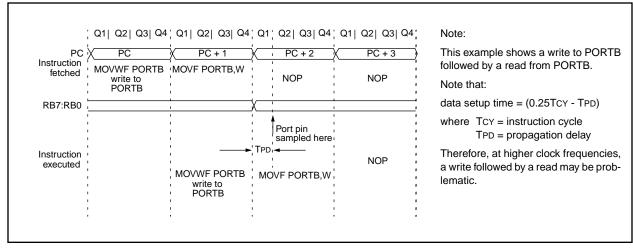

### 5.6.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-10). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/ O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

# FIGURE 5-10: SUCCESSIVE I/O OPERATION

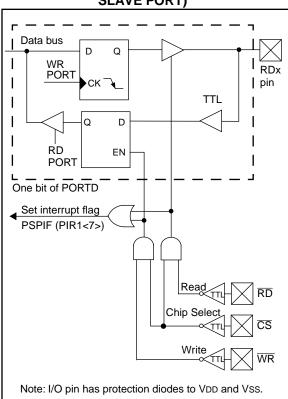

# 5.7 Parallel Slave Port Applicable Devices 72 73 73 74 74 76 77

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port when control bit PSPMODE (TRISE<4>) is set. In slave mode it is asynchronously readable and writable by the external world through  $\overline{RD}$  control input pin RE0/ $\overline{RD}$ /AN5 and  $\overline{WR}$  control input pin RE1/ $\overline{WR}$ /AN6.

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD/AN5 to be the RD input, RE1/ WR/AN6 to be the WR input and RE2/CS/AN7 to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set) and the A/D port configuration bits PCFG2:PCFG0 (ADCON1<2:0>) must be set, which will configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches, one for data-out (from the PIC16/17) and one for data input. The user writes 8-bit data to PORTD data latch and reads data from the port pin latch (note that they have the same address). In this mode, the TRISD register is ignored, since the microprocessor is controlling the direction of data flow.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$ lines are first detected low. When either the  $\overline{CS}$  or  $\overline{WR}$ lines become high (level triggered), then the Input Buffer Full status flag bit IBF (TRISE<7>) is set on the Q4 clock cycle, following the next Q2 cycle, to signal the write is complete (Figure 5-12). The interrupt flag bit PSPIF (PIR1<7>) is also set on the same Q4 clock cycle. IBF can only be cleared by reading the PORTD input latch. The input Buffer Overflow status flag bit IBOV (TRISE<5>) is set if a second write to the Parallel Slave Port is attempted when the previous byte has not been read out of the buffer.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The Output Buffer Full status flag bit OBF (TRISE<6>) is cleared immediately (Figure 5-13) indicating that the PORTD latch is waiting to be read by the external bus. When either the  $\overline{CS}$  or  $\overline{RD}$  pin becomes high (level triggered), the interrupt flag bit PSPIF is set on the Q4 clock cycle, following the next Q2 cycle, indicating that the read is complete. OBF remains low until data is written to PORTD by the user firmware.

When not in Parallel Slave Port mode, the IBF and OBF bits are held clear. However, if flag bit IBOV was previously set, it must be cleared in firmware.

An interrupt is generated and latched into flag bit PSPIF when a read or write operation is completed. PSPIF must be cleared by the user in firmware and the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

### FIGURE 5-11: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

NOTES:

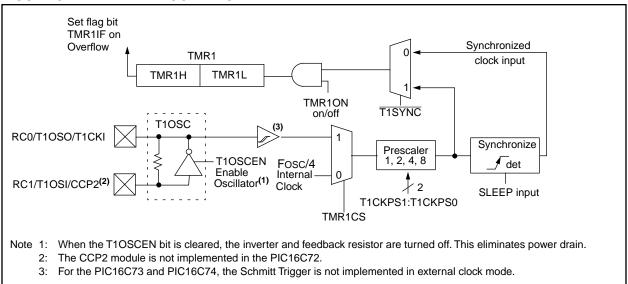

# 8.1 <u>Timer1 Operation in Timer Mode</u>

# Applicable Devices

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect since the internal clock is always in sync.

### 8.2 <u>Timer1 Operation in Synchronized</u> Counter Mode Applicable Devices 72 73 73A 74 74A 76 77

Counter mode is selected by setting bit TMR1CS. In this mode the timer increments on every rising edge of clock input on pin RC1/T1OSI/CCP2 when bit T1OSCEN is set or pin RC0/T1OSO/T1CKI when bit T1OSCEN is cleared.

If T1SYNC is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple-counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut off. The prescaler however will continue to increment.

### 8.2.1 EXTERNAL CLOCK INPUT TIMING FOR SYNCHRONIZED COUNTER MODE

When an external clock input is used for Timer1 in synchronized counter mode, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of TMR1 after synchronization.

When the prescaler is 1:1, the external clock input is the same as the prescaler output. The synchronization of T1CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T1CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the appropriate electrical specifications, parameters 45, 46, and 47.

When a prescaler other than 1:1 is used, the external clock input is divided by the asynchronous ripplecounter type prescaler so that the prescaler output is symmetrical. In order for the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for T1CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T1CKI high and low time is that they do not violate the minimum pulse width requirements of 10 ns). Refer to the appropriate electrical specifica-tions, parameters 40, 42, 45, 46, and 47.

# FIGURE 8-2: TIMER1 BLOCK DIAGRAM

### 11.4.4 MULTI-MASTER

The  $I^2C$  protocol allows a system to have more than one master. This is called multi-master. When two or more masters try to transfer data at the same time, arbitration and synchronization occur.

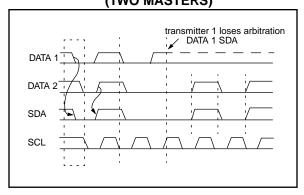

### 11.4.4.1 ARBITRATION

Arbitration takes place on the SDA line, while the SCL line is high. The master which transmits a high when the other master transmits a low loses arbitration (Figure 11-22), and turns off its data output stage. A master which lost arbitration can generate clock pulses until the end of the data byte where it lost arbitration. When the master devices are addressing the same device, arbitration continues into the data.

### FIGURE 11-22: MULTI-MASTER ARBITRATION (TWO MASTERS)

Masters that also incorporate the slave function, and have lost arbitration must immediately switch over to slave-receiver mode. This is because the winning master-transmitter may be addressing it.

Arbitration is not allowed between:

- A repeated START condition

- A STOP condition and a data bit

- A repeated START condition and a STOP condition

Care needs to be taken to ensure that these conditions do not occur.

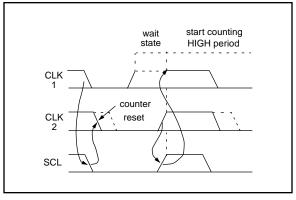

### 11.2.4.2 Clock Synchronization

Clock synchronization occurs after the devices have started arbitration. This is performed using a wired-AND connection to the SCL line. A high to low transition on the SCL line causes the concerned devices to start counting off their low period. Once a device clock has gone low, it will hold the SCL line low until its SCL high state is reached. The low to high transition of this clock may not change the state of the SCL line, if another device clock is still within its low period. The SCL line is held low by the device with the longest low period. Devices with shorter low periods enter a high wait-state, until the SCL line comes high. When the SCL line comes high, all devices start counting off their high periods. The first device to complete its high period will pull the SCL line low. The SCL line high time is determined by the device with the shortest high period, Figure 11-23.

### FIGURE 11-23: CLOCK SYNCHRONIZATION

TABLE 13-2: REGISTERS/BITS ASSOCIATED WITH A/D, PIC16C72

| Address | Name   | Bit 7   | Bit 6       | Bit 5 | Bit 4  | Bit 3      | Bit 2    | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|--------|---------|-------------|-------|--------|------------|----------|--------|--------|--------------------------|---------------------------|

| 0Bh,8Bh | INTCON | GIE     | PEIE        | TOIE  | INTE   | RBIE       | T0IF     | INTF   | RBIF   | 0000 000x                | 0000 000u                 |

| 0Ch     | PIR1   | —       | ADIF        | -     | —      | SSPIF      | CCP1IF   | TMR2IF | TMR1IF | -0 0000                  | -0 0000                   |

| 8Ch     | PIE1   | —       | ADIE        | -     | _      | SSPIE      | CCP1IE   | TMR2IE | TMR1IE | -0 0000                  | -0 0000                   |

| 1Eh     | ADRES  | A/D Res | sult Regist | ter   |        |            |          |        |        | xxxx xxxx                | uuuu uuuu                 |

| 1Fh     | ADCON0 | ADCS1   | ADCS0       | CHS2  | CHS1   | CHS0       | GO/DONE  | —      | ADON   | 0000 00-0                | 0000 00-0                 |

| 9Fh     | ADCON1 | —       | —           | _     | _      | _          | PCFG2    | PCFG1  | PCFG0  | 000                      | 000                       |

| 05h     | PORTA  | _       | _           | RA5   | RA4    | RA3        | RA2      | RA1    | RA0    | 0x 0000                  | 0u 0000                   |

| 85h     | TRISA  | _       |             | PORTA | Data D | irection F | Register |        |        | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

# PIC16C7X

| Register |    | Applicable Devices |     |    |     |    |    | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT<br>or<br>Interrupt |

|----------|----|--------------------|-----|----|-----|----|----|------------------------------------|--------------------------|------------------------------------|

| SSPADD   | 72 | 73                 | 73A | 74 | 74A | 76 | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                          |

| SSPSTAT  | 72 | 73                 | 73A | 74 | 74A | 76 | 77 | 00 0000                            | 00 0000                  | uu uuuu                            |

| TXSTA    | 72 | 73                 | 73A | 74 | 74A | 76 | 77 | 0000 -010                          | 0000 -010                | uuuu -uuu                          |

| SPBRG    | 72 | 73                 | 73A | 74 | 74A | 76 | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                          |

| ADCON1   | 72 | 73                 | 73A | 74 | 74A | 76 | 77 | 000                                | 000                      | uuu                                |

# TABLE 14-8: INITIALIZATION CONDITIONS FOR ALL REGISTERS (Cont.'d)

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 14-7 for reset value for specific condition.

# Applicable Devices 72 73 73A 74 74A 76 77

# 17.5 <u>Timing Diagrams and Specifications</u>

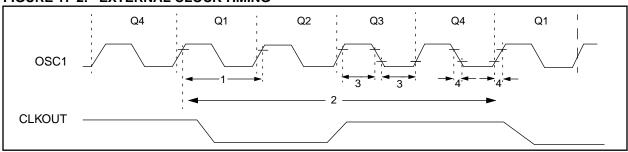

# FIGURE 17-2: EXTERNAL CLOCK TIMING

# TABLE 17-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                   | Min | Тур† | Max    | Units | Conditions         |

|------------------|-------|----------------------------------|-----|------|--------|-------|--------------------|

|                  | Fosc  | External CLKIN Frequency         | DC  | _    | 4      | MHz   | XT and RC osc mode |

|                  |       | (Note 1)                         | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|                  |       |                                  | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|                  |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|                  |       |                                  | DC  | _    | 200    | kHz   | LP osc mode        |

|                  |       | Oscillator Frequency             | DC  | _    | 4      | MHz   | RC osc mode        |

|                  |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode        |

|                  |       |                                  | 4   | _    | 20     | MHz   | HS osc mode        |

|                  |       |                                  | 5   | —    | 200    | kHz   | LP osc mode        |

| 1                | Tosc  | External CLKIN Period            | 250 | —    | —      | ns    | XT and RC osc mode |

|                  |       | (Note 1)                         | 250 | —    | —      | ns    | HS osc mode (-04)  |

|                  |       |                                  | 100 | _    | _      | ns    | HS osc mode (-10)  |

|                  |       |                                  | 50  | _    | _      | ns    | HS osc mode (-20)  |

|                  |       |                                  | 5   | _    | _      | μs    | LP osc mode        |

|                  |       | Oscillator Period                | 250 | _    | _      | ns    | RC osc mode        |

|                  |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode        |

|                  |       |                                  | 250 | _    | 250    | ns    | HS osc mode (-04)  |

|                  |       |                                  | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|                  |       |                                  | 50  | —    | 250    | ns    | HS osc mode (-20)  |

|                  |       |                                  | 5   | —    | _      | μs    | LP osc mode        |

| 2                | Тсү   | Instruction Cycle Time (Note 1)  | 200 | —    | DC     | ns    | TCY = 4/FOSC       |

| 3                | TosL, | External Clock in (OSC1) High or | 100 | _    | —      | ns    | XT oscillator      |

|                  | TosH  | Low Time                         | 2.5 | _    | _      | μs    | LP oscillator      |

|                  |       |                                  | 15  | _    | _      | ns    | HS oscillator      |

| 4                | TosR, | External Clock in (OSC1) Rise or | _   | _    | 25     | ns    | XT oscillator      |

|                  | TosF  | Fall Time                        | _   | _    | 50     | ns    | LP oscillator      |

|                  |       |                                  |     | _    | 15     | ns    | HS oscillator      |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

Applicable Devices 72 73 73A 74 74A 76 77

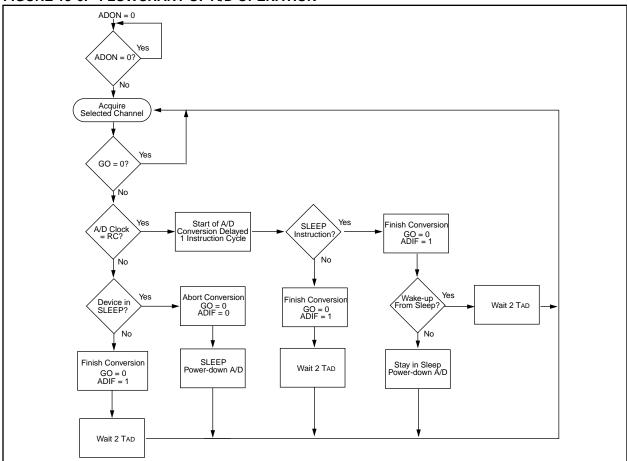

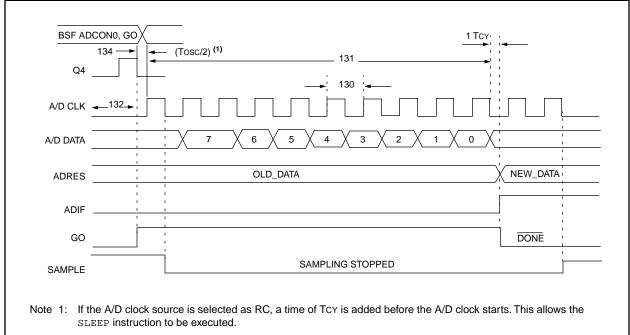

# FIGURE 17-11: A/D CONVERSION TIMING

# TABLE 17-11: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym  | Characteristic                      |                              | Min    | Тур†     | Мах | Units | Conditions                                                                                                                                                                                                                   |

|--------------|------|-------------------------------------|------------------------------|--------|----------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D clock period                    | PIC16 <b>C</b> 72            | 1.6    | _        | _   | μs    | Tosc based, VREF ≥ 3.0V                                                                                                                                                                                                      |

|              |      |                                     | PIC16 <b>LC</b> 72           | 2.0    | —        | —   | μs    | Tosc based, VREF full range                                                                                                                                                                                                  |

|              |      |                                     | PIC16 <b>C</b> 72            | 2.0    | 4.0      | 6.0 | μs    | A/D RC Mode                                                                                                                                                                                                                  |

|              |      |                                     | PIC16 <b>LC</b> 72           | 3.0    | 6.0      | 9.0 | μs    | A/D RC Mode                                                                                                                                                                                                                  |

| 131          | TCNV | Conversion time (not time) (Note 1) | including S/H                | _      | 9.5      | —   | TAD   |                                                                                                                                                                                                                              |

| 132          | TACQ | Acquisition time                    |                              | Note 2 | 20       | _   | μs    |                                                                                                                                                                                                                              |

|              |      |                                     |                              | 5*     | _        | _   | μs    | The minimum time is the amplifier<br>settling time. This may be used if<br>the "new" input voltage has not<br>changed by more than 1 LSb (i.e.<br>20.0 mV @ 5.12V) from the last<br>sampled voltage (as stated on<br>CHOLD). |

| 134          | TGO  | Q4 to A/D clock start               |                              | _      | Tosc/2 § | _   | _     | If the A/D clock source is selected<br>as RC, a time of TCY is added<br>before the A/D clock starts. This<br>allows the SLEEP instruction to be<br>executed.                                                                 |

| 135          | Tswc | Switching from conve                | $rt \rightarrow sample time$ | 1.5 §  |          | _   | TAD   |                                                                                                                                                                                                                              |

These parameters are characterized but not tested.

t Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 13.1 for min conditions.

Applicable Devices

72

73

73A

74

76

77

# FIGURE 18-13: A/D CONVERSION TIMING

# TABLE 18-14: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym  | Characteristic                       |                       | Min    | Тур†     | Мах | Units | Conditions                                                                                                                                                                                                                 |

|--------------|------|--------------------------------------|-----------------------|--------|----------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D clock period                     | PIC16 <b>C</b> 73/74  | 1.6    | —        |     | μs    | Tosc based, VREF ≥ 3.0V                                                                                                                                                                                                    |

|              |      |                                      | PIC16 <b>LC</b> 73/74 | 2.0    | —        |     | μs    | Tosc based, VREF full range                                                                                                                                                                                                |

|              |      |                                      | PIC16 <b>C</b> 73/74  | 2.0    | 4.0      | 6.0 | μs    | A/D RC Mode                                                                                                                                                                                                                |

|              |      |                                      | PIC16 <b>LC</b> 73/74 | 3.0    | 6.0      | 9.0 | μs    | A/D RC Mode                                                                                                                                                                                                                |

| 131          | TCNV | Conversion time (not inc<br>(Note 1) | luding S/H time)      | —      | 9.5      | —   | TAD   |                                                                                                                                                                                                                            |

| 132          | TACQ | Acquisition time                     |                       | Note 2 | 20       | _   | μs    |                                                                                                                                                                                                                            |

|              |      |                                      |                       | 5*     | _        | _   | μs    | The minimum time is the amplifier<br>settling time. This may be used if<br>the "new" input voltage has not<br>changed by more than 1 LSb (i.e.<br>20 mV @ 5.12V) from the last<br>sampled voltage (as stated on<br>CHOLD). |

| 134          | TGO  | Q4 to A/D clock start                |                       |        | Tosc/2 § | _   | _     | If the A/D clock source is selected<br>as RC, a time of TCY is added<br>before the A/D clock starts. This<br>allows the SLEEP instruction to be<br>executed.                                                               |

| 135          | Tswc | Switching from convert               | → sample time         | 1.5 §  | _        | _   | TAD   |                                                                                                                                                                                                                            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 13.1 for min conditions.

Applicable Devices 72 73 73A 74 74A 76 77

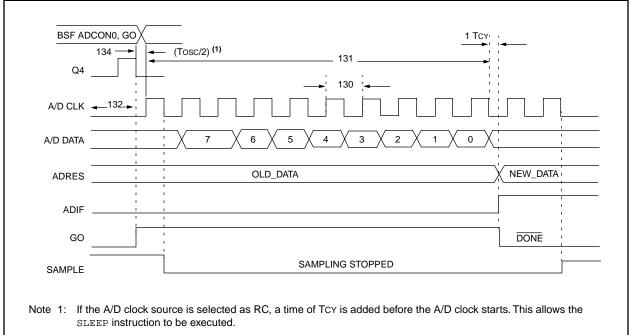

# FIGURE 19-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

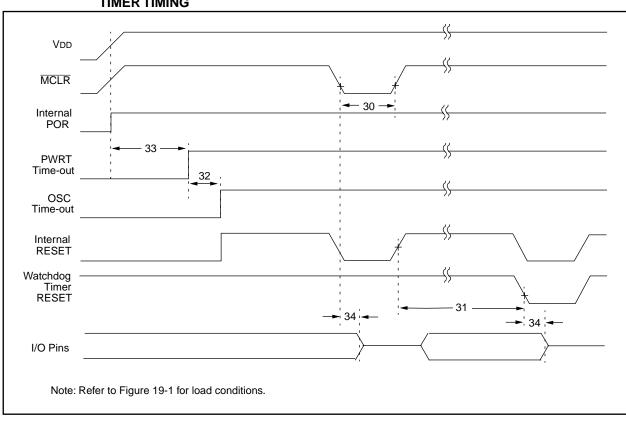

### FIGURE 19-5: BROWN-OUT RESET TIMING

# TABLE 19-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†     | Max | Units | Conditions                |

|------------------|-------|--------------------------------------------------------|-----|----------|-----|-------|---------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                 | 2   | _        | _   | μs    | VDD = 5V, -40°C to +125°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +125°C |

| 32               | Tost  | Oscillation Start-up Timer Period                      | —   | 1024Tosc | _   | —     | Tosc = OSC1 period        |

| 33*              | Tpwrt | Power up Timer Period                                  | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +125°C |

| 34               | Tioz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | _   | _        | 2.1 | μs    |                           |

| 35               | TBOR  | Brown-out Reset pulse width                            | 100 |          | _   | μs    | $VDD \le BVDD$ (D005)     |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16C7X

Applicable Devices 72 73 73A 74 74A 76 77

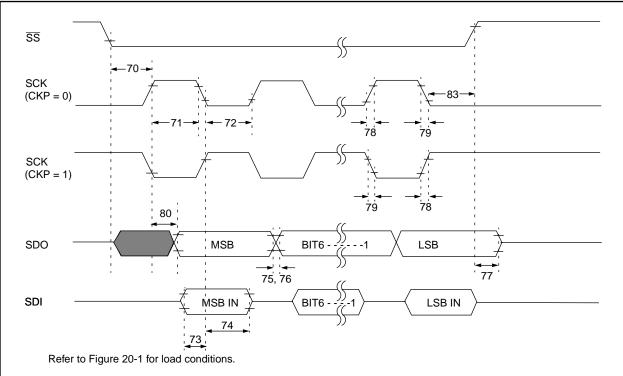

# FIGURE 20-11: SPI SLAVE MODE TIMING (CKE = 0)

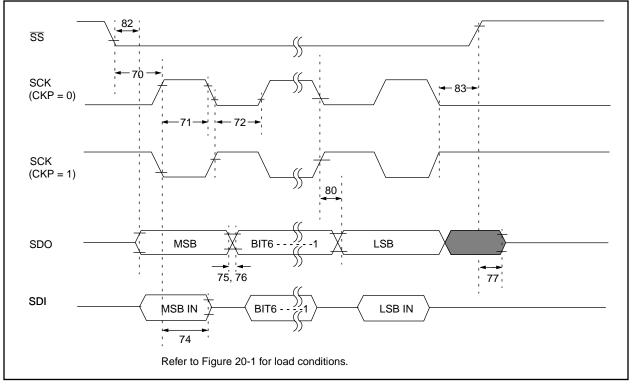

# FIGURE 20-12: SPI SLAVE MODE TIMING (CKE = 1)

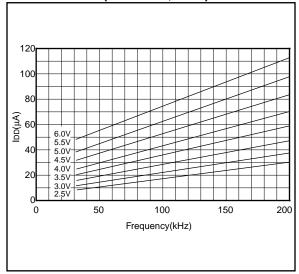

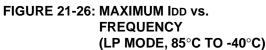

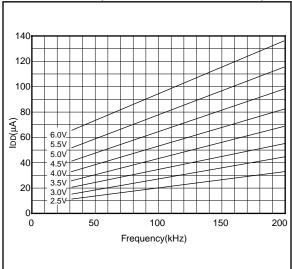

### FIGURE 21-25: TYPICAL IDD vs. FREQUENCY (LP MODE, 25°C)

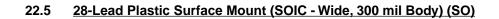

|        | Package Group: Plastic SOIC (SO) |             |         |        |            |         |  |  |  |

|--------|----------------------------------|-------------|---------|--------|------------|---------|--|--|--|

|        |                                  | Millimeters |         | Inches |            |         |  |  |  |

| Symbol | Min                              | Max         | Notes   | Min    | Max        | Notes   |  |  |  |

| α      | 0°                               | <b>8</b> °  |         | 0°     | <b>8</b> ° |         |  |  |  |

| А      | 2.362                            | 2.642       |         | 0.093  | 0.104      |         |  |  |  |

| A1     | 0.101                            | 0.300       |         | 0.004  | 0.012      |         |  |  |  |

| В      | 0.355                            | 0.483       |         | 0.014  | 0.019      |         |  |  |  |

| С      | 0.241                            | 0.318       |         | 0.009  | 0.013      |         |  |  |  |

| D      | 17.703                           | 18.085      |         | 0.697  | 0.712      |         |  |  |  |

| E      | 7.416                            | 7.595       |         | 0.292  | 0.299      |         |  |  |  |

| е      | 1.270                            | 1.270       | Typical | 0.050  | 0.050      | Typical |  |  |  |

| Н      | 10.007                           | 10.643      |         | 0.394  | 0.419      |         |  |  |  |

| h      | 0.381                            | 0.762       |         | 0.015  | 0.030      |         |  |  |  |

| L      | 0.406                            | 1.143       |         | 0.016  | 0.045      |         |  |  |  |

| Ν      | 28                               | 28          |         | 28     | 28         |         |  |  |  |

| CP     | -                                | 0.102       |         | —      | 0.004      |         |  |  |  |

## E.5 PIC16C55X Family of Devices

|            |                                      | PIC16C554                           | PIC16C556 <sup>(1)</sup>            | PIC16C558                           |

|------------|--------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| Clock      | Maximum Frequency of Operation (MHz) | 20                                  | 20                                  | 20                                  |

| lemory     | EPROM Program Memory (x14 words)     | 512                                 | 1K                                  | 2K                                  |

|            | Data Memory (bytes)                  | 80                                  | 80                                  | 128                                 |

|            | Timer Module(s)                      | TMR0                                | TMR0                                | TMR0                                |

| eripherals | Comparators(s)                       | —                                   | —                                   | —                                   |

|            | Internal Reference Voltage           | —                                   | —                                   | —                                   |

| eatures    | Interrupt Sources                    | 3                                   | 3                                   | 3                                   |

|            | I/O Pins                             | 13                                  | 13                                  | 13                                  |

|            | Voltage Range (Volts)                | 2.5-6.0                             | 2.5-6.0                             | 2.5-6.0                             |

|            | Brown-out Reset                      | —                                   | —                                   | —                                   |

|            | Packages                             | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C5XX Family devices use serial programming with clock pin RB6 and data pin RB7. Note 1: Please contact your local Microchip sales office for availability of these devices.

# E.6 PIC16C62X and PIC16C64X Family of Devices

|             |                                         | PIC16C620                           | PIC16C621                           | PIC16C622                           | PIC16C642                                 | PIC16C662                                                 |

|-------------|-----------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------------|-----------------------------------------------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz) | 20                                  | 20                                  | 20                                  | 20                                        | 20                                                        |

| Memory      | EPROM Program Memory<br>(x14 words)     | 512                                 | 1K                                  | 2К                                  | 4K                                        | 4K                                                        |

|             | Data Memory (bytes)                     | 80                                  | 80                                  | 128                                 | 176                                       | 176                                                       |

|             | Timer Module(s)                         | TMR0                                | TMR0                                | TMR0                                | TMR0                                      | TMR0                                                      |

| Peripherals | Comparators(s)                          | 2                                   | 2                                   | 2                                   | 2                                         | 2                                                         |

|             | Internal Reference Voltage              | Yes                                 | Yes                                 | Yes                                 | Yes                                       | Yes                                                       |

|             | Interrupt Sources                       | 4                                   | 4                                   | 4                                   | 4                                         | 5                                                         |

|             | I/O Pins                                | 13                                  | 13                                  | 13                                  | 22                                        | 33                                                        |

|             | Voltage Range (Volts)                   | 2.5-6.0                             | 2.5-6.0                             | 2.5-6.0                             | 3.0-6.0                                   | 3.0-6.0                                                   |

|             | Brown-out Reset                         | Yes                                 | Yes                                 | Yes                                 | Yes                                       | Yes                                                       |

| Features    | Packages                                | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin PDIP,<br>SOIC,<br>Windowed<br>CDIP | 40-pin PDIP,<br>Windowed<br>CDIP;<br>44-pin PLCC,<br>MQFP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high

I/O current capability. All PIC16C62X and PIC16C64X Family devices use serial programming with clock pin RB6 and data pin RB7.

### **ON-LINE SUPPORT**

Microchip provides two methods of on-line support. These are the Microchip BBS and the Microchip World Wide Web (WWW) site.

Use Microchip's Bulletin Board Service (BBS) to get current information and help about Microchip products. Microchip provides the BBS communication channel for you to use in extending your technical staff with microcontroller and memory experts.

To provide you with the most responsive service possible, the Microchip systems team monitors the BBS, posts the latest component data and software tool updates, provides technical help and embedded systems insights, and discusses how Microchip products provide project solutions.

The web site, like the BBS, is used by Microchip as a means to make files and information easily available to customers. To view the site, the user must have access to the Internet and a web browser, such as Netscape or Microsoft Explorer. Files are also available for FTP download from our FTP site.

### Connecting to the Microchip Internet Web Site

The Microchip web site is available by using your favorite Internet browser to attach to:

### www.microchip.com

The file transfer site is available by using an FTP service to connect to:

### ftp://ftp.futureone.com/pub/microchip

The web site and file transfer site provide a variety of services. Users may download files for the latest Development Tools, Data Sheets, Application Notes, User's Guides, Articles and Sample Programs. A variety of Microchip specific business information is also available, including listings of Microchip sales offices, distributors and factory representatives. Other data available for consideration is:

- Latest Microchip Press Releases

- Technical Support Section with Frequently Asked

Questions

- Design Tips

- Device Errata

- Job Postings

- · Microchip Consultant Program Member Listing

- Links to other useful web sites related to Microchip Products

### **Connecting to the Microchip BBS**

Connect worldwide to the Microchip BBS using either the Internet or the CompuServe<sup>®</sup> communications network.

### Internet:

You can telnet or ftp to the Microchip BBS at the address: mchipbbs.microchip.com

### CompuServe Communications Network:

When using the BBS via the Compuserve Network, in most cases, a local call is your only expense. The Microchip BBS connection does not use CompuServe membership services, therefore you do not need CompuServe membership to join Microchip's BBS. There is no charge for connecting to the Microchip BBS. The procedure to connect will vary slightly from country to country. Please check with your local CompuServe agent for details if you have a problem. CompuServe service allow multiple users various baud rates depending on the local point of access.

The following connect procedure applies in most locations.

- 1. Set your modem to 8-bit, No parity, and One stop (8N1). This is not the normal CompuServe setting which is 7E1.

- 2. Dial your local CompuServe access number.

- 3. Depress the **<Enter>** key and a garbage string will appear because CompuServe is expecting a 7E1 setting.

- Type +, depress the <Enter> key and "Host Name:" will appear.

- 5. Type MCHIPBBS, depress the **<Enter>** key and you will be connected to the Microchip BBS.

In the United States, to find the CompuServe phone number closest to you, set your modem to 7E1 and dial (800) 848-4480 for 300-2400 baud or (800) 331-7166 for 9600-14400 baud connection. After the system responds with "Host Name:", type NETWORK, depress the **<Enter>** key and follow CompuServe's directions.

For voice information (or calling from overseas), you may call (614) 723-1550 for your local CompuServe number.

Microchip regularly uses the Microchip BBS to distribute technical information, application notes, source code, errata sheets, bug reports, and interim patches for Microchip systems software products. For each SIG, a moderator monitors, scans, and approves or disapproves files submitted to the SIG. No executable files are accepted from the user community in general to limit the spread of computer viruses.

### Systems Information and Upgrade Hot Line

The Systems Information and Upgrade Line provides system users a listing of the latest versions of all of Microchip's development systems software products. Plus, this line provides information on how customers can receive any currently available upgrade kits.The Hot Line Numbers are:

1-800-755-2345 for U.S. and most of Canada, and

1-602-786-7302 for the rest of the world.

970301

**Trademarks:** The Microchip name, logo, PIC, PICSTART, PICMASTER and PRO MATE are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. *Flex*ROM, MPLAB and *fuzzy*LAB, are trademarks and SQTP is a service mark of Microchip in the U.S.A.

*fuzzy*TECH is a registered trademark of Inform Software Corporation. IBM, IBM PC-AT are registered trademarks of International Business Machines Corp. Pentium is a trademark of Intel Corporation. Windows is a trademark and MS-DOS, Microsoft Windows are registered trademarks of Microsoft Corporation. CompuServe is a registered trademark of CompuServe Incorporated.

All other trademarks mentioned herein are the property of their respective companies.

# WORLDWIDE SALES AND SERVICE

### AMERICAS

**Corporate Office** 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: 480-792-7627 Web Address: http://www.microchip.com

#### **Rocky Mountain**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7966 Fax: 480-792-7456

#### Atlanta

500 Sugar Mill Road, Suite 200B Atlanta, GA 30350 Tel: 770-640-0034 Fax: 770-640-0307

#### Boston

2 Lan Drive, Suite 120 Westford, MA 01886 Tel: 978-692-3848 Fax: 978-692-3821

### Chicago

333 Pierce Road, Suite 180 Itasca, IL 60143 Tel: 630-285-0071 Fax: 630-285-0075

Dallas

4570 Westgrove Drive, Suite 160 Addison, TX 75001 Tel: 972-818-7423 Fax: 972-818-2924

Detroit Tri-Atria Office Building

32255 Northwestern Highway, Suite 190 Farmington Hills, MI 48334 Tel: 248-538-2250 Fax: 248-538-2260 Kokomo

# 2767 S. Albright Road

Kokomo, Indiana 46902 Tel: 765-864-8360 Fax: 765-864-8387 Los Angeles

18201 Von Karman, Suite 1090 Irvine, CA 92612

Tel: 949-263-1888 Fax: 949-263-1338 New York

150 Motor Parkway, Suite 202 Hauppauge, NY 11788 Tel: 631-273-5305 Fax: 631-273-5335 San Jose

Microchip Technology Inc. 2107 North First Street, Suite 590 San Jose, CA 95131 Tel: 408-436-7950 Fax: 408-436-7955

Toronto

6285 Northam Drive, Suite 108 Mississauga, Ontario L4V 1X5, Canada Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

Australia

Microchip Technology Australia Pty Ltd Suite 22, 41 Rawson Street Epping 2121, NSW Australia

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755 China - Beijing

Microchip Technology Consulting (Shanghai) Co., Ltd., Beijing Liaison Office Unit 915 Bei Hai Wan Tai Bldg. No. 6 Chaoyangmen Beidajie Beijing, 100027, No. China Tel: 86-10-85282100 Fax: 86-10-85282104

#### China - Chengdu

Microchip Technology Consulting (Shanghai) Co., Ltd., Chengdu Liaison Office Rm. 2401, 24th Floor, Ming Xing Financial Tower No. 88 TIDU Street Chengdu 610016, China Tel: 86-28-6766200 Fax: 86-28-6766599

### China - Fuzhou

Microchip Technology Consulting (Shanghai) Co., Ltd., Fuzhou Liaison Office Unit 28F, World Trade Plaza No. 71 Wusi Road Fuzhou 350001, China Tel: 86-591-7503506 Fax: 86-591-7503521 China - Shanghai

Microchip Technology Consulting (Shanghai) Co., Ltd. Room 701, Bldg. B Far East International Plaza No. 317 Xian Xia Road Shanghai, 200051 Tel: 86-21-6275-5700 Fax: 86-21-6275-5060

#### China - Shenzhen

Microchip Technology Consulting (Shanghai) Co., Ltd., Shenzhen Liaison Office Rm. 1315, 13/F, Shenzhen Kerry Centre, Renminnan Lu Shenzhen 518001, China Tel: 86-755-2350361 Fax: 86-755-2366086 Hong Kong Microchip Technology Hongkong Ltd. Unit 901-6, Tower 2, Metroplaza

223 Hing Fong Road Kwai Fong, N.T., Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

### India

Microchip Technology Inc. India Liaison Office **Divvasree Chambers** 1 Floor, Wing A (A3/A4) No. 11, O'Shaugnessey Road Bangalore, 560 025, India Tel: 91-80-2290061 Fax: 91-80-2290062

### Japan

Microchip Technology Japan K.K. Benex S-1 6F 3-18-20, Shinyokohama Kohoku-Ku, Yokohama-shi Kanagawa, 222-0033, Japan Tel: 81-45-471- 6166 Fax: 81-45-471-6122 Korea Microchip Technology Korea 168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku Seoul, Korea 135-882 Tel: 82-2-554-7200 Fax: 82-2-558-5934 Singapore Microchip Technology Singapore Pte Ltd. 200 Middle Road #07-02 Prime Centre Singapore, 188980 Tel: 65-334-8870 Fax: 65-334-8850 Taiwan Microchip Technology Taiwan 11F-3, No. 207 Tung Hua North Road Taipei, 105, Taiwan Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

### EUROPE

Denmark

Microchip Technology Nordic ApS **Regus Business Centre** Lautrup hoj 1-3 Ballerup DK-2750 Denmark Tel: 45 4420 9895 Fax: 45 4420 9910 France Microchip Technology SARL Parc d'Activite du Moulin de Massy 43 Rue du Saule Trapu Batiment A - ler Etage 91300 Massy, France Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79 Germany Microchip Technology GmbH

Gustav-Heinemann Ring 125 D-81739 Munich, Germany Tel: 49-89-627-144 0 Fax: 49-89-627-144-44 Italy

Microchip Technology SRL Centro Direzionale Colleoni Palazzo Taurus 1 V. Le Colleoni 1 20041 Agrate Brianza Milan, Italy Tel: 39-039-65791-1 Fax: 39-039-6899883

#### United Kinadom

Arizona Microchip Technology Ltd. 505 Eskdale Road Winnersh Triangle Wokingham Berkshire, England RG41 5TU Tel: 44 118 921 5869 Fax: 44-118 921-5820

01/18/02