Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 10MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 14KB (8K x 14)                                                          |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 368 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                 |

| Data Converters            | A/D 8x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c77-10-l |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 GENERAL DESCRIPTION

The PIC16C7X is a family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with integrated analog-to-digital (A/D) converters, in the PIC16CXX mid-range family.

All PIC16/17 microcontrollers employ an advanced RISC architecture. The PIC16CXX microcontroller family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches which require two cycles. A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The **PIC16C72** has 128 bytes of RAM and 22 I/O pins. In addition several peripheral features are available including: three timer/counters, one Capture/Compare/ PWM module and one serial port. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. Also a 5-channel high-speed 8-bit A/D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The PIC16C73/73A devices have 192 bytes of RAM, while the PIC16C76 has 368 byes of RAM. Each device has 22 I/O pins. In addition, several peripheral features are available including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. The Universal Syn-Asynchronous Receiver chronous Transmitter (USART) is also known as the Serial Communications Interface or SCI. Also a 5-channel high-speed 8-bit A/ D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The **PIC16C74/74A** devices have 192 bytes of RAM, while the **PIC16C77** has 368 bytes of RAM. Each device has 33 I/O pins. In addition several peripheral features are available including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. The Universal Synchronous Asynchronous Receiver Transmitter (USART) is also known as the Serial Communications Interface or SCI. An 8-bit Parallel Slave Port is provided. Also an 8-channel high-speed

8-bit A/D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The PIC16C7X family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) feature provides a power saving mode. The user can wake up the chip from SLEEP through several external and internal interrupts and resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lockup.

A UV erasable CERDIP packaged version is ideal for code development while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume.

The PIC16C7X family fits perfectly in applications ranging from security and remote sensors to appliance control and automotive. The EPROM technology makes customization of application programs (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16C7X very versatile even in areas where no microcontroller use has been considered before (e.g. timer functions, serial communication, capture and compare, PWM functions and coprocessor applications).

## 1.1 Family and Upward Compatibility

Users familiar with the PIC16C5X microcontroller family will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for the PIC16C5X can be easily ported to the PIC16CXX family of devices (Appendix B).

## 1.2 Development Support

PIC16C7X devices are supported by the complete line of Microchip Development tools.

Please refer to Section 16.0 for more details about Microchip's development tools.

| Address              | Name    | Bit 7                | Bit 6           | Bit 5          | Bit 4           | Bit 3         | Bit 2           | Bit 1         | Bit 0    | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(2) |

|----------------------|---------|----------------------|-----------------|----------------|-----------------|---------------|-----------------|---------------|----------|--------------------------|-------------------------------------|

| Bank 0               | ·       | ·                    |                 |                |                 |               |                 |               |          |                          |                                     |

| 00h <sup>(4)</sup>   | INDF    | Addressing           | this location   | uses conter    | ts of FSR to a  | ddress data r | nemory (not     | a physical re | egister) | 0000 0000                | 0000 0000                           |

| 01h                  | TMR0    | Timer0 mod           | lule's registe  | r              |                 |               |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 02h <sup>(4)</sup>   | PCL     | Program Co           | ounter's (PC)   | Least Signif   | icant Byte      |               |                 |               |          | 0000 0000                | 0000 0000                           |

| 03h <sup>(4)</sup>   | STATUS  | IRP                  | RP1             | RP0            | TO              | PD            | Z               | DC            | С        | 0001 1xxx                | 000q quuu                           |

| 04h <b>(4)</b>       | FSR     | Indirect data        | a memory ac     | dress pointe   | er              | 1             | I               | I             | 1        | xxxx xxxx                | uuuu uuuu                           |

| 05h                  | PORTA   | _                    | _               | PORTA Dat      | a Latch when    | written: POR  | TA pins wher    | read          |          | 0x 0000                  | 0u 0000                             |

| 06h                  | PORTB   | PORTB Dat            | a Latch whe     | n written: PC  | ORTB pins whe   | n read        |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 07h                  | PORTC   | PORTC Dat            | ta Latch whe    | n written: PC  | DRTC pins whe   | en read       |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 08h <sup>(5)</sup>   | PORTD   | PORTD Dat            | ta Latch whe    | n written: PC  | ORTD pins whe   | en read       |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 09h <sup>(5)</sup>   | PORTE   | —                    | _               | _              | _               | _             | RE2             | RE1           | RE0      | xxx                      | uuu                                 |

| 0Ah <sup>(1,4)</sup> | PCLATH  | —                    | _               | _              | Write Buffer fo | or the upper  | 5 bits of the I | Program Cou   | unter    | 0 0000                   | 0 0000                              |

| 0Bh <b>(4)</b>       | INTCON  | GIE                  | PEIE            | TOIE           | INTE            | RBIE          | TOIF            | INTF          | RBIF     | 0000 000x                | 0000 000u                           |

| 0Ch                  | PIR1    | PSPIF <sup>(3)</sup> | ADIF            | RCIF           | TXIF            | SSPIF         | CCP1IF          | TMR2IF        | TMR1IF   | 0000 0000                | 0000 0000                           |

| 0Dh                  | PIR2    | —                    | _               | _              | -               | _             | —               | _             | CCP2IF   | 0                        | 0                                   |

| 0Eh                  | TMR1L   | Holding reg          | ister for the l | _east Signific | ant Byte of the | e 16-bit TMR  | 1 register      |               | •        | xxxx xxxx                | uuuu uuuu                           |

| 0Fh                  | TMR1H   | Holding reg          | ister for the I | Most Signific  | ant Byte of the | 16-bit TMR1   | register        |               |          | xxxx xxxx                | uuuu uuuu                           |

| 10h                  | T1CON   | _                    | _               | T1CKPS1        | T1CKPS0         | T1OSCEN       | T1SYNC          | TMR1CS        | TMR10N   | 00 0000                  | uu uuuu                             |

| 11h                  | TMR2    | Timer2 mod           | lule's registe  | r              |                 | •             |                 |               |          | 0000 0000                | 0000 0000                           |

| 12h                  | T2CON   | —                    | TOUTPS3         | TOUTPS2        | TOUTPS1         | TOUTPS0       | TMR2ON          | T2CKPS1       | T2CKPS0  | -000 0000                | -000 0000                           |

| 13h                  | SSPBUF  | Synchronou           | s Serial Por    | t Receive Bu   | ffer/Transmit R | egister       |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 14h                  | SSPCON  | WCOL                 | SSPOV           | SSPEN          | СКР             | SSPM3         | SSPM2           | SSPM1         | SSPM0    | 0000 0000                | 0000 0000                           |

| 15h                  | CCPR1L  | Capture/Co           | mpare/PWM       | Register1 (I   | _SB)            |               |                 |               |          | XXXX XXXX                | uuuu uuuu                           |

| 16h                  | CCPR1H  | Capture/Co           | mpare/PWM       | Register1 (I   | MSB)            |               |                 |               |          | XXXX XXXX                | uuuu uuuu                           |

| 17h                  | CCP1CON | —                    | _               | CCP1X          | CCP1Y           | CCP1M3        | CCP1M2          | CCP1M1        | CCP1M0   | 00 0000                  | 00 0000                             |

| 18h                  | RCSTA   | SPEN                 | RX9             | SREN           | CREN            | _             | FERR            | OERR          | RX9D     | 0000 -00x                | 0000 -00x                           |

| 19h                  | TXREG   | USART Trai           | nsmit Data R    | egister        |                 |               |                 |               |          | 0000 0000                | 0000 0000                           |

| 1Ah                  | RCREG   | USART Red            | ceive Data R    | egister        |                 |               |                 |               |          | 0000 0000                | 0000 0000                           |

| 1Bh                  | CCPR2L  | Capture/Co           | mpare/PWM       | Register2 (I   | _SB)            |               |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 1Ch                  | CCPR2H  | Capture/Co           | mpare/PWM       | Register2 (I   | MSB)            |               |                 |               |          | XXXX XXXX                | uuuu uuuu                           |

| 1Dh                  | CCP2CON | —                    | _               | CCP2X          | CCP2Y           | CCP2M3        | CCP2M2          | CCP2M1        | CCP2M0   | 00 0000                  | 00 0000                             |

| 1Eh                  | ADRES   | A/D Result           | Register        |                |                 |               |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 1Fh                  | ADCON0  | ADCS1                | ADCS0           | CHS2           | CHS1            | CHS0          | GO/DONE         | —             | ADON     | 0000 00-0                | 0000 00-0                           |

TABLE 4-3: PIC16C76/77 SPECIAL FUNCTION REGISTER SUMMARY

$\label{eq:legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.$  Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the PIC16C76, always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD and PORTE are not physically implemented on the PIC16C76, read as '0'.

NOTES:

#### FIGURE 9-2: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

| U-0      | R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0                                                                                                     |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| <u> </u> | TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0 R = Readable bit                                                                 |  |

| bit7     | bit0<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset                                           |  |

| bit 7:   | Unimplemented: Read as '0'                                                                                                              |  |

| bit 6-3: | TOUTPS3:TOUTPS0: Timer2 Output Postscale Select bits<br>0000 = 1:1 Postscale<br>0001 = 1:2 Postscale<br>•<br>•<br>1111 = 1:16 Postscale |  |

| bit 2:   | TMR2ON: Timer2 On bit<br>1 = Timer2 is on<br>0 = Timer2 is off                                                                          |  |

| bit 1-0: | <b>T2CKPS1:T2CKPS0</b> : Timer2 Clock Prescale Select bits<br>00 = Prescaler is 1<br>01 = Prescaler is 4<br>1x = Prescaler is 16        |  |

#### **TABLE 9-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER**

| Address               | Name   | Bit 7                  | Bit 6          | Bit 5               | Bit 4               | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|-----------------------|--------|------------------------|----------------|---------------------|---------------------|---------|--------|---------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                    | PEIE           | TOIE                | INTE                | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1   | PSPIF <sup>(1,2)</sup> | ADIF           | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000                | 0000 0000                       |

| 8Ch                   | PIE1   | PSPIE <sup>(1,2)</sup> | ADIE           | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup> | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000                | 0000 0000                       |

| 11h                   | TMR2   | Timer2 mod             | lule's registe | r                   |                     |         |        |         |         | 0000 0000                | 0000 0000                       |

| 12h                   | T2CON  | _                      | TOUTPS3        | TOUTPS2             | TOUTPS1             | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000                | -000 0000                       |

| 92h                   | PR2    | Timer2 Peri            | od Register    |                     |                     |         |        |         |         | 1111 1111                | 1111 1111                       |

Legend:

x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

Note

1:

Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

2:

The PIC16C72 does not have a Parallel Slave Port or a USART, these bits are unimplemented, read as '0'.

## FIGURE 10-1: CCP1CON REGISTER (ADDRESS 17h)/CCP2CON REGISTER (ADDRESS 1Dh)

| U-0      | U-0                                                                                                                                                                                                                               | R/W-0                                                                                             | R/W-0                                                                                                                                                                 | R/W-0                                                                                                                              | R/W-0                                                                                            | R/W-0                                                       | R/W-0                                   |                                                                                      |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------|--|--|--|

|          | —                                                                                                                                                                                                                                 | CCPxX                                                                                             | CCPxY                                                                                                                                                                 | CCPxM3                                                                                                                             | CCPxM2                                                                                           | CCPxM1                                                      | CCPxM0                                  | R = Readable bit                                                                     |  |  |  |

| bit7     |                                                                                                                                                                                                                                   |                                                                                                   |                                                                                                                                                                       |                                                                                                                                    |                                                                                                  |                                                             | bit0                                    | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset |  |  |  |

| bit 7-6: | Unimplemented: Read as '0'                                                                                                                                                                                                        |                                                                                                   |                                                                                                                                                                       |                                                                                                                                    |                                                                                                  |                                                             |                                         |                                                                                      |  |  |  |

| bit 5-4: | <ul> <li>CCPxX:CCPxY: PWM Least Significant bits</li> <li>Capture Mode: Unused</li> <li>Compare Mode: Unused</li> <li>PWM Mode: These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.</li> </ul> |                                                                                                   |                                                                                                                                                                       |                                                                                                                                    |                                                                                                  |                                                             |                                         |                                                                                      |  |  |  |

| bit 3-0: | 0000<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001<br>1010<br>1011                                                                                                                                                              | = Capture<br>= Capture<br>= Capture<br>= Capture<br>= Capture<br>= Compai<br>= Compai<br>= Compai | A/Compare<br>e mode, ev<br>e mode, ev<br>e mode, ev<br>e mode, ev<br>re mode, ev<br>re mode, ev<br>re mode, g<br>re mode, t<br>re mode, t<br>re mode, t<br>re mode, t | very falling e<br>very rising e<br>very 4th risin<br>very 16th ris<br>set output o<br>clear output<br>generate sof<br>rigger speci | resets CCP:<br>edge<br>dge<br>ng edge<br>ning edge<br>n match (CC<br>on match (C<br>tware intern | CPxIF bit is<br>CCPxIF bit i<br>upt on matc<br>CPxIF bit is | is set)<br>h (CCPxIF bi<br>set; CCP1 re | it is set, CCPx pin is unaffected)<br>sets TMR1; CCP2 resets TMR1                    |  |  |  |

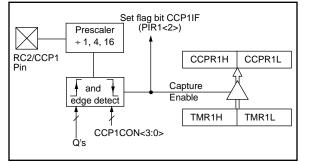

## 10.1 <u>Capture Mode</u>

Applicable Devices

72 73 73A 74 74A 76 77

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as:

- · Every falling edge

- · Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

## 10.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 is configured as an out-     |

|-------|----------------------------------------------|

|       | put, a write to the port can cause a capture |

|       | condition.                                   |

## FIGURE 10-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

## 10.1.2 TIMER1 MODE SELECTION

Timer1 must be running in timer mode or synchronized counter mode for the CCP module to use the capture feature. In asynchronous counter mode, the capture operation may not work.

#### 10.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in operating mode.

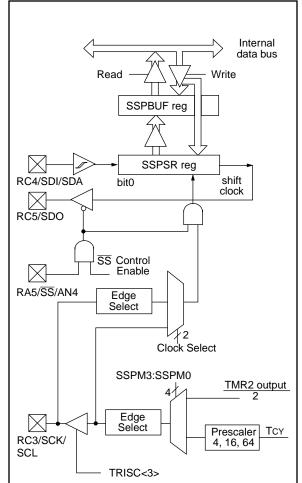

11.2.1 OPERATION OF SSP MODULE IN SPI MODE

| Applicable Devices |    |     |    |     |    |    |  |  |  |

|--------------------|----|-----|----|-----|----|----|--|--|--|

| 72                 | 73 | 73A | 74 | 74A | 76 | 77 |  |  |  |

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Serial Clock (SCK)

Additionally a fourth pin may be used when in a slave mode of operation:

Slave Select (SS)

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>). These control bits allow the following to be specified:

- Master Mode (SCK is the clock output)

- Slave Mode (SCK is the clock input)

- Clock Polarity (Output/Input data on the Rising/ Falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select Mode (Slave mode only)

The SSP consists of a transmit/receive Shift Register (SSPSR) and a Buffer register (SSPBUF). The SSPSR shifts the data in and out of the device. MSb first. The SSPBUF holds the data that was written to the SSPSR, until the received data is ready. Once the 8-bits of data have been received, that byte is moved to the SSPBUF register. Then the Buffer Full bit, BF (SSPSTAT<0>) and flag bit SSPIF are set. This double buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored, and the write collision detect bit, WCOL (SSPCON<7>) will be set. User software must clear bit WCOL so that it can be determined if the following write(s) to the SSPBUF completed successfully. When the application software is expecting to receive valid data, the SSPBUF register should be read before the next byte of data to transfer is written to the SSPBUF register. The Buffer Full bit BF (SSPSTAT<0>) indicates when the SSPBUF register has been loaded with the received data (transmission is complete). When the SSPBUF is read, bit BF is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally the SSP Interrupt is used to determine when the transmission/reception has completed. The SSPBUF register must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 11-1 shows the loading of the SSPBUF (SSPSR) register for data transmission. The shaded instruction is only required if the received data is meaningful.

## EXAMPLE 11-1: LOADING THE SSPBUF (SSPSR) REGISTER

|      |       | •       |      |                   |

|------|-------|---------|------|-------------------|

|      | BSF   | STATUS, | RP0  | ;Specify Bank 1   |

| LOOP | BTFSS | SSPSTAT | , BF | ;Has data been    |

|      |       |         |      | received          |

|      |       |         |      | ;(transmit        |

|      |       |         |      | ;complete)?       |

|      | GOTO  | LOOP    |      | ;No               |

|      | BCF   | STATUS, | RP0  | ;Specify Bank 0   |

|      | MOVF  | SSPBUF, | W    | ;W reg = contents |

|      |       |         |      | ;of SSPBUF        |

|      | MOVWF | RXDATA  |      | ;Save in user RAM |

|      | MOVF  | TXDATA, | W    | ;W reg = contents |

|      |       |         |      | ; of TXDATA       |

|      | MOVWF | SSPBUF  |      | ;New data to xmit |

|      |       |         |      |                   |

The block diagram of the SSP module, when in SPI mode (Figure 11-3), shows that the SSPSR register is not directly readable or writable, and can only be accessed from addressing the SSPBUF register. Additionally, the SSP status register (SSPSTAT) indicates the various status conditions.

## FIGURE 11-3: SSP BLOCK DIAGRAM (SPI MODE)

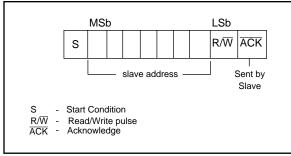

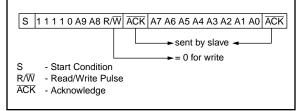

## 11.4.2 ADDRESSING I<sup>2</sup>C DEVICES

There are two address formats. The simplest is the 7-bit address format with a  $R/\overline{W}$  bit (Figure 11-15). The more complex is the 10-bit address with a  $R/\overline{W}$  bit (Figure 11-16). For 10-bit address format, two bytes must be transmitted with the first five bits specifying this to be a 10-bit address.

#### FIGURE 11-15: 7-BIT ADDRESS FORMAT

## FIGURE 11-16: I<sup>2</sup>C 10-BIT ADDRESS FORMAT

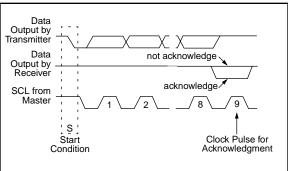

## 11.4.3 TRANSFER ACKNOWLEDGE

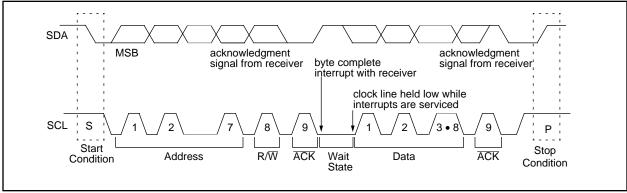

All data must be transmitted per byte, with no limit to the number of bytes transmitted per data transfer. After each byte, the slave-receiver generates an acknowledge bit ( $\overline{ACK}$ ) (Figure 11-17). When a slave-receiver doesn't acknowledge the slave address or received data, the master must abort the transfer. The slave must leave SDA high so that the master can generate the STOP condition (Figure 11-14).

## FIGURE 11-17: SLAVE-RECEIVER ACKNOWLEDGE

If the master is receiving the data (master-receiver), it generates an acknowledge signal for each received byte of data, except for the last byte. To signal the end of data to the slave-transmitter, the master does not generate an acknowledge (not acknowledge). The slave then releases the SDA line so the master can generate the STOP condition. The master can also generate the STOP condition during the acknowledge pulse for valid termination of data transfer.

If the slave needs to delay the transmission of the next byte, holding the SCL line low will force the master into a wait state. Data transfer continues when the slave releases the SCL line. This allows the slave to move the received data or fetch the data it needs to transfer before allowing the clock to start. This wait state technique can also be implemented at the bit level, Figure 11-18. The slave will inherently stretch the clock, when it is a transmitter, but will not when it is a receiver. The slave will have to clear the SSPCON<4> bit to enable clock stretching when it is a receiver.

## FIGURE 11-18: DATA TRANSFER WAIT STATE

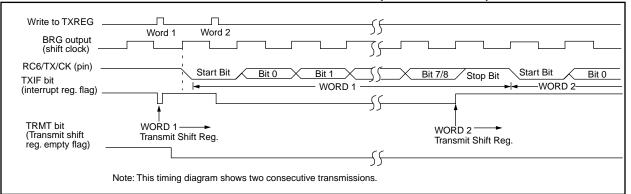

Steps to follow when setting up an Asynchronous Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH. (Section 12.1)

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

## FIGURE 12-8: ASYNCHRONOUS MASTER TRANSMISSION

## FIGURE 12-9: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

## TABLE 12-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address | Name                               | Bit 7                | Bit 6    | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0     | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|------------------------------------|----------------------|----------|--------|-------|-------|--------|--------|-----------|--------------------------|---------------------------------|

| 0Ch     | PIR1                               | PSPIF <sup>(1)</sup> | ADIF     | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF    | 0000 0000                | 0000 0000                       |

| 18h     | RCSTA                              | SPEN                 | RX9      | SREN   | CREN  | —     | FERR   | OERR   | RX9D      | 0000 -00x                | 0000 -00x                       |

| 19h     | TXREG                              | USART Trar           | nsmit Re | gister |       |       |        |        |           | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1                               | PSPIE <sup>(1)</sup> | ADIE     | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE    | 0000 0000                | 0000 0000                       |

| 98h     | TXSTA                              | CSRC                 | TX9      | TXEN   | SYNC  | _     | BRGH   | TRMT   | TX9D      | 0000 -010                | 0000 -010                       |

| 99h     | SPBRG Baud Rate Generator Register |                      |          |        |       |       |        |        | 0000 0000 | 0000 0000                |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH. (Section 12.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC, and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

## TABLE 12-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address | Name                               | Bit 7                | Bit 6    | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|------------------------------------|----------------------|----------|--------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Ch     | PIR1                               | PSPIF <sup>(1)</sup> | ADIF     | RCIF   | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h     | RCSTA                              | SPEN                 | RX9      | SREN   | CREN  |       | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 1Ah     | RCREG                              | USART Rec            | eive Reg | gister |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1                               | PSPIE <sup>(1)</sup> | ADIE     | RCIE   | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h     | TXSTA                              | CSRC                 | TX9      | TXEN   | SYNC  |       | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h     | SPBRG Baud Rate Generator Register |                      |          |        |       |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

## 14.3 <u>Reset</u> Applicable Devices 72|73|73A|74|74A|76|77

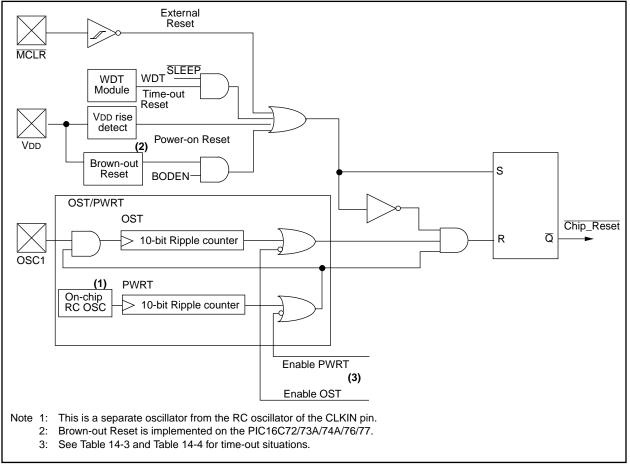

The PIC16CXX differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- MCLR reset during SLEEP

- WDT Reset (normal operation)

- Brown-out Reset (BOR) (PIC16C72/73A/74A/76/ 77)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged in any other reset. Most other registers are reset to a "reset state" on Power-on Reset (POR), on the  $\overline{\text{MCLR}}$  and WDT Reset, on  $\overline{\text{MCLR}}$  reset during SLEEP, and Brownout Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different reset situations as indicated in Table 14-5 and Table 14-6. These bits are used in software to determine the nature of the reset. See Table 14-8 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 14-8.

The PIC16C72/73A/74A/76/77 have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

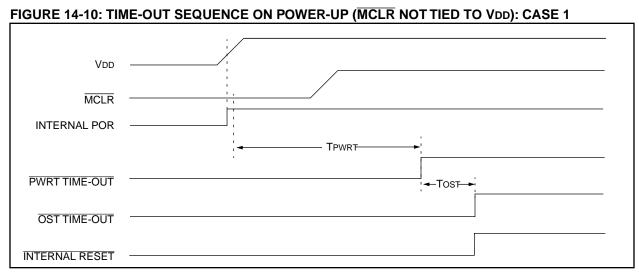

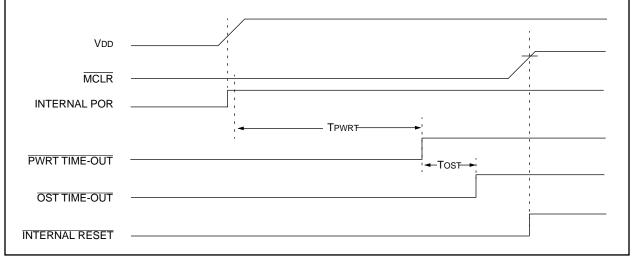

FIGURE 14-11: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

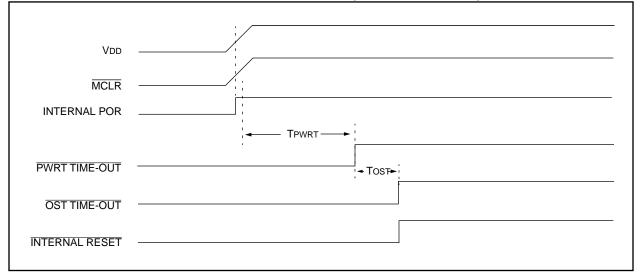

## FIGURE 14-12: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

# PIC16C7X

## Applicable Devices 72 73 73A 74 74A 76 77

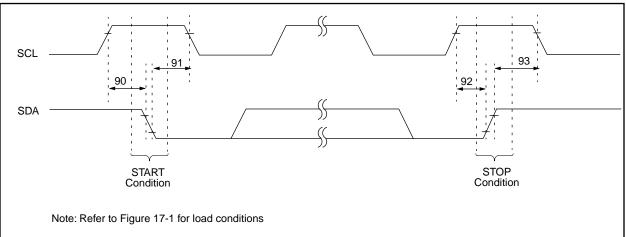

## TABLE 17-8: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Parameter<br>No. | Sym     | Characteristic  |              | Min  | Тур | Max | Units | Conditions                        |  |

|------------------|---------|-----------------|--------------|------|-----|-----|-------|-----------------------------------|--|

| 90               | TSU:STA | START condition | 100 kHz mode | 4700 | —   | —   | ns    | Only relevant for repeated START  |  |

|                  |         | Setup time      | 400 kHz mode | 600  | —   | —   |       | condition                         |  |

| 91               | THD:STA | START condition | 100 kHz mode | 4000 | —   | —   | ns    | After this period the first clock |  |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | 115   | pulse is generated                |  |

| 92               | Tsu:sto | STOP condition  | 100 kHz mode | 4700 | —   | —   | ns    |                                   |  |

|                  |         | Setup time      | 400 kHz mode | 600  | —   | —   | 113   |                                   |  |

| 93               | THD:STO | STOP condition  | 100 kHz mode | 4000 | —   | —   | ns    |                                   |  |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | 113   |                                   |  |

Applicable Devices 72 73 73A 74 74A 76 77

## 18.0 ELECTRICAL CHARACTERISTICS FOR PIC16C73/74

## Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                                    | 55 to +125°C                       |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage temperature                                                                                                               | 65°C to +150°C                     |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                                                | 0.3V to (VDD + 0.3V)               |

| Voltage on VDD with respect to Vss                                                                                                | 0.3 to +7.5V                       |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                      | 0 to +14V                          |

| Voltage on RA4 with respect to Vss                                                                                                | 0 to +14V                          |

| Total power dissipation (Note 1)                                                                                                  | 1.0W                               |

| Maximum current out of Vss pin                                                                                                    | 300 mA                             |

| Maximum current into VDD pin                                                                                                      | 250 mA                             |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                                      |                                    |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                                                    | ±20 mA                             |

| Maximum output current sunk by any I/O pin                                                                                        | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                                                     | 25 mA                              |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                                               | 200 mA                             |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                                            | 200 mA                             |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                                                       | 200 mA                             |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                                                    | 200 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\Sigma$ IOH} + $\Sigma$ {(VDD -                   | Voh) x Ioh} + $\Sigma$ (Vol x Iol) |

| Note $0$ , $\lambda$ (alternative balance) (as a table $\overline{\mathbf{MOLD}}$ are inducting summation matching the $0$ or $0$ |                                    |

- **Note 2:** Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

- Note 3: PORTD and PORTE are not implemented on the PIC16C73.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## TABLE 18-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C73-04<br>PIC16C74-04                                                                                                                          | PIC16C73-10<br>PIC16C74-10                                                                                                                         | PIC16C73-20<br>PIC16C74-20                                                                                                                         | PIC16LC73-04<br>PIC16LC74-04                                                                               | JW Devices                                                                                                                                         |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                            | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 3.0V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 13.5 μA max. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                           |

| хт  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                            | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 3.0V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 13.5 μA max. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                           |

| HS  | VDD:         4.5V to 5.5V           IDD:         13.5 mA typ. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         4 MHz max. | VDD:         4.5V to 5.5V           IDD:         15 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         10 MHz max. | VDD:         4.5V to 5.5V           IDD:         30 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         20 MHz max. | Not recommended for<br>use in HS mode                                                                      | VDD:         4.5V to 5.5V           IDD:         30 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         20 MHz max. |

| LP  | VDD: 4.0V to 6.0V<br>IDD: 52.5 μA typ. at<br>32 kHz, 4.0V<br>IPD: 0.9 μA typ. at 4.0V<br>Freq: 200 kHz max.                                         | Not recommended for<br>use in LP mode                                                                                                              | Not recommended for<br>use in LP mode                                                                                                              | VDD: 3.0V to 6.0V<br>IDD: 48 μA max. at<br>32 kHz, 3.0V<br>IPD: 13.5 μA max. at 3.0V<br>Freq: 200 kHz max. | VDD: 3.0V to 6.0V<br>IDD: 48 μA max. at<br>32 kHz, 3.0V<br>IPD: 13.5 μA max. at 3.0V<br>Freq: 200 kHz max.                                         |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

Applicable Devices 72 73 73A 74 74A 76 77

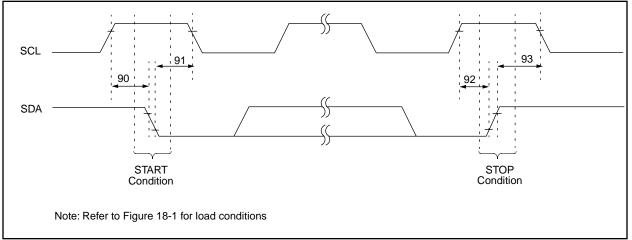

## FIGURE 18-9: I<sup>2</sup>C BUS START/STOP BITS TIMING

| Parameter<br>No. | Sym     | Characteristic  |              | Min  | Тур | Max | Units | Conditions                        |  |

|------------------|---------|-----------------|--------------|------|-----|-----|-------|-----------------------------------|--|

| 90               | TSU:STA | START condition | 100 kHz mode | 4700 | _   | —   | ns    | Only relevant for repeated START  |  |

|                  |         | Setup time      | 400 kHz mode | 600  |     | —   | 113   | condition                         |  |

| 91               | THD:STA | START condition | 100 kHz mode | 4000 |     | —   | ns    | After this period the first clock |  |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | 115   | pulse is generated                |  |

| 92               | TSU:STO | STOP condition  | 100 kHz mode | 4700 | —   | —   | ns    |                                   |  |

|                  |         | Setup time      | 400 kHz mode | 600  | —   | —   | 115   |                                   |  |

| 93               | THD:STO | STOP condition  | 100 kHz mode | 4000 | —   | —   | ns    |                                   |  |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | 113   |                                   |  |

Applicable Devices

72

73

73A

74

74A

76

77

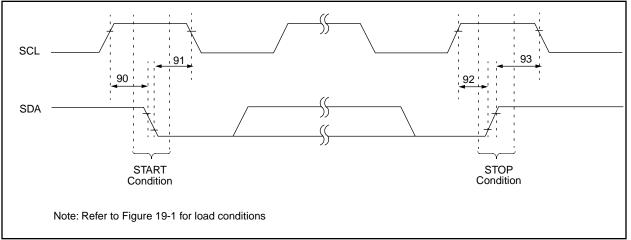

## FIGURE 19-10: I<sup>2</sup>C BUS START/STOP BITS TIMING

| Parameter<br>No. | Sym     | Characteristic  |              | Min  | Тур | Max | Units | Conditions                        |  |  |

|------------------|---------|-----------------|--------------|------|-----|-----|-------|-----------------------------------|--|--|

| 90               | TSU:STA | START condition | 100 kHz mode | 4700 | —   | —   | ns    | Only relevant for repeated STAR   |  |  |

|                  |         | Setup time      | 400 kHz mode | 600  | -   | —   | 110   | condition                         |  |  |

| 91               | THD:STA | START condition | 100 kHz mode | 4000 | —   | —   | ns    | After this period the first clock |  |  |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | 115   | pulse is generated                |  |  |

| 92               | Tsu:sto | STOP condition  | 100 kHz mode | 4700 | —   | —   | ns    |                                   |  |  |

|                  |         | Setup time      | 400 kHz mode | 600  | —   | —   | 115   |                                   |  |  |

| 93               | THD:STO | STOP condition  | 100 kHz mode | 4000 | —   | —   | ns    |                                   |  |  |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | 115   |                                   |  |  |

## Applicable Devices 72 73 73A 74 74A 76 77

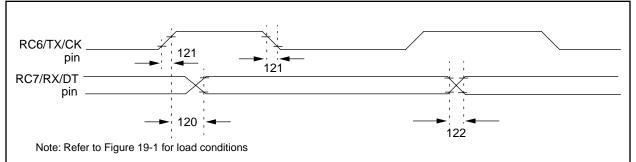

## FIGURE 19-12: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

## TABLE 19-11: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                                  |                         | Min | Тур† | Мах | Units | Conditions |

|--------------|----------|-------------------------------------------------|-------------------------|-----|------|-----|-------|------------|

| 120          | TckH2dtV | SYNC XMIT (MASTER &<br>SLAVE)                   | PIC16 <b>C</b> 73A/74A  | _   | _    | 80  | ns    |            |

|              |          | Clock high to data out valid                    | PIC16 <b>LC</b> 73A/74A | _   | —    | 100 | ns    |            |

| 121          | Tckrf    | Clock out rise time and fall time (Master Mode) | PIC16 <b>C</b> 73A/74A  | -   | —    | 45  | ns    |            |

|              |          |                                                 | PIC16 <b>LC</b> 73A/74A | -   | —    | 50  | ns    |            |

| 122          | Tdtrf    | Data out rise time and fall time                | PIC16 <b>C</b> 73A/74A  | - 1 | -    | 45  | ns    |            |

|              |          |                                                 | PIC16 <b>LC</b> 73A/74A | -   | —    | 50  | ns    |            |

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

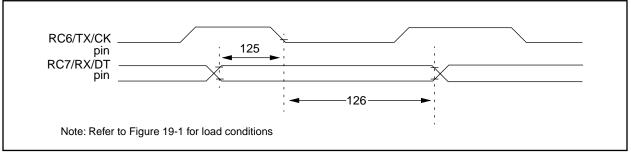

## FIGURE 19-13: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

## TABLE 19-12: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                                                            | Min | Тур† | Мах | Units | Conditions |

|------------------|----------|-----------------------------------------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | $\frac{\text{SYNC RCV (MASTER \& SLAVE)}}{\text{Data setup before CK} \downarrow (\text{DT setup time})}$ | 15  | _    | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                                            | 15  | —    | —   | ns    |            |

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Applicable Devices 72 73 73A 74 74A 76 77

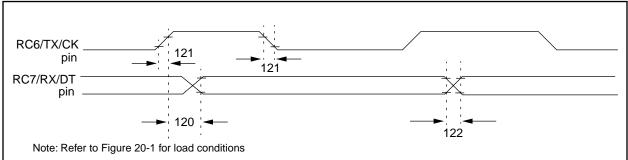

## FIGURE 20-15: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

## TABLE 20-11: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                                                |                                               | Min | Тур† | Max       | Units    | Conditions |

|--------------|----------|---------------------------------------------------------------|-----------------------------------------------|-----|------|-----------|----------|------------|

| 120          | TckH2dtV | SYNC XMIT (MASTER &<br>SLAVE)<br>Clock high to data out valid | PIC16 <b>C</b> 76/77<br>PIC16 <b>LC</b> 76/77 | _   | _    | 80<br>100 | ns<br>ns |            |

| 121          | Tckrf    | Clock out rise time and fall time                             | PIC16 <b>C</b> 76/77                          |     |      | 45        | ns       |            |

|              |          | (Master Mode)                                                 | PIC16 <b>LC</b> 76/77                         | —   |      | 50        | ns       |            |

| 122          | Tdtrf    | Data out rise time and fall time                              | PIC16 <b>C</b> 76/77                          | —   | -    | 45        | ns       |            |

|              |          |                                                               | PIC16 <b>LC</b> 76/77                         | —   | —    | 50        | ns       |            |

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

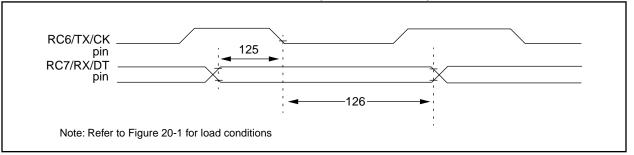

#### FIGURE 20-16: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

## TABLE 20-12: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                                 | Min | Тур† | Мах | Units | Conditions |

|------------------|----------|--------------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data setup before $CK \downarrow (DT setup time)$ | 15  | _    | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                 | 15  | —    | —   | ns    |            |

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## TABLE 21-1: RC OSCILLATOR FREQUENCIES

| Cext   | Rext  | Average         |        |  |  |  |  |

|--------|-------|-----------------|--------|--|--|--|--|

| Cext   | T CAL | Fosc @ 5V, 25°C |        |  |  |  |  |

| 22 pF  | 5k    | 4.12 MHz        | ± 1.4% |  |  |  |  |

|        | 10k   | 2.35 MHz        | ± 1.4% |  |  |  |  |

|        | 100k  | 268 kHz         | ± 1.1% |  |  |  |  |

| 100 pF | 3.3k  | 1.80 MHz        | ± 1.0% |  |  |  |  |

|        | 5k    | 1.27 MHz        | ± 1.0% |  |  |  |  |

|        | 10k   | 688 kHz         | ± 1.2% |  |  |  |  |

|        | 100k  | 77.2 kHz        | ± 1.0% |  |  |  |  |

| 300 pF | 3.3k  | 707 kHz         | ± 1.4% |  |  |  |  |

|        | 5k    | 501 kHz         | ± 1.2% |  |  |  |  |

|        | 10k   | 269 kHz         | ± 1.6% |  |  |  |  |

|        | 100k  | 28.3 kHz        | ± 1.1% |  |  |  |  |

The percentage variation indicated here is part to part variation due to normal process distribution. The variation indicated is  $\pm 3$  standard deviation from average value for VDD = 5V.

## Applicable Devices 72 73 73A 74 74A 76 77

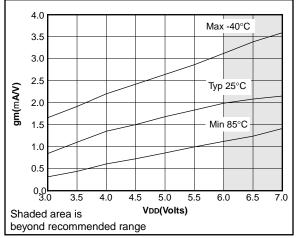

## FIGURE 21-19: TRANSCONDUCTANCE(gm) OF HS OSCILLATOR vs. VDD

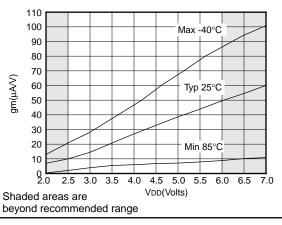

## FIGURE 21-20: TRANSCONDUCTANCE(gm) OF LP OSCILLATOR vs. VDD

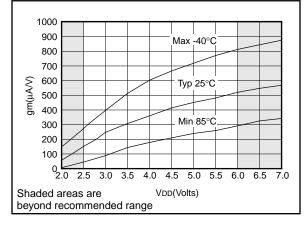

## FIGURE 21-21: TRANSCONDUCTANCE(gm) OF XT OSCILLATOR vs. VDD

Data based on matrix samples. See first page of this section for details.

# © 1997 Microchip Technology Inc.

## APPENDIX C: WHAT'S NEW

Added the following devices:

- PIC16C76

- PIC16C77

Removed the PIC16C710, PIC16C71, PIC16C711 from this datasheet.

Added PIC16C76 and PIC16C77 devices. The PIC16C76/77 devices have 368 bytes of data memory distributed in 4 banks and 8K of program memory in 4 pages. These two devices have an enhanced SPI that supports both clock phase and polarity. The USART has been enhanced.

When upgrading to the PIC16C76/77 please note that the upper 16 bytes of data memory in banks 1,2, and 3 are mapped into bank 0. This may require relocation of data memory usage in the user application code.

Added Q-cycle definitions to the Instruction Set Summary section.

## **APPENDIX D: WHAT'S CHANGED**

Minor changes, spelling and grammatical changes.

Added the following note to the USART section. This note applies to all devices except the PIC16C76 and PIC16C77.

For the PIC16C73/73A/74/74A the asynchronous high speed mode (BRGH = 1) may experience a high rate of receive errors. It is recommended that BRGH = 0. If you desire a higher baud rate than BRGH = 0 can support, refer to the device errata for additional information or use the PIC16C76/77.

Divided SPI section into SPI for the PIC16C76/77 and SPI for all other devices.

## U

| UA78, 83<br>Universal Synchronous Asynchronous Receiver Transmitter<br>(USART)99<br>Update Address bit, UA78, 83<br>USART |

|---------------------------------------------------------------------------------------------------------------------------|

| Asynchronous Mode106                                                                                                      |

| Asynchronous Receiver 108                                                                                                 |

| Asynchronous Reception109                                                                                                 |

| Asynchronous Transmission                                                                                                 |

| Asynchronous Transmitter                                                                                                  |

| Baud Rate Generator (BRG) 101                                                                                             |

| Receive Block Diagram108                                                                                                  |

| Sampling104                                                                                                               |

| Synchronous Master Mode110                                                                                                |

| Synchronous Master Reception                                                                                              |

| Synchronous Master Transmission                                                                                           |

| Synchronous Slave Mode114                                                                                                 |

| Synchronous Slave Reception114                                                                                            |

| Synchronous Slave Transmit114                                                                                             |

| Transmit Block Diagram106                                                                                                 |

| UV Erasable Devices7                                                                                                      |

## W

| W Register                       |                   |

|----------------------------------|-------------------|

| ALU                              | 9                 |

| Wake-up from SLEEP               | 145               |

| Watchdog Timer (WDT)1            | 29, 133, 136, 144 |

| WCOL                             |                   |

| WDT                              |                   |

| Block Diagram                    | 144               |

| Period                           | 144               |

| Programming Considerations       |                   |

| Timeout                          |                   |

| Word                             | 129               |

| WR pin                           | 54                |

| Write Collision Detect bit, WCOL |                   |

## Х

| XMIT_MODE |  |

|-----------|--|

| 7         |  |

| Z bit |     | ) |

|-------|-----|---|

| Zero  | bit | ) |

## LIST OF EXAMPLES

| Evernale 2.1   | Instruction Dinaling Flow             |

|----------------|---------------------------------------|

| Example 3-1:   | Instruction Pipeline Flow17           |

| Example 4-1:   | Call of a Subroutine in Page 1        |

| <b>F</b> 1 4 0 | from Page 041                         |

| Example 4-2:   | Indirect Addressing41                 |

| Example 5-1:   | Initializing PORTA43                  |

| Example 5-2:   | Initializing PORTB45                  |

| Example 5-3:   | Initializing PORTC48                  |

| Example 5-4:   | Read-Modify-Write Instructions        |

|                | on an I/O Port53                      |

| Example 7-1:   | Changing Prescaler (Timer0→WDT)63     |

| Example 7-2:   | Changing Prescaler (WDT→Timer0)63     |

| Example 8-1:   | Reading a 16-bit Free-Running Timer67 |

| Example 10-1:  | Changing Between Capture              |

|                | Prescalers73                          |

| Example 10-2:  | PWM Period and Duty Cycle             |

|                | Calculation                           |

| Example 11-1:  | Loading the SSPBUF (SSPSR)            |

| •              | Register                              |

| Example 11-2:  | Loading the SSPBUF (SSPSR)            |

|                | Register (PIC16C76/77)85              |

| Example 12-1:  | Calculating Baud Rate Error101        |

| Equation 13-1: | A/D Minimum Charging Time120          |

| Example 13-1:  | Calculating the Minimum Required      |

|                | Acquisition Time120                   |

| Example 13-2:  | A/D Conversion122                     |

| Example 13-3:  | 4-bit vs. 8-bit Conversion Times      |

| Example 14-1:  | Saving STATUS, W, and PCLATH          |

|                | Registers in RAM143                   |