Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 14KB (8K x 14)                                                          |

| Program Memory Type        | ОТР                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 368 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                 |

| Data Converters            | A/D 8x8b                                                                |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c77-20-l |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

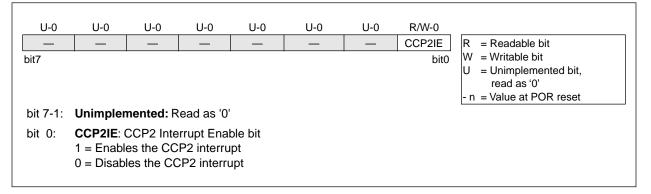

4.2.2.6 PIE2 REGISTER Applicable Devices 72 73 73 74 74 76 77

This register contains the individual enable bit for the CCP2 peripheral interrupt.

# FIGURE 4-14: PIE2 REGISTER (ADDRESS 8Dh)

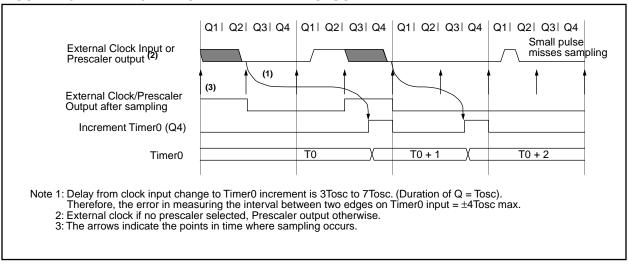

# 7.2 Using Timer0 with an External Clock Applicable Devices 72 73 73A 74 74A 76 77

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 7.2.2 TMR0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

#### FIGURE 7-5: TIMER0 TIMING WITH EXTERNAL CLOCK

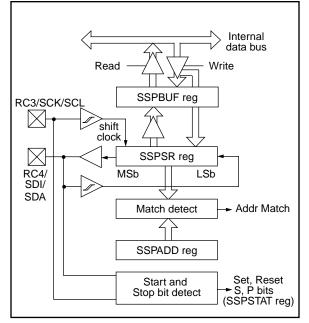

# 11.5 <u>SSP I<sup>2</sup>C Operation</u>

The SSP module in I<sup>2</sup>C mode fully implements all slave functions, except general call support, and provides interrupts on start and stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing. Two pins are used for data transfer. These are the RC3/SCK/SCL pin, which is the clock (SCL), and the RC4/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits. The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSP-CON<5>).

#### FIGURE 11-24: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  ${\rm I}^2{\rm C}$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Firmware controlled Master Mode, slave is idle

Selection of any I<sup>2</sup>C mode, with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits.

The SSPSTAT register gives the status of the data transfer. This information includes detection of a START or STOP bit, specifies if the received byte was data or address if the next byte is the completion of 10-bit address, and if this will be a read or write data transfer. The SSPSTAT register is read only.

The SSPBUF is the register to which transfer data is written to or read from. The SSPSR register shifts the data in or out of the device. In receive operations, the SSPBUF and SSPSR create a doubled buffered receiver. This allows reception of the next byte to begin before reading the last byte of received data. When the complete byte is received, it is transferred to the SSPBUF register and flag bit SSPIF is set. If another complete byte is received before the SSPBUF register is read, a receiver overflow has occurred and bit SSPOV (SSPCON<6>) is set and the byte in the SSPSR is lost.

The SSPADD register holds the slave address. In 10-bit mode, the user first needs to write the high byte of the address (1111 0 A9 A8 0). Following the high byte address match, the low byte of the address needs to be loaded (A7:A0).

#### 11.5.2 MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is idle and both the S and P bits are clear.

In master mode the SCL and SDA lines are manipulated by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- START condition

- STOP condition

- Data transfer byte transmitted/received

Master mode of operation can be done with either the slave mode idle (SSPM3:SSPM0 = 1011) or with the slave active. When both master and slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

#### 11.5.3 MULTI-MASTER MODE

In multi-master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

| Address                | Name    | Bit 7                | Bit 6              | Bit 5                  | Bit 4      | Bit 3      | Bit 2    | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other resets |

|------------------------|---------|----------------------|--------------------|------------------------|------------|------------|----------|--------|--------|-------------------------|---------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE               | TOIE                   | INTE       | RBIE       | TOIF     | INTF   | RBIF   | 0000 000x               | 0000 000u                 |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF               | RCIF                   | TXIF       | SSPIF      | CCP1IF   | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                 |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE               | RCIE                   | TXIE       | SSPIE      | CCP1IE   | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                 |

| 13h                    | SSPBUF  | Synchrono            | us Serial          | Port Rece              | eive Buffe | r/Transmit | Register |        |        | xxxx xxxx               | uuuu uuuu                 |

| 93h                    | SSPADD  | Synchrono            | us Serial          | Port (I <sup>2</sup> C | mode) Ad   | ldress Re  | gister   |        |        | 0000 0000               | 0000 0000                 |

| 14h                    | SSPCON  | WCOL                 | SSPOV              | SSPEN                  | CKP        | SSPM3      | SSPM2    | SSPM1  | SSPM0  | 0000 0000               | 0000 0000                 |

| 94h                    | SSPSTAT | SMP <sup>(2)</sup>   | CKE <sup>(2)</sup> | D/Ā                    | Р          | S          | R/W      | UA     | BF     | 0000 0000               | 0000 0000                 |

| 87h                    | TRISC   | PORTC Da             | ta Directi         | on registe             | er         |            |          |        |        | 1111 1111               | 1111 1111                 |

# TABLE 11-5: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

$\label{eq:Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in SPI mode.$

Note 1: PSPIF and PSPIE are reserved on the PIC16C73/73A/76, always maintain these bits clear.

2: The SMP and CKE bits are implemented on the PIC16C76/77 only. All other PIC16C7X devices have these two bits unimplemented, read as '0'.

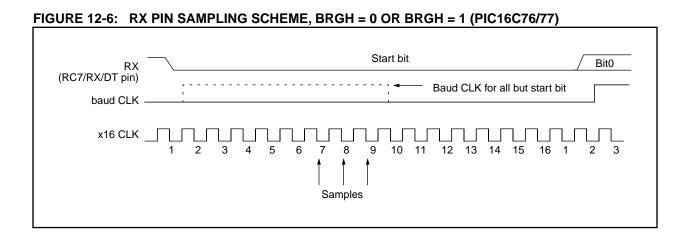

# 12.0 UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

# Applicable Devices

72 73 73A 74 74A 76 77

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI). The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, Serial EEPROMs etc.

The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>), and bits TRISC<7:6>, have to be set in order to configure pins RC6/TX/CK and RC7/ RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

#### FIGURE 12-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

| R/W-0  | R/W-0                                                                                                                                     | R/W-0                   | R/W-0        | U-0                     | R/W-0          | R-1      | R/W-0       |                                                                                            |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------|-------------------------|----------------|----------|-------------|--------------------------------------------------------------------------------------------|--|

| CSRC   | TX9                                                                                                                                       | TXEN                    | SYNC         | —                       | BRGH           | TRMT     | TX9D        | R = Readable bit                                                                           |  |

| bit7   |                                                                                                                                           |                         |              |                         |                |          | bit0        | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset       |  |

| bit 7: | CSRC: Clo                                                                                                                                 | ck Source               | Select bit   |                         |                |          |             |                                                                                            |  |

|        | Asynchrone<br>Don't care                                                                                                                  | <u>ous mode</u>         |              |                         |                |          |             |                                                                                            |  |

|        | $\frac{\text{Synchrono}}{1 = \text{Master}}$ $0 = \text{Slave n}$                                                                         | mode (Clo               |              |                         |                | .G)      |             |                                                                                            |  |

| bit 6: | <b>TX9</b> : 9-bit 7<br>1 = Selects<br>0 = Selects                                                                                        | 9-bit trans             | mission      |                         |                |          |             |                                                                                            |  |

| bit 5: | TXEN: Transmit Enable bit         1 = Transmit enabled         0 = Transmit disabled         Note: SREN/CREN overrides TXEN in SYNC mode. |                         |              |                         |                |          |             |                                                                                            |  |

| bit 4: | <b>SYNC</b> : US/<br>1 = Synchr<br>0 = Asynch                                                                                             | onous mod               | le           |                         |                |          |             |                                                                                            |  |

| bit 3: | Unimplem                                                                                                                                  | ented: Rea              | ad as '0'    |                         |                |          |             |                                                                                            |  |

| bit 2: | BRGH: Hig                                                                                                                                 | h Baud Ra               | te Select b  | it                      |                |          |             |                                                                                            |  |

|        | Asynchrone<br>1 = High sp                                                                                                                 |                         |              |                         |                |          |             |                                                                                            |  |

|        | Note:                                                                                                                                     | rience a h<br>baud rate | igh rate of  | receive er<br>H = 0 can | rors. It is re | commende | ed that BRG | ode (BRGH = 1) may expe-<br>H = 0. If you desire a higher<br>a for additional information, |  |

|        | 0 = Low sp                                                                                                                                | eed                     |              |                         |                |          |             |                                                                                            |  |

|        | Synchrono<br>Unused in t                                                                                                                  |                         |              |                         |                |          |             |                                                                                            |  |

| bit 1: | <b>TRMT</b> : Trar<br>1 = TSR en<br>0 = TSR ful                                                                                           | npty                    | Register St  | atus bit                |                |          |             |                                                                                            |  |

| bit 0: | <b>TX9D</b> : 9th I                                                                                                                       | bit of transi           | mit data. Ca | an be pari              | ty bit.        |          |             |                                                                                            |  |

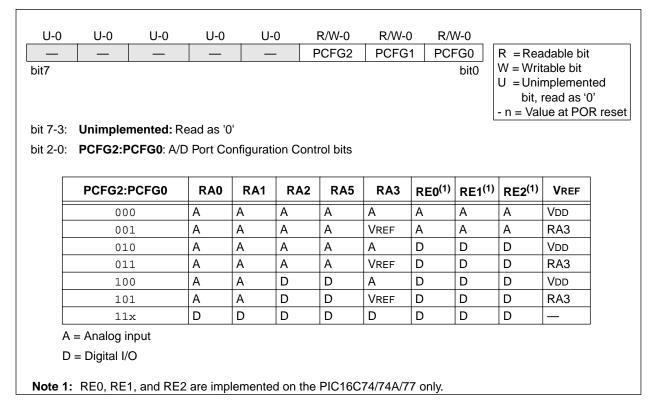

#### FIGURE 13-2: ADCON1 REGISTER (ADDRESS 9Fh)

# 13.8 Use of the CCP Trigger Applicable Devices 72 73 73A 74 74A 76 77

**Note:** In the PIC16C72, the "special event trigger" is implemented in the CCP1 module.

An A/D conversion can be started by the "special event trigger" of the CCP2 module (CCP1 on the PIC16C72 only). This requires that the CCP2M3:CCP2M0 bits (CCP2CON<3:0>) be programmed as 1011 and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving the ADRES to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

# 13.9 Connection Considerations Applicable Devices 72/73/73A/74/74A/76/77

If the input voltage exceeds the rail values (VSS or VDD) by greater than 0.2V, then the accuracy of the conversion is out of specification.

An external RC filter is sometimes added for anti-aliasing of the input signal. The R component should be selected to ensure that the total source impedance is kept under the 10 k $\Omega$  recommended specification. Any external components connected (via hi-impedance) to an analog input pin (capacitor, zener diode, etc.) should have very little leakage current at the pin.

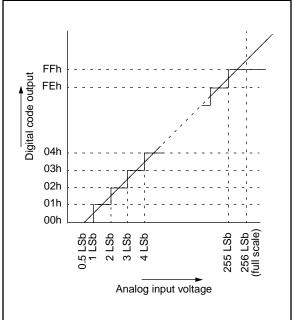

#### 13.10 Transfer Function Applicable Devices 72 73 73 74 74 76 77

The ideal transfer function of the A/D converter is as follows: the first transition occurs when the analog input voltage (VAIN) is Analog VREF/256 (Figure 13-5).

#### FIGURE 13-5: A/D TRANSFER FUNCTION

## 13.11 References

A very good reference for understanding A/D converters is the "Analog-Digital Conversion Handbook" third edition, published by Prentice Hall (ISBN 0-13-03-2848-0).

## FIGURE 14-2: CONFIGURATION WORD FOR PIC16C72/73A/74A/76/77

|          | P0 CP1                                                                                                | CP0     | CP1      | CP0      | _        | BODEN     | CP1     | CP0     | PWRTE    | WDTE    | FOSC1    |            | Register:<br>Address | CONFIG<br>2007h |

|----------|-------------------------------------------------------------------------------------------------------|---------|----------|----------|----------|-----------|---------|---------|----------|---------|----------|------------|----------------------|-----------------|

| bit13    |                                                                                                       |         |          |          |          |           |         |         |          |         |          | bit0       | Address              | 200711          |

| bit 13-8 |                                                                                                       |         |          |          |          |           |         |         |          |         |          |            |                      |                 |

| 5-4:     |                                                                                                       |         |          |          |          |           |         |         |          |         |          |            |                      |                 |

|          | 10 = Upper half of program memory code protected<br>01 = Upper 3/4th of program memory code protected |         |          |          |          |           |         |         |          |         |          |            |                      |                 |

|          | 01 = Opp<br>00 = All m                                                                                |         |          |          |          | / code pr | otected | 1       |          |         |          |            |                      |                 |

| bit 7:   | Unimpler                                                                                              | ,       |          | •        |          |           |         |         |          |         |          |            |                      |                 |

| bit 6:   | BODEN:                                                                                                |         |          |          | hle hit  | (1)       |         |         |          |         |          |            |                      |                 |

| 511 0.   | 1 = BOR (                                                                                             |         |          |          |          |           |         |         |          |         |          |            |                      |                 |

|          | 0 = BOR (                                                                                             | disable | d        |          |          |           |         |         |          |         |          |            |                      |                 |

| bit 3:   | PWRTE:                                                                                                | Power-u | up Time  | er Enab  | le bit ( | 1)        |         |         |          |         |          |            |                      |                 |

|          | 1 = PWR1                                                                                              |         |          |          |          |           |         |         |          |         |          |            |                      |                 |

|          | 0 = PWRT                                                                                              | enabl   | ed       |          |          |           |         |         |          |         |          |            |                      |                 |

| bit 2:   | WDTE: W                                                                                               |         |          | Enabl    | e bit    |           |         |         |          |         |          |            |                      |                 |

|          | 1 = WDT                                                                                               |         | -        |          |          |           |         |         |          |         |          |            |                      |                 |

|          | 0 = WDT                                                                                               |         | -        |          |          |           |         |         |          |         |          |            |                      |                 |

| bit 1-0: | FOSC1:F                                                                                               |         |          | tor Sele | ection   | bits      |         |         |          |         |          |            |                      |                 |

|          | 11 = RC (<br>10 = HS (                                                                                |         |          |          |          |           |         |         |          |         |          |            |                      |                 |

|          | 10 = HSC<br>01 = XTC                                                                                  |         |          |          |          |           |         |         |          |         |          |            |                      |                 |

|          | 01 = 100                                                                                              |         |          |          |          |           |         |         |          |         |          |            |                      |                 |

|          |                                                                                                       |         |          |          |          |           |         |         |          |         |          |            |                      |                 |

| Note 1:  | -                                                                                                     |         |          |          |          | •         |         |         |          | ,       | -        | ess of the | value of bit F       | PWRTE.          |

| ~        | Ensure th                                                                                             |         |          |          |          | ,         |         |         |          |         |          |            |                      |                 |

| 2:       | All of the                                                                                            | CP1:CF  | 20 pairs | s have t | to be g  | jiven the | same \  | alue to | o enable | the coo | de prote | ction sch  | eme listed.          |                 |

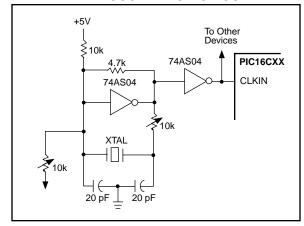

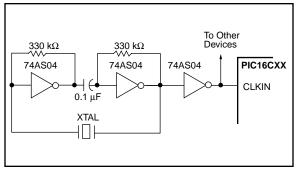

#### 14.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used; one with series resonance, or one with parallel resonance.

Figure 14-5 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometer biases the 74AS04 in the linear region. This could be used for external oscillator designs.

#### FIGURE 14-5: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

Figure 14-6 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 14-6: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

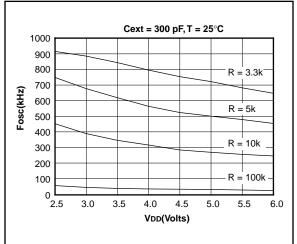

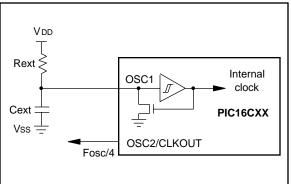

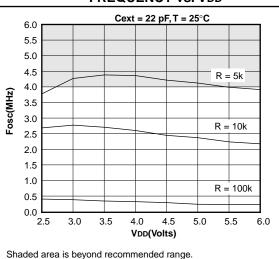

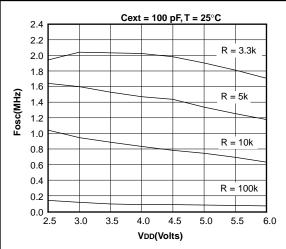

#### 14.2.4 RC OSCILLATOR

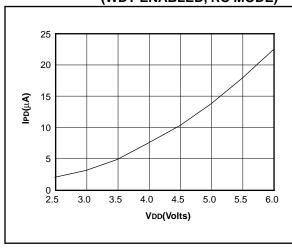

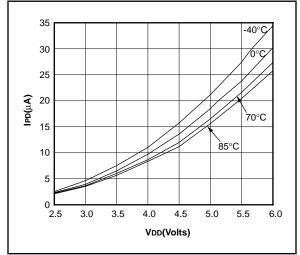

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (Rext) and capacitor (Cext) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low Cext values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 14-7 shows how the R/C combination is connected to the PIC16CXX. For Rext values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high Rext values (e.g. 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep Rext between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See characterization data for desired device for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See characterization data for desired device for variation of oscillator frequency due to VDD for given Rext/ Cext values as well as frequency variation due to operating temperature for given R, C, and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (see Figure 3-4 for waveform).

#### FIGURE 14-7: RC OSCILLATOR MODE

#### 14.4.5 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First PWRT time-out is invoked after the POR time delay has expired. Then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 14-10, Figure 14-11, and Figure 14-12 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 14-11). This is useful for testing purposes or to synchronize more than one PIC16CXX device operating in parallel.

Table 14-7 shows the reset conditions for some special function registers, while Table 14-8 shows the reset conditions for all the registers.

#### 14.4.6 POWER CONTROL/STATUS REGISTER (PCON)

| -  | Applicable Devices |     |    |     |    |    |  |  |

|----|--------------------|-----|----|-----|----|----|--|--|

| 72 | 73                 | 73A | 74 | 74A | 76 | 77 |  |  |

The Power Control/Status Register, PCON has up to two bits, depending upon the device. Bit0 is not implemented on the PIC16C73 or PIC16C74.

Bit0 is Brown-out Reset Status bit, BOR. Bit BOR is unknown on a Power-on Reset. It must then be set by the user and checked on subsequent resets to see if bit BOR cleared, indicating a BOR occurred. The BOR bit is a "Don't Care" bit and is not necessarily predictable if the Brown-out Reset circuitry is disabled (by clearing bit BODEN in the Configuration Word).

Bit1 is POR (Power-on Reset Status bit). It is cleared on a Power-on Reset and unaffected otherwise. The user must set this bit following a Power-on Reset.

#### TABLE 14-3: TIME-OUT IN VARIOUS SITUATIONS, PIC16C73/74

| Oscillator Configuration | Powe             | Wake-up from SLEEP |           |

|--------------------------|------------------|--------------------|-----------|

|                          | PWRTE = 1        | PWRTE = 0          |           |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc           | 1024 Tosc |

| RC                       | 72 ms            | _                  |           |

#### TABLE 14-4: TIME-OUT IN VARIOUS SITUATIONS, PIC16C72/73A/74A/76/77

| Oscillator Configuration | Power            | r-up      | Brown-out        | Wake-up from SLEEP |  |  |

|--------------------------|------------------|-----------|------------------|--------------------|--|--|

|                          | PWRTE = 0        | PWRTE = 1 | Brown-out        |                    |  |  |

| XT, HS, LP               | 72 ms + 1024Tosc | 1024Tosc  | 72 ms + 1024Tosc | 1024Tosc           |  |  |

| RC                       | 72 ms            |           | 72 ms            | _                  |  |  |

#### TABLE 14-5: STATUS BITS AND THEIR SIGNIFICANCE, PIC16C73/74

| POR | TO | PD |                                                         |  |  |  |

|-----|----|----|---------------------------------------------------------|--|--|--|

| 0   | 1  | 1  | Power-on Reset                                          |  |  |  |

| 0   | 0  | х  | Illegal, TO is set on POR                               |  |  |  |

| 0   | x  | 0  | Illegal, PD is set on POR                               |  |  |  |

| 1   | 0  | 1  | WDT Reset                                               |  |  |  |

| 1   | 0  | 0  | WDT Wake-up                                             |  |  |  |

| 1   | u  | u  | MCLR Reset during normal operation                      |  |  |  |

| 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |  |  |  |

Legend: u = unchanged, x = unknown

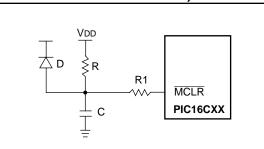

#### FIGURE 14-13: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

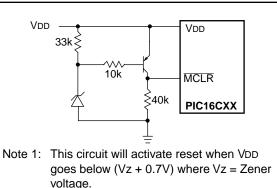

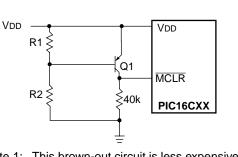

#### FIGURE 14-14: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- 2: Internal brown-out detection on the PIC16C72/73A/74A/76/77 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

#### FIGURE 14-15: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

- 2: Internal brown-out detection on the PIC16C72/73A/74A/76/77 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

| COMF                                                                                                                          | Complement f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DECFSZ            | Decrement f, Skip if 0                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                                       | [ <i>label</i> ] COMF f,d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Syntax:           | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                        |

| Operands:                                                                                                                     | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Operands:         | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                 |

| Operation:                                                                                                                    | $(\overline{f}) \rightarrow$ (destination)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Operation:        | (f) - 1 $\rightarrow$ (destination);                                                                                                                                                                                                                                                               |

| Status Affected:                                                                                                              | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   | skip if result = 0                                                                                                                                                                                                                                                                                 |

| Encoding:                                                                                                                     | 00 1001 dfff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Status Affected:  | None                                                                                                                                                                                                                                                                                               |

| Description:                                                                                                                  | The contents of register 'f' are comple-<br>mented. If 'd' is 0 the result is stored in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Encoding:         | 00 1011 dfff ffff                                                                                                                                                                                                                                                                                  |

|                                                                                                                               | W. If 'd' is 1 the result is stored back in register 'f'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Description:      | The contents of register 'f' are decre-<br>mented. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed                                                                                                                                                         |

| Words:                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   | back in register 'f'.<br>If the result is 1, the next instruction, is                                                                                                                                                                                                                              |

| Cycles:                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   | executed. If the result is 0, then a NOP is<br>executed instead making it a 2TCY instruc-                                                                                                                                                                                                          |

| Q Cycle Activity:                                                                                                             | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   | tion.                                                                                                                                                                                                                                                                                              |

|                                                                                                                               | Decode Read Process Write to register data destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Words:            | 1                                                                                                                                                                                                                                                                                                  |

|                                                                                                                               | f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Cycles:           | 1(2)                                                                                                                                                                                                                                                                                               |

|                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                        |

| Example                                                                                                                       | COMF REG1,0<br>Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   | Decode Read register 'f' Process Write to destination                                                                                                                                                                                                                                              |

|                                                                                                                               | REG1 = 0x13<br>After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | If Skip:          | (2nd Cycle)                                                                                                                                                                                                                                                                                        |

|                                                                                                                               | REG1 = 0x13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                        |

|                                                                                                                               | W = 0xEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   | No-No-No-OperationOperationOperation                                                                                                                                                                                                                                                               |

|                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |                                                                                                                                                                                                                                                                                                    |