Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | A/D 8x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c77-20e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0 General Description                                              | 5     |

|----------------------------------------------------------------------|-------|

| 2.0 PIC16C7X Device Varieties                                        | 7     |

| 3.0 Architectural Overview                                           | 9     |

| 4.0 Memory Organization                                              | 19    |

| 5.0 I/O Ports                                                        | 43    |

| 6.0 Overview of Timer Modules                                        | 57    |

| 7.0 Timer0 Module                                                    | 59    |

| 8.0 Timer1 Module                                                    | 65    |

| 9.0 Timer2 Module                                                    | 69    |

| 10.0 Capture/Compare/PWM Module(s)                                   |       |

| 11.0 Synchronous Serial Port (SSP) Module                            |       |

| 12.0 Universal Synchronous Asynchronous Receiver Transmitter (USART) | 99    |

| 13.0 Analog-to-Digital Converter (A/D) Module                        | . 117 |

| 14.0 Special Features of the CPU                                     |       |

| 15.0 Instruction Set Summary                                         | . 147 |

| 16.0 Development Support                                             |       |

| 17.0 Electrical Characteristics for PIC16C72                         |       |

| 18.0 Electrical Characteristics for PIC16C73/74                      |       |

| 19.0 Electrical Characteristics for PIC16C73A/74A                    |       |

| 20.0 Electrical Characteristics for PIC16C76/77                      | . 219 |

| 21.0 DC and AC Characteristics Graphs and Tables                     |       |

| 22.0 Packaging Information                                           | . 251 |

| Appendix A:                                                          |       |

| Appendix B: Compatibility                                            | . 263 |

| Appendix C: What's New                                               | . 264 |

| Appendix D: What's Changed                                           |       |

| Appendix E: PIC16/17 Microcontrollers                                | . 265 |

| Pin Compatibility                                                    |       |

| Index                                                                | . 273 |

| List of Examples                                                     | . 279 |

| List of Figures                                                      |       |

| List of Tables                                                       |       |

| Reader Response                                                      |       |

| PIC16C7X Product Identification System                               | . 287 |

For register and module descriptions in this data sheet, device legends show which devices apply to those sections. As an example, the legend below would mean that the following section applies only to the PIC16C72, PIC16C73A and PIC16C74A devices.

## Applicable Devices 72 73 73A 74 74A 76 77

12|13|13A|14|14A|16|11

## To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent an exceptional amount of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

### TABLE 3-2:PIC16C73/73A/76 PINOUT DESCRIPTION

| Pin Name                | DIP<br>Pin# | SOIC<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                                  |

|-------------------------|-------------|--------------|---------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN              | 9           | 9            | I             | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                        |

| OSC2/CLKOUT             | 10          | 10           | 0             | -                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp                | 1           | 1            | I/P           | ST                     | Master clear (reset) input or programming voltage input. This pin is an active low reset to the device.                                                                                                      |

|                         |             |              |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                          |

| RA0/AN0                 | 2           | 2            | I/O           | TTL                    | RA0 can also be analog input0                                                                                                                                                                                |

| RA1/AN1                 | 3           | 3            | I/O           | TTL                    | RA1 can also be analog input1                                                                                                                                                                                |

| RA2/AN2                 | 4           | 4            | I/O           | TTL                    | RA2 can also be analog input2                                                                                                                                                                                |

| RA3/AN3/VREF            | 5           | 5            | I/O           | TTL                    | RA3 can also be analog input3 or analog reference voltage                                                                                                                                                    |

| RA4/T0CKI               | 6           | 6            | I/O           | ST                     | RA4 can also be the clock input to the Timer0 module.<br>Output is open drain type.                                                                                                                          |

| RA5/ <del>SS</del> /AN4 | 7           | 7            | I/O           | TTL                    | RA5 can also be analog input4 or the slave select for the<br>synchronous serial port.                                                                                                                        |

|                         |             |              |               |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                                |

| RB0/INT                 | 21          | 21           | I/O           | TTL/ST(1)              | RB0 can also be the external interrupt pin.                                                                                                                                                                  |

| RB1                     | 22          | 22           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB2                     | 23          | 23           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB3                     | 24          | 24           | I/O           | TTL                    |                                                                                                                                                                                                              |

| RB4                     | 25          | 25           | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |

| RB5                     | 26          | 26           | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |

| RB6                     | 27          | 27           | I/O           | TTL/ST(2)              | Interrupt on change pin. Serial programming clock.                                                                                                                                                           |

| RB7                     | 28          | 28           | I/O           | TTL/ST(2)              | Interrupt on change pin. Serial programming data.                                                                                                                                                            |

|                         |             |              |               |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                          |

| RC0/T1OSO/T1CKI         | 11          | 11           | I/O           | ST                     | RC0 can also be the Timer1 oscillator output or Timer1 clock input.                                                                                                                                          |

| RC1/T1OSI/CCP2          | 12          | 12           | I/O           | ST                     | RC1 can also be the Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output.                                                                                                                   |

| RC2/CCP1                | 13          | 13           | I/O           | ST                     | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                                                                                                                          |

| RC3/SCK/SCL             | 14          | 14           | I/O           | ST                     | RC3 can also be the synchronous serial clock input/output for both SPI and I <sup>2</sup> C modes.                                                                                                           |

| RC4/SDI/SDA             | 15          | 15           | I/O           | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                                                                                              |

| RC5/SDO                 | 16          | 16           | I/O           | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                 |

| RC6/TX/CK               | 17          | 17           | I/O           | ST                     | RC6 can also be the USART Asynchronous Transmit of<br>Synchronous Clock.                                                                                                                                     |

| RC7/RX/DT               | 18          | 18           | I/O           | ST                     | RC7 can also be the USART Asynchronous Receive of<br>Synchronous Data.                                                                                                                                       |

| Vss                     | 8, 19       | 8, 19        | Р             | <u> </u>               | Ground reference for logic and I/O pins.                                                                                                                                                                     |

| VDD                     | 20          | 20           | P             | <u> </u>               | Positive supply for logic and I/O pins.                                                                                                                                                                      |

| Legend: I = input       | O = outp    |              |               | input/output           | P = power                                                                                                                                                                                                    |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

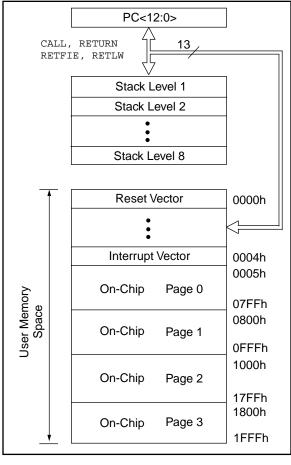

### FIGURE 4-3: PIC16C76/77 PROGRAM MEMORY MAP AND STACK

### 4.2 Data Memory Organization

Applicable Devices 72 73 73 74 74 76 77

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

RP1:RP0 (STATUS<6:5>)

- = 00  $\rightarrow$  Bank0

- = 01  $\rightarrow$  Bank1

- =  $10 \rightarrow \text{Bank2}$

- = 11  $\rightarrow$  Bank3

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain special function registers. Some "high use" special function registers from one bank may be mirrored in another bank for code reduction and quicker access.

### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR (Section 4.5).

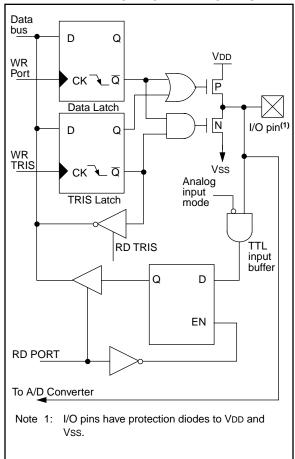

### 5.0 I/O PORTS Applicable Devices 72 73 73A 74 74A 76 77

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

### 5.1 PORTA and TRISA Registers Applicable Devices 72 73 73A 74 74A 76 77

### PORTA is a 6-bit latch.

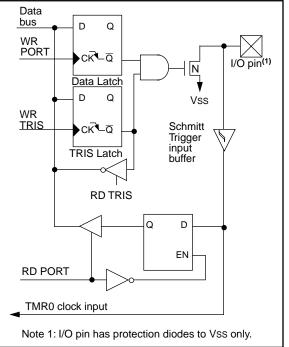

The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as output or input.

Setting a TRISA register bit puts the corresponding output driver in a hi-impedance mode. Clearing a bit in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

Note: On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

### EXAMPLE 5-1: INITIALIZING PORTA

| BCF   | STATUS, | RP0 | ; |                       |

|-------|---------|-----|---|-----------------------|

| BCF   | STATUS, | RP1 | ; | PIC16C76/77 only      |

| CLRF  | PORTA   |     | ; | Initialize PORTA by   |

|       |         |     | ; | clearing output       |

|       |         |     | ; | data latches          |

| BSF   | STATUS, | RP0 | ; | Select Bank 1         |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISA   |     | ; | Set RA<3:0> as inputs |

|       |         |     | ; | RA<5:4> as outputs    |

|       |         |     | ; | TRISA<7:6> are always |

|       |         |     | ; | read as '0'.          |

|       |         |     |   |                       |

### FIGURE 5-1: BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

### FIGURE 5-2: BLOCK DIAGRAM OF RA4/ T0CKI PIN

|  | TABLE 5-4: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTB |

|--|------------|--------------------------------------------|

|--|------------|--------------------------------------------|

| Address   | Name   | Bit 7 | Bit 6         | Bit 5      | Bit 4 | Bit 3     | Bit 2     | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------|--------|-------|---------------|------------|-------|-----------|-----------|-------|-------|--------------------------|---------------------------|

| 06h, 106h | PORTB  | RB7   | RB6           | RB5        | RB4   | RB3       | RB2       | RB1   | RB0   | xxxx xxxx                | uuuu uuuu                 |

| 86h, 186h | TRISB  | PORTB | Data Directic | on Registe |       | 1111 1111 | 1111 1111 |       |       |                          |                           |

| 81h, 181h | OPTION | RBPU  | INTEDG        | TOCS       | TOSE  | PSA       | PS2       | PS1   | PS0   | 1111 1111                | 1111 1111                 |

Legend: x = unknown, u = unchanged. Shaded cells are not used by PORTB.

### TABLE 5-9:PORTE FUNCTIONS

| Name       | Bit# | Buffer Type           | Function                                                                                                                                                                                         |

|------------|------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or read control input in parallel slave port mode or<br>analog input:<br>RD<br>1 = Not a read operation<br>0 = Read operation. Reads PORTD register (if chip selected)     |

| RE1/WR/AN6 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or write control input in parallel slave port mode or<br>analog input:<br>WR<br>1 = Not a write operation<br>0 = Write operation. Writes PORTD register (if chip selected) |

| RE2/CS/AN7 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or chip select control input in parallel slave port<br>mode or analog input:<br>CS<br>1 = Device is not selected<br>0 = Device is selected                                 |

Legend: ST = Schmitt Trigger input TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port Mode.

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2    | Bit 1        | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|--------|-------|-------|-------|---------|-------|----------|--------------|-------|--------------------------|---------------------------|

| 09h     | PORTE  | _     | _     | _     | —       | —     | RE2      | RE1          | RE0   | xxx                      | uuu                       |

| 89h     | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | —     | PORTE Da | ta Direction | Bits  | 0000 -111                | 0000 -111                 |

| 9Fh     | ADCON1 |       |       | —     | —       | —     | PCFG2    | PCFG1        | PCFG0 | 000                      | 000                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTE.

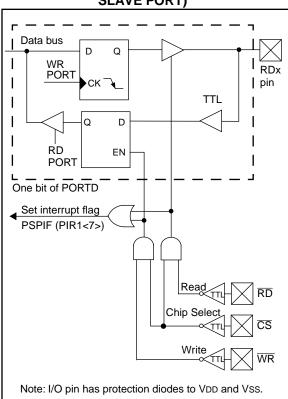

### 5.7 Parallel Slave Port Applicable Devices 72 73 73 74 74 76 77

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port when control bit PSPMODE (TRISE<4>) is set. In slave mode it is asynchronously readable and writable by the external world through  $\overline{RD}$  control input pin RE0/ $\overline{RD}$ /AN5 and  $\overline{WR}$  control input pin RE1/ $\overline{WR}$ /AN6.

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD/AN5 to be the RD input, RE1/ WR/AN6 to be the WR input and RE2/CS/AN7 to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set) and the A/D port configuration bits PCFG2:PCFG0 (ADCON1<2:0>) must be set, which will configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches, one for data-out (from the PIC16/17) and one for data input. The user writes 8-bit data to PORTD data latch and reads data from the port pin latch (note that they have the same address). In this mode, the TRISD register is ignored, since the microprocessor is controlling the direction of data flow.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$ lines are first detected low. When either the  $\overline{CS}$  or  $\overline{WR}$ lines become high (level triggered), then the Input Buffer Full status flag bit IBF (TRISE<7>) is set on the Q4 clock cycle, following the next Q2 cycle, to signal the write is complete (Figure 5-12). The interrupt flag bit PSPIF (PIR1<7>) is also set on the same Q4 clock cycle. IBF can only be cleared by reading the PORTD input latch. The input Buffer Overflow status flag bit IBOV (TRISE<5>) is set if a second write to the Parallel Slave Port is attempted when the previous byte has not been read out of the buffer.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The Output Buffer Full status flag bit OBF (TRISE<6>) is cleared immediately (Figure 5-13) indicating that the PORTD latch is waiting to be read by the external bus. When either the  $\overline{CS}$  or  $\overline{RD}$  pin becomes high (level triggered), the interrupt flag bit PSPIF is set on the Q4 clock cycle, following the next Q2 cycle, indicating that the read is complete. OBF remains low until data is written to PORTD by the user firmware.

When not in Parallel Slave Port mode, the IBF and OBF bits are held clear. However, if flag bit IBOV was previously set, it must be cleared in firmware.

An interrupt is generated and latched into flag bit PSPIF when a read or write operation is completed. PSPIF must be cleared by the user in firmware and the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

### FIGURE 5-11: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

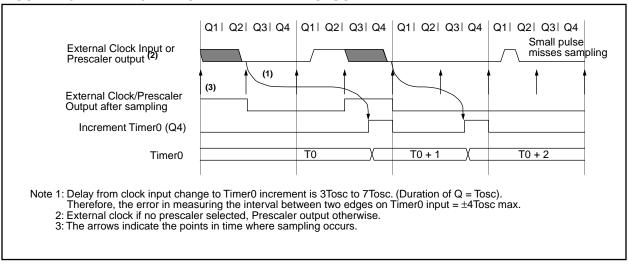

### 7.2 Using Timer0 with an External Clock Applicable Devices 72 73 73A 74 74A 76 77

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

### 7.2.2 TMR0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

### FIGURE 7-5: TIMER0 TIMING WITH EXTERNAL CLOCK

### FIGURE 9-2: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

| U-0      | R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0                                                                                                     |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| <u> </u> | TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0 R = Readable bit                                                                 |  |

| bit7     | bit0<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset                                           |  |

| bit 7:   | Unimplemented: Read as '0'                                                                                                              |  |

| bit 6-3: | TOUTPS3:TOUTPS0: Timer2 Output Postscale Select bits<br>0000 = 1:1 Postscale<br>0001 = 1:2 Postscale<br>•<br>•<br>1111 = 1:16 Postscale |  |

| bit 2:   | TMR2ON: Timer2 On bit<br>1 = Timer2 is on<br>0 = Timer2 is off                                                                          |  |

| bit 1-0: | <b>T2CKPS1:T2CKPS0</b> : Timer2 Clock Prescale Select bits<br>00 = Prescaler is 1<br>01 = Prescaler is 4<br>1x = Prescaler is 16        |  |

### **TABLE 9-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER**

| Address               | Name   | Bit 7                  | Bit 6          | Bit 5               | Bit 4               | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|-----------------------|--------|------------------------|----------------|---------------------|---------------------|---------|--------|---------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                    | PEIE           | TOIE                | INTE                | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1   | PSPIF <sup>(1,2)</sup> | ADIF           | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000                | 0000 0000                       |

| 8Ch                   | PIE1   | PSPIE <sup>(1,2)</sup> | ADIE           | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup> | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000                | 0000 0000                       |

| 11h                   | TMR2   | Timer2 mod             | lule's registe | r                   |                     |         |        |         |         | 0000 0000                | 0000 0000                       |

| 12h                   | T2CON  | _                      | TOUTPS3        | TOUTPS2             | TOUTPS1             | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000                | -000 0000                       |

| 92h                   | PR2    | Timer2 Peri            | 1111 1111      | 1111 1111           |                     |         |        |         |         |                          |                                 |

Legend:

x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

Note

1:

Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

2:

The PIC16C72 does not have a Parallel Slave Port or a USART, these bits are unimplemented, read as '0'.

### 12.0 UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

### Applicable Devices

72 73 73A 74 74A 76 77

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI). The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, Serial EEPROMs etc.

The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>), and bits TRISC<7:6>, have to be set in order to configure pins RC6/TX/CK and RC7/ RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

### FIGURE 12-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

| R/W-0  | R/W-0                                                                                                                                                                                                                                                                                                           | R/W-0                     | R/W-0        | U-0        | R/W-0    | R-1  | R/W-0 |                                                                                      |  |  |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------|------------|----------|------|-------|--------------------------------------------------------------------------------------|--|--|--|

| CSRC   | TX9                                                                                                                                                                                                                                                                                                             | TXEN                      | SYNC         | —          | BRGH     | TRMT | TX9D  | R = Readable bit                                                                     |  |  |  |

| bit7   |                                                                                                                                                                                                                                                                                                                 |                           |              |            |          |      | bit0  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset |  |  |  |

| bit 7: | CSRC: Clo                                                                                                                                                                                                                                                                                                       | ck Source                 | Select bit   |            |          |      |       |                                                                                      |  |  |  |

|        | Asynchrone<br>Don't care                                                                                                                                                                                                                                                                                        | <u>ous mode</u>           |              |            |          |      |       |                                                                                      |  |  |  |

|        | $\frac{\text{Synchrono}}{1 = \text{Master}}$ $0 = \text{Slave n}$                                                                                                                                                                                                                                               | mode (Clo                 |              |            |          | .G)  |       |                                                                                      |  |  |  |

| bit 6: | <b>TX9</b> : 9-bit 7<br>1 = Selects<br>0 = Selects                                                                                                                                                                                                                                                              | 9-bit trans               | mission      |            |          |      |       |                                                                                      |  |  |  |

| bit 5: | <b>TXEN</b> : Tran<br>1 = Transm<br>0 = Transm<br>Note: SREI                                                                                                                                                                                                                                                    | it enabled<br>it disabled |              | EN in SYN  | NC mode. |      |       |                                                                                      |  |  |  |

| bit 4: | <b>SYNC</b> : US/<br>1 = Synchr<br>0 = Asynch                                                                                                                                                                                                                                                                   | onous mod                 | le           |            |          |      |       |                                                                                      |  |  |  |

| bit 3: | Unimplem                                                                                                                                                                                                                                                                                                        | ented: Rea                | ad as '0'    |            |          |      |       |                                                                                      |  |  |  |

| bit 2: | BRGH: Hig                                                                                                                                                                                                                                                                                                       | h Baud Ra                 | te Select b  | it         |          |      |       |                                                                                      |  |  |  |

|        | Asynchrone<br>1 = High sp                                                                                                                                                                                                                                                                                       |                           |              |            |          |      |       |                                                                                      |  |  |  |

|        | <b>Note:</b> For the PIC16C73/73A/74/74A, the asynchronous high speed mode (BRGH = 1) may experience a high rate of receive errors. It is recommended that BRGH = 0. If you desire a higher baud rate than BRGH = 0 can support, refer to the device errata for additional information, or use the PIC16C76/77. |                           |              |            |          |      |       |                                                                                      |  |  |  |

|        | 0 = Low sp                                                                                                                                                                                                                                                                                                      | eed                       |              |            |          |      |       |                                                                                      |  |  |  |

|        | Synchrono<br>Unused in t                                                                                                                                                                                                                                                                                        |                           |              |            |          |      |       |                                                                                      |  |  |  |

| bit 1: | <b>TRMT</b> : Trar<br>1 = TSR en<br>0 = TSR ful                                                                                                                                                                                                                                                                 | npty                      | Register St  | atus bit   |          |      |       |                                                                                      |  |  |  |

| bit 0: | <b>TX9D</b> : 9th I                                                                                                                                                                                                                                                                                             | bit of transi             | mit data. Ca | an be pari | ty bit.  |      |       |                                                                                      |  |  |  |

### 13.8 Use of the CCP Trigger Applicable Devices 72 73 73A 74 74A 76 77

**Note:** In the PIC16C72, the "special event trigger" is implemented in the CCP1 module.

An A/D conversion can be started by the "special event trigger" of the CCP2 module (CCP1 on the PIC16C72 only). This requires that the CCP2M3:CCP2M0 bits (CCP2CON<3:0>) be programmed as 1011 and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving the ADRES to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

# 13.9 Connection Considerations Applicable Devices 72/73/73A/74/74A/76/77

If the input voltage exceeds the rail values (VSS or VDD) by greater than 0.2V, then the accuracy of the conversion is out of specification.

An external RC filter is sometimes added for anti-aliasing of the input signal. The R component should be selected to ensure that the total source impedance is kept under the 10 k $\Omega$  recommended specification. Any external components connected (via hi-impedance) to an analog input pin (capacitor, zener diode, etc.) should have very little leakage current at the pin.

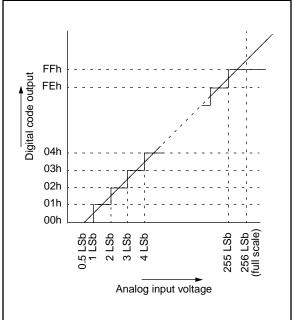

### 13.10 Transfer Function Applicable Devices 72 73 73 74 74 76 77

The ideal transfer function of the A/D converter is as follows: the first transition occurs when the analog input voltage (VAIN) is Analog VREF/256 (Figure 13-5).

### FIGURE 13-5: A/D TRANSFER FUNCTION

### 13.11 References

A very good reference for understanding A/D converters is the "Analog-Digital Conversion Handbook" third edition, published by Prentice Hall (ISBN 0-13-03-2848-0).

### 17.2 DC Characteristics: PIC16LC72-04 (Commercial, Industrial)

| DC CHA                | ARACTERISTICS                                                    |               |             | ard Ope<br>ing tem |              |                | itions (unless otherwise stated)<br>$0^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial and<br>$C \leq TA \leq +70^{\circ}C$ for commercial                           |

|-----------------------|------------------------------------------------------------------|---------------|-------------|--------------------|--------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.          | Characteristic                                                   | Sym           | Min         | Тур†               | Max          | Units          | Conditions                                                                                                                                                              |

| D001                  | Supply Voltage                                                   | Vdd           | 2.5         | -                  | 6.0          | V              | LP, XT, RC osc configuration (DC - 4 MHz)                                                                                                                               |

| D002*                 | RAM Data Retention Volt-<br>age (Note 1)                         | Vdr           | -           | 1.5                | -            | V              |                                                                                                                                                                         |

| D003                  | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR          | -           | Vss                | -            | V              | See section on Power-on Reset for details                                                                                                                               |

| D004*                 | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | Svdd          | 0.05        | -                  | -            | V/ms           | See section on Power-on Reset for details                                                                                                                               |

| D005                  | Brown-out Reset Voltage                                          | Bvdd          | 3.7         | 4.0                | 4.3          | V              | BODEN bit in configuration word enabled                                                                                                                                 |

| D010                  | Supply Current<br>(Note 2,5)                                     | IDD           | -           | 2.0                | 3.8          | mA             | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                                                           |

| D010A                 |                                                                  |               | -           | 22.5               | 48           | μA             | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                                                                                         |

| D015*                 | Brown-out Reset Current (Note 6)                                 | $\Delta$ IBOR | -           | 350                | 425          | μA             | BOR enabled VDD = 5.0V                                                                                                                                                  |

| D020<br>D021<br>D021A | Power-down Current<br>(Note 3,5)                                 | IPD           | -<br>-<br>- | 7.5<br>0.9<br>0.9  | 30<br>5<br>5 | μΑ<br>μΑ<br>μΑ | $VDD = 3.0V, WDT enabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 3.0V, WDT disabled, 0^{\circ}C to +70^{\circ}C$ $VDD = 3.0V, WDT disabled, -40^{\circ}C to +85^{\circ}C$ |

| D023*                 | Brown-out Reset Current<br>(Note 6)                              | $\Delta$ IBOR | -           | 350                | 425          | μA             | BOR enabled VDD = 5.0V                                                                                                                                                  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption. The test conditions for all IDD measurements in active operation mode are:

$OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD <math>\overline{MCLR} = VDD; WDT$  enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

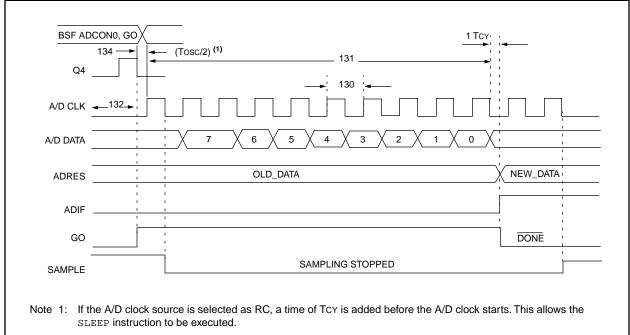

### FIGURE 17-11: A/D CONVERSION TIMING

### TABLE 17-11: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym  | Characteristic                                       |                              | Min    | Тур†     | Мах | Units | Conditions                                                                                                                                                                                                                   |

|--------------|------|------------------------------------------------------|------------------------------|--------|----------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D clock period                                     | PIC16 <b>C</b> 72            | 1.6    | _        | _   | μs    | Tosc based, VREF ≥ 3.0V                                                                                                                                                                                                      |

|              |      |                                                      | PIC16 <b>LC</b> 72           | 2.0    | —        | —   | μs    | Tosc based, VREF full range                                                                                                                                                                                                  |

|              |      |                                                      | PIC16 <b>C</b> 72            | 2.0    | 4.0      | 6.0 | μs    | A/D RC Mode                                                                                                                                                                                                                  |

|              |      |                                                      | PIC16 <b>LC</b> 72           | 3.0    | 6.0      | 9.0 | μs    | A/D RC Mode                                                                                                                                                                                                                  |

| 131          | TCNV | Conversion time (not including S/H<br>time) (Note 1) |                              | _      | 9.5      | —   | TAD   |                                                                                                                                                                                                                              |

| 132          | TACQ | Acquisition time                                     |                              | Note 2 | 20       | _   | μs    |                                                                                                                                                                                                                              |

|              |      |                                                      |                              | 5*     | _        | _   | μs    | The minimum time is the amplifier<br>settling time. This may be used if<br>the "new" input voltage has not<br>changed by more than 1 LSb (i.e.<br>20.0 mV @ 5.12V) from the last<br>sampled voltage (as stated on<br>CHOLD). |

| 134          | TGO  | Q4 to A/D clock start                                |                              | _      | Tosc/2 § | _   | _     | If the A/D clock source is selected<br>as RC, a time of TCY is added<br>before the A/D clock starts. This<br>allows the SLEEP instruction to be<br>executed.                                                                 |

| 135          | Tswc | Switching from conve                                 | $rt \rightarrow sample time$ | 1.5 §  |          | _   | TAD   |                                                                                                                                                                                                                              |

These parameters are characterized but not tested.

t Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 13.1 for min conditions.

### TABLE 18-13: A/D CONVERTER CHARACTERISTICS:

### PIC16C73/74-04 (Commercial, Industrial) PIC16C73/74-10 (Commercial, Industrial) PIC16C73/74-20 (Commercial, Industrial) PIC16LC73/74-04 (Commercial, Industrial)

| Param<br>No. | Sym  | Characteristic                               |                       | Min       | Тур†       | Мах        | Units | Conditions                                                                                                  |

|--------------|------|----------------------------------------------|-----------------------|-----------|------------|------------|-------|-------------------------------------------------------------------------------------------------------------|

| A01          | Nr   | Resolution                                   |                       | _         | _          | 8-bits     | bit   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A02          | Eabs | Total Absolute error                         |                       | _         | _          | <±1        | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A03          | EIL  | Integral linearity error                     |                       |           | —          | <±1        | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A04          | Edl  | Differential linearity errol                 |                       | _         | —          | <±1        | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A05          | EFS  | Full scale error                             |                       | _         | _          | <±1        | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A06          | EOFF | Offset error                                 |                       | _         | —          | <±1        | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A10          | —    | Monotonicity                                 |                       | —         | guaranteed | —          | _     | $VSS \leq VAIN \leq VREF$                                                                                   |

| A20          | VREF | Reference voltage                            |                       | 3.0V      | —          | Vdd + 0.3  | V     |                                                                                                             |

| A25          | VAIN | Analog input voltage                         |                       | Vss - 0.3 | —          | Vref + 0.3 | V     |                                                                                                             |

| A30          | ZAIN | Recommended impedar<br>analog voltage source | ce of                 | _         | —          | 10.0       | kΩ    |                                                                                                             |

| A40          | IAD  | A/D conversion current                       | PIC16 <b>C</b> 73/74  | _         | 180        | —          | μΑ    | Average current consump-                                                                                    |

|              |      | (VDD)                                        | PIC16 <b>LC</b> 73/74 | —         | 90         | _          | μΑ    | tion when A/D is on.<br>(Note 1)                                                                            |

| A50          | IREF | VREF input current (Note 2)                  |                       | 10        | _          | 1000       | μΑ    | During VAIN acquisition.<br>Based on differential of<br>VHOLD to VAIN to charge<br>CHOLD, see Section 13.1. |

|              |      | so paramotore are obarac                     |                       | _         | _          | 10         | μA    | During A/D Conversion cycle                                                                                 |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

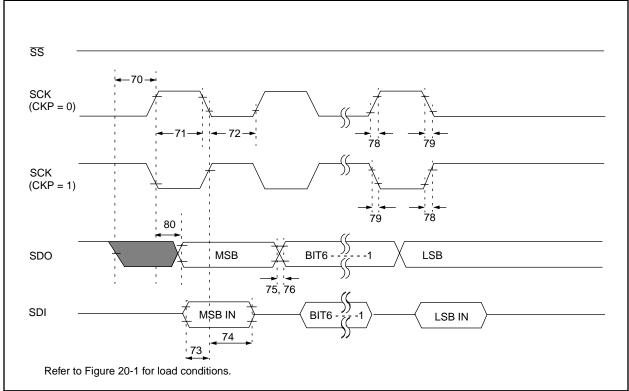

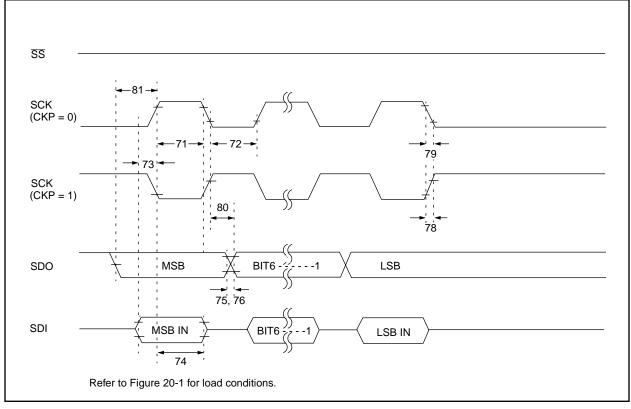

### FIGURE 20-9: SPI MASTER MODE TIMING (CKE = 0)

### FIGURE 20-10: SPI MASTER MODE TIMING (CKE = 1)

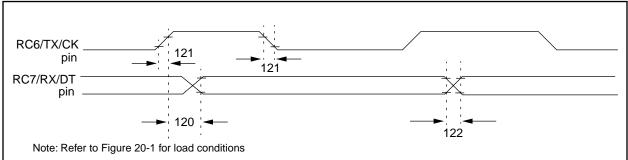

### FIGURE 20-15: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

### TABLE 20-11: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Sym           | Characteristic                                                |                                               | Min | Тур† | Мах       | Units    | Conditions |

|--------------|---------------|---------------------------------------------------------------|-----------------------------------------------|-----|------|-----------|----------|------------|

| 120          | TckH2dtV      | SYNC XMIT (MASTER &<br>SLAVE)<br>Clock high to data out valid | PIC16 <b>C</b> 76/77<br>PIC16 <b>LC</b> 76/77 | _   | _    | 80<br>100 | ns<br>ns |            |

| 121          | Tckrf         | Clock out rise time and fall time                             | PIC16 <b>C</b> 76/77                          |     |      | 45        | ns       |            |

|              | (Master Mode) |                                                               | PIC16 <b>LC</b> 76/77                         | —   |      | 50        | ns       |            |

| 122          | Tdtrf         | Data out rise time and fall time                              | PIC16 <b>C</b> 76/77                          | —   | -    | 45        | ns       |            |

|              |               |                                                               | PIC16 <b>LC</b> 76/77                         | —   | —    | 50        | ns       |            |

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

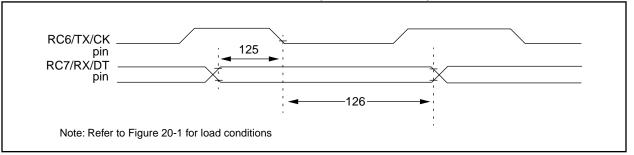

### FIGURE 20-16: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

### TABLE 20-12: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                                 | Min | Тур† | Мах | Units | Conditions |

|------------------|----------|--------------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data setup before CK $\downarrow$ (DT setup time) | 15  |      | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                 | 15  | _    | _   | ns    |            |

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### TABLE 20-13: A/D CONVERTER CHARACTERISTICS:

PIC16C76/77-04 (Commercial, Industrial, Extended) PIC16C76/77-10 (Commercial, Industrial, Extended) PIC16C76/77-20 (Commercial, Industrial, Extended) PIC16LC76/77-04 (Commercial, Industrial)

| Param<br>No. | Sym  | Characteristic                                 |                       | Min       | Тур†       | Мах        | Units | Conditions                                                                                                  |

|--------------|------|------------------------------------------------|-----------------------|-----------|------------|------------|-------|-------------------------------------------------------------------------------------------------------------|

| A01          | NR   | Resolution                                     |                       |           |            | 8-bits     | bit   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A02          | EABS | Total Absolute error                           |                       |           | _          | <±1        | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A03          | EIL  | Integral linearity error                       |                       | _         | _          | <±1        | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A04          | EDL  | Differential linearity error                   |                       | —         | _          | <±1        | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A05          | EFS  | Full scale error                               |                       | —         | —          | <±1        | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A06          | EOFF | Offset error                                   |                       | _         | _          | <±1        | LSb   | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A10          | —    | Monotonicity                                   |                       | —         | guaranteed | _          | _     | $VSS \leq VAIN \leq VREF$                                                                                   |

| A20          | Vref | Reference voltage                              |                       | 3.0V      | —          | Vdd + 0.3  | V     |                                                                                                             |

| A25          | VAIN | Analog input voltage                           |                       | Vss - 0.3 | —          | Vref + 0.3 | V     |                                                                                                             |

| A30          | ZAIN | Recommended impedance of analog voltage source |                       |           | _          | 10.0       | kΩ    |                                                                                                             |

| A40          | IAD  | A/D conversion current                         | PIC16 <b>C</b> 76/77  | —         | 180        | _          | μΑ    | Average current consump-                                                                                    |

|              |      | (VDD)                                          | PIC16 <b>LC</b> 76/77 | —         | 90         |            | μΑ    | tion when A/D is on.<br>(Note 1)                                                                            |

| A50          | IREF | VREF input current (Note 2)                    |                       | 10        | _          | 1000       | μA    | During VAIN acquisition.<br>Based on differential of<br>VHOLD to VAIN to charge<br>CHOLD, see Section 13.1. |

|              |      |                                                |                       | —         | —          | 10         | μA    | During A/D Conversion cycle                                                                                 |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

Applicable Devices

72

73

73A

74

74A

76

77

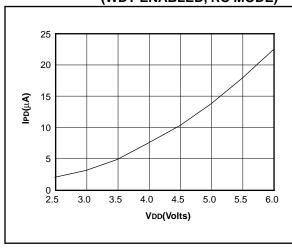

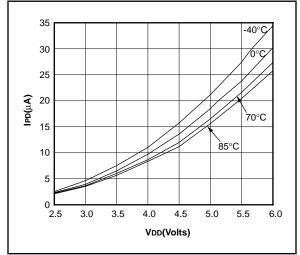

FIGURE 21-3: TYPICAL IPD vs. VDD @ 25°C (WDT ENABLED, RC MODE)

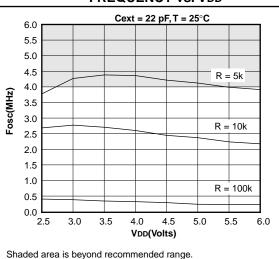

### FIGURE 21-5: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

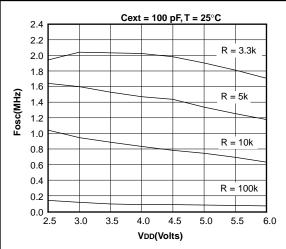

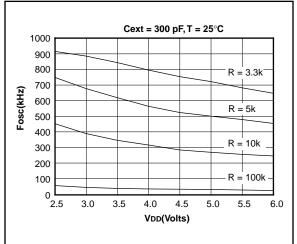

FIGURE 21-7: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

### 22.0 PACKAGING INFORMATION

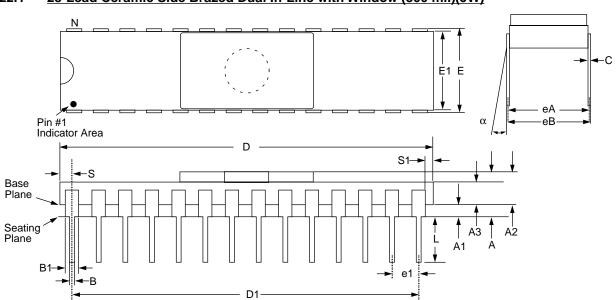

### 22.1 28-Lead Ceramic Side Brazed Dual In-Line with Window (300 mil)(JW)

| Package Group: Ceramic Side Brazed Dual In-Line (CER) |            |             |           |        |       |       |  |  |

|-------------------------------------------------------|------------|-------------|-----------|--------|-------|-------|--|--|

| Cumhal                                                |            | Millimeters |           | Inches |       |       |  |  |

| Symbol                                                | Min        | Мах         | Notes     | Min    | Max   | Notes |  |  |

| α                                                     | <b>0</b> ° | 10°         |           | 0°     | 10°   |       |  |  |

| А                                                     | 3.937      | 5.030       |           | 0.155  | 0.198 |       |  |  |

| A1                                                    | 1.016      | 1.524       |           | 0.040  | 0.060 |       |  |  |

| A2                                                    | 2.921      | 3.506       |           | 0.115  | 0.138 |       |  |  |

| A3                                                    | 1.930      | 2.388       |           | 0.076  | 0.094 |       |  |  |

| В                                                     | 0.406      | 0.508       |           | 0.016  | 0.020 |       |  |  |

| B1                                                    | 1.219      | 1.321       | Typical   | 0.048  | 0.052 |       |  |  |

| С                                                     | 0.228      | 0.305       | Typical   | 0.009  | 0.012 |       |  |  |

| D                                                     | 35.204     | 35.916      |           | 1.386  | 1.414 |       |  |  |

| D1                                                    | 32.893     | 33.147      | Reference | 1.295  | 1.305 |       |  |  |

| E                                                     | 7.620      | 8.128       |           | 0.300  | 0.320 |       |  |  |

| E1                                                    | 7.366      | 7.620       |           | 0.290  | 0.300 |       |  |  |

| e1                                                    | 2.413      | 2.667       | Typical   | 0.095  | 0.105 |       |  |  |

| eA                                                    | 7.366      | 7.874       | Reference | 0.290  | 0.310 |       |  |  |

| eB                                                    | 7.594      | 8.179       |           | 0.299  | 0.322 |       |  |  |

| L                                                     | 3.302      | 4.064       |           | 0.130  | 0.160 |       |  |  |

| Ν                                                     | 28         | 28          |           | 28     | 28    |       |  |  |

| S                                                     | 1.143      | 1.397       |           | 0.045  | 0.055 |       |  |  |

| S1                                                    | 0.533      | 0.737       |           | 0.021  | 0.029 |       |  |  |

# PIC16C7X

| Figure 12-5:                 | RX Pin Sampling Scheme, BRGH = 1                         |

|------------------------------|----------------------------------------------------------|

|                              | (PIC16C73/73A/74/74A) 104                                |

| Figure 12-6:                 | RX Pin Sampling Scheme,                                  |

|                              | BRGH = 0 OR BRGH = 1 (                                   |

|                              | PIC16C76/77) 105                                         |

| Figure 12-7:                 | USART Transmit Block Diagram 106                         |

| Figure 12-8:                 | Asynchronous Master Transmission 107                     |

| Figure 12-9:                 | Asynchronous Master Transmission                         |

| Figure 12-10:                | (Back to Back)107<br>USART Receive Block Diagram108      |

| Figure 12-10.                | Asynchronous Reception                                   |

| Figure 12-12:                | Synchronous Transmission                                 |

| Figure 12-13:                | Synchronous Transmission                                 |

|                              | (Through TXEN) 111                                       |

| Figure 12-14:                | Synchronous Reception                                    |

| 0                            | (Master Mode, SREN)113                                   |

| Figure 13-1:                 | ADCON0 Register (Address 1Fh) 117                        |

| Figure 13-2:                 | ADCON1 Register (Address 9Fh) 118                        |

| Figure 13-3:                 | A/D Block Diagram119                                     |

| Figure 13-4:                 | Analog Input Model 120                                   |

| Figure 13-5:                 | A/D Transfer Function 125                                |

| Figure 13-6:                 | Flowchart of A/D Operation126                            |

| Figure 14-1:                 | Configuration Word for                                   |

|                              | PIC16C73/74129                                           |

| Figure 14-2:                 | Configuration Word for                                   |

| <b>F</b> inance <b>44.0</b>  | PIC16C72/73A/74A/76/77130                                |

| Figure 14-3:                 | Crystal/Ceramic Resonator                                |

|                              | Operation (HS, XT or LP                                  |

| Figure 14-4:                 | OSC Configuration)                                       |

| Figure 14-4.                 | (HS, XT or LP OSC Configuration) 131                     |

| Figure 14-5:                 | External Parallel Resonant Crystal                       |

| rigulo i i o.                | Oscillator Circuit                                       |

| Figure 14-6:                 | External Series Resonant Crystal                         |

| 3                            | Oscillator Circuit 132                                   |

| Figure 14-7:                 | RC Oscillator Mode 132                                   |

| Figure 14-8:                 | Simplified Block Diagram of On-chip                      |

|                              | Reset Circuit 133                                        |

| Figure 14-9:                 | Brown-out Situations 134                                 |

| Figure 14-10:                | Time-out Sequence on Power-up                            |

|                              | (MCLR not Tied to VDD): Case 1                           |

| Figure 14-11:                | Time-out Sequence on Power-up                            |

| <b>Figure 11 10</b>          | (MCLR Not Tied To VDD): Case 2                           |

| Figure 14-12:                | Time-out Sequence on Power-up                            |

| Figure 14-13:                | (MCLR Tied to VDD)139<br>External Power-on Reset Circuit |

| 1 igule 14-13.               | (for Slow VDD Power-up)                                  |

| Figure 14-14:                | External Brown-out Protection                            |

|                              | Circuit 1 140                                            |

| Figure 14-15:                | External Brown-out Protection                            |

| U U                          | Circuit 2140                                             |

| Figure 14-16:                | Interrupt Logic 142                                      |

| Figure 14-17:                | INT Pin Interrupt Timing142                              |

| Figure 14-18:                | Watchdog Timer Block Diagram 144                         |

| Figure 14-19:                | Summary of Watchdog                                      |

|                              | Timer Registers                                          |

| Figure 14-20:                | Wake-up from Sleep Through                               |

| Figure 44.04                 | Interrupt                                                |

| Figure 14-21:                | Typical In-Circuit Serial                                |

| Figuro 15 1                  | Programming Connection                                   |

| Figure 15-1:<br>Figure 17-1: | Load Conditions 172                                      |

| Figure 17-1.<br>Figure 17-2: | External Clock Timing                                    |

| Figure 17-2:                 | CLKOUT and I/O Timing                                    |

| 0                            |                                                          |

| <b>E</b> : <b>4- 4</b> |                                                  |

|------------------------|--------------------------------------------------|

| Figure 17-4:           | Reset, Watchdog Timer, Oscillator                |

|                        | Start-up Timer and Power-up Timer                |

|                        | Timing175                                        |

| Figure 17-5:           | Brown-out Reset Timing175                        |

| Figure 17-6:           | Timer0 and Timer1 External                       |

|                        | Clock Timings176                                 |

| Figure 17-7:           | Capture/Compare/PWM                              |

|                        | Timings (CCP1)177                                |

| Figure 17-8:           | SPI Mode Timing178                               |

| Figure 17-9:           | I <sup>2</sup> C Bus Start/Stop Bits Timing179   |

| Figure 17-10:          | I <sup>2</sup> C Bus Data Timing180              |

| Figure 17-11:          | A/D Conversion Timing182                         |

| Figure 18-1:           | Load Conditions188                               |

| Figure 18-2:           | External Clock Timing189                         |

| Figure 18-3:           | CLKOUT and I/O Timing190                         |

| Figure 18-4:           | Reset, Watchdog Timer,                           |

| 0                      | Oscillator Start-up Timer and Power-up Tim-      |