#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | $4V \sim 6V$                                                             |

| Data Converters            | A/D 8x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c77-20i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### FIGURE 4-6: PIC16C76/77 REGISTER FILE MAP

| Indirect addr.(*)                          | 00h       | Indirect addr.(*)                          | 80h        | Indirect addr.(*)                          | 100h         | Indirect addr.(*)                          | 180        |

|--------------------------------------------|-----------|--------------------------------------------|------------|--------------------------------------------|--------------|--------------------------------------------|------------|

| TMR0                                       | 01h       | OPTION                                     | 81h        | TMR0                                       | 101h         | OPTION                                     | 181        |

| PCL                                        | 02h       | PCL                                        | 82h        | PCL                                        | 102h         | PCL                                        | 182        |

| STATUS                                     | 03h       | STATUS                                     | 83h        | STATUS                                     | 103h         | STATUS                                     | 183        |

| FSR                                        | 04h       | FSR                                        | 84h        | FSR                                        | 104h         | FSR                                        | 184        |

| PORTA                                      | 05h       | TRISA                                      | 85h        |                                            | 105h         |                                            | 185        |

| PORTB                                      | 06h       | TRISB                                      | 86h        | PORTB                                      | 106h         | TRISB                                      | 186        |

| PORTC                                      | 07h       | TRISC                                      | 87h        |                                            | 107h         |                                            | 187        |

| PORTD (1)                                  | 08h       | TRISD <sup>(1)</sup>                       | 88h        |                                            | 108h         |                                            | 188        |

| PORTE (1)                                  | 09h       | TRISE (1)                                  | 89h        |                                            | 109h         |                                            | 189        |

| PCLATH                                     | 0Ah       | PCLATH                                     | 8Ah        | PCLATH                                     | 10Ah         | PCLATH                                     | 18A        |

| INTCON                                     | 0Bh       | INTCON                                     | 8Bh        | INTCON                                     | 10Bh         | INTCON                                     | 18B        |

| PIR1                                       | 0Ch       | PIE1                                       | 8Ch        |                                            | 10Ch         |                                            | 1 18C      |

| PIR2                                       | 0Dh       | PIE2                                       | 8Dh        |                                            | 10Dh         |                                            | 18D        |

| TMR1L                                      | 0Eh       | PCON                                       | 8Eh        |                                            | 10Eh         |                                            | 18E        |

| TMR1H                                      | 0Fh       |                                            | 8Fh        |                                            | 10Fh         |                                            | 18F        |

| T1CON                                      | 10h       |                                            | 90h        |                                            | 110h         |                                            | 190        |

| TMR2                                       | 11h       |                                            | 91h        |                                            | 111h         |                                            | 191        |

| T2CON                                      | 12h       | PR2                                        | 92h        |                                            | 112h         |                                            | 192        |

| SSPBUF                                     | 13h       | SSPADD                                     | 93h        |                                            | 113h         |                                            | 193        |

| SSPCON                                     | 14h       | SSPSTAT                                    | 94h        |                                            | 114h         |                                            | 194        |

| CCPR1L                                     | 15h       |                                            | 95h        |                                            | 115h         |                                            | 195        |

| CCPR1H                                     | 16h       |                                            | 96h        |                                            | 116h         |                                            | 196        |

| CCP1CON                                    | 17h       |                                            | 97h        | General                                    | 117h         | General                                    | 197        |

| RCSTA                                      | 18h       | TXSTA                                      | 98h        | Purpose<br>Register                        | 118h         | Purpose<br>Register                        | 198        |

| TXREG                                      | 19h       | SPBRG                                      | 99h        | 16 Bytes                                   | 119h         | 16 Bytes                                   | 199        |

| RCREG                                      | 1Ah       |                                            | 9Ah        |                                            | 11Ah         |                                            | 19A        |

| CCPR2L                                     | 1Bh       |                                            | 9Bh        |                                            | 11Bh         |                                            | 19B        |

| CCPR2H                                     | 1Ch       |                                            | 9Ch        |                                            | 11Ch         |                                            | 19C        |

| CCP2CON                                    | 1Dh       |                                            | 9Dh        |                                            | 11Dh         |                                            | 19D        |

| ADRES                                      | 1Eh       |                                            | 9Eh        |                                            | 11Eh         |                                            | 19E        |

| ADCON0                                     | 1Fh       | ADCON1                                     | 9Fh        |                                            | 11Fh         |                                            | 19F        |

|                                            | 20h       |                                            | A0h        |                                            | 120h         |                                            | 1A0        |

| General<br>Purpose<br>Register<br>96 Bytes |           | General<br>Purpose<br>Register<br>80 Bytes | EFh        | General<br>Purpose<br>Register<br>80 Bytes | 16Fh         | General<br>Purpose<br>Register<br>80 Bytes | 1EF        |

| -                                          | 7Fh       | accesses<br>70h-7Fh                        | F0h<br>FFh | accesses<br>70h-7Fh                        | 170h<br>17Fh | accesses<br>70h - 7Fh                      | ] 1F0 <br> |

| Bank 0                                     |           | Bank 1                                     |            | Bank 2                                     |              | Bank 3                                     |            |

| _                                          | nted data | memory locations, re                       |            |                                            |              | Bank 3                                     |            |

**Note:** The upper 16 bytes of data memory in banks 1, 2, and 3 are mapped in Bank 0. This may require relocation of data memory usage in the user application code if upgrading to the PIC16C76/77.

#### 4.2.2.3 INTCON REGISTER

Applicable Devices

72 73 73A 74 74A 76 77

The INTCON Register is a readable and writable register which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts.

#### FIGURE 4-9: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

**Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

| R/W-0   | R/W-0     | R/W-0                                      | R/W-0       | R/W-0        | R/W-0           | R/W-0       | R/W-x        | <b></b>                                                                                                              |

|---------|-----------|--------------------------------------------|-------------|--------------|-----------------|-------------|--------------|----------------------------------------------------------------------------------------------------------------------|

| GIE     | PEIE      | TOIE                                       | INTE        | RBIE         | TOIF            | INTF        | RBIF         | R = Readable bit                                                                                                     |

| bit7    |           |                                            |             |              |                 |             | bit0         | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |

| bit 7:  |           | obal Interi<br>es all un-r<br>les all inte | nasked in   |              |                 |             |              |                                                                                                                      |

| bit 6:  |           | ipheral Int<br>es all un-r<br>les all peri | nasked pe   | ripheral ir  | iterrupts       |             |              |                                                                                                                      |

| bit 5:  |           | R0 Overflo<br>es the TM<br>les the TM      | R0 interru  | pt           | bit             |             |              |                                                                                                                      |

| bit 4:  |           | 0/INT Exte<br>es the RB<br>les the RE      | 0/INT exte  | ernal interr | upt             |             |              |                                                                                                                      |

| bit 3:  | 1 = Enabl | Port Char<br>es the RB<br>les the RE       | port char   | ge interru   | pt              |             |              |                                                                                                                      |

| bit 2:  | 1 = TMR0  | R0 Overflo<br>) register h<br>) register c | has overflo | wed (mus     | t be cleare     | d in softwa | are)         |                                                                                                                      |

| bit 1:  |           |                                            | ternal inte | errupt occu  | urred (must     | be cleare   | d in softwa  | re)                                                                                                                  |

| bit 0:  |           | st one of t                                | he RB7:R    | B4 pins cł   |                 |             | e cleared in | software)                                                                                                            |

| Note 1: | may be u  |                                            | ally re-ena | bled by th   | <b>e</b> RETFIE |             |              | it is being cleared, the GIE bit<br>'s Interrupt Service Routine.                                                    |

| global  |           | GIE (INTCO                                 |             |              |                 |             |              | corresponding enable bit or the rupt flag bits are clear prior to                                                    |

4.2.2.4 PIE1 REGISTER

Applicable Devices

72 73 73A 74 74A 76 77

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

This register contains the individual enable bits for the peripheral interrupts.

#### FIGURE 4-10: PIE1 REGISTER PIC16C72 (ADDRESS 8Ch)

| U-0      | R/W-0                                                                                                                                                 | U-0                        | U-0                                      | R/W-0      | R/W-0  | R/W-0  | R/W-0  |                                                                                                                        |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------|------------|--------|--------|--------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|          | ADIE                                                                                                                                                  | —                          | —                                        | SSPIE      | CCP1IE | TMR2IE | TMR1IE | R = Readable bit                                                                                                       |  |  |  |  |

| bit7     |                                                                                                                                                       |                            |                                          |            |        |        | bit0   | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>- n = Value at POR reset</li> </ul> |  |  |  |  |

| bit 7:   | Unimpler                                                                                                                                              | Unimplemented: Read as '0' |                                          |            |        |        |        |                                                                                                                        |  |  |  |  |

| bit 6:   | ADIE: A/D Converter Interrupt Enable bit<br>1 = Enables the A/D interrupt<br>0 = Disables the A/D interrupt                                           |                            |                                          |            |        |        |        |                                                                                                                        |  |  |  |  |

| bit 5-4: | Unimpler                                                                                                                                              | nented: R                  | ead as '0'                               |            |        |        |        |                                                                                                                        |  |  |  |  |

| bit 3:   | SSPIE: Synchronous Serial Port Interrupt Enable bit<br>1 = Enables the SSP interrupt<br>0 = Disables the SSP interrupt                                |                            |                                          |            |        |        |        |                                                                                                                        |  |  |  |  |

| bit 2:   | <b>CCP1IE</b> : CCP1 Interrupt Enable bit<br>1 = Enables the CCP1 interrupt<br>0 = Disables the CCP1 interrupt                                        |                            |                                          |            |        |        |        |                                                                                                                        |  |  |  |  |

| bit 1:   | <b>TMR2IE</b> : TMR2 to PR2 Match Interrupt Enable bit<br>1 = Enables the TMR2 to PR2 match interrupt<br>0 = Disables the TMR2 to PR2 match interrupt |                            |                                          |            |        |        |        |                                                                                                                        |  |  |  |  |

| bit 0:   | 1 = Enabl                                                                                                                                             | es the TM                  | erflow Inte<br>R1 overflo<br>IR1 overflo | w interrup | ot     |        |        |                                                                                                                        |  |  |  |  |

4.2.2.7 PIR2 REGISTER

Applicable Devices

72 73 73A 74 74A 76 77

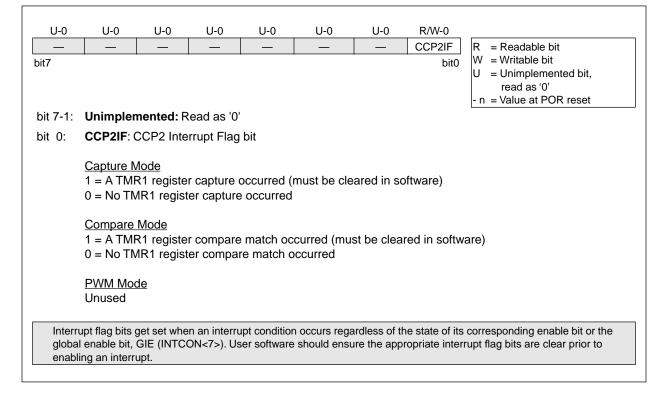

This register contains the CCP2 interrupt flag bit.

Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 4-15: PIR2 REGISTER (ADDRESS 0Dh)

### 5.6 <u>I/O Programming Considerations</u> Applicable Devices 72 73 73A 74 74A 76 77

#### 5.6.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched to an output, the content of the data latch may now be unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-4 shows the effect of two sequential readmodify-write instructions on an I/O port.

#### EXAMPLE 5-4: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT settings: PORTB<7:4> Inputs

; PORTB<3:0> Outputs

;PORTB<7:6> have external pull-ups and are

;not connected to other circuitry

| i |     |         |     |   |      |       |           |  |

|---|-----|---------|-----|---|------|-------|-----------|--|

| ; |     |         |     |   | PORT | latch | PORT pins |  |

| ; |     |         |     |   |      |       |           |  |

|   | BCF | PORTB,  | 7   | ; | 01pp | pppp  | 11pp pppp |  |

|   | BCF | PORTB,  | 6   | ; | 10pp | pppp  | llpp pppp |  |

|   | BSF | STATUS, | RP0 | ; |      |       |           |  |

|   | BCF | TRISB,  | 7   | ; | 10pp | pppp  | 11pp pppp |  |

|   | BCF | TRISB,  | 6   | ; | 10pp | pppp  | 10pp pppp |  |

| ; |     |         |     |   |      |       |           |  |

|   |     |         |     |   |      |       |           |  |

;Note that the user may have expected the ;pin values to be 00pp ppp. The 2nd BCF ;caused RB7 to be latched as the pin value ;(high).

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

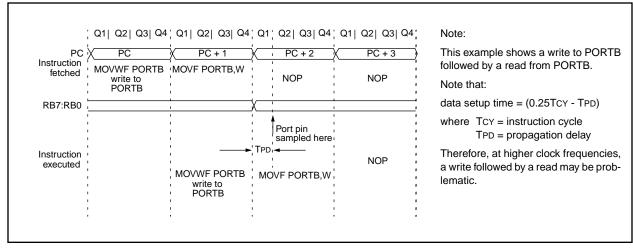

#### 5.6.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-10). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/ O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

#### FIGURE 5-10: SUCCESSIVE I/O OPERATION

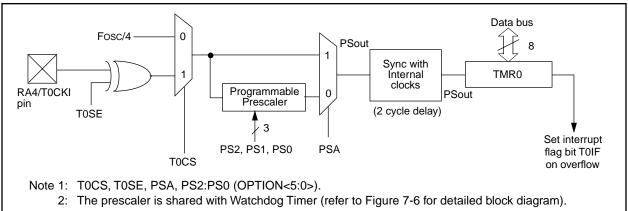

# 7.0 TIMER0 MODULE Applicable Devices 727373A7474A7677

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 7-1 is a simplified block diagram of the Timer0 module.

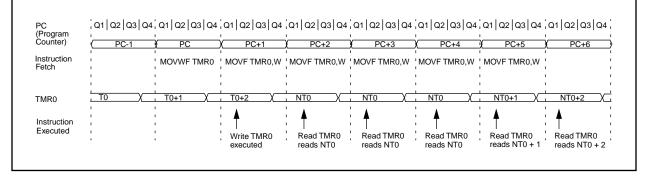

Timer mode is selected by clearing bit TOCS (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION<5>). In counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0

FIGURE 7-1: TIMER0 BLOCK DIAGRAM

Source Edge Select bit TOSE (OPTION<4>). Clearing bit TOSE selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.2.

The prescaler is mutually exclusively shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by control bit PSA (OPTION<3>). Clearing bit PSA will assign the prescaler to the Timer0 module. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable. Section 7.3 details the operation of the prescaler.

#### 7.1 <u>Timer0 Interrupt</u>

Applicable Devices

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP since the timer is shut off during SLEEP. See Figure 7-4 for Timer0 interrupt timing.

NOTES:

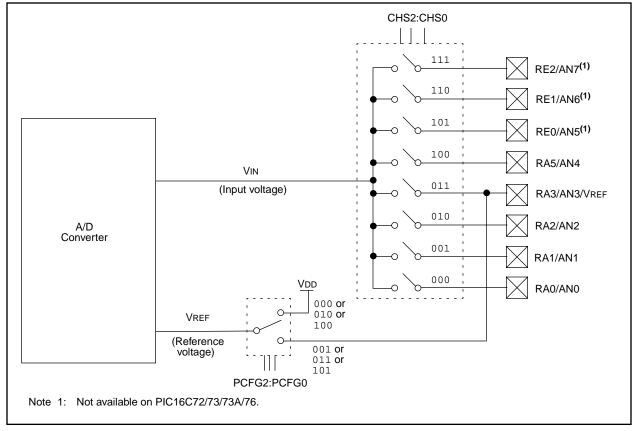

The ADRES register contains the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRES register, the GO/DONE bit (ADCON0<2>) is cleared, and A/D interrupt flag bit ADIF is set. The block diagrams of the A/D module are shown in Figure 13-3.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 13.1. After this acquisition time has elapsed the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins / voltage reference / and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set GIE bit

#### FIGURE 13-3: A/D BLOCK DIAGRAM

- 3. Wait the required acquisition time.

- 4. Start conversion:Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

Polling for the GO/DONE bit to be cleared

- OR

- Waiting for the A/D interrupt

- Read A/D Result register (ADRES), clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before next acquisition starts.

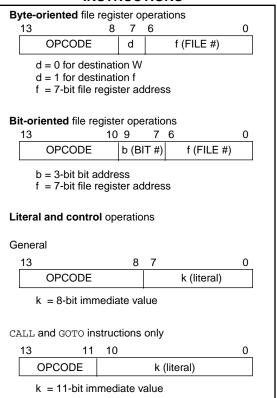

# 15.0 INSTRUCTION SET SUMMARY

Each PIC16CXX instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXX instruction set summary in Table 15-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 15-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

# TABLE 15-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| x             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                   |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| PCLATH        | Program Counter High Latch                                                                                                                                                     |

| GIE           | Global Interrupt Enable bit                                                                                                                                                    |

| WDT           | Watchdog Timer/Counter                                                                                                                                                         |

| TO            | Time-out bit                                                                                                                                                                   |

| PD            | Power-down bit                                                                                                                                                                 |

| dest          | Destination either the W register or the specified register file location                                                                                                      |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| <>            | Register bit field                                                                                                                                                             |

| ∈             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 15-2 lists the instructions recognized by the MPASM assembler.

Figure 15-1 shows the general formats that the instructions can have.

**Note:** To maintain upward compatibility with future PIC16CXX products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

# FIGURE 15-1: GENERAL FORMAT FOR INSTRUCTIONS

| INCFSZ            | Increment f, Skip if 0                                                                                                                                                                                                    | IORLW             | Inclusive OR Literal with W                                                 |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------|

| Syntax:           | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                               | Syntax:           | [ <i>label</i> ] IORLW k                                                    |

| Operands:         | $0 \le f \le 127$                                                                                                                                                                                                         | Operands:         | $0 \le k \le 255$                                                           |

|                   | d ∈ [0,1]                                                                                                                                                                                                                 | Operation:        | (W) .OR. $k \rightarrow$ (W)                                                |

| Operation:        | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                | Status Affected:  | Z                                                                           |

| Status Affected:  | None                                                                                                                                                                                                                      | Encoding:         | 11 1000 kkkk kkkk                                                           |

| Encoding:         | 00 1111 dfff fff                                                                                                                                                                                                          | Description:      | The contents of the W register is OR'ed with the eight bit literal 'k'. The |

| Description:      | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed in                                                                                                                                    |                   | result is placed in the W register.                                         |

|                   | the W register. If 'd' is 1 the result is                                                                                                                                                                                 | Words:            | 1                                                                           |

|                   | placed back in register 'f'.<br>If the result is 1, the next instruction is                                                                                                                                               | Cycles:           | 1                                                                           |

|                   | executed. If the result is 0, a NOP is executed instead making it a 2Tcy                                                                                                                                                  | Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                 |

| Words:            | instruction.                                                                                                                                                                                                              |                   | Decode Read Process Write to literal 'k' data W                             |

| Cycles:           | 1(2)                                                                                                                                                                                                                      | <b>F</b> ormula   |                                                                             |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                                                               | Example           | IORLW 0x35                                                                  |

|                   | Decode Read register 'f' Process Write to destination                                                                                                                                                                     |                   | Before Instruction<br>W = 0x9A<br>After Instruction                         |

| If Skip:          | (2nd Cycle)                                                                                                                                                                                                               |                   | W = 0xBF                                                                    |

|                   | Q1 Q2 Q3 Q4                                                                                                                                                                                                               |                   | Z = 1                                                                       |

|                   | No-<br>OperationNo-<br>OperationNo-<br>Operation                                                                                                                                                                          |                   |                                                                             |

| Example           | HERE INCFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE<br>•<br>•<br>Before Instruction<br>PC = address HERE<br>After Instruction<br>CNT = CNT + 1<br>if CNT= 0,<br>PC = address CONTINUE<br>if CNT $\neq$ 0,<br>PC = address HERE +1 |                   |                                                                             |

| RLF               | Rotate Left f th                                                                                                  | rough Ca                                     | rry                        | RRF               | Rotate Rig                                                        | ght f through                                                                                                  | Carry                                    |

|-------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------|-------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Syntax:           | [ <i>label</i> ] RLF                                                                                              | f,d                                          |                            | Syntax:           | [label] R                                                         | RRF f,d                                                                                                        |                                          |

| Operands:         | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                          |                                              |                            | Operands:         | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$ |                                                                                                                |                                          |

| Operation:        | See description                                                                                                   | below                                        |                            | Operation:        | See descrip                                                       | iption below                                                                                                   |                                          |

| Status Affected:  | С                                                                                                                 |                                              |                            | Status Affected:  | С                                                                 |                                                                                                                |                                          |

| Encoding:         | 00 1101                                                                                                           | dfff                                         | ffff                       | Encoding:         | 00                                                                | 1100 dfff                                                                                                      | ffff                                     |

| Description:      | The contents of r<br>one bit to the left<br>Flag. If 'd' is 0 the<br>W register. If 'd' is<br>back in register 'f | through the<br>result is pla<br>1 the result | Carry<br>ced in the        | Description:      | one bit to the<br>Flag. If 'd' is (                               | s of register 'f' a<br>e right through t<br>0 the result is p<br>f 'd' is 1 the resu<br>ster 'f'.<br>→ Registe | he Carry<br>aced in the<br>Ilt is placed |

| Words:            | 1                                                                                                                 |                                              |                            | Words:            | 1                                                                 |                                                                                                                |                                          |

| Cycles:           | 1                                                                                                                 |                                              |                            | Cycles:           | 1                                                                 |                                                                                                                |                                          |

| Q Cycle Activity: | Q1 Q2                                                                                                             | Q3                                           | Q4                         | Q Cycle Activity: | Q1                                                                | Q2 Q3                                                                                                          | Q4                                       |

|                   | Decode Read<br>registe<br>'f'                                                                                     | r Process<br>r data                          | Write to destination       |                   |                                                                   | Read Procest<br>register data                                                                                  | s Write to destination                   |

| Example           | RLF R                                                                                                             | EG1,0                                        |                            | Example           | RRF                                                               | REG1,0                                                                                                         |                                          |

|                   | Before Instructi<br>REG1<br>C<br>After Instructior<br>REG1<br>W<br>C                                              | = 111<br>= 0<br>= 111                        | 0 0110<br>0 0110<br>0 1100 |                   | C<br>After Instru                                                 | EG1 = 11<br>= 0<br>uction<br>EG1 = 11<br>/ = 01                                                                | 10 0110<br>10 0110<br>11 0011            |

# 16.0 DEVELOPMENT SUPPORT

#### 16.1 <u>Development Tools</u>

The PIC16/17 microcontrollers are supported with a full range of hardware and software development tools:

- PICMASTER/PICMASTER CE Real-Time In-Circuit Emulator

- ICEPIC Low-Cost PIC16C5X and PIC16CXXX In-Circuit Emulator

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- PICDEM-1 Low-Cost Demonstration Board

- PICDEM-2 Low-Cost Demonstration Board

- PICDEM-3 Low-Cost Demonstration Board

- MPASM Assembler

- MPLAB-SIM Software Simulator

- MPLAB-C (C Compiler)

- Fuzzy logic development system (*fuzzy*TECH<sup>®</sup>–MP)

#### 16.2 <u>PICMASTER: High Performance</u> <u>Universal In-Circuit Emulator with</u> <u>MPLAB IDE</u>

The PICMASTER Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for all microcontrollers in the PIC12C5XX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX families. PICMASTER is supplied with the MPLAB<sup>™</sup> Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable target probes allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the PICMASTER allows expansion to support all new Microchip microcontrollers.

The PICMASTER Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC compatible 386 (and higher) machine platform and Microsoft Windows<sup>®</sup> 3.x environment were chosen to best make these features available to you, the end user.

A CE compliant version of PICMASTER is available for European Union (EU) countries.

#### 16.3 ICEPIC: Low-cost PIC16CXXX In-Circuit Emulator

ICEPIC is a low-cost in-circuit emulator solution for the Microchip PIC16C5X and PIC16CXXX families of 8-bit OTP microcontrollers.

ICEPIC is designed to operate on PC-compatible machines ranging from 286-AT<sup>®</sup> through Pentium<sup>™</sup> based machines under Windows 3.x environment. ICEPIC features real time, non-intrusive emulation.

#### 16.4 PRO MATE II: Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for displaying error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In standalone mode the PRO MATE II can read, verify or program PIC16C5X, PIC16CXXX, PIC17CXX and PIC14000 devices. It can also set configuration and code-protect bits in this mode.

#### 16.5 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. PICSTART Plus is not recommended for production programming.

PICSTART Plus supports all PIC12C5XX, PIC14000, PIC16C5X, PIC16CXXX and PIC17CXX devices with up to 40 pins. Larger pin count devices such as the PIC16C923 and PIC16C924 may be supported with an adapter socket.

# Applicable Devices 72 73 73A 74 74A 76 77

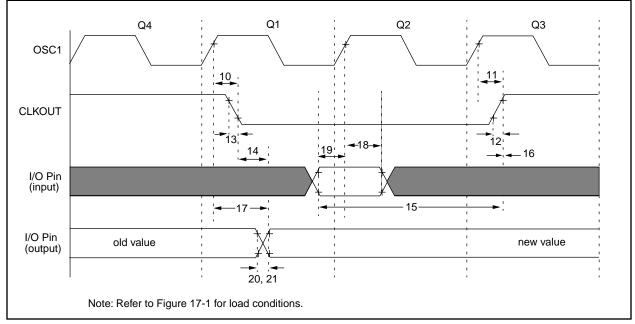

#### FIGURE 17-3: CLKOUT AND I/O TIMING

| TABLE 17-3: CLKOUT AND I/O TIMING REQUIREMENTS | ГABLE 17-3: |

|------------------------------------------------|-------------|

|------------------------------------------------|-------------|

| Parameter<br>No. | Sym      | Characteristic                                    |                     | Min        | Тур† | Мах         | Units | Conditions |

|------------------|----------|---------------------------------------------------|---------------------|------------|------|-------------|-------|------------|

| 10*              | TosH2ckL | OSC1 <sup>↑</sup> to CLKOUT↓                      |                     | _          | 75   | 200         | ns    | Note 1     |

| 11*              | TosH2ckH | OSC1 <sup>↑</sup> to CLKOUT <sup>↑</sup>          |                     | _          | 75   | 200         | ns    | Note 1     |

| 12*              | TckR     | CLKOUT rise time                                  |                     | _          | 35   | 100         | ns    | Note 1     |

| 13*              | TckF     | CLKOUT fall time                                  |                     | _          | 35   | 100         | ns    | Note 1     |

| 14*              | TckL2ioV | CLKOUT ↓ to Port out vali                         | d                   | _          | —    | 0.5Tcy + 20 | ns    | Note 1     |

| 15*              | TioV2ckH | Port in valid before CLKOU                        | T ↑                 | Tosc + 200 | -    | _           | ns    | Note 1     |

| 16*              | TckH2iol | Port in hold after CLKOUT                         | $\uparrow$          | 0          | -    | -           | ns    | Note 1     |

| 17*              | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to<br>Port out valid | _                   | 50         | 150  | ns          |       |            |

| 18*              | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to                   | PIC16 <b>C</b> 72   | 100        | -    | -           | ns    |            |

|                  |          | Port input invalid (I/O in hold time)             | PIC16 <b>LC</b> 72  | 200        | -    | _           | ns    |            |

| 19*              | TioV2osH | Port input valid to OSC11                         | (I/O in setup time) | 0          | -    | _           | ns    |            |

| 20*              | TioR     | Port output rise time                             | PIC16 <b>C</b> 72   | —          | 10   | 40          | ns    |            |

|                  |          |                                                   | PIC16 <b>LC</b> 72  | _          | —    | 80          | ns    |            |

| 21*              | TioF     | Port output fall time                             | PIC16 <b>C</b> 72   | _          | 10   | 40          | ns    |            |

|                  |          |                                                   | PIC16 <b>LC</b> 72  | _          | -    | 80          | ns    |            |

| 22††*            | Tinp     | INT pin high or low time                          |                     | Тсү        | -    | _           | ns    |            |

| 23††*            | Trbp     | RB7:RB4 change INT high                           | n or low time       | Тсү        | -    | _           | ns    |            |

$^{\ast}$  These parameters are characterized but not tested.

†Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

these parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

## Applicable Devices 72 73 73A 74 74A 76 77

19.1 DC Characteristics: PIC16C73A/74A-04 (Commercial, Industrial, Extended) PIC16C73A/74A-10 (Commercial, Industrial, Extended) PIC16C73A/74A-20 (Commercial, Industrial, Extended)

| DC CHA                         | ARACTERISTICS                                                    |               | $\begin{array}{l lllllllllllllllllllllllllllllllllll$ |                           |                      |                      |                                                                                                                                                                                                                                                                                                                                       |  |

|--------------------------------|------------------------------------------------------------------|---------------|-------------------------------------------------------|---------------------------|----------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.                   | Characteristic                                                   | Sym           | Min                                                   | Тур†                      | Max                  | Units                | Conditions                                                                                                                                                                                                                                                                                                                            |  |

| D001<br>D001A                  | Supply Voltage                                                   | Vdd           | 4.0<br>4.5                                            | -                         | 6.0<br>5.5           | V<br>V               | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                                                                                                                                                               |  |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                           | Vdr           | -                                                     | 1.5                       | -                    | V                    |                                                                                                                                                                                                                                                                                                                                       |  |

| D003                           | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR          | -                                                     | Vss                       | -                    | V                    | See section on Power-on Reset for details                                                                                                                                                                                                                                                                                             |  |

| D004*                          | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | Svdd          | 0.05                                                  | -                         | -                    | V/ms                 | See section on Power-on Reset for details                                                                                                                                                                                                                                                                                             |  |

| D005                           | Brown-out Reset Voltage                                          | Bvdd          | 3.7                                                   | 4.0                       | 4.3                  | V                    | BODEN bit in configuration word enabled                                                                                                                                                                                                                                                                                               |  |

|                                |                                                                  |               | 3.7                                                   | 4.0                       | 4.4                  | V                    | Extended Range Only                                                                                                                                                                                                                                                                                                                   |  |

| D010                           | Supply Current (Note 2,5)                                        | IDD           | -                                                     | 2.7                       | 5                    | mA                   | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                                                                                                                                                                                                                                         |  |

| D013                           |                                                                  |               | -                                                     | 10                        | 20                   | mA                   | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                                                                                                                                                                                     |  |

| D015*                          | Brown-out Reset Current<br>(Note 6)                              | $\Delta$ IBOR | -                                                     | 350                       | 425                  | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                                                                                                                                |  |

| D020<br>D021<br>D021A<br>D021B | Power-down Current<br>(Note 3,5)                                 | IPD           | -<br>-<br>-<br>-                                      | 10.5<br>1.5<br>1.5<br>2.5 | 42<br>16<br>19<br>19 | μΑ<br>μΑ<br>μΑ<br>μΑ | $\label{eq:VDD} \begin{array}{l} VDD = 4.0V, WDT \text{ enabled}, -40^\circC \text{ to } +85^\circC \\ VDD = 4.0V, WDT \text{ disabled}, -0^\circC \text{ to } +70^\circC \\ VDD = 4.0V, WDT \text{ disabled}, -40^\circC \text{ to } +85^\circC \\ VDD = 4.0V, WDT \text{ disabled}, -40^\circC \text{ to } +125^\circC \end{array}$ |  |

| D023*                          | Brown-out Reset Current<br>(Note 6)                              | $\Delta$ IBOR | -                                                     | 350                       | 425                  | μA                   | BOR enabled VDD = 5.0V                                                                                                                                                                                                                                                                                                                |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

$\overline{\text{MCLR}}$  = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

# PIC16C7X

Applicable Devices 72 73 73A 74 74A 76 77

# 20.0 ELECTRICAL CHARACTERISTICS FOR PIC16C76/77

#### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                 | 55 to +125°C                     |

|----------------------------------------------------------------------------------------------------------------|----------------------------------|

| Storage temperature                                                                                            |                                  |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                             | 0.3V to (VDD + 0.3V)             |

| Voltage on VDD with respect to Vss                                                                             | 0.3 to +7.5V                     |

| Voltage on MCLR with respect to Vss (Note 2)                                                                   | 0 to +14V                        |

| Voltage on RA4 with respect to Vss                                                                             | 0 to +14V                        |

| Total power dissipation (Note 1)                                                                               | 1.0W                             |

| Maximum current out of Vss pin                                                                                 | 300 mA                           |

| Maximum current into VDD pin                                                                                   | 250 mA                           |

| Input clamp current, liк (Vi < 0 or Vi > VDD)                                                                  | ±20 mA                           |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                                 | ±20 mA                           |

| Maximum output current sunk by any I/O pin                                                                     | 25 mA                            |

| Maximum output current sourced by any I/O pin                                                                  | 25 mA                            |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                            | 200 mA                           |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                         | 200 mA                           |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                                    | 200 mA                           |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                                 | 200 mA                           |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD - VO | H) x IOH} + $\Sigma$ (VOI x IOL) |

| Note 2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, ma                     | ay cause latch-up. Thus,         |

**lote 2:** Voltage spikes below VSS at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. I hus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to VSS.

Note 3: PORTD and PORTE are not implemented on the PIC16C76.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# PIC16C7X

# Applicable Devices 72 73 73A 74 74A 76 77

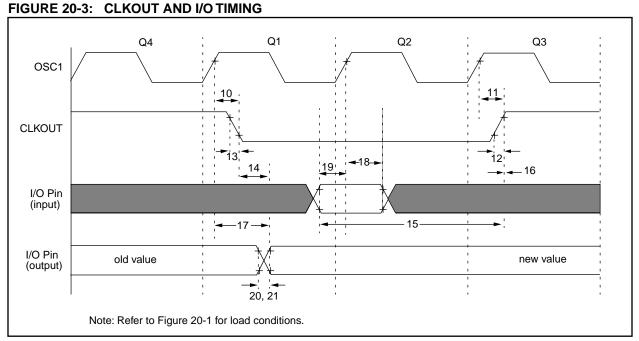

| TABLE 20-3: | <b>CLKOUT AND I/O TIMING REQUIREMENTS</b> |

|-------------|-------------------------------------------|

| IADEE 20-3. |                                           |

| Param<br>No. | Sym      | Characteristic                                    |                       | Min        | Тур† | Мах         | Units | Conditions |

|--------------|----------|---------------------------------------------------|-----------------------|------------|------|-------------|-------|------------|

| 10*          | TosH2ckL | OSC1 <sup>↑</sup> to CLKOUT↓                      |                       | _          | 75   | 200         | ns    | Note 1     |

| 11*          | TosH2ckH | OSC1 <sup>↑</sup> to CLKOUT <sup>↑</sup>          |                       | _          | 75   | 200         | ns    | Note 1     |

| 12*          | TckR     | CLKOUT rise time                                  |                       | _          | 35   | 100         | ns    | Note 1     |

| 13*          | TckF     | CLKOUT fall time                                  |                       | _          | 35   | 100         | ns    | Note 1     |

| 14*          | TckL2ioV | CLKOUT $\downarrow$ to Port out valid             | t                     | _          | -    | 0.5Tcy + 20 | ns    | Note 1     |

| 15*          | TioV2ckH | Port in valid before CLKOL                        | T ↑                   | Tosc + 200 | -    | _           | ns    | Note 1     |

| 16*          | TckH2iol | Port in hold after CLKOUT                         | $\uparrow$            | 0          | —    |             | ns    | Note 1     |

| 17*          | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to<br>Port out valid |                       | -          | 50   | 150         | ns    |            |

| 18*          | TosH2iol | OSC1↑ (Q2 cycle) to                               | PIC16 <b>C</b> 76/77  | 100        | -    | _           | ns    |            |

|              |          | Port input invalid (I/O in hold time)             | PIC16 <b>LC</b> 76/77 | 200        | -    | _           | ns    |            |

| 19*          | TioV2osH | Port input valid to OSC11                         | (I/O in setup time)   | 0          | —    | _           | ns    |            |

| 20*          | TioR     | Port output rise time                             | PIC16 <b>C</b> 76/77  | _          | 10   | 40          | ns    |            |

|              |          |                                                   | PIC16 <b>LC</b> 76/77 | _          | —    | 80          | ns    |            |

| 21*          | TioF     | Port output fall time                             | PIC16 <b>C</b> 76/77  | _          | 10   | 40          | ns    |            |

|              |          |                                                   | PIC16 <b>LC</b> 76/77 | _          | —    | 80          | ns    |            |

| 22††*        | Tinp     | INT pin high or low time                          |                       | Тсү        | -    | -           | ns    |            |

| 23††*        | Trbp     | RB7:RB4 change INT high                           | or low time           | Тсү        | -    | _           | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

# PIC16C7X

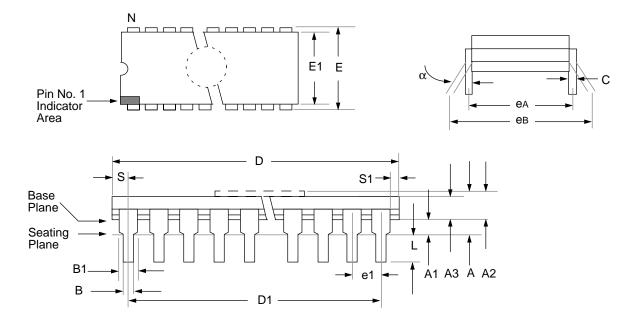

## 22.2 40-Lead Ceramic CERDIP Dual In-line with Window (600 mil) (JW)

|        | Pa     | ckage Group: ( | Ceramic CERDIP | Dual In-Line (C | DP)    |           |

|--------|--------|----------------|----------------|-----------------|--------|-----------|

|        |        | Millimeters    |                |                 | Inches |           |

| Symbol | Min    | Max            | Notes          | Min             | Max    | Notes     |

| α      | 0°     | 10°            |                | 0°              | 10°    |           |

| А      | 4.318  | 5.715          |                | 0.170           | 0.225  |           |

| A1     | 0.381  | 1.778          |                | 0.015           | 0.070  |           |

| A2     | 3.810  | 4.699          |                | 0.150           | 0.185  |           |

| A3     | 3.810  | 4.445          |                | 0.150           | 0.175  |           |

| В      | 0.355  | 0.585          |                | 0.014           | 0.023  |           |

| B1     | 1.270  | 1.651          | Typical        | 0.050           | 0.065  | Typical   |

| С      | 0.203  | 0.381          | Typical        | 0.008           | 0.015  | Typical   |

| D      | 51.435 | 52.705         |                | 2.025           | 2.075  |           |

| D1     | 48.260 | 48.260         | Reference      | 1.900           | 1.900  | Reference |

| E      | 15.240 | 15.875         |                | 0.600           | 0.625  |           |

| E1     | 12.954 | 15.240         |                | 0.510           | 0.600  |           |

| e1     | 2.540  | 2.540          | Reference      | 0.100           | 0.100  | Reference |

| eA     | 14.986 | 16.002         | Typical        | 0.590           | 0.630  | Typical   |

| eB     | 15.240 | 18.034         |                | 0.600           | 0.710  |           |

| L      | 3.175  | 3.810          |                | 0.125           | 0.150  |           |

| Ν      | 40     | 40             |                | 40              | 40     |           |

| S      | 1.016  | 2.286          |                | 0.040           | 0.090  |           |

| S1     | 0.381  | 1.778          |                | 0.015           | 0.070  |           |

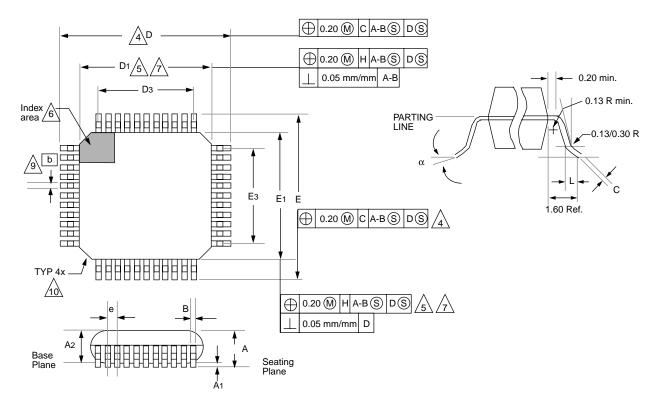

#### 22.8 44-Lead Plastic Surface Mount (MQFP 10x10 mm Body 1.6/0.15 mm Lead Form) (PQ)

|        |            | Packa       | ge Group: Plastic | : MQFP |            |           |

|--------|------------|-------------|-------------------|--------|------------|-----------|

|        |            | Millimeters |                   |        | Inches     |           |

| Symbol | Min        | Max         | Notes             | Min    | Max        | Notes     |

| α      | <b>0</b> ° | 7°          |                   | 0°     | <b>7</b> ° |           |

| А      | 2.000      | 2.350       |                   | 0.078  | 0.093      |           |

| A1     | 0.050      | 0.250       |                   | 0.002  | 0.010      |           |

| A2     | 1.950      | 2.100       |                   | 0.768  | 0.083      |           |

| b      | 0.300      | 0.450       | Typical           | 0.011  | 0.018      | Typical   |

| С      | 0.150      | 0.180       |                   | 0.006  | 0.007      |           |

| D      | 12.950     | 13.450      |                   | 0.510  | 0.530      |           |

| D1     | 9.900      | 10.100      |                   | 0.390  | 0.398      |           |

| D3     | 8.000      | 8.000       | Reference         | 0.315  | 0.315      | Reference |

| E      | 12.950     | 13.450      |                   | 0.510  | 0.530      |           |

| E1     | 9.900      | 10.100      |                   | 0.390  | 0.398      |           |

| E3     | 8.000      | 8.000       | Reference         | 0.315  | 0.315      | Reference |

| е      | 0.800      | 0.800       |                   | 0.031  | 0.032      |           |

| L      | 0.730      | 1.030       |                   | 0.028  | 0.041      |           |

| Ν      | 44         | 44          |                   | 44     | 44         |           |

| CP     | 0.102      | -           |                   | 0.004  | _          |           |

# U

| UA78, 83<br>Universal Synchronous Asynchronous Receiver Transmitter<br>(USART)99<br>Update Address bit, UA78, 83<br>USART |