#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

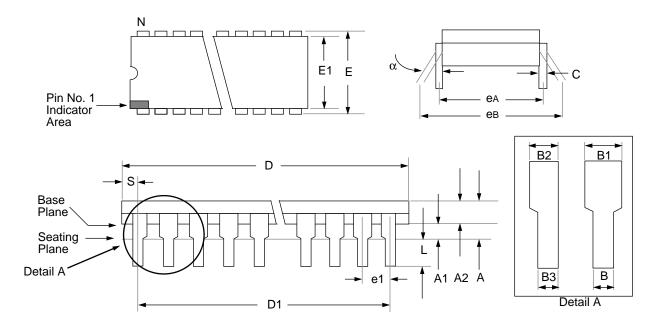

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc73a-04-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|            |                                                 | PIC16C710                           | PIC16C71            | PIC16C711                           | PIC16C715                           | PIC16C72                   | PIC16CR72 <sup>(1)</sup>   |

|------------|-------------------------------------------------|-------------------------------------|---------------------|-------------------------------------|-------------------------------------|----------------------------|----------------------------|

| Clock      | Maximum Frequency<br>of Operation (MHz)         | 20                                  | 20                  | 20                                  | 20                                  | 20                         | 20                         |

|            | EPROM Program Memory<br>(x14 words)             | 512                                 | 1K                  | 1K                                  | 2К                                  | 2К                         | —                          |

| lemory     | ROM Program Memory<br>(14K words)               | _                                   | _                   | _                                   | _                                   | _                          | 2К                         |

|            | Data Memory (bytes)                             | 36                                  | 36                  | 68                                  | 128                                 | 128                        | 128                        |

|            | Timer Module(s)                                 | TMR0                                | TMR0                | TMR0                                | TMR0                                | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2     |

| eripherals | Capture/Compare/<br>PWM Module(s)               | —                                   | _                   | —                                   | —                                   | 1                          | 1                          |

|            | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | _                                   | —                   | —                                   | —                                   | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C       |

|            | Parallel Slave Port                             | _                                   | —                   | —                                   | _                                   | _                          | —                          |

|            | A/D Converter (8-bit) Channels                  | 4                                   | 4                   | 4                                   | 4                                   | 5                          | 5                          |

|            | Interrupt Sources                               | 4                                   | 4                   | 4                                   | 4                                   | 8                          | 8                          |

|            | I/O Pins                                        | 13                                  | 13                  | 13                                  | 13                                  | 22                         | 22                         |

|            | Voltage Range (Volts)                           | 3.0-6.0                             | 3.0-6.0             | 3.0-6.0                             | 3.0-5.5                             | 2.5-6.0                    | 3.0-5.5                    |

| atures     | In-Circuit Serial Programming                   | Yes                                 | Yes                 | Yes                                 | Yes                                 | Yes                        | Yes                        |

|            | Brown-out Reset                                 | Yes                                 | —                   | Yes                                 | Yes                                 | Yes                        | Yes                        |

|            | Packages                                        | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC, SSOP |

## TABLE 1-1: PIC16C7XX FAMILY OF DEVCES

|             |                                                   | PIC16C73A                   | PIC16C74A                                 | PIC16C76                    | PIC16C77                                  |

|-------------|---------------------------------------------------|-----------------------------|-------------------------------------------|-----------------------------|-------------------------------------------|

| Clock       | Maximum Frequency of Oper-<br>ation (MHz)         | 20                          | 20                                        | 20                          | 20                                        |

| Memory      | EPROM Program Memory<br>(x14 words)               | 4K                          | 4K                                        | 8K                          | 8K                                        |

|             | Data Memory (bytes)                               | 192                         | 192                                       | 368                         | 368                                       |

|             | Timer Module(s)                                   | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    |

| Peripherals | Capture/Compare/PWM Mod-<br>ule(s)                | 2                           | 2                                         | 2                           | 2                                         |

|             | Serial Port(s) (SPI/I <sup>2</sup> C, US-<br>ART) | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               |

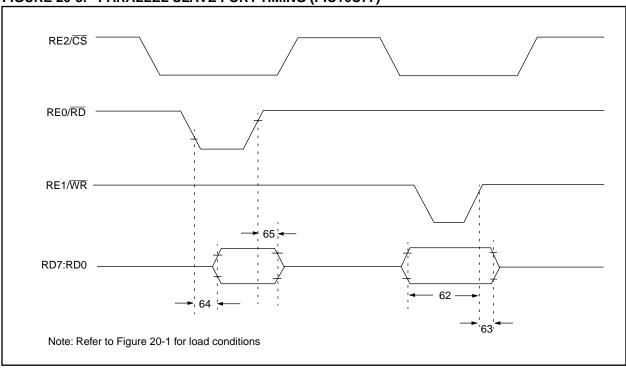

|             | Parallel Slave Port                               | —                           | Yes                                       | —                           | Yes                                       |

|             | A/D Converter (8-bit) Channels                    | 5                           | 8                                         | 5                           | 8                                         |

|             | Interrupt Sources                                 | 11                          | 12                                        | 11                          | 12                                        |

|             | I/O Pins                                          | 22                          | 33                                        | 22                          | 33                                        |

|             | Voltage Range (Volts)                             | 2.5-6.0                     | 2.5-6.0                                   | 2.5-6.0                     | 2.5-6.0                                   |

| eatures     | In-Circuit Serial Programming                     | Yes                         | Yes                                       | Yes                         | Yes                                       |

|             | Brown-out Reset                                   | Yes                         | Yes                                       | Yes                         | Yes                                       |

|             | Packages                                          | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C7XX Family devices use serial programming with clock pin RB6 and data pin RB7.

Note 1: Please contact your local Microchip sales office for availability of these devices.

## TABLE 3-3: PIC16C74/74A/77 PINOUT DESCRIPTION (Cont.'d)

| Pin Name          | DIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                            |

|-------------------|-------------|--------------|-------------|---------------|-----------------------|--------------------------------------------------------------------------------------------------------|

|                   |             |              |             |               |                       | PORTC is a bi-directional I/O port.                                                                    |

| RC0/T1OSO/T1CKI   | 15          | 16           | 32          | I/O           | ST                    | RC0 can also be the Timer1 oscillator output or a<br>Timer1 clock input.                               |

| RC1/T1OSI/CCP2    | 16          | 18           | 35          | I/O           | ST                    | RC1 can also be the Timer1 oscillator input or<br>Capture2 input/Compare2 output/PWM2 output.          |

| RC2/CCP1          | 17          | 19           | 36          | I/O           | ST                    | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                    |

| RC3/SCK/SCL       | 18          | 20           | 37          | I/O           | ST                    | RC3 can also be the synchronous serial clock input/<br>output for both SPI and I <sup>2</sup> C modes. |

| RC4/SDI/SDA       | 23          | 25           | 42          | I/O           | ST                    | RC4 can also be the SPI Data In (SPI mode) or data I/O ( $I^2$ C mode).                                |

| RC5/SDO           | 24          | 26           | 43          | I/O           | ST                    | RC5 can also be the SPI Data Out (SPI mode).                                                           |

| RC6/TX/CK         | 25          | 27           | 44          | I/O           | ST                    | RC6 can also be the USART Asynchronous Transmit or<br>Synchronous Clock.                               |

| RC7/RX/DT         | 26          | 29           | 1           | I/O           | ST                    | RC7 can also be the USART Asynchronous Receive or<br>Synchronous Data.                                 |

|                   |             |              |             |               |                       | PORTD is a bi-directional I/O port or parallel slave port when interfacing to a microprocessor bus.    |

| RD0/PSP0          | 19          | 21           | 38          | I/O           | ST/TTL <sup>(3)</sup> | when interfacing to a microprocessor bus.                                                              |

| RD1/PSP1          | 20          | 21           | 39          | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD2/PSP2          | 20          | 22           | 40          | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD3/PSP3          | 22          | 23           | 41          | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD4/PSP4          | 27          | 30           | 2           | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD5/PSP5          | 28          | 31           | 3           | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD6/PSP6          | 29          | 32           | 4           | 1/O           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD7/PSP7          | 30          | 33           | 5           | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

|                   |             |              |             | 1/0           | OI/ITE                | PORTE is a bi-directional I/O port.                                                                    |

| RE0/RD/AN5        | 8           | 9            | 25          | I/O           | ST/TTL <sup>(3)</sup> | RE0 can also be read control for the parallel slave port,<br>or analog input5.                         |

| RE1/WR/AN6        | 9           | 10           | 26          | I/O           | ST/TTL <sup>(3)</sup> | RE1 can also be write control for the parallel slave port, or analog input6.                           |

| RE2/CS/AN7        | 10          | 11           | 27          | I/O           | ST/TTL <sup>(3)</sup> | RE2 can also be select control for the parallel slave port, or analog input7.                          |

| Vss               | 12,31       | 13,34        | 6,29        | Р             |                       | Ground reference for logic and I/O pins.                                                               |

| Vdd               | 11,32       | 12,35        | 7,28        | Р             | _                     | Positive supply for logic and I/O pins.                                                                |

| NC                | —           | 1,17,28,     | 12,13,      |               |                       | These pins are not internally connected. These pins should                                             |

|                   |             | 40           | 33,34       |               |                       | be left unconnected.                                                                                   |

| Legend: I = input | 0 = oi      | •            |             |               | put/output            | P = power                                                                                              |

|                   |             | lot used     |             |               | TL input              | ST = Schmitt Trigger input<br>external interrupt.                                                      |

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

This buffer is a Schmitt Trigger input when used in serial programming mode.

This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel

Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

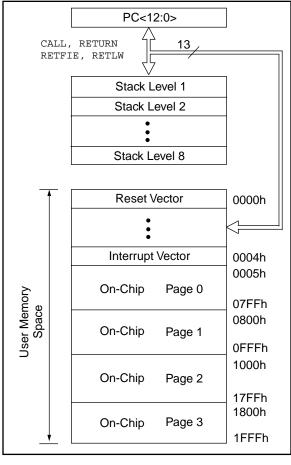

### FIGURE 4-3: PIC16C76/77 PROGRAM MEMORY MAP AND STACK

## 4.2 Data Memory Organization

Applicable Devices

72

73

73

74

74

76

77

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

RP1:RP0 (STATUS<6:5>)

- = 00  $\rightarrow$  Bank0

- = 01  $\rightarrow$  Bank1

- =  $10 \rightarrow \text{Bank2}$

- = 11  $\rightarrow$  Bank3

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain special function registers. Some "high use" special function registers from one bank may be mirrored in another bank for code reduction and quicker access.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR (Section 4.5).

| Address              | Name    | Bit 7                | Bit 6          | Bit 5                     | Bit 4            | Bit 3        | Bit 2           | Bit 1         | Bit 0    | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(2) |

|----------------------|---------|----------------------|----------------|---------------------------|------------------|--------------|-----------------|---------------|----------|--------------------------|-------------------------------------|

| Bank 1               |         |                      |                |                           |                  |              |                 |               |          |                          |                                     |

| 80h <sup>(4)</sup>   | INDF    | Addressing           | this location  | uses conter               | nts of FSR to ac | dress data   | memory (not     | a physical re | egister) | 0000 0000                | 0000 0000                           |

| 81h                  | OPTION  | RBPU                 | INTEDG         | TOCS                      | TOSE             | PSA          | PS2             | PS1           | PS0      | 1111 1111                | 1111 1111                           |

| 82h <sup>(4)</sup>   | PCL     | Program Co           | ounter's (PC)  |                           | 0000 0000        | 0000 0000    |                 |               |          |                          |                                     |

| 83h <b>(4)</b>       | STATUS  | IRP                  | RP1            | С                         | 0001 1xxx        | 000q quuu    |                 |               |          |                          |                                     |

| 84h <sup>(4)</sup>   | FSR     | Indirect data        | a memory ac    | dress pointe              | er               |              |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 85h                  | TRISA   | _                    | _              | PORTA Dat                 | ta Direction Re  | gister       |                 |               |          | 11 1111                  | 11 1111                             |

| 86h                  | TRISB   | PORTB Dat            | ta Direction F | Register                  |                  |              |                 |               |          | 1111 1111                | 1111 1111                           |

| 87h                  | TRISC   | PORTC Dat            | ta Direction I | Register                  |                  |              |                 |               |          | 1111 1111                | 1111 1111                           |

| 88h <b>(5)</b>       | TRISD   | PORTD Dat            | ta Direction F | Register                  |                  |              |                 |               |          | 1111 1111                | 1111 1111                           |

| 89h <b>(5)</b>       | TRISE   | IBF                  | OBF            | IBOV                      | PSPMODE          | _            | PORTE Dat       | a Direction E | Bits     | 0000 -111                | 0000 -111                           |

| 8Ah <sup>(1,4)</sup> | PCLATH  | _                    | —              | _                         | Write Buffer fo  | or the upper | 5 bits of the l | Program Cou   | Inter    | 0 0000                   | 0 0000                              |

| 8Bh <sup>(4)</sup>   | INTCON  | GIE                  | PEIE           | TOIE                      | INTE             | RBIE         | TOIF            | INTF          | RBIF     | 0000 000x                | 0000 000u                           |

| 8Ch                  | PIE1    | PSPIE <sup>(3)</sup> | ADIE           | RCIE                      | TXIE             | SSPIE        | CCP1IE          | TMR2IE        | TMR1IE   | 0000 0000                | 0000 0000                           |

| 8Dh                  | PIE2    | _                    | _              | —                         | _                | _            | —               | —             | CCP2IE   | 0                        | 0                                   |

| 8Eh                  | PCON    | _                    | _              | _                         | _                | _            | _               | POR           | BOR      | dd                       | uu                                  |

| 8Fh                  | _       | Unimpleme            | nted           | •                         |                  | •            |                 | •             | •        | _                        | _                                   |

| 90h                  | _       | Unimpleme            | nted           |                           |                  |              |                 |               |          | _                        | _                                   |

| 91h                  | _       | Unimpleme            | nted           |                           |                  |              |                 |               |          | -                        | _                                   |

| 92h                  | PR2     | Timer2 Peri          | od Register    |                           |                  |              |                 |               |          | 1111 1111                | 1111 1111                           |

| 93h                  | SSPADD  | Synchronou           | us Serial Por  | t (I <sup>2</sup> C mode) | Address Regis    | ter          |                 |               |          | 0000 0000                | 0000 0000                           |

| 94h                  | SSPSTAT | SMP                  | CKE            | D/Ā                       | Р                | S            | R/W             | UA            | BF       | 0000 0000                | 0000 0000                           |

| 95h                  | _       | Unimpleme            | nted           | •                         |                  |              |                 |               | •        | _                        | _                                   |

| 96h                  | _       | Unimpleme            | nted           |                           |                  |              |                 |               |          | _                        | _                                   |

| 97h                  | _       | Unimpleme            | nted           |                           |                  |              |                 |               |          | _                        | _                                   |

| 98h                  | TXSTA   | CSRC                 | TX9            | TXEN                      | SYNC             | _            | BRGH            | TRMT          | TX9D     | 0000 -010                | 0000 -010                           |

| 99h                  | SPBRG   | Baud Rate            | Generator R    | egister                   |                  |              |                 |               |          | 0000 0000                | 0000 0000                           |

| 9Ah                  | _       | Unimpleme            | nted           |                           |                  |              |                 |               |          | _                        | _                                   |

| 9Bh                  | _       | Unimpleme            | nted           |                           |                  |              |                 |               |          | _                        | _                                   |

| 9Ch                  | _       | Unimpleme            | nted           |                           |                  |              |                 |               |          | _                        | _                                   |

| 9Dh                  | -       | Unimpleme            | nted           |                           |                  |              |                 |               |          | _                        | —                                   |

| 9Eh                  | -       | Unimpleme            | nted           |                           |                  |              |                 |               |          | -                        | —                                   |

| 9Fh                  | ADCON1  | _                    | _              | _                         | _                | _            | PCFG2           | PCFG1         | PCFG0    | 000                      | 000                                 |

## TABLE 4-3: PIC16C76/77 SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the PIC16C76, always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD and PORTE are not physically implemented on the PIC16C76, read as '0'.

## FIGURE 4-11: PIE1 REGISTER PIC16C73/73A/74/74A/76/77 (ADDRESS 8Ch)

| PSPIE <sup>(1)</sup> | ADIE      | RCIE                                     | TXIE        | SSPIE       | CCP1IE      | TMR2IE       | TMR1IE    | R      | = Readable bit                                                                                           |

|----------------------|-----------|------------------------------------------|-------------|-------------|-------------|--------------|-----------|--------|----------------------------------------------------------------------------------------------------------|

| bit7                 | 1         |                                          |             |             |             |              | bit0      | U      | <ul> <li>Writable bit</li> <li>Unimplemented bit,<br/>read as '0'</li> <li>Value at POR reset</li> </ul> |

| bit 7:               | 1 = Enabl | Parallel S<br>es the PS<br>les the PS    | P read/wr   | te interrup |             | Enable bit   |           |        |                                                                                                          |

| bit 6:               | 1 = Enabl | D Converte<br>les the A/E<br>les the A/I | ) interrupt |             | it          |              |           |        |                                                                                                          |

| bit 5:               | 1 = Enabl | ART Rece<br>es the US<br>les the US      | ART recei   | ve interrup | ot          |              |           |        |                                                                                                          |

| bit 4:               | 1 = Enabl | ART Trans<br>es the US<br>les the US     | ART trans   | mit interru | ıpt         |              |           |        |                                                                                                          |

| bit 3:               | 1 = Enabl | ynchronou<br>es the SS<br>les the SS     | P interrup  | t           | pt Enable b | bit          |           |        |                                                                                                          |

| bit 2:               | 1 = Enabl | CCP1 Inte<br>es the CC<br>les the CC     | P1 interru  | pt          |             |              |           |        |                                                                                                          |

| bit 1:               | 1 = Enabl | TMR2 to F<br>es the TM<br>les the TM     | R2 to PR2   | 2 match in  | •           |              |           |        |                                                                                                          |

| bit 0:               | 1 = Enabl | TMR1 Ove<br>es the TM<br>les the TM      | R1 overflo  | w interrup  | ot          |              |           |        |                                                                                                          |

| Note 1:              | PIC16C73  |                                          |             |             |             | Slave Port i | mplemente | ed, tl | his bit location is reserved                                                                             |

# 6.0 OVERVIEW OF TIMER MODULES

Applicable Devices

The PIC16C72, PIC16C73/73A, PIC16C74/74A, PIC16C76/77 each have three timer modules.

Each module can generate an interrupt to indicate that an event has occurred (i.e. timer overflow). Each of these modules is explained in full detail in the following sections. The timer modules are:

- Timer0 Module (Section 7.0)

- Timer1 Module (Section 8.0)

- Timer2 Module (Section 9.0)

## 6.1 <u>Timer0 Overview</u> Applicable Devices 72|73|73A|74|74A|76|77

The Timer0 module is a simple 8-bit overflow counter. The clock source can be either the internal system clock (Fosc/4) or an external clock. When the clock source is an external clock, the Timer0 module can be selected to increment on either the rising or falling edge.

The Timer0 module also has a programmable prescaler option. This prescaler can be assigned to either the Timer0 module or the Watchdog Timer. Bit PSA (OPTION<3>) assigns the prescaler, and bits PS2:PS0 (OPTION<2:0>) determine the prescaler value. Timer0 can increment at the following rates: 1:1 (when prescaler assigned to Watchdog timer), 1:2, 1:4, 1:8, 1:16, 1:32, 1:64, 1:128, and 1:256 (Timer0 only).

Synchronization of the external clock occurs after the prescaler. When the prescaler is used, the external clock frequency may be higher then the device's frequency. The maximum frequency is 50 MHz, given the high and low time requirements of the clock.

## 6.2 <u>Timer1 Overview</u> Applicable Devices 72 73 73 74 74 76 77

Timer1 is a 16-bit timer/counter. The clock source can be either the internal system clock (Fosc/4), an external clock, or an external crystal. Timer1 can operate as either a timer or a counter. When operating as a counter (external clock source), the counter can either operate synchronized to the device or asynchronously to the device. Asynchronous operation allows Timer1 to operate during sleep, which is useful for applications that require a real-time clock as well as the power savings of SLEEP mode.

Timer1 also has a prescaler option which allows Timer1 to increment at the following rates: 1:1, 1:2, 1:4, and 1:8. Timer1 can be used in conjunction with the Capture/Compare/PWM module. When used with a CCP module, Timer1 is the time-base for 16-bit Capture or the 16-bit Compare and must be synchronized to the device.

## 6.3 <u>Timer2 Overview</u> Applicable Devices

|    |    |     |    | evic |    | _  |

|----|----|-----|----|------|----|----|

| 72 | 73 | 73A | 74 | 74A  | 76 | 77 |

Timer2 is an 8-bit timer with a programmable prescaler and postscaler, as well as an 8-bit period register (PR2). Timer2 can be used with the CCP1 module (in PWM mode) as well as the Baud Rate Generator for the Synchronous Serial Port (SSP). The prescaler option allows Timer2 to increment at the following rates: 1:1, 1:4, 1:16.

The postscaler allows the TMR2 register to match the period register (PR2) a programmable number of times before generating an interrupt. The postscaler can be programmed from 1:1 to 1:16 (inclusive).

## 6.4 <u>CCP Overview</u>

Applicable Devices

72

73

73

74

74

76

77

The CCP module(s) can operate in one of these three modes: 16-bit capture, 16-bit compare, or up to 10-bit Pulse Width Modulation (PWM).

Capture mode captures the 16-bit value of TMR1 into the CCPRxH:CCPRxL register pair. The capture event can be programmed for either the falling edge, rising edge, fourth rising edge, or the sixteenth rising edge of the CCPx pin.

Compare mode compares the TMR1H:TMR1L register pair to the CCPRxH:CCPRxL register pair. When a match occurs an interrupt can be generated, and the output pin CCPx can be forced to given state (High or Low), TMR1 can be reset (CCP1), or TMR1 reset and start A/D conversion (CCP2). This depends on the control bits CCPxM3:CCPxM0.

PWM mode compares the TMR2 register to a 10-bit duty cycle register (CCPRxH:CCPRxL<5:4>) as well as to an 8-bit period register (PR2). When the TMR2 register = Duty Cycle register, the CCPx pin will be forced low. When TMR2 = PR2, TMR2 is cleared to 00h, an interrupt can be generated, and the CCPx pin (if an output) will be forced high.

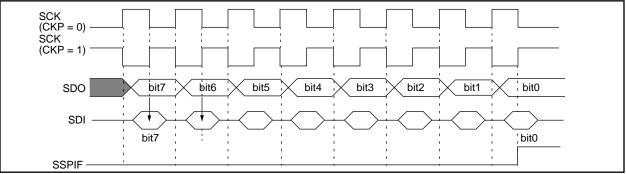

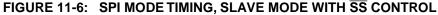

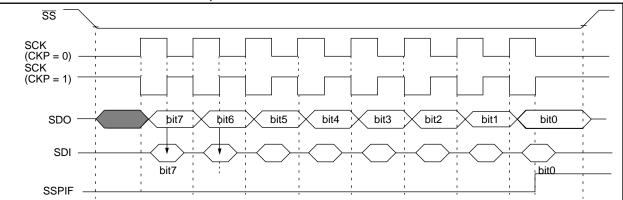

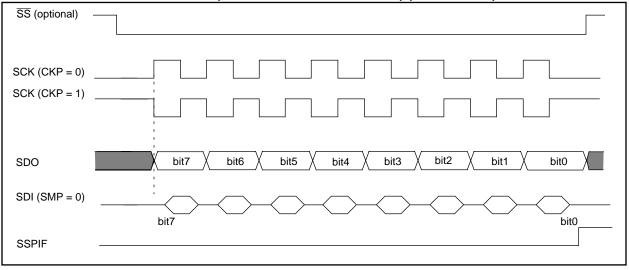

The  $\overline{SS}$  pin allows a synchronous slave mode. The SPI must be in slave mode (SSPCON<3:0> = 04h) and the TRISA<5> bit must be set the for synchronous slave mode to be enabled. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. If the  $\overline{SS}$  pin is taken low without resetting SPI mode, the transmission will continue from the

point at which it was taken high. External pull-up/ pull-down resistors may be desirable, depending on the application.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

|  | <b>TABLE 11-1:</b> | <b>REGISTERS ASSOCIATED WITH SPI OPERATION</b> |

|--|--------------------|------------------------------------------------|

|--|--------------------|------------------------------------------------|

| Address | Name    | Bit 7                  | Bit 6       | Bit 5               | Bit 4                         | Bit 3     | Bit 2    | Bit 1  | Bit 0  | Value<br>POF<br>BOF | ٦,   | all o | e on<br>ther<br>ets |

|---------|---------|------------------------|-------------|---------------------|-------------------------------|-----------|----------|--------|--------|---------------------|------|-------|---------------------|

| 0Bh,8Bh | INTCON  | GIE                    | PEIE        | TOIE                | INTE                          | RBIE      | TOIF     | INTF   | RBIF   | 0000 0              | 200x | 0000  | 000u                |

| 0Ch     | PIR1    | PSPIF <sup>(1,2)</sup> | ADIF        | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup>           | SSPIF     | CCP1IF   | TMR2IF | TMR1IF | 0000 0              | 0000 | 0000  | 0000                |

| 8Ch     | PIE1    | PSPIE <sup>(1,2)</sup> | ADIE        | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup>           | SSPIE     | CCP1IE   | TMR2IE | TMR1IE | 0000 0              | 0000 | 0000  | 0000                |

| 87h     | TRISC   | PORTC Da               | ta Directio | on Registe          | er                            |           |          |        |        | 1111 1              | 1111 | 1111  | 1111                |

| 13h     | SSPBUF  | Synchronou             | us Serial I | Port Rece           | ive Buffer                    | /Transmit | Register |        |        | XXXX X              | xxxx | uuuu  | uuuu                |

| 14h     | SSPCON  | WCOL                   | SSPOV       | SSPEN               | CKP                           | SSPM3     | SSPM2    | SSPM1  | SSPM0  | 0000 0              | 0000 | 0000  | 0000                |

| 85h     | TRISA   | _                      | _           | PORTA I             | PORTA Data Direction Register |           |          |        |        |                     |      | 11    | 1111                |

| 94h     | SSPSTAT | —                      | —           | D/Ā                 | Р                             | S         | R/W      | UA     | BF     | 00 C                | 0000 | 00    | 0000                |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the SSP in SPI mode.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A, always maintain these bits clear.

2: The PIC16C72 does not have a Parallel Slave Port or USART, these bits are unimplemented, read as '0'.

The  $\overline{SS}$  pin allows a synchronous slave mode. The SPI must be in slave mode (SSPCON<3:0> = 04h) and the TRISA<5> bit must be set for the synchronous slave mode to be enabled. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. If the  $\overline{SS}$  pin is taken low without resetting SPI mode, the transmission will continue from the point at which it was taken high. External pull-up/ pull-down resistors may be desirable, depending on the application.

| Note: | When the SPI is in Slave Mode with $\overline{SS}$ pin<br>control enabled, (SSPCON<3:0> = 0100)<br>the SPI module will reset if the $\overline{SS}$ pin is set<br>to VDD. |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | If the SPI is used in Slave Mode with                                                                                                                                     |

CKE = '1', then the SS pin control must be enabled. To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as

be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

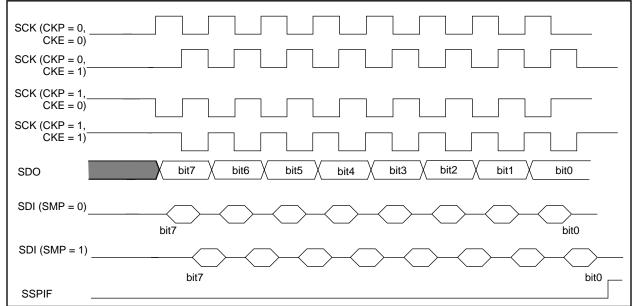

## FIGURE 11-11: SPI MODE TIMING, MASTER MODE (PIC16C76/77)

## FIGURE 11-12: SPI MODE TIMING (SLAVE MODE WITH CKE = 0) (PIC16C76/77)

## TABLE 12-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Address | Name  | Bit 7                | Bit 6     | Bit 5     | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|-------|----------------------|-----------|-----------|-------|-------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF      | RCIF      | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA | SPEN                 | RX9       | SREN      | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                 |

| 19h     | TXREG | USART Tra            | ansmit Re | egister   |       |       |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE      | RCIE      | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA | CSRC                 | TX9       | TXEN      | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | SPBRG | Baud Rate            | 0000 0000 | 0000 0000 |       |       |        |        |        |                          |                           |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Transmission. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

#### TABLE 12-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address | Name  | Bit 7                | Bit 6     | Bit 5    | Bit 4 | Bit 3     | Bit 2     | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|-------|----------------------|-----------|----------|-------|-----------|-----------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF      | RCIF     | TXIF  | SSPIF     | CCP1IF    | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA | SPEN                 | RX9       | SREN     | CREN  | _         | FERR      | OERR   | RX9D   | 0000 -00x                | 0000 -00x                 |

| 1Ah     | RCREG | USART Re             | eceive Re | egister  |       |           |           |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE      | RCIE     | TXIE  | SSPIE     | CCP1IE    | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA | CSRC                 | TX9       | TXEN     | SYNC  | _         | BRGH      | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | SPBRG | Baud Rate            | Generat   | or Regis |       | 0000 0000 | 0000 0000 |        |        |                          |                           |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

| Address               | Name   | Bit 7                | Bit 6      | Bit 5   | Bit 4          | Bit 3    | Bit 2     | Bit 1       | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|-----------------------|--------|----------------------|------------|---------|----------------|----------|-----------|-------------|--------|--------------------------|---------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE       | TOIE    | INTE           | RBIE     | TOIF      | INTF        | RBIF   | 0000 000x                | 0000 000u                 |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF       | RCIF    | TXIF           | SSPIF    | CCP1IF    | TMR2IF      | TMR1IF | 0000 0000                | 0000 0000                 |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE       | RCIE    | TXIE           | SSPIE    | CCP1IE    | TMR2IE      | TMR1IE | 0000 0000                | 0000 0000                 |

| 0Dh                   | PIR2   | —                    | —          | —       | —              | _        | —         | —           | CCP2IF | 0                        | 0                         |

| 8Dh                   | PIE2   | _                    | _          | _       | —              | _        | —         | —           | CCP2IE | 0                        | 0                         |

| 1Eh                   | ADRES  | A/D Resu             | It Registe | er      |                |          |           |             |        | xxxx xxxx                | uuuu uuuu                 |

| 1Fh                   | ADCON0 | ADCS1                | ADCS0      | CHS2    | CHS1           | CHS0     | GO/DONE   | —           | ADON   | 0000 00-0                | 0000 00-0                 |

| 9Fh                   | ADCON1 | —                    | _          | _       | —              | _        | PCFG2     | PCFG1       | PCFG0  | 000                      | 000                       |

| 05h                   | PORTA  | _                    | _          | RA5     | RA4            | RA3      | RA2       | RA1         | RA0    | 0x 0000                  | Ou 0000                   |

| 85h                   | TRISA  | _                    | _          | PORTA I | Data Directior | Register | •         |             |        | 11 1111                  | 11 1111                   |

| 09h                   | PORTE  | —                    |            | —       | —              | —        | RE2       | RE1         | RE0    | xxx                      | uuu                       |

| 89h                   | TRISE  | IBF                  | OBF        | IBOV    | PSPMODE        | _        | PORTE Dat | a Directior | n Bits | 0000 -111                | 0000 -111                 |

| TABLE 13-3: \$ | SUMMARY OF A/D REGISTERS, PIC16C73/73A/74/74A/76/77 |  |

|----------------|-----------------------------------------------------|--|

|----------------|-----------------------------------------------------|--|

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC6C73/73A/76, always maintain these bits clear.

## 14.0 SPECIAL FEATURES OF THE CPU Applicable Devices

72 73 73A 74 74A 76 77

What sets a microcontroller apart from other processors are special circuits to deal with the needs of realtime applications. The PIC16CXX family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- · Oscillator selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- · In-circuit serial programming

The PIC16CXX has a Watchdog Timer which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

# 14.1 Configuration Bits

Applicable Devices

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

#### FIGURE 14-1: CONFIGURATION WORD FOR PIC16C73/74

|           |                                                           | —                                   | —                                | —                     |          | _    | CP1 | CP0 | PWRTE | WDTE | FOSC1 | FOSC0 | Register: | CONFIG |

|-----------|-----------------------------------------------------------|-------------------------------------|----------------------------------|-----------------------|----------|------|-----|-----|-------|------|-------|-------|-----------|--------|

| bit13     |                                                           |                                     |                                  |                       |          |      |     |     |       |      |       | bit0  | Address   | 2007h  |

| bit 13-5: | Unimple                                                   | mented                              | I: Read                          | as '1'                |          |      |     |     |       |      |       |       |           |        |

| bit 4:    | CP1:CP0<br>11 = Coo<br>10 = Upp<br>01 = Upp<br>00 = All r | le prote<br>per half<br>per 3/4th   | ction of<br>of progin<br>of prog | f<br>ram me<br>gram m | emory    | •    |     | d   |       |      |       |       |           |        |

| bit 3:    | <b>PWRTE</b> :<br>1 = Powe<br>0 = Powe                    | r-up Tin                            | ner ena                          | bled                  | le bit   |      |     |     |       |      |       |       |           |        |

| bit 2:    | <b>WDTE</b> : W<br>1 = WDT<br>0 = WDT                     | enable                              | d                                | r Enable              | e bit    |      |     |     |       |      |       |       |           |        |

| bit 1-0:  | FOSC1:F<br>11 = RC<br>10 = HS<br>01 = XT<br>00 = LP 0     | oscillato<br>oscillato<br>oscillato | or<br>or<br>or                   | tor Sele              | ection b | vits |     |     |       |      |       |       |           |        |

# PIC16C7X

| Register |    | Applicable Devices |     |    |     |    |    | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT<br>or<br>Interrupt |

|----------|----|--------------------|-----|----|-----|----|----|------------------------------------|--------------------------|------------------------------------|

| SSPADD   | 72 | 73                 | 73A | 74 | 74A | 76 | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                          |

| SSPSTAT  | 72 | 73                 | 73A | 74 | 74A | 76 | 77 | 00 0000                            | 00 0000                  | uu uuuu                            |

| TXSTA    | 72 | 73                 | 73A | 74 | 74A | 76 | 77 | 0000 -010                          | 0000 -010                | uuuu -uuu                          |

| SPBRG    | 72 | 73                 | 73A | 74 | 74A | 76 | 77 | 0000 0000                          | 0000 0000                | uuuu uuuu                          |

| ADCON1   | 72 | 73                 | 73A | 74 | 74A | 76 | 77 | 000                                | 000                      | uuu                                |

## TABLE 14-8: INITIALIZATION CONDITIONS FOR ALL REGISTERS (Cont.'d)

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 14-7 for reset value for specific condition.

| GOTO              | Uncondit                                                               | tional Br                         | anch                                 |                           |   | INCF              | Increment                                                   | tf                           |                            |                      |

|-------------------|------------------------------------------------------------------------|-----------------------------------|--------------------------------------|---------------------------|---|-------------------|-------------------------------------------------------------|------------------------------|----------------------------|----------------------|

| Syntax:           | [ label ]                                                              | GOTO                              | k                                    |                           |   | Syntax:           | [label]                                                     | NCF f                        | ,d                         |                      |

| Operands:         | $0 \le k \le 20$                                                       | )47                               |                                      |                           |   | Operands:         | $0 \le f \le 127$                                           | ,                            |                            |                      |

| Operation:        | $k \rightarrow PC < 2$                                                 | 10:0>                             |                                      |                           |   |                   | d ∈ [0,1]                                                   |                              |                            |                      |

|                   | PCLATH<                                                                | <4:3> → I                         | PC<12:11                             | >                         |   | Operation:        | (f) + 1 $\rightarrow$ (c                                    | destina                      | tion)                      |                      |

| Status Affected:  | None                                                                   |                                   |                                      |                           |   | Status Affected:  | Z                                                           |                              |                            |                      |

| Encoding:         | 10                                                                     | 1kkk                              | kkkk                                 | kkkk                      | ] | Encoding:         | 00                                                          | 1010                         | dfff                       | ffff                 |

| Description:      | GOTO is an<br>eleven bit i<br>into PC bit<br>PC are loa<br>GOTO is a f | mmediate<br>s <10:0>.<br>ded from | value is lo<br>The upper<br>PCLATH<4 | baded<br>bits of<br>4:3>. | - | Description:      | The content<br>mented. If 'd<br>the W regist<br>placed back | d' is 0 the<br>ter. If 'd' i | e result is<br>is 1 the re | placed in            |

| Words:            | 1                                                                      |                                   |                                      |                           |   | Words:            | 1                                                           |                              |                            |                      |

| Cycles:           | 2                                                                      |                                   |                                      |                           |   | Cycles:           | 1                                                           |                              |                            |                      |

| Q Cycle Activity: | Q1                                                                     | Q2                                | Q3                                   | Q4                        |   | Q Cycle Activity: | Q1                                                          | Q2                           | Q3                         | Q4                   |

| 1st Cycle         | Decode                                                                 | Read<br>literal 'k'               | Process<br>data                      | Write to<br>PC            |   |                   | Decode                                                      | Read<br>register<br>'f'      | Process<br>data            | Write to destination |

| 2nd Cycle         | No-<br>Operation                                                       | No-<br>Operation                  | No-<br>Operation                     | No-<br>Operation          |   |                   |                                                             |                              |                            |                      |

|                   |                                                                        |                                   |                                      |                           |   | Example           | INCF                                                        | CNT,                         |                            |                      |

| Example           | GOTO TH                                                                | IERE                              |                                      |                           |   |                   | Before Inst                                                 |                              |                            | -                    |

|                   | After Insti                                                            | ruction                           |                                      |                           |   |                   | 7                                                           | NT                           | = 0xF<br>= 0               | F                    |

|                   | I                                                                      | PC = Address THERE                |                                      | THERE                     |   |                   | After Instru                                                |                              | - 0                        |                      |

|                   |                                                                        |                                   |                                      |                           |   |                   |                                                             | NT                           | = 0x0                      | D                    |

|                   |                                                                        |                                   |                                      |                           |   |                   | Z                                                           |                              | = 1                        |                      |

## Applicable Devices 72 73 73A 74 74A 76 77

## 17.5 <u>Timing Diagrams and Specifications</u>

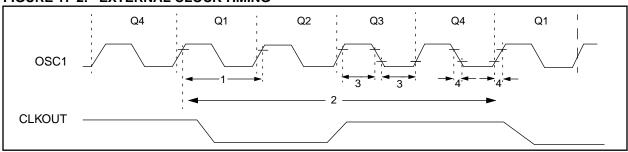

# FIGURE 17-2: EXTERNAL CLOCK TIMING

## TABLE 17-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                   | Min | Тур† | Max    | Units | Conditions         |

|------------------|-------|----------------------------------|-----|------|--------|-------|--------------------|

|                  | Fosc  | External CLKIN Frequency         | DC  | _    | 4      | MHz   | XT and RC osc mode |

|                  |       | (Note 1)                         | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|                  |       |                                  | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|                  |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|                  |       |                                  | DC  | _    | 200    | kHz   | LP osc mode        |

|                  |       | Oscillator Frequency             | DC  | _    | 4      | MHz   | RC osc mode        |

|                  |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode        |

|                  |       |                                  | 4   | _    | 20     | MHz   | HS osc mode        |

|                  |       |                                  | 5   | —    | 200    | kHz   | LP osc mode        |

| 1                | Tosc  | External CLKIN Period            | 250 | —    | —      | ns    | XT and RC osc mode |

|                  |       | (Note 1)                         | 250 | —    | —      | ns    | HS osc mode (-04)  |

|                  |       |                                  | 100 | —    | _      | ns    | HS osc mode (-10)  |

|                  |       |                                  | 50  | —    | —      | ns    | HS osc mode (-20)  |

|                  |       |                                  | 5   | _    | _      | μs    | LP osc mode        |

|                  |       | Oscillator Period                | 250 |      | —      | ns    | RC osc mode        |

|                  |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode        |

|                  |       |                                  | 250 | _    | 250    | ns    | HS osc mode (-04)  |

|                  |       |                                  | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|                  |       |                                  | 50  | —    | 250    | ns    | HS osc mode (-20)  |

|                  |       |                                  | 5   | —    | —      | μs    | LP osc mode        |

| 2                | Тсү   | Instruction Cycle Time (Note 1)  | 200 | —    | DC     | ns    | TCY = 4/FOSC       |

| 3                | TosL, | External Clock in (OSC1) High or | 100 | _    | _      | ns    | XT oscillator      |

|                  | TosH  | Low Time                         | 2.5 | —    | _      | μs    | LP oscillator      |

|                  |       |                                  | 15  |      |        | ns    | HS oscillator      |

| 4                | TosR, | External Clock in (OSC1) Rise or | —   |      | 25     | ns    | XT oscillator      |

|                  | TosF  | Fall Time                        |     | _    | 50     | ns    | LP oscillator      |

|                  |       |                                  |     | _    | 15     | ns    | HS oscillator      |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

# PIC16C7X

Applicable Devices 72 73 73A 74 74A 76 77

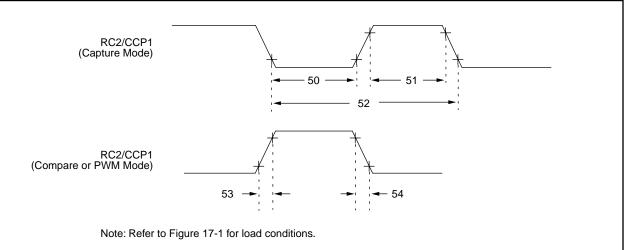

# TABLE 17-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1)

| Param<br>No. | Sym  | Characteristic        |                       |                    | Min                   | Тур† | Max | Units | Conditions                        |

|--------------|------|-----------------------|-----------------------|--------------------|-----------------------|------|-----|-------|-----------------------------------|

| 50*          | TccL | CCP1 input low time   | No Prescaler          |                    | 0.5Tcy + 20           | —    |     | ns    |                                   |

|              |      |                       | With Prescaler PIC16C |                    | 10                    | —    | _   | ns    |                                   |

|              |      |                       | PIC16 <b>LC</b> 72    |                    | 20                    | —    | _   | ns    |                                   |

| 51*          | TccH | CCP1 input high time  | No Prescaler          | •                  | 0.5Tcy + 20           | —    | —   | ns    |                                   |

|              |      |                       | With Prescaler PIC16C |                    | 10                    | —    | _   | ns    |                                   |

|              |      |                       |                       | PIC16 <b>LC</b> 72 | 20                    | —    | _   | ns    |                                   |

| 52*          | TccP | CCP1 input period     |                       |                    | <u>3Tcy + 40</u><br>N | —    | —   | ns    | N = prescale<br>value (1,4 or 16) |

| 53*          | TccR | CCP1 output rise time |                       | PIC16 <b>C</b> 72  | _                     | 10   | 25  | ns    |                                   |

|              |      |                       |                       | PIC16 <b>LC</b> 72 | —                     | 25   | 45  | ns    |                                   |

| 54*          | TccF | CCP1 output fall time |                       | PIC16 <b>C</b> 72  | _                     | 10   | 25  | ns    |                                   |

|              |      |                       |                       | PIC16 <b>LC</b> 72 | _                     | 25   | 45  | ns    |                                   |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# Applicable Devices 72 73 73A 74 74A 76 77

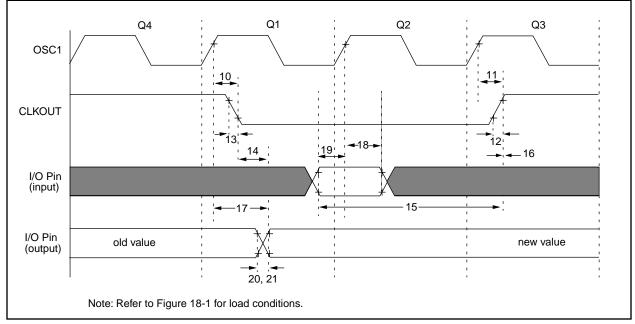

## FIGURE 18-3: CLKOUT AND I/O TIMING

| TABLE 18-3: CLKOUT AND I/O TIMING REQUIREMENTS |

|------------------------------------------------|

|------------------------------------------------|

| Parameter<br>No. | Sym      | Characteristic                                    |                                     | Min          | Тур† | Мах         | Units | Conditions |

|------------------|----------|---------------------------------------------------|-------------------------------------|--------------|------|-------------|-------|------------|

| 10*              | TosH2ckL | OSC1 <sup>↑</sup> to CLKOUT↓                      |                                     | _            | 75   | 200         | ns    | Note 1     |

| 11*              | TosH2ckH | OSC1 <sup>↑</sup> to CLKOUT <sup>↑</sup>          |                                     | —            | 75   | 200         | ns    | Note 1     |

| 12*              | TckR     | CLKOUT rise time                                  |                                     | _            | 35   | 100         | ns    | Note 1     |

| 13*              | TckF     | CLKOUT fall time                                  | T fall time                         |              |      | 100         | ns    | Note 1     |

| 14*              | TckL2ioV | CLKOUT ↓ to Port out vali                         | d                                   | _            | _    | 0.5Tcy + 20 | ns    | Note 1     |

| 15*              | TioV2ckH | Port in valid before CLKOU                        | דע ↑                                | 0.25Tcy + 25 | _    | _           | ns    | Note 1     |

| 16*              | TckH2iol | Port in hold after CLKOUT                         | · ↑                                 | 0            | _    | -           | ns    | Note 1     |

| 17*              | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to<br>Port out valid |                                     | -            | 50   | 150         | ns    |            |

| 18*              | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to                   | PIC16 <b>C</b> 73/74                | 100          | -    |             | ns    |            |

|                  |          | Port input invalid (I/O in hold time)             | PIC16 <b>LC</b> 73/74               | 200          | _    | _           | ns    |            |

| 19*              | TioV2osH | Port input valid to OSC11                         | (I/O in setup time)                 | 0            |      |             | ns    |            |

| 20*              | TioR     | Port output rise time                             | PIC16 <b>C</b> 73/74                | —            | 10   | 25          | ns    |            |

|                  |          |                                                   | PIC16 <b>LC</b> 73/74               | —            | _    | 60          | ns    |            |

| 21*              | TioF     | Port output fall time                             | PIC16 <b>C</b> 73/74                | _            | 10   | 25          | ns    |            |

|                  |          |                                                   | PIC16 <b>LC</b> 73/74               | —            | _    | 60          | ns    |            |

| 22††*            | Tinp     | INT pin high or low time                          | pin high or low time                |              |      | _           | ns    |            |

| 23††*            | Trbp     | RB7:RB4 change INT high                           | RB7:RB4 change INT high or low time |              |      | _           | ns    |            |

\* These parameters are characterized but not tested.

†Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

these parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

## Applicable Devices 72 73 73A 74 74A 76 77

|       |                                            | Standa        | rd Opera    | ting  | Conditio  | ons (un | less otherwise stated)                                                |  |  |

|-------|--------------------------------------------|---------------|-------------|-------|-----------|---------|-----------------------------------------------------------------------|--|--|

|       |                                            |               | ing tempe   | -     |           | •       | $\leq$ TA $\leq$ +125°C for extended,                                 |  |  |

|       | ARACTERISTICS                              | -             |             |       | -40       | )°C ≤   | $\leq$ TA $\leq$ +85°C for industrial and                             |  |  |

|       | ARACTERISTICS                              |               |             |       | 0°0       | 2 ≤     | $\leq$ TA $\leq$ +70°C for commercial                                 |  |  |

|       |                                            | Operati       | ing voltage | e Vdi | D range a | as desc | ribed in DC spec Section 19.1 and                                     |  |  |

|       |                                            | Section 19.2. |             |       |           |         |                                                                       |  |  |

| Param | Characteristic                             | Sym           | Min         | Тур   | Max       | Units   | Conditions                                                            |  |  |

| No.   |                                            |               |             | †     |           |         |                                                                       |  |  |

|       | Output High Voltage                        |               |             |       |           |         |                                                                       |  |  |

| D090  | I/O ports (Note 3)                         | Voн           | Vdd - 0.7   | -     | -         | V       | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                          |  |  |

| D090A |                                            |               | Vdd - 0.7   | -     | -         | V       | IOH = -2.5 mA, VDD = 4.5V,<br>-40°С to +125°С                         |  |  |

| D092  | OSC2/CLKOUT (RC osc config)                |               | Vdd - 0.7   | -     | -         | V       | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                          |  |  |

| D092A |                                            |               | Vdd - 0.7   | -     | -         | V       | IOH = -1.0 mA, VDD = 4.5V,<br>-40°С to +125°С                         |  |  |

| D150* | Open-Drain High Voltage                    | Vod           | -           | -     | 14        | V       | RA4 pin                                                               |  |  |

|       | Capacitive Loading Specs on<br>Output Pins |               |             |       |           |         |                                                                       |  |  |

| D100  | OSC2 pin                                   | Cosc2         | -           | -     | 15        | pF      | In XT, HS and LP modes when exter<br>nal clock is used to drive OSC1. |  |  |

| D101  | All I/O pins and OSC2 (in RC               | Сю            | -           | -     | 50        | pF      |                                                                       |  |  |

| D102  | mode) SCL, SDA in I <sup>2</sup> C mode    | Св            | -           | -     | 400       | pF      |                                                                       |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C7X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

# Applicable Devices 72 73 73A 74 74A 76 77

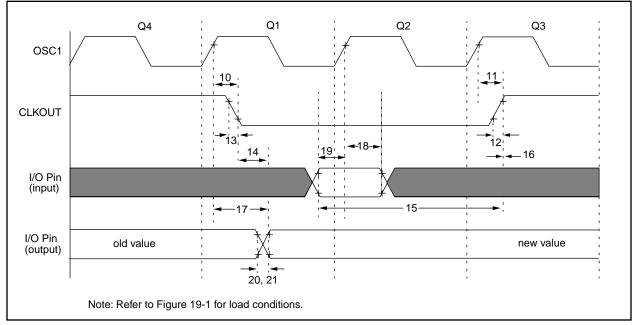

## FIGURE 19-3: CLKOUT AND I/O TIMING

## TABLE 19-3: CLKOUT AND I/O TIMING REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                                    |                         | Min | Тур†        | Max | Units  | Conditions |

|--------------|----------|---------------------------------------------------|-------------------------|-----|-------------|-----|--------|------------|

| 10*          | TosH2ckL | OSC1 <sup>↑</sup> to CLKOUT↓                      |                         | _   | 75          | 200 | ns     | Note 1     |

| 11*          | TosH2ckH | OSC1 <sup>↑</sup> to CLKOUT <sup>↑</sup>          |                         | _   | 75          | 200 | ns     | Note 1     |

| 12*          | TckR     | CLKOUT rise time                                  |                         | —   | 35          | 100 | ns     | Note 1     |

| 13*          | TckF     | CLKOUT fall time                                  | —                       | 35  | 100         | ns  | Note 1 |            |