Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 192 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | A/D 5x8b                                                                    |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 28-SPDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc73a-04i-sp |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                | DIP<br>Pin# | PLCC<br>Pin#      | QFP<br>Pin# | l/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                              |

|-------------------------|-------------|-------------------|-------------|---------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN              | 13          | 14                | 30          | I             | ST/CMOS <sup>(4)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                    |

| OSC2/CLKOUT             | 14          | 15                | 31          | 0             | _                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp                | 1           | 2                 | 18          | I/P           | ST                     | Master clear (reset) input or programming voltage input.<br>This pin is an active low reset to the device.                                                                                               |

|                         |             |                   |             |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                      |

| RA0/AN0                 | 2           | 3                 | 19          | I/O           | TTL                    | RA0 can also be analog input0                                                                                                                                                                            |

| RA1/AN1                 | 3           | 4                 | 20          | I/O           | TTL                    | RA1 can also be analog input1                                                                                                                                                                            |

| RA2/AN2                 | 4           | 5                 | 21          | I/O           | TTL                    | RA2 can also be analog input2                                                                                                                                                                            |

| RA3/AN3/Vref            | 5           | 6                 | 22          | I/O           | TTL                    | RA3 can also be analog input3 or analog reference voltage                                                                                                                                                |

| RA4/T0CKI               | 6           | 7                 | 23          | I/O           | ST                     | RA4 can also be the clock input to the Timer0 timer/ counter. Output is open drain type.                                                                                                                 |

| RA5/ <del>SS</del> /AN4 | 7           | 8                 | 24          | I/O           | TTL                    | RA5 can also be analog input4 or the slave select for the synchronous serial port.                                                                                                                       |

|                         |             |                   |             |               |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                            |

| RB0/INT                 | 33          | 36                | 8           | I/O           | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                              |

| RB1                     | 34          | 37                | 9           | I/O           | TTL                    |                                                                                                                                                                                                          |

| RB2                     | 35          | 38                | 10          | I/O           | TTL                    |                                                                                                                                                                                                          |

| RB3                     | 36          | 39                | 11          | I/O           | TTL                    |                                                                                                                                                                                                          |

| RB4                     | 37          | 41                | 14          | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                 |

| RB5                     | 38          | 42                | 15          | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                 |

| RB6                     | 39          | 43                | 16          | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming clock.                                                                                                                                                       |

| RB7                     | 40          | 44                | 17          | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming data.                                                                                                                                                        |

| Legend: I = input       | 0 = 0       | utput<br>lot used |             |               | put/output             | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                  |

| TABLE 3-3: PIC16C/4//4A/// PINOUT DESCRIPTION | TABLE 3-3: | PIC16C74/74A/77 PINOUT DESCRIPTION |

|-----------------------------------------------|------------|------------------------------------|

|-----------------------------------------------|------------|------------------------------------|

— = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

| IABLE                | <b>4-Z</b> . |                      | 3// 3A// 4         | 114A SP                 | ECIAL FU         | INC HOIN     | REGISI        | ER SUN         |          | (Cont.a)                 |                                     |

|----------------------|--------------|----------------------|--------------------|-------------------------|------------------|--------------|---------------|----------------|----------|--------------------------|-------------------------------------|

| Address              | Name         | Bit 7                | Bit 6              | Bit 5                   | Bit 4            | Bit 3        | Bit 2         | Bit 1          | Bit 0    | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(2) |

| Bank 1               |              | •                    |                    | ·                       |                  |              |               |                |          | -                        |                                     |

| 80h <sup>(4)</sup>   | INDF         | Addressing           | this location      | uses conter             | nts of FSR to ac | dress data i | memory (not   | a physical re  | egister) | 0000 0000                | 0000 0000                           |

| 81h                  | OPTION       | RBPU                 | INTEDG             | TOCS                    | TOSE             | PSA          | PS2           | PS1            | PS0      | 1111 1111                | 1111 1111                           |

| 82h <sup>(4)</sup>   | PCL          | Program Co           | ounter's (PC)      | Least Signif            | ficant Byte      | •            | •             |                |          | 0000 0000                | 0000 0000                           |

| 83h <sup>(4)</sup>   | STATUS       | IRP(7)               | RP1 <sup>(7)</sup> | RP0                     | TO               | PD           | Z             | DC             | С        | 0001 1xxx                | 000q quuu                           |

| 84h <sup>(4)</sup>   | FSR          | Indirect data        | a memory ad        | ldress pointe           | er               |              |               |                |          | XXXX XXXX                | uuuu uuuu                           |

| 85h                  | TRISA        | —                    | —                  | PORTA Dat               | ta Direction Re  | gister       |               |                |          | 11 1111                  | 11 1111                             |

| 86h                  | TRISB        | PORTB Dat            | a Direction F      | Register                |                  |              |               |                |          | 1111 1111                | 1111 1111                           |

| 87h                  | TRISC        | PORTC Dat            | ta Direction F     | Register                |                  |              |               |                |          | 1111 1111                | 1111 1111                           |

| 88h <b>(5)</b>       | TRISD        | PORTD Dat            | ta Direction F     | Register                |                  |              |               |                |          | 1111 1111                | 1111 1111                           |

| 89h <b>(5)</b>       | TRISE        | IBF                  | OBF                | IBOV                    | PSPMODE          | —            | PORTE Da      | ta Direction E | Bits     | 0000 -111                | 0000 -111                           |

| 8Ah <sup>(1,4)</sup> | PCLATH       | —                    | —                  | —                       | Write Buffer fo  | or the upper | 5 bits of the | Program Cou    | unter    | 0 0000                   | 0 0000                              |

| 8Bh <sup>(4)</sup>   | INTCON       | GIE                  | PEIE               | TOIE                    | INTE             | RBIE         | TOIF          | INTF           | RBIF     | 0000 000x                | 0000 000u                           |

| 8Ch                  | PIE1         | PSPIE <sup>(3)</sup> | ADIE               | RCIE                    | TXIE             | SSPIE        | CCP1IE        | TMR2IE         | TMR1IE   | 0000 0000                | 0000 0000                           |

| 8Dh                  | PIE2         | —                    | —                  | —                       | —                | —            | —             | —              | CCP2IE   | 0                        | 0                                   |

| 8Eh                  | PCON         | —                    | —                  | —                       | -                | —            | _             | POR            | BOR(6)   | dd                       | uu                                  |

| 8Fh                  | —            | Unimpleme            | nted               |                         |                  |              |               |                |          | -                        | —                                   |

| 90h                  | —            | Unimpleme            | nted               |                         |                  |              |               |                |          | -                        | —                                   |

| 91h                  | _            | Unimpleme            | nted               |                         |                  |              |               |                |          | —                        | —                                   |

| 92h                  | PR2          | Timer2 Peri          | od Register        |                         |                  |              |               |                |          | 1111 1111                | 1111 1111                           |

| 93h                  | SSPADD       | Synchronou           | is Serial Port     | (I <sup>2</sup> C mode) | Address Regis    | ter          |               |                |          | 0000 0000                | 0000 0000                           |

| 94h                  | SSPSTAT      | —                    | —                  | D/Ā                     | Р                | S            | R/W           | UA             | BF       | 00 0000                  | 00 0000                             |

| 95h                  | —            | Unimpleme            | nted               | •                       |                  |              |               |                |          | -                        | _                                   |

| 96h                  | —            | Unimpleme            | nted               |                         |                  |              |               |                |          | -                        | —                                   |

| 97h                  | —            | Unimpleme            | nted               |                         |                  |              |               |                |          | -                        | -                                   |

| 98h                  | TXSTA        | CSRC                 | TX9                | TXEN                    | SYNC             | _            | BRGH          | TRMT           | TX9D     | 0000 -010                | 0000 -010                           |

| 99h                  | SPBRG        | Baud Rate            | Generator Re       | egister                 |                  |              |               |                |          | 0000 0000                | 0000 0000                           |

| 9Ah                  | _            | Unimpleme            | nted               |                         |                  |              |               |                |          | -                        | _                                   |

| 9Bh                  | —            | Unimpleme            | nted               |                         |                  |              |               |                |          | -                        | -                                   |

| 9Ch                  | _            | Unimpleme            | nted               |                         |                  |              |               |                |          |                          | _                                   |

| 9Dh                  | —            | Unimpleme            | nted               |                         |                  |              |               |                |          | _                        | _                                   |

| 9Eh                  | —            | Unimpleme            | nted               |                         |                  |              |               |                |          | -                        | _                                   |

| 9Fh                  | ADCON1       | _                    | _                  | _                       | _                | _            | PCFG2         | PCFG1          | PCFG0    | 000                      | 000                                 |

#### TABLE 4-2: PIC16C73/73A/74/74A SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A, always maintain these bits clear.

- 4: These registers can be addressed from either bank.

- 5: PORTD and PORTE are not physically implemented on the PIC16C73/73A, read as '0'.

- 6: Brown-out Reset is not implemented on the PIC16C73 or the PIC16C74, read as '0'.

7: The IRP and RP1 bits are reserved on the PIC16C73/73A/74/74A, always maintain these bits clear.

## TABLE 5-1: PORTA FUNCTIONS

| Name         | Bit# | Buffer | Function                                                                       |

|--------------|------|--------|--------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF                                           |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0                                |

|              |      |        | Output is open drain type                                                      |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input |

Legend: TTL = TTL input, ST = Schmitt Trigger input

# TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5     | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|--------|-------|-------|-----------|-------------------------------|-------|-------|-------|-------|--------------------------|---------------------------|

| 05h     | PORTA  | —     | _     | RA5       | RA4                           | RA3   | RA2   | RA1   | RA0   | 0x 0000                  | 0u 0000                   |

| 85h     | TRISA  | —     | —     | PORTA Dat | PORTA Data Direction Register |       |       |       |       | 11 1111                  | 11 1111                   |

| 9Fh     | ADCON1 | —     |       | —         | _                             | _     | PCFG2 | PCFG1 | PCFG0 | 000                      | 000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

# 5.6 <u>I/O Programming Considerations</u> Applicable Devices 72 73 73A 74 74A 76 77

#### 5.6.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched to an output, the content of the data latch may now be unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (ex. BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-4 shows the effect of two sequential readmodify-write instructions on an I/O port.

#### EXAMPLE 5-4: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

;Initial PORT settings: PORTB<7:4> Inputs

; PORTB<3:0> Outputs

;PORTB<7:6> have external pull-ups and are

;not connected to other circuitry

| i |     |         |     |   |      |       |           |  |

|---|-----|---------|-----|---|------|-------|-----------|--|

| ; |     |         |     |   | PORT | latch | PORT pins |  |

| ; |     |         |     |   |      |       |           |  |

|   | BCF | PORTB,  | 7   | ; | 01pp | pppp  | 11pp pppp |  |

|   | BCF | PORTB,  | 6   | ; | 10pp | pppp  | llpp pppp |  |

|   | BSF | STATUS, | RP0 | ; |      |       |           |  |

|   | BCF | TRISB,  | 7   | ; | 10pp | pppp  | 11pp pppp |  |

|   | BCF | TRISB,  | 6   | ; | 10pp | pppp  | 10pp pppp |  |

| ; |     |         |     |   |      |       |           |  |

|   |     |         |     |   |      |       |           |  |

;Note that the user may have expected the ;pin values to be 00pp ppp. The 2nd BCF ;caused RB7 to be latched as the pin value ;(high).

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

#### 5.6.2 SUCCESSIVE OPERATIONS ON I/O PORTS

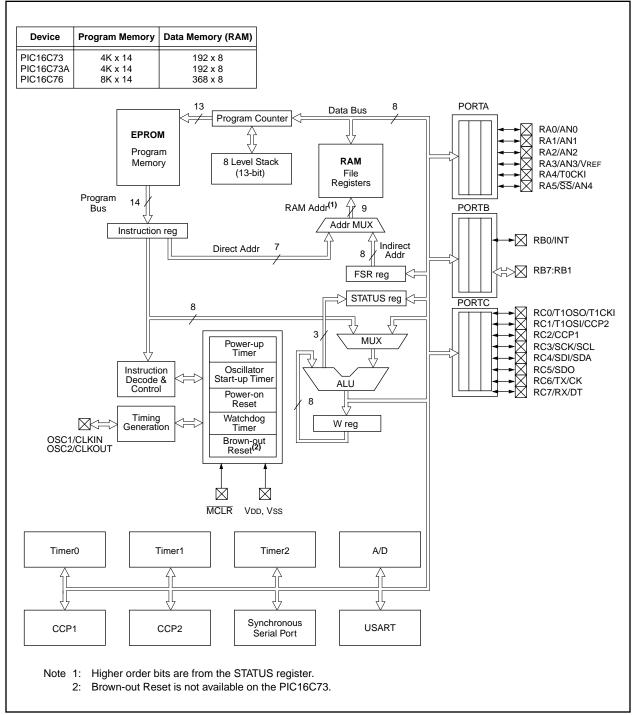

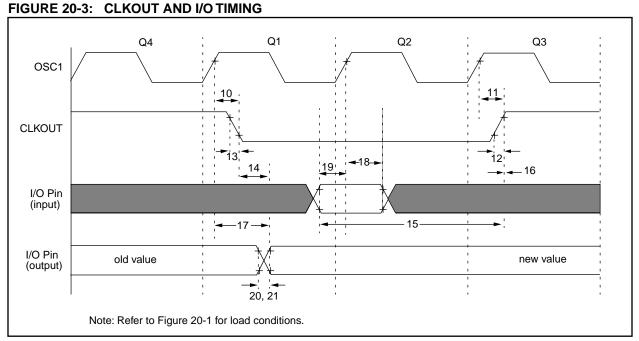

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-10). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/ O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before the next instruction which causes that file to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

# FIGURE 5-10: SUCCESSIVE I/O OPERATION

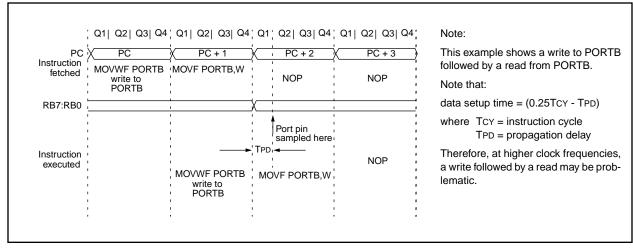

# 5.7 Parallel Slave Port Applicable Devices 72 73 73 74 74 76 77

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port when control bit PSPMODE (TRISE<4>) is set. In slave mode it is asynchronously readable and writable by the external world through  $\overline{RD}$  control input pin RE0/ $\overline{RD}$ /AN5 and  $\overline{WR}$  control input pin RE1/ $\overline{WR}$ /AN6.

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD/AN5 to be the RD input, RE1/ WR/AN6 to be the WR input and RE2/CS/AN7 to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set) and the A/D port configuration bits PCFG2:PCFG0 (ADCON1<2:0>) must be set, which will configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches, one for data-out (from the PIC16/17) and one for data input. The user writes 8-bit data to PORTD data latch and reads data from the port pin latch (note that they have the same address). In this mode, the TRISD register is ignored, since the microprocessor is controlling the direction of data flow.

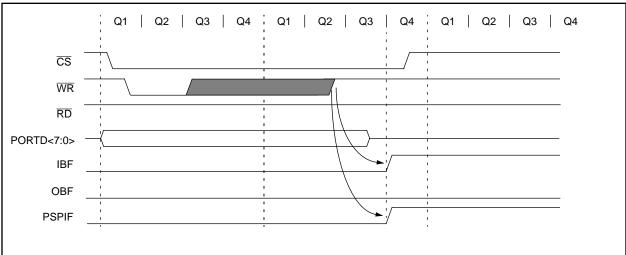

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$ lines are first detected low. When either the  $\overline{CS}$  or  $\overline{WR}$ lines become high (level triggered), then the Input Buffer Full status flag bit IBF (TRISE<7>) is set on the Q4 clock cycle, following the next Q2 cycle, to signal the write is complete (Figure 5-12). The interrupt flag bit PSPIF (PIR1<7>) is also set on the same Q4 clock cycle. IBF can only be cleared by reading the PORTD input latch. The input Buffer Overflow status flag bit IBOV (TRISE<5>) is set if a second write to the Parallel Slave Port is attempted when the previous byte has not been read out of the buffer.

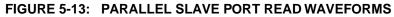

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The Output Buffer Full status flag bit OBF (TRISE<6>) is cleared immediately (Figure 5-13) indicating that the PORTD latch is waiting to be read by the external bus. When either the  $\overline{CS}$  or  $\overline{RD}$  pin becomes high (level triggered), the interrupt flag bit PSPIF is set on the Q4 clock cycle, following the next Q2 cycle, indicating that the read is complete. OBF remains low until data is written to PORTD by the user firmware.

When not in Parallel Slave Port mode, the IBF and OBF bits are held clear. However, if flag bit IBOV was previously set, it must be cleared in firmware.

An interrupt is generated and latched into flag bit PSPIF when a read or write operation is completed. PSPIF must be cleared by the user in firmware and the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

#### FIGURE 5-11: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

FIGURE 5-12: PARALLEL SLAVE PORT WRITE WAVEFORMS

| Address | Name   | Bit 7    | Bit 6   | Bit 5  | Bit 4           | Bit 3   | Bit 2    | Bit 1         | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|--------|----------|---------|--------|-----------------|---------|----------|---------------|--------|--------------------------|---------------------------|

| 08h     | PORTD  | Port dat | a latch | when w | ritten: Port pi | ns when | read     |               |        | xxxx xxxx                | uuuu uuuu                 |

| 09h     | PORTE  | _        | —       | _      | _               | _       | RE2      | RE1           | RE0    | xxx                      | uuu                       |

| 89h     | TRISE  | IBF      | OBF     | IBOV   | PSPMODE         | —       | PORTE Da | ata Directior | n Bits | 0000 -111                | 0000 -111                 |

| 0Ch     | PIR1   | PSPIF    | ADIF    | RCIF   | TXIF            | SSPIF   | CCP1IF   | TMR2IF        | TMR1IF | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1   | PSPIE    | ADIE    | RCIE   | TXIE            | SSPIE   | CCP1IE   | TMR2IE        | TMR1IE | 0000 0000                | 0000 0000                 |

| 9Fh     | ADCON1 | —        | —       |        | —               | _       | PCFG2    | PCFG1         | PCFG0  | 000                      | 000                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Parallel Slave Port.

# 8.3 <u>Timer1 Operation in Asynchronous</u> <u>Counter Mode</u> Applicable Devices 72 73 73A 74 74A 76 77

If control bit T1SYNC (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt on overflow which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 8.3.2).

In asynchronous counter mode, Timer1 can not be used as a time-base for capture or compare operations.

# 8.3.1 EXTERNAL CLOCK INPUT TIMING WITH UNSYNCHRONIZED CLOCK

If control bit T1SYNC is set, the timer will increment completely asynchronously. The input clock must meet certain minimum high time and low time requirements. Refer to the appropriate Electrical Specifications Section, timing parameters 45, 46, and 47.

# 8.3.2 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running, from an external asynchronous clock, will guarantee a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself poses certain problems since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Example 8-1 is an example routine to read the 16-bit timer value. This is useful if the timer cannot be stopped.

#### EXAMPLE 8-1: READING A 16-BIT FREE-RUNNING TIMER

```

; All interrupts are disabled

MOVE

TMR1H, W ;Read high byte

MOVWF TMPH

;

TMR1L, W ;Read low byte

MOVF

MOVWE TMPL

;

MOVF

TMR1H, W ;Read high byte

TMPH, W ;Sub 1st read

SUBWF

; with 2nd read

BTFSC STATUS,Z ;Is result = 0

CONTINUE ;Good 16-bit read

GOTO

;

; TMR1L may have rolled over between the read

of the high and low bytes. Reading the high

;

and low bytes now will read a good value.

MOVF

TMR1H, W ;Read high byte

MOVWF

TMPH

TMR1L, W ;Read low byte

MOVE

MOVWE TMPL

;

; Re-enable the Interrupt (if required)

;Continue with your code

CONTINUE

```

# 8.4 <u>Timer1 Oscillator</u> Applicable Devices 72 73 73 74 74 76 77

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 8-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

# TABLE 8-1: CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR

| Osc Type                               | pe Freq C1 C2                                                                                                |               |          |  |  |  |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------|----------|--|--|--|--|

| LP                                     | 32 kHz 33 pF 33 pF                                                                                           |               |          |  |  |  |  |

|                                        | 100 kHz                                                                                                      | 15 pF         | 15 pF    |  |  |  |  |

|                                        | 200 kHz 15 pF 15 pF                                                                                          |               |          |  |  |  |  |

| These v                                | alues are for o                                                                                              | design guidan | ce only. |  |  |  |  |

| <b>Crystals Tes</b>                    | ted:                                                                                                         |               |          |  |  |  |  |

| 32.768 kHz                             | 32.768 kHz Epson C-001R32.768K-A ± 20 PP                                                                     |               |          |  |  |  |  |

| 100 kHz                                | Hz Epson C-2 100.00 KC-P ± 20 PPM                                                                            |               |          |  |  |  |  |

| 200 kHz                                | kHz STD XTL 200.000 kHz ± 20 PPN                                                                             |               |          |  |  |  |  |

| of o<br>time<br>2: Sind<br>cha<br>reso | lote 1: Higher capacitance increases the stability<br>of oscillator but also increases the start-up<br>time. |               |          |  |  |  |  |

#### 12.1.1 SAMPLING

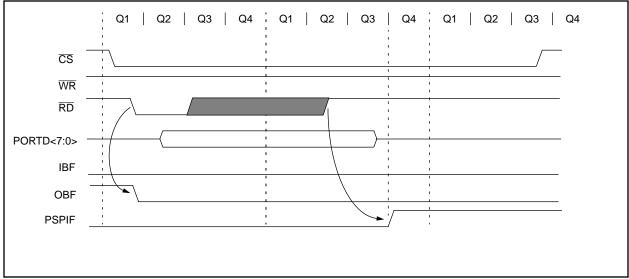

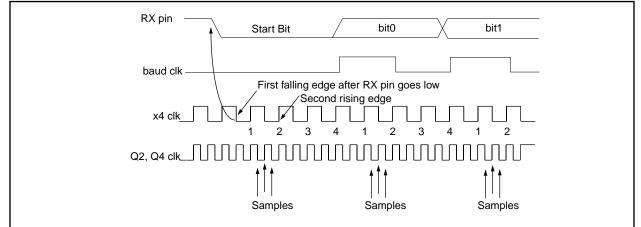

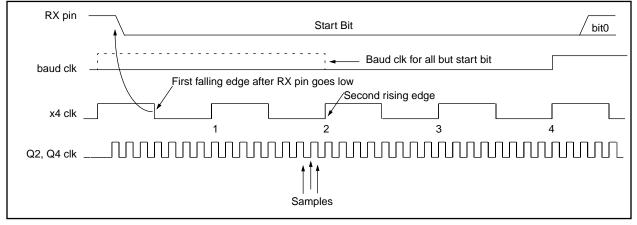

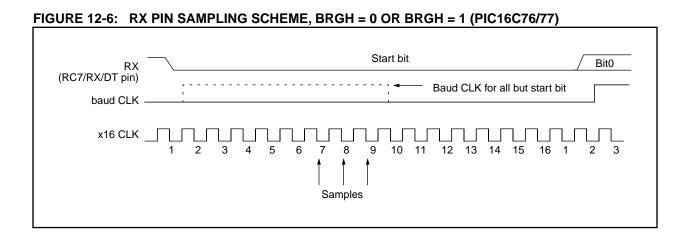

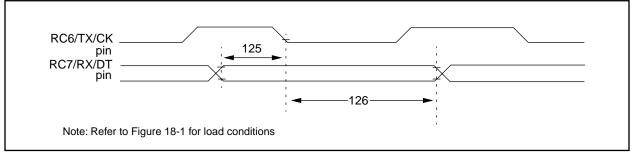

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin. If bit BRGH (TXSTA<2>) is clear (i.e., at the low baud rates), the sampling is done on the seventh, eighth and ninth falling edges of a x16 clock (Figure 12-3). If bit BRGH is set (i.e., at the high baud rates), the sampling is done on the 3 clock edges preceding the second rising edge after the first falling edge of a x4 clock (Figure 12-4 and Figure 12-5).

# FIGURE 12-3: RX PIN SAMPLING SCHEME. BRGH = 0 (PIC16C73/73A/74/74A)

#### FIGURE 12-4: RX PIN SAMPLING SCHEME, BRGH = 1 (PIC16C73/73A/74/74A)

# 13.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

# Applicable Devices

The analog-to-digital (A/D) converter module has five inputs for the PIC16C72/73/73A/76, and eight for the PIC16C74/74A/77.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the RA3/AN3/VREF pin. The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

The ADCON0 register, shown in Figure 13-1, controls the operation of the A/D module. The ADCON1 register, shown in Figure 13-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/O.

| R/W-0                                                                         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0     | R/W-0      | R/W-0      | R/W-0   | U-0 | R/W-0 |                  |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|------------|---------|-----|-------|------------------|

| ADCS1                                                                         | ADCS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CHS2      | CHS1       | CHS0       | GO/DONE | _   | ADON  | R = Readable bit |

| bit7                                                                          | bito bito visual construction c |           |            |            |         |     |       |                  |

| bit 7-6:                                                                      | t 7-6: ADCS1:ADCS0: A/D Conversion Clock Select bits<br>00 = Fosc/2<br>01 = Fosc/8<br>10 = Fosc/32<br>11 = FRC (clock derived from an internal RC oscillator)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |            |            |         |     |       |                  |

| bit 5-3:                                                                      | bit 5-3: <b>CHS2:CHS0</b> : Analog Channel Select bits<br>000 = channel 0, (RA0/AN0)<br>001 = channel 1, (RA1/AN1)<br>010 = channel 2, (RA2/AN2)<br>011 = channel 3, (RA3/AN3)<br>100 = channel 4, (RA5/AN4)<br>$101 = channel 5, (RE0/AN5)^{(1)}$<br>$110 = channel 6, (RE1/AN6)^{(1)}$<br>$111 = channel 7, (RE2/AN7)^{(1)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |            |            |         |     |       |                  |

| bit 2:                                                                        | GO/DON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | E: A/D Co | nversion S | Status bit |         |     |       |                  |

|                                                                               | <u>If ADON = 1</u><br>1 = A/D conversion in progress (setting this bit starts the A/D conversion)<br>0 = A/D conversion not in progress (This bit is automatically cleared by hardware when the A/D conversion<br>is complete)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |            |            |         |     |       |                  |

| bit 1:                                                                        | Unimpler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nented: F | Read as '0 | ,          |         |     |       |                  |

| bit 0:                                                                        | <ul> <li>t 0: ADON: A/D On bit</li> <li>1 = A/D converter module is operating</li> <li>0 = A/D converter module is shutoff and consumes no operating current</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |            |            |         |     |       |                  |

| Note 1: A/D channels 5, 6, and 7 are implemented on the PIC16C74/74A/77 only. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |            |            |         |     |       |                  |

# FIGURE 13-1: ADCON0 REGISTER (ADDRESS 1Fh)

#### 14.5.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered: either rising if bit INTEDG (OPTION<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 14.8 for details on SLEEP mode.

#### 14.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>). (Section 7.0)

#### 14.5.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>). (Section 5.2)

| Note: | For the PIC16C73/74, if a change on the      |

|-------|----------------------------------------------|

|       | I/O pin should occur when the read opera-    |

|       | tion is being executed (start of the Q2      |

|       | cycle), then the RBIF interrupt flag may not |

|       | get set.                                     |

#### 14.6 <u>Context Saving During Interrupts</u> Applicable Devices

# 72 73 73A 74 74A 76 77

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt i.e., W register and STATUS register. This will have to be implemented in software.

Example 14-1 stores and restores the STATUS, W, and PCLATH registers. The register, W\_TEMP, must be defined in each bank and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1).

The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Stores the PCLATH register.

- d) Executes the ISR code.

- e) Restores the STATUS register (and bank select bit).

- f) Restores the W and PCLATH registers.

#### EXAMPLE 14-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

| MOVWF<br>SWAPF<br>CLRF | W_TEMP<br>STATUS,W<br>STATUS | ;Copy W to TEMP register, could be bank one or zero<br>;Swap status to be saved into W<br>;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

|------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVWF                  | STATUS_TEMP                  | ;Save status to bank zero STATUS_TEMP register                                                                                                    |

| MOVF                   | PCLATH, W                    | ;Only required if using pages 1, 2 and/or 3                                                                                                       |

| MOVWF                  | PCLATH_TEMP                  | ;Save PCLATH into W                                                                                                                               |

| CLRF                   | PCLATH                       | ;Page zero, regardless of current page                                                                                                            |

| BCF                    | STATUS, IRP                  | ;Return to Bank 0                                                                                                                                 |

| MOVF                   | FSR, W                       | ;Copy FSR to W                                                                                                                                    |

| MOVWF                  | FSR_TEMP                     | ;Copy FSR from W to FSR_TEMP                                                                                                                      |

| :                      |                              |                                                                                                                                                   |

| :(ISR)                 |                              |                                                                                                                                                   |

| :                      |                              |                                                                                                                                                   |

| MOVF                   | PCLATH_TEMP, W               | ;Restore PCLATH                                                                                                                                   |

| MOVWF                  | PCLATH                       | ;Move W into PCLATH                                                                                                                               |

| SWAPF                  | STATUS_TEMP,W                | ;Swap STATUS_TEMP register into W                                                                                                                 |

|                        |                              | ;(sets bank to original state)                                                                                                                    |

| MOVWF                  | STATUS                       | ;Move W into STATUS register                                                                                                                      |

| SWAPF                  | W_TEMP,F                     | ;Swap W_TEMP                                                                                                                                      |

| SWAPF                  | W_TEMP,W                     | ;Swap W_TEMP into W                                                                                                                               |

|                        |                              |                                                                                                                                                   |

# 15.1 Instruction Descriptions

| ADDLW             | Add Lite            | ral and                                                                                                                 | N               |               |  |  |  |  |  |

|-------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|--|--|--|--|--|

| Syntax:           | [ <i>label</i> ] Al | DDLW                                                                                                                    | k               |               |  |  |  |  |  |

| Operands:         | $0 \le k \le 2k$    | 55                                                                                                                      |                 |               |  |  |  |  |  |

| Operation:        | (W) + k –           | $(W) + k \to (W)$                                                                                                       |                 |               |  |  |  |  |  |

| Status Affected:  | C, DC, Z            |                                                                                                                         |                 |               |  |  |  |  |  |

| Encoding:         | 11                  | 111x                                                                                                                    | kkkk            | kkkk          |  |  |  |  |  |

| Description:      | added to t          | The contents of the W register are<br>added to the eight bit literal 'k' and the<br>result is placed in the W register. |                 |               |  |  |  |  |  |

| Words:            | 1                   |                                                                                                                         |                 |               |  |  |  |  |  |

| Cycles:           | 1                   |                                                                                                                         |                 |               |  |  |  |  |  |

| Q Cycle Activity: | Q1                  | Q2                                                                                                                      | Q3              | Q4            |  |  |  |  |  |

|                   | Decode              | Read<br>literal 'k'                                                                                                     | Process<br>data | Write to<br>W |  |  |  |  |  |

| Example:          | ADDLW               | 0x15                                                                                                                    |                 |               |  |  |  |  |  |

|                   | Before In           | struction                                                                                                               | 1               |               |  |  |  |  |  |

|                   |                     | = W                                                                                                                     | 0x10            |               |  |  |  |  |  |

|                   | After Inst          |                                                                                                                         | 005             |               |  |  |  |  |  |

|                   |                     | W =                                                                                                                     | 0x25            |               |  |  |  |  |  |

|                   |                     |                                                                                                                         |                 |               |  |  |  |  |  |

| ADDWF             | Add W a             | nd f                                                                                                                    |                 |               |  |  |  |  |  |

| Syntax:           | [ <i>label</i> ] A  | DDWF                                                                                                                    | f,d             |               |  |  |  |  |  |

| Operands:         | $0 \le f \le 12$    | 27                                                                                                                      |                 |               |  |  |  |  |  |

| ANDLW             | AND Lite                               | eral with              | w               |               |

|-------------------|----------------------------------------|------------------------|-----------------|---------------|

| Syntax:           | [ <i>label</i> ] A                     | NDLW                   | k               |               |

| Operands:         | $0 \le k \le 2$                        | 55                     |                 |               |

| Operation:        | (W) .AND                               | D. (k) $\rightarrow$ ( | W)              |               |

| Status Affected:  | Z                                      |                        |                 |               |

| Encoding:         | 11                                     | 1001                   | kkkk            | kkkk          |

| Description:      | The conte<br>AND'ed wi<br>result is pl | ith the eig            | 0               | l 'k'. The    |

| Words:            | 1                                      |                        |                 |               |

| Cycles:           | 1                                      |                        |                 |               |

| Q Cycle Activity: | Q1                                     | Q2                     | Q3              | Q4            |

|                   | Decode                                 | Read<br>literal "k"    | Process<br>data | Write to<br>W |

| Example           | ANDLW                                  | 0x5F                   |                 |               |

|                   | Before In                              | struction              | 1               |               |

|                   |                                        | W =                    | 0xA3            |               |

|                   | After Inst                             | W =                    | 0x03            |               |

|                   |                                        |                        |                 |               |

| ANDWF             | AND W v                                | vith f                 |                 |               |

| Syntax:           | [ <i>label</i> ] A                     | NDWF                   | f,d             |               |

| Operands:         | $0 \le f \le 12$                       | 27                     |                 |               |

| ADDWF             | Add W and f                           |                                                                                                                                                                           |                 |                      |  |  |  |  |

|-------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|--|--|--|--|

| Syntax:           | [ <i>label</i> ] A                    | DDWF                                                                                                                                                                      | f,d             |                      |  |  |  |  |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                         |                 |                      |  |  |  |  |

| Operation:        | (W) + (f) $\rightarrow$ (destination) |                                                                                                                                                                           |                 |                      |  |  |  |  |

| Status Affected:  | C, DC, Z                              |                                                                                                                                                                           |                 |                      |  |  |  |  |

| Encoding:         | 00                                    | 0111                                                                                                                                                                      | dfff            | ffff                 |  |  |  |  |

| Description:      | register 'f'.<br>in the W re          | Add the contents of the W register with<br>register 'f'. If 'd' is 0 the result is stored<br>in the W register. If 'd' is 1 the result is<br>stored back in register 'f'. |                 |                      |  |  |  |  |

| Words:            | 1                                     |                                                                                                                                                                           |                 |                      |  |  |  |  |

| Cycles:           | 1                                     |                                                                                                                                                                           |                 |                      |  |  |  |  |

| Q Cycle Activity: | Q1                                    | Q2                                                                                                                                                                        | Q3              | Q4                   |  |  |  |  |

|                   | Decode                                | Read<br>register<br>'f'                                                                                                                                                   | Process<br>data | Write to destination |  |  |  |  |

| Example           | ADDWF                                 | FSR,                                                                                                                                                                      | 0               |                      |  |  |  |  |