Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 22                                                                           |

| Program Memory Size        | 7KB (4K x 14)                                                                |

| Program Memory Type        | ОТР                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 192 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                    |

| Data Converters            | A/D 5x8b                                                                     |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc73at-04i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.0 ARCHITECTURAL OVERVIEW

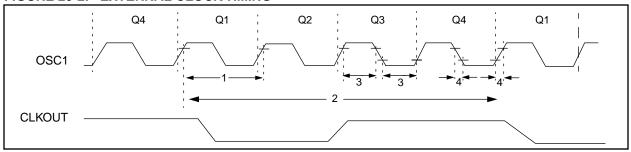

The high performance of the PIC16CXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXX uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture in which program and data are fetched from the same memory using the same bus. Separating program and data buses further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The table below lists program memory (EPROM) and data memory (RAM) for each PIC16C7X device.

| Device    | Program<br>Memory | Data Memory |

|-----------|-------------------|-------------|

| PIC16C72  | 2K x 14           | 128 x 8     |

| PIC16C73  | 4K x 14           | 192 x 8     |

| PIC16C73A | 4K x 14           | 192 x 8     |

| PIC16C74  | 4K x 14           | 192 x 8     |

| PIC16C74A | 4K x 14           | 192 x 8     |

| PIC16C76  | 8K x 14           | 368 x 8     |

| PIC16C77  | 8K x 14           | 386 x 8     |

The PIC16CXX can directly or indirectly address its register files or data memory. All special function registers, including the program counter, are mapped in the data memory. The PIC16CXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16CXX simple yet efficient. In addition, the learning curve is reduced significantly.

PIC16CXX devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between the data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow bit and a digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

TABLE 4-2: PIC16C73/73A/74/74A SPECIAL FUNCTION REGISTER SUMMARY

| Address              | Name    | Bit 7                                                                       | Bit 6                                                 | Bit 5              | Bit 4           | Bit 3         | Bit 2         | Bit 1         | Bit 0    | Value on:<br>POR,<br>BOR | Value on all other resets (2) |

|----------------------|---------|-----------------------------------------------------------------------------|-------------------------------------------------------|--------------------|-----------------|---------------|---------------|---------------|----------|--------------------------|-------------------------------|

| Bank 0               | (0      |                                                                             |                                                       |                    |                 |               |               |               |          |                          |                               |

| 00h <sup>(4)</sup>   | INDF    | Addressing                                                                  | this location                                         | uses conten        | ts of FSR to ac | ddress data r | memory (not   | a physical re | egister) | 0000 0000                | 0000 0000                     |

| 01h                  | TMR0    | Timer0 mod                                                                  | lule's registe                                        |                    | xxxx xxxx       | uuuu uuuu     |               |               |          |                          |                               |

| 02h <sup>(4)</sup>   | PCL     | Program Co                                                                  | ounter's (PC)                                         |                    | 0000 0000       | 0000 0000     |               |               |          |                          |                               |

| 03h <sup>(4)</sup>   | STATUS  | IRP <sup>(7)</sup>                                                          | RP <sup>(7)</sup> RP1 <sup>(7)</sup> RP0 TO PD Z DC C |                    |                 |               |               |               |          |                          | 000q quuu                     |

| 04h <sup>(4)</sup>   | FSR     | Indirect data memory address pointer                                        |                                                       |                    |                 |               |               |               |          |                          | uuuu uuuu                     |

| 05h                  | PORTA   | _                                                                           | _                                                     |                    | 0x 0000         | 0u 0000       |               |               |          |                          |                               |

| 06h                  | PORTB   | PORTB Dat                                                                   | ta Latch whe                                          | n written: PC      | RTB pins whe    | n read        |               |               |          | xxxx xxxx                | uuuu uuuu                     |

| 07h                  | PORTC   | PORTC Da                                                                    | ta Latch whe                                          | n written: PC      | ORTC pins whe   | n read        |               |               |          | xxxx xxxx                | uuuu uuuu                     |

| 08h <sup>(5)</sup>   | PORTD   | PORTD Da                                                                    | ta Latch whe                                          | n written: PC      | ORTD pins whe   | n read        |               |               |          | xxxx xxxx                | uuuu uuuu                     |

| 09h <sup>(5)</sup>   | PORTE   | _                                                                           | _                                                     | _                  | _               | _             | RE2           | RE1           | RE0      | xxx                      | uuu                           |

| 0Ah <sup>(1,4)</sup> | PCLATH  | _                                                                           | _                                                     | -                  | Write Buffer fo | or the upper  | 5 bits of the | Program Cou   | ınter    | 0 0000                   | 0 0000                        |

| 0Bh <sup>(4)</sup>   | INTCON  | GIE                                                                         | PEIE                                                  | TOIE               | INTE            | RBIE          | TOIF          | INTF          | RBIF     | 0000 000x                | 0000 000u                     |

| 0Ch                  | PIR1    | PSPIF <sup>(3)</sup>                                                        | ADIF                                                  | RCIF               | TXIF            | SSPIF         | CCP1IF        | TMR2IF        | TMR1IF   | 0000 0000                | 0000 0000                     |

| 0Dh                  | PIR2    | _                                                                           | _                                                     | -                  | -               | _             | _             | _             | CCP2IF   | 0                        | 0                             |

| 0Eh                  | TMR1L   | Holding register for the Least Significant Byte of the 16-bit TMR1 register |                                                       |                    |                 |               |               |               |          |                          | uuuu uuuu                     |

| 0Fh                  | TMR1H   | Holding reg                                                                 | ister for the N                                       | Nost Signification | ant Byte of the | 16-bit TMR1   | register      |               |          | xxxx xxxx                | uuuu uuuu                     |

| 10h                  | T1CON   | _                                                                           | _                                                     | T1CKPS1            | T1CKPS0         | T10SCEN       | T1SYNC        | TMR1CS        | TMR10N   | 00 0000                  | uu uuuu                       |

| 11h                  | TMR2    | Timer2 mod                                                                  | lule's registe                                        | r                  |                 |               |               |               | •        | 0000 0000                | 0000 0000                     |

| 12h                  | T2CON   | _                                                                           | TOUTPS3                                               | TOUTPS2            | TOUTPS1         | TOUTPS0       | TMR2ON        | T2CKPS1       | T2CKPS0  | -000 0000                | -000 0000                     |

| 13h                  | SSPBUF  | Synchronou                                                                  | ıs Serial Port                                        | Receive Bu         | ffer/Transmit R | egister       |               | •             | •        | xxxx xxxx                | uuuu uuuu                     |

| 14h                  | SSPCON  | WCOL                                                                        | SSPOV                                                 | SSPEN              | СКР             | SSPM3         | SSPM2         | SSPM1         | SSPM0    | 0000 0000                | 0000 0000                     |

| 15h                  | CCPR1L  | Capture/Co                                                                  | mpare/PWM                                             | Register1 (L       | -SB)            |               |               |               | •        | xxxx xxxx                | uuuu uuuu                     |

| 16h                  | CCPR1H  | Capture/Co                                                                  | mpare/PWM                                             | Register1 (N       | MSB)            |               |               |               |          | xxxx xxxx                | uuuu uuuu                     |

| 17h                  | CCP1CON | _                                                                           | _                                                     | CCP1X              | CCP1Y           | CCP1M3        | CCP1M2        | CCP1M1        | CCP1M0   | 00 0000                  | 00 0000                       |

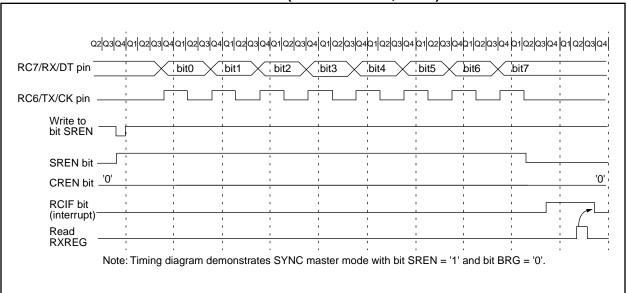

| 18h                  | RCSTA   | SPEN                                                                        | RX9                                                   | SREN               | CREN            | _             | FERR          | OERR          | RX9D     | 0000 -00x                | 0000 -00x                     |

| 19h                  | TXREG   | USART Trai                                                                  | nsmit Data R                                          | egister            |                 |               | •             | -             | •        | 0000 0000                | 0000 0000                     |

| 1Ah                  | RCREG   | USART Red                                                                   | ceive Data R                                          | egister            |                 |               |               |               |          | 0000 0000                | 0000 0000                     |

| 1Bh                  | CCPR2L  | Capture/Co                                                                  | mpare/PWM                                             | Register2 (L       | _SB)            |               |               |               |          | xxxx xxxx                | uuuu uuuu                     |

| 1Ch                  | CCPR2H  | Capture/Co                                                                  | mpare/PWM                                             | Register2 (M       | MSB)            |               |               |               |          | xxxx xxxx                | uuuu uuuu                     |

| 1Dh                  | CCP2CON | _                                                                           | _                                                     | CCP2X              | CCP2Y           | ССР2М3        | CCP2M2        | CCP2M1        | CCP2M0   | 00 0000                  | 00 0000                       |

| 1Eh                  | ADRES   | A/D Result                                                                  | Register                                              |                    |                 |               |               |               |          | xxxx xxxx                | uuuu uuuu                     |

| 1Fh                  | ADCON0  | ADCS1                                                                       | ADCS0                                                 | CHS2               | CHS1            | CHS0          | GO/DONE       | _             | ADON     | 0000 00-0                | 0000 00-0                     |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

- Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

- 2: Other (non power-up) resets include external reset through  $\overline{\text{MCLR}}$  and Watchdog Timer Reset.

- 3: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A, always maintain these bits clear.

- 4: These registers can be addressed from either bank.

- 5: PORTD and PORTE are not physically implemented on the PIC16C73/73A, read as '0'.

- 6: Brown-out Reset is not implemented on the PIC16C73 or the PIC16C74, read as '0'.

- 7: The IRP and RP1 bits are reserved on the PIC16C73/73A/74/74A, always maintain these bits clear.

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

Note: To avoid an unintended device RESET, the following instruction sequence (shown in Example 7-1) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

### **EXAMPLE 7-1: CHANGING PRESCALER (TIMER0→WDT)**

Lines 2 and 3 do NOT have to be included if the final desired prescale value is other than 1:1. If 1:1 is final desired value, then a temporary prescale value is set in lines 2 and 3 and the final prescale value will be set in lines 10 and 11.

```

STATUS, RPO

1) BSF

2) MOVLW b'xx0x0xxx'

;Select clock source and prescale value of

3) MOVWF OPTION_REG

;other than 1:1

BCF

STATUS, RPO

;Bank 0

5) CLRF

TMR0

;Clear TMR0 and prescaler

6)

BSF

STATUS, RP1

;Bank 1

MOVLW b'xxxx1xxx'

;Select WDT, do not change prescale value

7)

MOVWF OPTION_REG

8)

9)

CLRWDT

;Clears WDT and prescaler

10) MOVLW b'xxxx1xxx'

;Select new prescale value and WDT

11) MOVWF OPTION_REG

12) BCF

STATUS, RPO

;Bank 0

```

To change prescaler from the WDT to the Timer0 module use the sequence shown in Example 7-2.

### **EXAMPLE 7-2: CHANGING PRESCALER (WDT→TIMER0)**

```

CLRWDT ;Clear WDT and prescaler

BSF STATUS, RP0 ;Bank 1

MOVLW b'xxxx0xxx' ;Select TMR0, new prescale value and

MOVWF OPTION_REG ;clock source

BCF STATUS, RP0 ;Bank 0

```

### TABLE 7-1: REGISTERS ASSOCIATED WITH TIMERO

| Address               | Name   | Bit 7  | Bit 6             | Bit 5    | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------------------|--------|--------|-------------------|----------|-------------------------------|-------|-------|-------|-------|--------------------------|---------------------------|

| 01h,101h              | TMR0   | Timer0 | module's register |          |                               |       |       |       |       | xxxx xxxx                | uuuu uuuu                 |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE    | PEIE              | TOIE     | INTE                          | RBIE  | T0IF  | INTF  | RBIF  | 0000 000x                | 0000 000u                 |

| 81h,181h              | OPTION | RBPU   | INTEDG            | T0CS     | TOCS TOSE PSA PS2 PS1 PS0     |       |       |       |       | 1111 1111                | 1111 1111                 |

| 85h                   | TRISA  | _      | _                 | PORTA Da | PORTA Data Direction Register |       |       |       |       |                          | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

### 8.3 <u>Timer1 Operation in Asynchronous</u> Counter Mode

Applicable Devices 72 73 73A 74 74A 76 77

If control bit T1SYNC (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt on overflow which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 8.3.2).

In asynchronous counter mode, Timer1 can not be used as a time-base for capture or compare operations.

### 8.3.1 EXTERNAL CLOCK INPUT TIMING WITH UNSYNCHRONIZED CLOCK

If control bit T1SYNC is set, the timer will increment completely asynchronously. The input clock must meet certain minimum high time and low time requirements. Refer to the appropriate Electrical Specifications Section, timing parameters 45, 46, and 47.

### 8.3.2 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running, from an external asynchronous clock, will guarantee a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself poses certain problems since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Example 8-1 is an example routine to read the 16-bit timer value. This is useful if the timer cannot be stopped.

### EXAMPLE 8-1: READING A 16-BIT FREE-RUNNING TIMER

```

; All interrupts are disabled

MOVF

TMR1H, W ; Read high byte

MOVWF TMPH

MOVF

TMR1L, W ; Read low byte

MOVWE TMPL

MOVF

TMR1H, W ; Read high byte

TMPH, W ;Sub 1st read

SUBWF

; with 2nd read

BTFSC STATUS, Z ; Is result = 0

CONTINUE ; Good 16-bit read

GOTO

; TMR1L may have rolled over between the read

of the high and low bytes. Reading the high

and low bytes now will read a good value.

MOVF

TMR1H, W ; Read high byte

MOVWF

TMPH

TMR1L, W ; Read low byte

MOVF

MOVWF TMPL

; Re-enable the Interrupt (if required)

;Continue with your code

CONTINUE

```

### 8.4 Timer1 Oscillator

Applicable Devices 72 73 73 A 74 74 A 76 77

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 8-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

TABLE 8-1: CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR

| Osc Type                                   | Freq C1 C2                     |                                |          |  |  |  |  |

|--------------------------------------------|--------------------------------|--------------------------------|----------|--|--|--|--|

| LP                                         | 32 kHz                         | 33 pF                          | 33 pF    |  |  |  |  |

|                                            | 100 kHz                        | 15 pF                          | 15 pF    |  |  |  |  |

|                                            | 200 kHz                        | 15 pF                          | 15 pF    |  |  |  |  |

| These values are for design guidance only. |                                |                                |          |  |  |  |  |

| Crystals Tested:                           |                                |                                |          |  |  |  |  |

| 32.768 kHz                                 | Epson C-00                     | Epson C-001R32.768K-A ± 20 PPM |          |  |  |  |  |

| 100 kHz                                    | Epson C-2 100.00 KC-P ± 20 PPM |                                |          |  |  |  |  |

| 200 kHz                                    | STD XTL 20                     | 0.000 kHz                      | ± 20 PPM |  |  |  |  |

|                                            | • •                            |                                |          |  |  |  |  |

- Note 1: Higher capacitance increases the stability of oscillator but also increases the start-up time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

### FIGURE 10-1: CCP1CON REGISTER (ADDRESS 17h)/CCP2CON REGISTER (ADDRESS 1Dh)

U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 CCPxX **CCPxY** CCPxM3 CCPxM1 CCPxM0 R = Readable bit CCPxM2 W = Writable bit bit7 bit0 U = Unimplemented bit, read as '0' - n =Value at POR reset

bit 7-6: Unimplemented: Read as '0'

bit 5-4: CCPxX:CCPxY: PWM Least Significant bits

Capture Mode: Unused Compare Mode: Unused

PWM Mode: These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.

bit 3-0: CCPxM3:CCPxM0: CCPx Mode Select bits

0000 = Capture/Compare/PWM off (resets CCPx module)

0100 = Capture mode, every falling edge

0101 = Capture mode, every rising edge

0110 = Capture mode, every 4th rising edge

0111 = Capture mode, every 16th rising edge

1000 = Compare mode, set output on match (CCPxIF bit is set)

1001 = Compare mode, clear output on match (CCPxIF bit is set)

1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set, CCPx pin is unaffected)

1011 = Compare mode, trigger special event (CCPxIF bit is set; CCP1 resets TMR1; CCP2 resets TMR1 and starts an A/D conversion (if A/D module is enabled))

11xx = PWM mode

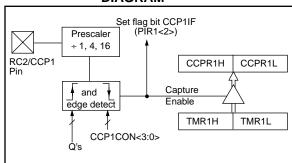

### 10.1 Capture Mode

Applicable Devices 72 73 73 A 74 74 A 76 77

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as:

- · Every falling edge

- · Every rising edge

- Every 4th rising edge

- · Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 10.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

**Note:** If the RC2/CCP1 is configured as an output, a write to the port can cause a capture condition.

# FIGURE 10-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

### 10.1.2 TIMER1 MODE SELECTION

Timer1 must be running in timer mode or synchronized counter mode for the CCP module to use the capture feature. In asynchronous counter mode, the capture operation may not work.

#### 10.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in operating mode.

### 13.4.1 FASTER CONVERSION - LOWER RESOLUTION TRADE-OFF

Not all applications require a result with 8-bits of resolution, but may instead require a faster conversion time. The A/D module allows users to make the trade-off of conversion speed to resolution. Regardless of the resolution required, the acquisition time is the same. To speed up the conversion, the clock source of the A/D module may be switched so that the TAD time violates the minimum specified time (see the applicable electrical specification). Once the TAD time violates the minimum specified time, all the following A/D result bits are not valid (see A/D Conversion Timing in the Electrical Specifications section.) The clock sources may only be switched between the three oscillator versions (cannot be switched from/to RC). The equation to determine the time before the oscillator can be switched is as follows:

Conversion time =  $2TAD + N \cdot TAD + (8 - N)(2TOSC)$ Where: N = number of bits of resolution required. Since the TAD is based from the device oscillator, the user must use some method (a timer, software loop, etc.) to determine when the A/D oscillator may be changed. Example 13-3 shows a comparison of time required for a conversion with 4-bits of resolution, versus the 8-bit resolution conversion. The example is for devices operating at 20 MHz and 16 MHz (The A/D clock is programmed for 32Tosc), and assumes that immediately after 6TAD, the A/D clock is programmed for 2Tosc.

The 2Tosc violates the minimum TAD time since the last 4-bits will not be converted to correct values.

### **EXAMPLE 13-3: 4-BIT vs. 8-BIT CONVERSION TIMES**

|                                 | - (m. )(1)                 | Resolution |         |  |

|---------------------------------|----------------------------|------------|---------|--|

|                                 | Freq. (MHz) <sup>(1)</sup> | 4-bit      | 8-bit   |  |

| TAD                             | 20                         | 1.6 μs     | 1.6 µs  |  |

|                                 | 16                         | 2.0 μs     | 2.0 μs  |  |

| Tosc                            | 20                         | 50 ns      | 50 ns   |  |

|                                 | 16                         | 62.5 ns    | 62.5 ns |  |

| 2TAD + N • TAD + (8 - N)(2TOSC) | 20                         | 10 μs      | 16 μs   |  |

|                                 | 16                         | 12.5 μs    | 20 μs   |  |

Note 1: PIC16C7X devices have a minimum TAD time of 1.6 µs.

Yes ADON = 01 No Acquire Selected Channel Yes GO = 0? No Start of A/D Conversion Delayed 1 Instruction Cycle SLEEP Instruction Finish Conversion A/D Clock = RC? GO = 0 ADIF = 1 No Νo Yes Abort Conversion Wake-up From Sleep Finish Conversion Device ir SLEEP? Wait 2 TAD GO = 0ADIF = 0 GO = 0ADIF = 1 No No SLEEP Power-down A/D Finish Conversion Stay in Sleep Power-down A/D Wait 2 TAD GO = 0 ADIF = 1 Wait 2 TAD

FIGURE 13-6: FLOWCHART OF A/D OPERATION

TABLE 13-2: REGISTERS/BITS ASSOCIATED WITH A/D, PIC16C72

| Address | Name   | Bit 7   | Bit 6      | Bit 5 | Bit 4  | Bit 3      | Bit 2     | Bit 1     | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|--------|---------|------------|-------|--------|------------|-----------|-----------|--------|--------------------------|---------------------------|

| 0Bh,8Bh | INTCON | GIE     | PEIE       | TOIE  | INTE   | RBIE       | TOIF      | INTF      | RBIF   | 0000 000x                | 0000 000u                 |

| 0Ch     | PIR1   | _       | ADIF       | _     | _      | SSPIF      | CCP1IF    | TMR2IF    | TMR1IF | -0 0000                  | -0 0000                   |

| 8Ch     | PIE1   | _       | ADIE       | _     | _      | SSPIE      | CCP1IE    | TMR2IE    | TMR1IE | -0 0000                  | -0 0000                   |

| 1Eh     | ADRES  | A/D Res | sult Regis | ter   |        |            | xxxx xxxx | uuuu uuuu |        |                          |                           |

| 1Fh     | ADCON0 | ADCS1   | ADCS0      | CHS2  | CHS1   | CHS0       | GO/DONE   | _         | ADON   | 0000 00-0                | 0000 00-0                 |

| 9Fh     | ADCON1 | _       | _          | _     | _      | _          | PCFG2     | PCFG1     | PCFG0  | 000                      | 000                       |

| 05h     | PORTA  | _       | _          | RA5   | RA4    | RA3        | RA2       | RA1       | RA0    | 0x 0000                  | 0u 0000                   |

| 85h     | TRISA  | _       | _          | PORTA | Data D | irection F | Register  |           |        | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

# 14.0 SPECIAL FEATURES OF THE CPU

**Applicable Devices** 72 | 73 | 73 A | 74 | 74 A | 76 | 77

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real-time applications. The PIC16CXX family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- · Oscillator selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- · Code protection

- ID locations

- · In-circuit serial programming

The PIC16CXX has a Watchdog Timer which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep

the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

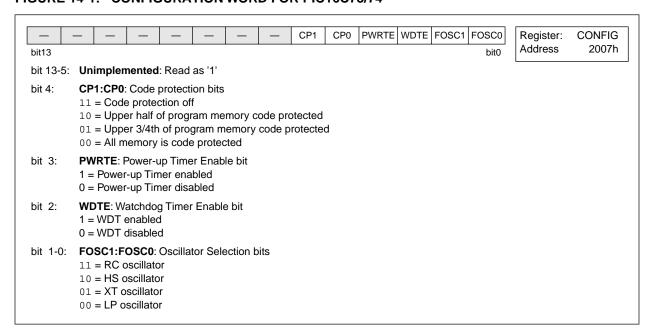

### 14.1 Configuration Bits

Applicable Devices

72 | 73 | 73 A | 74 | 74 A | 76 | 77

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

### FIGURE 14-1: CONFIGURATION WORD FOR PIC16C73/74

| XORLW                                 | Exclusive OR Literal with W                                                                                       | XORWF                          | Exclusive OR W with f                                                                                                        |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                               | [label] XORLW k                                                                                                   | Syntax:                        | [label] XORWF f,d                                                                                                            |

| Operands:                             | 0 ≤ k ≤ 255                                                                                                       | Operands:                      | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                           |

| Operation: Status Affected: Encoding: | (W) .XOR. $k \rightarrow (W)$ Z  11   1010   kkkk   kkkk                                                          | Operation:<br>Status Affected: | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                    |

| Description:                          | The contents of the W register are XOR'ed with the eight bit literal 'k'. The result is placed in the W register. | Encoding: Description:         | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0 the result is stored in the W register. If 'd' is |

| Words:                                | 1                                                                                                                 | Marda.                         | 1 the result is stored back in register 'f'.                                                                                 |

| Cycles:                               | 1                                                                                                                 | Words:                         | 1                                                                                                                            |

| Q Cycle Activity:                     | Q1 Q2 Q3 Q4                                                                                                       | Cycles:                        | 1                                                                                                                            |

|                                       | Decode Read Process Write to data W                                                                               | Q Cycle Activity:              | Q1 Q2 Q3 Q4    Decode   Read   Process   Write to   destination                                                              |

| Example:                              | XORLW 0xAF                                                                                                        |                                |                                                                                                                              |

|                                       | Before Instruction                                                                                                | Example                        | XORWF REG 1                                                                                                                  |

|                                       | W = 0xB5                                                                                                          |                                | Before Instruction                                                                                                           |

|                                       | After Instruction $W = 0x1A$                                                                                      |                                | $ \begin{array}{rcl} REG & = & 0xAF \\ W & = & 0xB5 \end{array} $                                                            |

|                                       |                                                                                                                   |                                | After Instruction                                                                                                            |

|                                       |                                                                                                                   |                                | REG = 0x1A  W = 0xB5                                                                                                         |

### 17.0 ELECTRICAL CHARACTERISTICS FOR PIC16C72

### **Absolute Maximum Ratings †**

| Ambient temperature under bias                                                             | 55 to +125°C                                            |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Storage temperature                                                                        | 65°C to +150°C                                          |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                         | 0.3V to (VDD + 0.3V)                                    |

| Voltage on VDD with respect to Vss                                                         | 0.3 to +7.5V                                            |

| Voltage on MCLR with respect to Vss (Note 2)                                               | 0 to +14V                                               |

| Voltage on RA4 with respect to Vss                                                         | 0 to +14V                                               |

| Total power dissipation (Note 1)                                                           | 1.0W                                                    |

| Maximum current out of Vss pin                                                             | 300 mA                                                  |

| Maximum current into VDD pin                                                               | 250 mA                                                  |

| Input clamp current, lik (VI < 0 or VI > VDD)                                              | ±20 mA                                                  |

| Output clamp current, loκ (Vo < 0 or Vo > VDD)                                             |                                                         |

| Maximum output current sunk by any I/O pin                                                 | 25 mA                                                   |

| Maximum output current sourced by any I/O pin                                              | 25 mA                                                   |

| Maximum current sunk by PORTA and PORTB (combined)                                         | 200 mA                                                  |

| Maximum current sourced by PORTA and PORTB (combined)                                      | 200 mA                                                  |

| Maximum current sunk by PORTC                                                              | 200 mA                                                  |

| Maximum current sourced by PORTC                                                           | 200 mA                                                  |

| Note 1: Power discipation is calculated as follows: Pdis - Van v (Inn. 7 Iou) + 7 ((Van. V | $O(1) \times IO(1) + \sum_{i=1}^{N} IO(1) \times IO(1)$ |

**Note 1:** Power dissipation is calculated as follows: Pdis = VDD x {IDD -  $\sum$  IOH} +  $\sum$  {(VDD - VOH) x IOH} +  $\sum$ (VOI x IOL)

Note 2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

TABLE 17-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C72-04                                                                                                 | PIC16C72-10                                                                                   | PIC16C72-20                                                                                   | PIC16LC72-04                                                                                              | JW Devices                                                                                                |

|-----|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                    | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 µA typ. at 4V<br>Freq: 4 MHz max.   | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 µA typ. at 4V<br>Freq: 4 MHz max.   | VDD: 2.5V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 5.0 μA max. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                  |

| XT  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                    | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 µA typ. at 4V<br>Freq: 4 MHz max.   | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 µA typ. at 4V<br>Freq: 4 MHz max.   | VDD: 2.5V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 5.0 μA max. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                  |

| HS  | VDD: 4.5V to 5.5V<br>IDD: 13.5 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 4 MHz max.              | VDD: 4.5V to 5.5V<br>IDD: 10 mA max. at 5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 10 MHz max. | VDD: 4.5V to 5.5V<br>IDD: 20 mA max. at 5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 20 MHz max. | Not recommended for use in HS mode                                                                        | VDD: 4.5V to 5.5V<br>IDD: 20 mA max. at 5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 20 MHz max.             |

| LP  | VDD: 4.0V to 6.0V<br>IDD: 52.5 μA typ. at<br>32 kHz, 4.0V<br>IPD: 0.9 μA typ. at 4.0V<br>Freq: 200 kHz max. | Not recommended for use in LP mode                                                            | Not recommended for use in LP mode                                                            | VDD: 2.5V to 6.0V<br>IDD: 48 μA max. at<br>32 kHz, 3.0V<br>IPD: 5.0 μA max. at 3.0V<br>Freq: 200 kHz max. | VDD: 2.5V to 6.0V<br>IDD: 48 μA max. at<br>32 kHz, 3.0V<br>IPD: 5.0 μA max. at 3.0V<br>Freq: 200 kHz max. |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

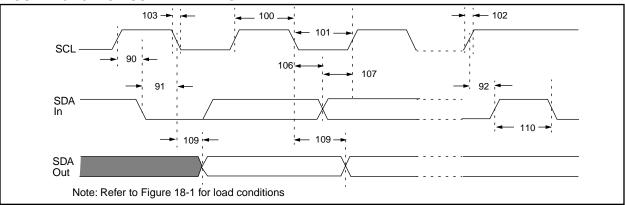

### FIGURE 18-10: I<sup>2</sup>C BUS DATA TIMING

### TABLE 18-10: I<sup>2</sup>C BUS DATA REQUIREMENTS

| 101 T                        | Thigh Thow Tr | Clock high time  Clock low time  SDA and SCL rise time  SDA and SCL fall time | 100 kHz mode  400 kHz mode  SSP Module 100 kHz mode  400 kHz mode  SSP Module 100 kHz mode  100 kHz mode  100 kHz mode  400 kHz mode | 4.0  0.6  1.5TcY 4.7  1.3  1.5TcY — 20 + 0.1Cb  20 + 0.1Cb |                       | μs  μs  μs  μs  ns  ns | Device must operate at a minimum of 1.5 MHz  Device must operate at a minimum of 10 MHz  Device must operate at a minimum of 1.5 MHz  Device must operate at a minimum of 10 MHz  Ce must operate at a minimum of 10 MHz |

|------------------------------|---------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 102<br>103<br>90 Ts<br>91 Tr | TR            | SDA and SCL rise time                                                         | SSP Module 100 kHz mode 400 kHz mode SSP Module 100 kHz mode 400 kHz mode 100 kHz mode                                               | 1.5Tcy 4.7  1.3  1.5Tcy — 20 + 0.1Cb                       | —<br>—<br>1000<br>300 | μs<br>μs<br>ns         | mum of 10 MHz  Device must operate at a minimum of 1.5 MHz  Device must operate at a minimum of 10 MHz  Cb is specified to be from                                                                                       |

| 102<br>103<br>90 Ts<br>91 Tr | TR            | SDA and SCL rise time                                                         | 100 kHz mode 400 kHz mode SSP Module 100 kHz mode 400 kHz mode 100 kHz mode                                                          | 4.7  1.3  1.5Tcy  20 + 0.1Cb                               | —<br>—<br>1000<br>300 | μs<br>ns<br>ns         | mum of 1.5 MHz  Device must operate at a minimum of 10 MHz  Cb is specified to be from                                                                                                                                   |

| 102<br>103<br>90 Ts<br>91 Tr | TR            | SDA and SCL rise time                                                         | 400 kHz mode  SSP Module 100 kHz mode 400 kHz mode 100 kHz mode                                                                      | 1.3<br>1.5Tcy<br>—<br>20 + 0.1Cb                           | 300                   | μs<br>ns<br>ns         | mum of 1.5 MHz  Device must operate at a minimum of 10 MHz  Cb is specified to be from                                                                                                                                   |

| 90 Ts                        |               | time                                                                          | SSP Module<br>100 kHz mode<br>400 kHz mode                                                                                           | 1.5Tcy<br>—<br>20 + 0.1Cb                                  | 300                   | ns<br>ns               | mum of 10 MHz  Cb is specified to be from                                                                                                                                                                                |

| 90 Ts                        |               | time                                                                          | 100 kHz mode<br>400 kHz mode<br>100 kHz mode                                                                                         | 20 + 0.1Cb                                                 | 300                   | ns                     |                                                                                                                                                                                                                          |

| 90 Ts                        |               | time                                                                          | 400 kHz mode<br>100 kHz mode                                                                                                         | _                                                          | 300                   | ns                     |                                                                                                                                                                                                                          |

| 90 Ts                        | TF            |                                                                               | 100 kHz mode                                                                                                                         | _                                                          | 300                   | _                      |                                                                                                                                                                                                                          |

| 90 Ts                        | TF            | SDA and SCL fall time                                                         |                                                                                                                                      | -<br>20 ± 0.1Cb                                            |                       | ns                     |                                                                                                                                                                                                                          |

| 91 T <sub>F</sub>            |               |                                                                               | 400 kHz mode                                                                                                                         | 20 ± 0.1Ch                                                 | 000                   |                        |                                                                                                                                                                                                                          |

| 91 T <sub>F</sub>            |               |                                                                               |                                                                                                                                      | 20 1 0.100                                                 | 300                   | ns                     | Cb is specified to be from 10 to 400 pF                                                                                                                                                                                  |

|                              | ΓSU:STA       | START condition                                                               | 100 kHz mode                                                                                                                         | 4.7                                                        | _                     | μs                     | Only relevant for repeated                                                                                                                                                                                               |

|                              |               | setup time                                                                    | 400 kHz mode                                                                                                                         | 0.6                                                        | _                     | μs                     | START condition                                                                                                                                                                                                          |

| 106 TH                       | THD:STA       | START condition hold                                                          | 100 kHz mode                                                                                                                         | 4.0                                                        | _                     | μs                     | After this period the first clock                                                                                                                                                                                        |

| 106 T⊦                       |               | time                                                                          | 400 kHz mode                                                                                                                         | 0.6                                                        | _                     | μs                     | pulse is generated                                                                                                                                                                                                       |

| 100                          | THD:DAT       | Data input hold time                                                          | 100 kHz mode                                                                                                                         | 0                                                          | _                     | ns                     |                                                                                                                                                                                                                          |

|                              |               |                                                                               | 400 kHz mode                                                                                                                         | 0                                                          | 0.9                   | μs                     |                                                                                                                                                                                                                          |

| 107 Ts                       | ΓSU:DAT       | Data input setup time                                                         | 100 kHz mode                                                                                                                         | 250                                                        | _                     | ns                     | Note 2                                                                                                                                                                                                                   |

|                              |               |                                                                               | 400 kHz mode                                                                                                                         | 100                                                        |                       | ns                     |                                                                                                                                                                                                                          |

| 92 Ts                        | SU:STO        | STOP condition setup                                                          | 100 kHz mode                                                                                                                         | 4.7                                                        |                       | μs                     |                                                                                                                                                                                                                          |

|                              |               | time                                                                          | 400 kHz mode                                                                                                                         | 0.6                                                        |                       | μs                     |                                                                                                                                                                                                                          |

| 109                          | TAA           | Output valid from                                                             | 100 kHz mode                                                                                                                         | _                                                          | 3500                  | ns                     | Note 1                                                                                                                                                                                                                   |

|                              |               | clock                                                                         | 400 kHz mode                                                                                                                         | _                                                          | _                     | ns                     |                                                                                                                                                                                                                          |

| 110                          | TBUF          | Bus free time                                                                 | 100 kHz mode                                                                                                                         | 4.7                                                        | _                     | μs                     | Time the bus must be free                                                                                                                                                                                                |

|                              |               |                                                                               | 400 kHz mode                                                                                                                         | 1.3                                                        | _                     | μs                     | before a new transmission can start                                                                                                                                                                                      |

|                              | Cb            | Bus capacitive loading                                                        |                                                                                                                                      | I —                                                        | 400                   | pF                     |                                                                                                                                                                                                                          |

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

<sup>2:</sup> A fast-mode (400 kHz) I<sup>2</sup>C-bus device can be used in a standard-mode (100 kHz) I<sup>2</sup>C-bus system, but the requirement tsu;DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+tsu;DAT = 1000 + 250 = 1250 ns (according to the standard-mode I<sup>2</sup>C bus specification) before the SCL line is released.

### 19.2 DC Characteristics: PIC16LC73A/74A-04 (Commercial, Industrial)

| DC CHA        | RACTERISTICS                                                     |       |      | ard Ope | •      | •      | itions (unless otherwise stated)  °C ≤ TA ≤ +85°C for industrial and  C ≤ TA ≤ +70°C for commercial |

|---------------|------------------------------------------------------------------|-------|------|---------|--------|--------|-----------------------------------------------------------------------------------------------------|

| Param<br>No.  | Characteristic                                                   | Sym   | Min  | Тур†    | Max    | Units  | Conditions                                                                                          |

| D001          | Supply Voltage                                                   | VDD   | 2.5  | -       | 6.0    | V      | LP, XT, RC osc configuration (DC - 4 MHz)                                                           |

| D002*         | RAM Data Retention<br>Voltage (Note 1)                           | VDR   | -    | 1.5     | -      | V      |                                                                                                     |

| D003          | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR  | -    | Vss     | -      | >      | See section on Power-on Reset for details                                                           |

| D004*         | VDD rise rate to ensure internal Power-on Reset signal           | SVDD  | 0.05 | -       | -      | V/ms   | See section on Power-on Reset for details                                                           |

| D005          | Brown-out Reset Voltage                                          | BVDD  | 3.7  | 4.0     | 4.3    | V      | BODEN bit in configuration word enabled                                                             |

| D010          | Supply Current (Note 2,5)                                        | IDD   | -    | 2.0     | 3.8    | mA     | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                       |

| D010A         |                                                                  |       | -    | 22.5    | 48     | μΑ     | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                     |

| D015*         | Brown-out Reset Current (Note 6)                                 | ΔIBOR | -    | 350     | 425    | μΑ     | BOR enabled VDD = 5.0V                                                                              |

| D020          | Power-down Current                                               | IPD   | -    | 7.5     | 30     | μΑ     | VDD = 3.0V, WDT enabled, -40°C to +85°C                                                             |

| D021<br>D021A | (Note 3,5)                                                       |       | -    | 0.9     | 5<br>5 | μΑ     | VDD = 3.0V, WDT disabled, 0°C to +70°C                                                              |

| 1             | Brown-out Reset Current                                          | Albor | _    | 0.9     | •      | μA<br> | VDD = 3.0V, WDT disabled, -40°C to +85°C                                                            |

| D023*         | (Note 6)                                                         | Δlbor | -    | 350     | 425    | μΑ     | BOR enabled VDD = 5.0V                                                                              |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

- The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

- MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

DC CHARACTERISTICS

### **Applicable Devices** 72 73 73A 74 74A 76 77

19.3 DC Characteristics: PIC16C73A/74A-04 (Commercial, Industrial, Extended)

PIC16C73A/74A-10 (Commercial, Industrial, Extended) PIC16C73A/74A-20 (Commercial, Industrial, Extended)

PIC16LC73A/74A-04 (Commercial, Industrial)

Standard Operating Conditions (unless otherwise stated)

Operating temperature  $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$  for extended,  $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$  for industrial and

$0^{\circ}$ C  $\leq TA \leq +70^{\circ}$ C for commercial

Operating voltage VDD range as described in DC spec Section 19.1 and

Section 19.2.

| Section 19.2. |                             |       |         |     |         |       |                                                   |  |  |

|---------------|-----------------------------|-------|---------|-----|---------|-------|---------------------------------------------------|--|--|

| Param         | Characteristic              | Sym   | Min     | Тур | Max     | Units | Conditions                                        |  |  |

| No.           |                             |       |         | †   |         |       |                                                   |  |  |

|               | Input Low Voltage           |       |         |     |         |       |                                                   |  |  |

|               | I/O ports                   | VIL   |         |     |         |       |                                                   |  |  |

| D030          | with TTL buffer             |       | Vss     | -   | 0.15VDD | V     | For entire VDD range                              |  |  |

| D030A         |                             |       | Vss     | -   | 0.8V    |       | 4.5V ≤ VDD ≤ 5.5V                                 |  |  |

| D031          | with Schmitt Trigger buffer |       | Vss     | -   | 0.2Vdd  | V     |                                                   |  |  |

| D032          | MCLR, OSC1 (in RC mode)     |       | Vss     | -   | 0.2Vdd  | V     |                                                   |  |  |

| D033          | OSC1 (in XT, HS and LP)     |       | Vss     | -   | 0.3VDD  | V     | Note1                                             |  |  |

|               | Input High Voltage          |       |         |     |         |       |                                                   |  |  |

|               | I/O ports                   | ViH   |         | -   |         |       |                                                   |  |  |

| D040          | with TTL buffer             |       | 2.0     | -   | VDD     | V     | 4.5V ≤ VDD ≤ 5.5V                                 |  |  |

| D040A         |                             |       | 0.25VDD | -   | VDD     | V     | For entire VDD range                              |  |  |

|               |                             |       | + 0.8V  |     |         |       |                                                   |  |  |

|               |                             |       |         |     |         |       |                                                   |  |  |

| D041          | with Schmitt Trigger buffer |       | 0.8VDD  | -   | VDD     | V     | For entire VDD range                              |  |  |

| D042          | MCLR                        |       | 0.8VDD  | -   | VDD     | V     |                                                   |  |  |

| D042A         | OSC1 (XT, HS and LP)        |       | 0.7Vdd  | -   | VDD     | V     | Note1                                             |  |  |

| D043          | OSC1 (in RC mode)           |       | 0.9Vdd  | -   | VDD     | V     |                                                   |  |  |

| D070          | PORTB weak pull-up current  | IPURB | 50      | 250 | 400     | μΑ    | VDD = 5V, VPIN = VSS                              |  |  |

|               | Input Leakage Current       |       |         |     |         |       |                                                   |  |  |

|               | (Notes 2, 3)                |       |         |     |         |       |                                                   |  |  |

| D060          | I/O ports                   | lı∟   | -       | -   | ±1      | μΑ    | Vss ≤ VPIN ≤ VDD, Pin at hi-imped-                |  |  |

| D004          | MOLD DAA/TOOKI              |       |         |     |         | _     | ance                                              |  |  |

| D061          | MCLR, RA4/T0CKI             |       | -       | -   | ±5      | μΑ    | Vss \le Vpin \le Vdd                              |  |  |

| D063          | OSC1                        |       | -       | -   | ±5      | μΑ    | Vss ≤ VPIN ≤ VDD, XT, HS and LP osc configuration |  |  |

|               | Output Low Voltage          |       |         |     |         |       | Configuration                                     |  |  |

| D080          | I/O ports                   | Vol   | _       | _   | 0.6     | V     | IOL = 8.5 mA, VDD = 4.5V,                         |  |  |

| D000          | I/O ports                   | VOL   | _       | -   | 0.0     | \ \ \ | -40°C to +85°C                                    |  |  |

| D080A         |                             |       | _       | _   | 0.6     | V     | IOL = 7.0 mA, VDD = 4.5V,                         |  |  |

| DOOOA         |                             |       | _       |     | 0.0     | , v   | -40°C to +125°C                                   |  |  |

| D083          | OSC2/CLKOUT (RC osc config) |       | _       | _   | 0.6     | V     | IOL = 1.6 mA, VDD = 4.5V,                         |  |  |

|               | (100 000 comg)              |       |         |     | 0.0     | •     | -40°C to +85°C                                    |  |  |

| D083A         |                             |       | -       | _   | 0.6     | V     | IOL = 1.2 mA, VDD = 4.5V,                         |  |  |

|               |                             |       |         |     |         |       | -40°C to +125°C                                   |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C7X be driven with external clock in RC mode.

<sup>2:</sup> The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>3:</sup> Negative current is defined as current sourced by the pin.

### **TABLE 19-13: A/D CONVERTER CHARACTERISTICS:**

PIC16C73A/74A-04 (Commercial, Industrial, Extended) PIC16C73A/74A-10 (Commercial, Industrial, Extended) PIC16C73A/74A-20 (Commercial, Industrial, Extended) PIC16LC73A/74A-04 (Commercial, Industrial)

| Param<br>No. | Sym                                      | Characteristic                                 |                         | Min       | Тур†       | Max        | Units                                                                                              | Conditions                               |

|--------------|------------------------------------------|------------------------------------------------|-------------------------|-----------|------------|------------|----------------------------------------------------------------------------------------------------|------------------------------------------|