Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I²C, SPI, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 192 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | A/D 5x8b                                                                    |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc74a-04i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address                   | Name                                                                                                | Bit 7                | Bit 6              | Bit 5          | Bit 4           | Bit 3          | Bit 2           | Bit 1       | Bit 0   | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(2) |

|---------------------------|-----------------------------------------------------------------------------------------------------|----------------------|--------------------|----------------|-----------------|----------------|-----------------|-------------|---------|--------------------------|-------------------------------------|

| Bank 0                    |                                                                                                     |                      |                    |                |                 |                |                 |             |         |                          |                                     |

| 00h <sup>(4)</sup>        | INDF Addressing this location uses contents of FSR to address data memory (not a physical register) |                      |                    |                |                 |                |                 |             |         |                          | 0000 0000                           |

| 01h                       | TMR0                                                                                                | Timer0 mod           | lule's registe     | r              |                 |                |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 02h <sup>(4)</sup>        | PCL                                                                                                 | Program Co           | ounter's (PC)      | Least Signif   | icant Byte      |                |                 |             |         | 0000 0000                | 0000 0000                           |

| 03h <b>(4)</b>            | STATUS                                                                                              | IRP <sup>(7)</sup>   | RP1 <sup>(7)</sup> | RP0            | TO              | PD             | Z               | DC          | С       | 0001 1xxx                | 000q quuu                           |

| 04h <b>(4)</b>            | FSR                                                                                                 | Indirect data        | a memory ad        | dress pointe   | er              |                |                 |             | •       | XXXX XXXX                | uuuu uuuu                           |

| 05h                       | PORTA                                                                                               | _                    | _                  | PORTA Dat      | a Latch when    | written: POR   | TA pins wher    | read        |         | 0x 0000                  | 0u 0000                             |

| 06h                       | PORTB                                                                                               | PORTB Dat            | a Latch whe        | n written: PC  | ORTB pins whe   | n read         |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 07h                       | PORTC                                                                                               | PORTC Dat            | ta Latch whe       | n written: PC  | DRTC pins whe   | en read        |                 |             |         | XXXX XXXX                | uuuu uuuu                           |

| 08h <sup>(5)</sup>        | PORTD                                                                                               | PORTD Dat            | a Latch whe        | n written: PC  | ORTD pins whe   | en read        |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 09h <b>(5)</b>            | PORTE                                                                                               | _                    | _                  | _              | _               | _              | RE2             | RE1         | RE0     | xxx                      | uuu                                 |

| 0Ah <b>(1,4)</b>          | PCLATH                                                                                              | _                    | _                  | _              | Write Buffer fo | or the upper t | 5 bits of the I | Program Cou | unter   | 0 0000                   | 0 0000                              |

| 0Bh <b><sup>(4)</sup></b> | INTCON                                                                                              | GIE                  | PEIE               | TOIE           | INTE            | RBIE           | T0IF            | INTF        | RBIF    | 0000 000x                | 0000 000u                           |

| 0Ch                       | PIR1                                                                                                | PSPIF <sup>(3)</sup> | ADIF               | RCIF           | TXIF            | SSPIF          | CCP1IF          | TMR2IF      | TMR1IF  | 0000 0000                | 0000 0000                           |

| 0Dh                       | PIR2                                                                                                | —                    | —                  | -              | -               | -              | —               | —           | CCP2IF  | 0                        | 0                                   |

| 0Eh                       | TMR1L                                                                                               | Holding reg          | ister for the L    | east Signific  | ant Byte of the | e 16-bit TMR1  | l register      |             |         | xxxx xxxx                | uuuu uuuu                           |

| 0Fh                       | TMR1H                                                                                               | Holding reg          | ister for the N    | lost Significa | ant Byte of the | 16-bit TMR1    | register        |             |         | XXXX XXXX                | uuuu uuuu                           |

| 10h                       | T1CON                                                                                               | —                    | —                  | T1CKPS1        | T1CKPS0         | T1OSCEN        | <b>T1SYNC</b>   | TMR1CS      | TMR10N  | 00 0000                  | uu uuuu                             |

| 11h                       | TMR2                                                                                                | Timer2 mod           | lule's registe     | r              |                 |                |                 |             |         | 0000 0000                | 0000 0000                           |

| 12h                       | T2CON                                                                                               | —                    | TOUTPS3            | TOUTPS2        | TOUTPS1         | TOUTPS0        | TMR2ON          | T2CKPS1     | T2CKPS0 | -000 0000                | -000 0000                           |

| 13h                       | SSPBUF                                                                                              | Synchronou           | is Serial Port     | Receive Bu     | ffer/Transmit R | egister        |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 14h                       | SSPCON                                                                                              | WCOL                 | SSPOV              | SSPEN          | СКР             | SSPM3          | SSPM2           | SSPM1       | SSPM0   | 0000 0000                | 0000 0000                           |

| 15h                       | CCPR1L                                                                                              | Capture/Co           | mpare/PWM          | Register1 (L   | _SB)            |                |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 16h                       | CCPR1H                                                                                              | Capture/Co           | mpare/PWM          | Register1 (N   | MSB)            |                |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 17h                       | CCP1CON                                                                                             | —                    | —                  | CCP1X          | CCP1Y           | CCP1M3         | CCP1M2          | CCP1M1      | CCP1M0  | 00 0000                  | 00 0000                             |

| 18h                       | RCSTA                                                                                               | SPEN                 | RX9                | SREN           | CREN            | —              | FERR            | OERR        | RX9D    | 0000 -00x                | 0000 -00x                           |

| 19h                       | TXREG                                                                                               | USART Trar           | nsmit Data R       | egister        |                 |                |                 |             |         | 0000 0000                | 0000 0000                           |

| 1Ah                       | RCREG                                                                                               | USART Red            | ceive Data R       | egister        |                 |                |                 |             |         | 0000 0000                | 0000 0000                           |

| 1Bh                       | CCPR2L                                                                                              | Capture/Co           | mpare/PWM          | Register2 (L   | _SB)            |                |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 1Ch                       | CCPR2H                                                                                              | Capture/Co           | mpare/PWM          | Register2 (N   | MSB)            |                |                 |             |         | xxxx xxxx                | uuuu uuuu                           |

| 1Dh                       | CCP2CON                                                                                             | —                    | —                  | CCP2X          | CCP2Y           | CCP2M3         | CCP2M2          | CCP2M1      | CCP2M0  | 00 0000                  | 00 0000                             |

| 1Eh                       | ADRES                                                                                               | A/D Result           | Register           |                |                 |                |                 |             |         | XXXX XXXX                | uuuu uuuu                           |

| 1Fh                       | ADCON0                                                                                              | ADCS1                | ADCS0              | CHS2           | CHS1            | CHS0           | GO/DONE         | —           | ADON    | 0000 00-0                | 0000 00-0                           |

TABLE 4-2:

PIC16C73/73A/74/74A SPECIAL FUNCTION REGISTER SUMMARY

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A, always maintain these bits clear.

4: These registers can be addressed from either bank.

5: PORTD and PORTE are not physically implemented on the PIC16C73/73A, read as '0'.

6: Brown-out Reset is not implemented on the PIC16C73 or the PIC16C74, read as '0'.

7: The IRP and RP1 bits are reserved on the PIC16C73/73A/74/74A, always maintain these bits clear.

| IABLE                | <b>4-Z</b> . |                      | 3// 3A// 4                                                                                     | 114A SP                 | ECIAL FU        | INC HOIN     | REGISI        | ER SUN         |        | (Cont.a)                 |                                     |  |

|----------------------|--------------|----------------------|------------------------------------------------------------------------------------------------|-------------------------|-----------------|--------------|---------------|----------------|--------|--------------------------|-------------------------------------|--|

| Address              | Name         | Bit 7                | Bit 6                                                                                          | Bit 5                   | Bit 4           | Bit 3        | Bit 2         | Bit 1          | Bit 0  | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(2) |  |

| Bank 1               |              | •                    |                                                                                                | L                       |                 |              |               |                |        | -                        |                                     |  |

| 80h <sup>(4)</sup>   | INDF         | Addressing           | Addressing this location uses contents of FSR to address data memory (not a physical register) |                         |                 |              |               |                |        |                          |                                     |  |

| 81h                  | OPTION       | RBPU                 | INTEDG                                                                                         | TOCS                    | TOSE            | PSA          | PS2           | PS1            | PS0    | 1111 1111                | 1111 1111                           |  |

| 82h <sup>(4)</sup>   | PCL          | Program Co           | ounter's (PC)                                                                                  | Least Signif            | ficant Byte     | •            | •             |                |        | 0000 0000                | 0000 0000                           |  |

| 83h <sup>(4)</sup>   | STATUS       | IRP(7)               | RP1 <sup>(7)</sup>                                                                             | RP0                     | TO              | PD           | Z             | DC             | С      | 0001 1xxx                | 000q quuu                           |  |

| 84h <sup>(4)</sup>   | FSR          | Indirect data        | a memory ad                                                                                    | ldress pointe           | er              |              |               |                |        | XXXX XXXX                | uuuu uuuu                           |  |

| 85h                  | TRISA        | —                    | —                                                                                              | PORTA Dat               | ta Direction Re | gister       |               |                |        | 11 1111                  | 11 1111                             |  |

| 86h                  | TRISB        | PORTB Dat            | a Direction F                                                                                  | Register                |                 |              |               |                |        | 1111 1111                | 1111 1111                           |  |

| 87h                  | TRISC        | PORTC Dat            | ta Direction F                                                                                 | Register                |                 |              |               |                |        | 1111 1111                | 1111 1111                           |  |

| 88h <b>(5)</b>       | TRISD        | PORTD Dat            | ta Direction F                                                                                 | Register                |                 |              |               |                |        | 1111 1111                | 1111 1111                           |  |

| 89h <b>(5)</b>       | TRISE        | IBF                  | OBF                                                                                            | IBOV                    | PSPMODE         | —            | PORTE Da      | ta Direction E | Bits   | 0000 -111                | 0000 -111                           |  |

| 8Ah <sup>(1,4)</sup> | PCLATH       | —                    | —                                                                                              | —                       | Write Buffer fo | or the upper | 5 bits of the | Program Cou    | unter  | 0 0000                   | 0 0000                              |  |

| 8Bh <sup>(4)</sup>   | INTCON       | GIE                  | PEIE                                                                                           | TOIE                    | INTE            | RBIE         | TOIF          | INTF           | RBIF   | 0000 000x                | 0000 000u                           |  |

| 8Ch                  | PIE1         | PSPIE <sup>(3)</sup> | ADIE                                                                                           | RCIE                    | TXIE            | SSPIE        | CCP1IE        | TMR2IE         | TMR1IE | 0000 0000                | 0000 0000                           |  |

| 8Dh                  | PIE2         | —                    | —                                                                                              | —                       | —               | —            | —             | —              | CCP2IE | 0                        | 0                                   |  |

| 8Eh                  | PCON         | —                    | —                                                                                              | —                       | _               | —            | _             | POR            | BOR(6) | dd                       | uu                                  |  |

| 8Fh                  | —            | Unimpleme            | nted                                                                                           |                         |                 |              |               |                |        | -                        | —                                   |  |

| 90h                  | —            | Unimpleme            | nted                                                                                           |                         |                 |              |               |                |        | -                        | —                                   |  |

| 91h                  | _            | Unimpleme            | nted                                                                                           |                         |                 |              |               |                |        | —                        | —                                   |  |

| 92h                  | PR2          | Timer2 Peri          | od Register                                                                                    |                         |                 |              |               |                |        | 1111 1111                | 1111 1111                           |  |

| 93h                  | SSPADD       | Synchronou           | is Serial Port                                                                                 | (I <sup>2</sup> C mode) | Address Regis   | ter          |               |                |        | 0000 0000                | 0000 0000                           |  |

| 94h                  | SSPSTAT      | —                    | —                                                                                              | D/Ā                     | Р               | S            | R/W           | UA             | BF     | 00 0000                  | 00 0000                             |  |

| 95h                  | —            | Unimpleme            | nted                                                                                           | •                       |                 |              |               |                |        | -                        | _                                   |  |

| 96h                  | —            | Unimpleme            | nted                                                                                           |                         |                 |              |               |                |        | -                        | —                                   |  |

| 97h                  | —            | Unimpleme            | nted                                                                                           |                         |                 |              |               |                |        | -                        | -                                   |  |

| 98h                  | TXSTA        | CSRC                 | TX9                                                                                            | TXEN                    | SYNC            | _            | BRGH          | TRMT           | TX9D   | 0000 -010                | 0000 -010                           |  |

| 99h                  | SPBRG        | Baud Rate            | Generator Re                                                                                   | egister                 |                 |              |               |                |        | 0000 0000                | 0000 0000                           |  |

| 9Ah                  | _            | Unimpleme            | nted                                                                                           |                         |                 |              |               |                |        | -                        | _                                   |  |

| 9Bh                  | —            | Unimpleme            | nted                                                                                           |                         |                 |              |               |                |        | -                        | -                                   |  |

| 9Ch                  | _            | Unimpleme            | nted                                                                                           |                         |                 |              |               |                |        |                          | _                                   |  |

| 9Dh                  | —            | Unimpleme            | nted                                                                                           |                         |                 |              |               |                |        | _                        | _                                   |  |

| 9Eh                  | —            | Unimpleme            | nted                                                                                           |                         |                 |              |               |                |        | -                        | _                                   |  |

| 9Fh                  | ADCON1       | _                    | _                                                                                              | _                       | _               | _            | PCFG2         | PCFG1          | PCFG0  | 000                      | 000                                 |  |

#### TABLE 4-2: PIC16C73/73A/74/74A SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A, always maintain these bits clear.

- 4: These registers can be addressed from either bank.

- 5: PORTD and PORTE are not physically implemented on the PIC16C73/73A, read as '0'.

- 6: Brown-out Reset is not implemented on the PIC16C73 or the PIC16C74, read as '0'.

7: The IRP and RP1 bits are reserved on the PIC16C73/73A/74/74A, always maintain these bits clear.

## FIGURE 4-11: PIE1 REGISTER PIC16C73/73A/74/74A/76/77 (ADDRESS 8Ch)

| PSPIE <sup>(1)</sup> | ADIE      | RCIE                                  | TXIE       | SSPIE       | CCP1IE      | TMR2IE       | TMR1IE    | R      | = Readable bit                                                                                           |  |  |

|----------------------|-----------|---------------------------------------|------------|-------------|-------------|--------------|-----------|--------|----------------------------------------------------------------------------------------------------------|--|--|

| bit7                 | 1         |                                       |            |             |             |              | bit0      | U      | <ul> <li>Writable bit</li> <li>Unimplemented bit,<br/>read as '0'</li> <li>Value at POR reset</li> </ul> |  |  |

| bit 7:               | 1 = Enabl | Parallel S<br>es the PS<br>les the PS | P read/wr  | te interrup |             | Enable bit   |           |        |                                                                                                          |  |  |

| bit 6:               | ·         |                                       |            |             |             |              |           |        |                                                                                                          |  |  |

| bit 5:               | 1 = Enabl | ART Rece<br>es the US<br>les the US   | ART recei  | ve interrup | ot          |              |           |        |                                                                                                          |  |  |

| bit 4:               | 1 = Enabl | ART Trans<br>es the US<br>les the US  | ART trans  | mit interru | ıpt         |              |           |        |                                                                                                          |  |  |

| bit 3:               | 1 = Enabl | ynchronou<br>es the SS<br>les the SS  | P interrup | t           | pt Enable b | bit          |           |        |                                                                                                          |  |  |

| bit 2:               | 1 = Enabl | CCP1 Inte<br>les the CC<br>les the CC | P1 interru | pt          |             |              |           |        |                                                                                                          |  |  |

| bit 1:               | 1 = Enabl | TMR2 to F<br>es the TM<br>les the TM  | R2 to PR2  | 2 match in  | •           |              |           |        |                                                                                                          |  |  |

| bit 0:               | 1 = Enabl | TMR1 Ove<br>es the TM<br>les the TM   | R1 overflo | w interrup  | ot          |              |           |        |                                                                                                          |  |  |

| Note 1:              | PIC16C73  |                                       |            |             |             | Slave Port i | mplemente | ed, tl | his bit location is reserved                                                                             |  |  |

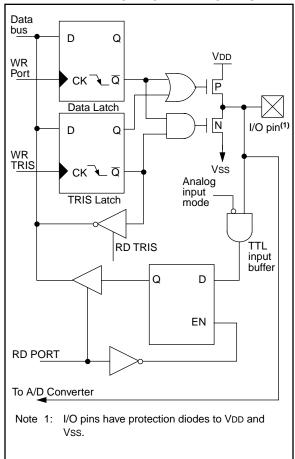

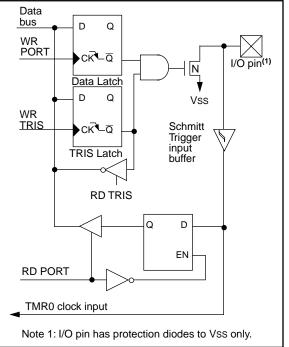

## 5.0 I/O PORTS Applicable Devices 72 73 73A 74 74A 76 77

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

## 5.1 PORTA and TRISA Registers Applicable Devices 72 73 73A 74 74A 76 77

#### PORTA is a 6-bit latch.

The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as output or input.

Setting a TRISA register bit puts the corresponding output driver in a hi-impedance mode. Clearing a bit in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

Note: On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

## EXAMPLE 5-1: INITIALIZING PORTA

| BCF   | STATUS, | RP0 | ; |                       |

|-------|---------|-----|---|-----------------------|

| BCF   | STATUS, | RP1 | ; | PIC16C76/77 only      |

| CLRF  | PORTA   |     | ; | Initialize PORTA by   |

|       |         |     | ; | clearing output       |

|       |         |     | ; | data latches          |

| BSF   | STATUS, | RP0 | ; | Select Bank 1         |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISA   |     | ; | Set RA<3:0> as inputs |

|       |         |     | ; | RA<5:4> as outputs    |

|       |         |     | ; | TRISA<7:6> are always |

|       |         |     | ; | read as '0'.          |

|       |         |     |   |                       |

#### FIGURE 5-1: BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

#### FIGURE 5-2: BLOCK DIAGRAM OF RA4/ T0CKI PIN

#### 10.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in capture mode, the prescaler counter is cleared. This means that any reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 10-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 10-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ; the new prescaler     |

|       |             | ; mode value and CCP ON |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ; value                 |

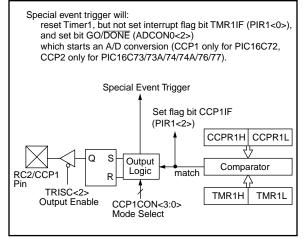

## 10.2 <u>Compare Mode</u>

Applicable Devices

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven High

- Driven Low

- · Remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### FIGURE 10-3: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 10.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force       |

|-------|------------------------------------------------|

|       | the RC2/CCP1 compare output latch to the       |

|       | default low level. This is not the data latch. |

#### 10.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 10.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 10.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special trigger output of CCP2 resets the TMR1 register pair, and starts an A/D conversion (if the A/D module is enabled).

For the PIC16C72 only, the special event trigger output of CCP1 resets the TMR1 register pair, and starts an A/D conversion (if the A/D module is enabled).

Note: The special event trigger from the CCP1and CCP2 modules will not set interrupt flag bit TMR1IF (PIR1<0>).

#### 13.4 A/D Conversions

Applicable Devices

72

73

73

74

74

76

77

Example 13-2 shows how to perform an A/D conversion. The RA pins are configured as analog inputs. The analog reference (VREF) is the device VDD. The A/D interrupt is enabled, and the A/D conversion clock is FRC. The conversion is performed on the RA0 pin (channel 0).

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRES register will NOT be updated with the partially completed A/D conversion sample. That is, the ADRES register will continue to contain the value of the last completed conversion (or the last value written to the ADRES register). After the A/D conversion is aborted, a 2TAD wait is required before the next acquisition is started. After this 2TAD wait, an acquisition is automatically started on the selected channel.

## EXAMPLE 13-2: A/D CONVERSION

;

; ;

| BSF        | STATUS,  | RP0           | ;   | Select Bank 1                                       |

|------------|----------|---------------|-----|-----------------------------------------------------|

| BCF        | STATUS,  | RP1           | ;   | PIC16C76/77 only                                    |

| CLRF       | ADCON1   |               | ;   | Configure A/D inputs                                |

| BSF        | PIE1,    | ADIE          | ;   | Enable A/D interrupts                               |

| BCF        | STATUS,  | RP0           | ;   | Select Bank 0                                       |

| MOVLW      | 0xC1     |               | ;   | RC Clock, A/D is on, Channel 0 is selected          |

| MOVWF      | ADCON0   |               | ;   |                                                     |

| BCF        | PIR1,    | ADIF          | ;   | Clear A/D interrupt flag bit                        |

| BSF        | INTCON,  | PEIE          | ;   | Enable peripheral interrupts                        |

| BSF        | INTCON,  | GIE           | ;   | Enable all interrupts                               |

| Enquiro th | at the m | oquirod gamp  | 14. | ng time for the selected input channel has elapsed. |

|            |          | on may be sta |     |                                                     |

| BSF | ADCON0, | GO | ; | ; Start A/D Conversion                              |  |

|-----|---------|----|---|-----------------------------------------------------|--|

| :   |         |    | ; | ; The ADIF bit will be set and the GO/DONE bit      |  |

| :   |         |    | ; | ; is cleared upon completion of the A/D Conversion. |  |

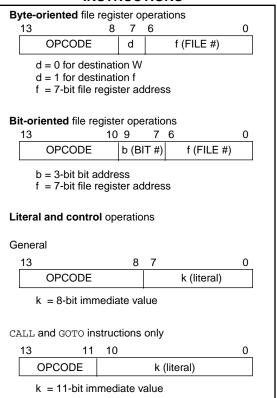

## 15.0 INSTRUCTION SET SUMMARY

Each PIC16CXX instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXX instruction set summary in Table 15-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 15-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

## TABLE 15-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| x             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                   |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| PCLATH        | Program Counter High Latch                                                                                                                                                     |

| GIE           | Global Interrupt Enable bit                                                                                                                                                    |

| WDT           | Watchdog Timer/Counter                                                                                                                                                         |

| TO            | Time-out bit                                                                                                                                                                   |

| PD            | Power-down bit                                                                                                                                                                 |

| dest          | Destination either the W register or the specified register file location                                                                                                      |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| <>            | Register bit field                                                                                                                                                             |

| ∈             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 15-2 lists the instructions recognized by the MPASM assembler.

Figure 15-1 shows the general formats that the instructions can have.

**Note:** To maintain upward compatibility with future PIC16CXX products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

# FIGURE 15-1: GENERAL FORMAT FOR INSTRUCTIONS

## 15.1 Instruction Descriptions

| ADDLW             | Add Lite                                   | ral and \           | ~               |               |  |  |  |  |  |

|-------------------|--------------------------------------------|---------------------|-----------------|---------------|--|--|--|--|--|

| Syntax:           | [label] Al                                 |                     | k               |               |  |  |  |  |  |

| Operands:         |                                            | $0 \le k \le 255$   |                 |               |  |  |  |  |  |

| ·                 |                                            |                     |                 |               |  |  |  |  |  |

| Operation:        | (W) + k –                                  | → (vv)              |                 |               |  |  |  |  |  |

| Status Affected:  | C, DC, Z                                   |                     | 1               |               |  |  |  |  |  |

| Encoding:         | 11                                         | 111x                | kkkk            | kkkk          |  |  |  |  |  |

| Description:      | The conter<br>added to the<br>result is pl | he eight b          | oit literal 'k' | and the       |  |  |  |  |  |

| Words:            | 1                                          |                     |                 |               |  |  |  |  |  |

| Cycles:           | 1                                          |                     |                 |               |  |  |  |  |  |

| Q Cycle Activity: | Q1                                         | Q2                  | Q3              | Q4            |  |  |  |  |  |

|                   | Decode                                     | Read<br>literal 'k' | Process<br>data | Write to<br>W |  |  |  |  |  |

| Example:          | ADDLW                                      | 0x15                |                 |               |  |  |  |  |  |

|                   | Before In                                  | Before Instruction  |                 |               |  |  |  |  |  |

|                   |                                            | - W                 | 0x10            |               |  |  |  |  |  |

|                   | After Inst                                 |                     | 0.05            |               |  |  |  |  |  |

|                   |                                            | W =                 | 0x25            |               |  |  |  |  |  |

|                   |                                            |                     |                 |               |  |  |  |  |  |

| ADDWF             | Add W a                                    | nd f                |                 |               |  |  |  |  |  |

| Syntax:           | [ <i>label</i> ] A                         | DDWF                | f,d             |               |  |  |  |  |  |

| Operands:         | $0 \le f \le 12$                           | 27                  |                 |               |  |  |  |  |  |

| ANDLW             | AND Lite                                                                                                            | eral with                | w               |               |  |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------|---------------|--|--|--|--|--|

| Syntax:           | [ <i>label</i> ] A                                                                                                  | [ <i>label</i> ] ANDLW k |                 |               |  |  |  |  |  |

| Operands:         | $0 \le k \le 2$                                                                                                     | $0 \le k \le 255$        |                 |               |  |  |  |  |  |

| Operation:        | (W) .AND                                                                                                            | D. (k) $\rightarrow$ (   | W)              |               |  |  |  |  |  |

| Status Affected:  | Z                                                                                                                   |                          |                 |               |  |  |  |  |  |

| Encoding:         | 11                                                                                                                  | 1001                     | kkkk            | kkkk          |  |  |  |  |  |

| Description:      | The contents of W register are<br>AND'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |                          |                 |               |  |  |  |  |  |

| Words:            | 1                                                                                                                   |                          |                 |               |  |  |  |  |  |

| Cycles:           | 1                                                                                                                   |                          |                 |               |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                  | Q2                       | Q3              | Q4            |  |  |  |  |  |

|                   | Decode                                                                                                              | Read<br>literal "k"      | Process<br>data | Write to<br>W |  |  |  |  |  |

| Example           | ANDLW                                                                                                               | 0x5F                     |                 |               |  |  |  |  |  |

|                   | Before In                                                                                                           | struction                | 1               |               |  |  |  |  |  |

|                   |                                                                                                                     | W =                      | 0xA3            |               |  |  |  |  |  |

|                   | After Inst                                                                                                          | W =                      | 0x03            |               |  |  |  |  |  |

|                   |                                                                                                                     |                          |                 |               |  |  |  |  |  |

| ANDWF             | AND W v                                                                                                             | vith f                   |                 |               |  |  |  |  |  |

| Syntax:           | [ <i>label</i> ] A                                                                                                  | NDWF                     | f,d             |               |  |  |  |  |  |

| Operands:         | $0 \le f \le 127$                                                                                                   |                          |                 |               |  |  |  |  |  |

| ADDWF             | Add W a                                                                                                                                                                   | nd f                    |                 |                      |  |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|----------------------|--|--|--|--|--|

| Syntax:           | [ <i>label</i> ] A                                                                                                                                                        | DDWF                    | f,d             |                      |  |  |  |  |  |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$                                                                                                                                            | 7                       |                 |                      |  |  |  |  |  |

| Operation:        | (W) + (f)                                                                                                                                                                 | ightarrow (desti        | nation)         |                      |  |  |  |  |  |

| Status Affected:  | C, DC, Z                                                                                                                                                                  |                         |                 |                      |  |  |  |  |  |

| Encoding:         | 00                                                                                                                                                                        | 0111                    | dfff            | ffff                 |  |  |  |  |  |

| Description:      | Add the contents of the W register with<br>register 'f'. If 'd' is 0 the result is stored<br>in the W register. If 'd' is 1 the result is<br>stored back in register 'f'. |                         |                 |                      |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                         |                         |                 |                      |  |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                         |                         |                 |                      |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                        | Q2                      | Q3              | Q4                   |  |  |  |  |  |

|                   | Decode                                                                                                                                                                    | Read<br>register<br>'f' | Process<br>data | Write to destination |  |  |  |  |  |

| Example           | ADDWF                                                                                                                                                                     | FSR,                    | 0               |                      |  |  |  |  |  |

|                   | Before In                                                                                                                                                                 |                         |                 |                      |  |  |  |  |  |

|                   |                                                                                                                                                                           | W =<br>FSR =            | 0x17<br>0xC2    |                      |  |  |  |  |  |

|                   | After Inst                                                                                                                                                                | ruction                 |                 |                      |  |  |  |  |  |

|                   |                                                                                                                                                                           | W =<br>FSR =            | 0xD9<br>0xC2    |                      |  |  |  |  |  |

| ANDWF             | AND W v                                                                                                                                                     | vith f                  |                 |                      |  |  |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|----------------------|--|--|--|--|--|--|

| Syntax:           | [ <i>label</i> ] A                                                                                                                                          | NDWF                    | f,d             |                      |  |  |  |  |  |  |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$                                                                                                                              | 27                      |                 |                      |  |  |  |  |  |  |

| Operation:        | (W) .AND                                                                                                                                                    | D. (f) $\rightarrow$ (d | destinatio      | n)                   |  |  |  |  |  |  |

| Status Affected:  | Z                                                                                                                                                           |                         |                 |                      |  |  |  |  |  |  |

| Encoding:         | 00                                                                                                                                                          | 0101                    | dfff            | ffff                 |  |  |  |  |  |  |

| Description:      | AND the W register with register 'f'. If 'd'<br>is 0 the result is stored in the W regis-<br>ter. If 'd' is 1 the result is stored back in<br>register 'f'. |                         |                 |                      |  |  |  |  |  |  |

| Words:            | 1                                                                                                                                                           |                         |                 |                      |  |  |  |  |  |  |

| Cycles:           | 1                                                                                                                                                           |                         |                 |                      |  |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                          | Q2                      | Q3              | Q4                   |  |  |  |  |  |  |

|                   | Decode                                                                                                                                                      | Read<br>register<br>'f' | Process<br>data | Write to destination |  |  |  |  |  |  |

| Example           | ANDWF                                                                                                                                                       | FSR,                    | 1               |                      |  |  |  |  |  |  |

|                   | Before In                                                                                                                                                   |                         |                 |                      |  |  |  |  |  |  |

|                   |                                                                                                                                                             | W =<br>FSR =            | 0x17<br>0xC2    |                      |  |  |  |  |  |  |

|                   | After Inst                                                                                                                                                  |                         |                 |                      |  |  |  |  |  |  |

|                   |                                                                                                                                                             | 0x17                    |                 |                      |  |  |  |  |  |  |

|                   |                                                                                                                                                             | FSR =                   | 0x02            |                      |  |  |  |  |  |  |

## 16.0 DEVELOPMENT SUPPORT

## 16.1 <u>Development Tools</u>

The PIC16/17 microcontrollers are supported with a full range of hardware and software development tools:

- PICMASTER/PICMASTER CE Real-Time In-Circuit Emulator

- ICEPIC Low-Cost PIC16C5X and PIC16CXXX In-Circuit Emulator

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- PICDEM-1 Low-Cost Demonstration Board

- PICDEM-2 Low-Cost Demonstration Board

- PICDEM-3 Low-Cost Demonstration Board

- MPASM Assembler

- MPLAB-SIM Software Simulator

- MPLAB-C (C Compiler)

- Fuzzy logic development system (*fuzzy*TECH<sup>®</sup>–MP)

## 16.2 <u>PICMASTER: High Performance</u> <u>Universal In-Circuit Emulator with</u> <u>MPLAB IDE</u>

The PICMASTER Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for all microcontrollers in the PIC12C5XX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX families. PICMASTER is supplied with the MPLAB<sup>TM</sup> Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable target probes allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the PICMASTER allows expansion to support all new Microchip microcontrollers.

The PICMASTER Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC compatible 386 (and higher) machine platform and Microsoft Windows<sup>®</sup> 3.x environment were chosen to best make these features available to you, the end user.

A CE compliant version of PICMASTER is available for European Union (EU) countries.

## 16.3 ICEPIC: Low-cost PIC16CXXX In-Circuit Emulator

ICEPIC is a low-cost in-circuit emulator solution for the Microchip PIC16C5X and PIC16CXXX families of 8-bit OTP microcontrollers.

ICEPIC is designed to operate on PC-compatible machines ranging from 286-AT<sup>®</sup> through Pentium<sup>™</sup> based machines under Windows 3.x environment. ICEPIC features real time, non-intrusive emulation.

## 16.4 PRO MATE II: Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for displaying error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In standalone mode the PRO MATE II can read, verify or program PIC16C5X, PIC16CXXX, PIC17CXX and PIC14000 devices. It can also set configuration and code-protect bits in this mode.

## 16.5 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. PICSTART Plus is not recommended for production programming.

PICSTART Plus supports all PIC12C5XX, PIC14000, PIC16C5X, PIC16CXXX and PIC17CXX devices with up to 40 pins. Larger pin count devices such as the PIC16C923 and PIC16C924 may be supported with an adapter socket.

## Applicable Devices 72 73 73A 74 74A 76 77

#### 18.1 DC Characteristics: PIC16C73/74-04 (Commercial, Industrial) PIC16C73/74-10 (Commercial, Industrial) PIC16C73/74-20 (Commercial, Industrial)

| DC CH                 | ARACTERISTICS                                                    |      | <b>Standa</b><br>Operat | -                  |                | ure -4         | itions (unless otherwise stated) $10^{\circ}C$ $\leq TA \leq +85^{\circ}C$ for industrial and $C$ $\leq TA \leq +70^{\circ}C$ for commercial                                                  |

|-----------------------|------------------------------------------------------------------|------|-------------------------|--------------------|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.          | Characteristic                                                   | Sym  | Min                     | Тур†               | Max            | Units          | Conditions                                                                                                                                                                                    |

| D001<br>D001A         | Supply Voltage                                                   | Vdd  | 4.0<br>4.5              |                    | 6.0<br>5.5     | V<br>V         | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                       |

| D002*                 | RAM Data Retention<br>Voltage (Note 1)                           | Vdr  | -                       | 1.5                | -              | V              |                                                                                                                                                                                               |

| D003                  | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR | -                       | Vss                | -              | V              | See section on Power-on Reset for details                                                                                                                                                     |

| D004*                 | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | SVDD | 0.05                    | -                  | -              | V/ms           | See section on Power-on Reset for details                                                                                                                                                     |

| D010                  | Supply Current (Note 2,5)                                        | IDD  | -                       | 2.7                | 5              | mA             | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                                                                                                 |

| D013                  |                                                                  |      | -                       | 13.5               | 30             | mA             | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                                             |

| D020<br>D021<br>D021A | Power-down Current<br>(Note 3,5)                                 | IPD  | -<br>-<br>-             | 10.5<br>1.5<br>1.5 | 42<br>21<br>24 | μΑ<br>μΑ<br>μΑ | $VDD = 4.0V$ , WDT enabled, $-40^{\circ}C$ to $+85^{\circ}C$<br>$VDD = 4.0V$ , WDT disabled, $-0^{\circ}C$ to $+70^{\circ}C$<br>$VDD = 4.0V$ , WDT disabled, $-40^{\circ}C$ to $+85^{\circ}C$ |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VbD and Vss.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

## Applicable Devices 72 73 73A 74 74A 76 77

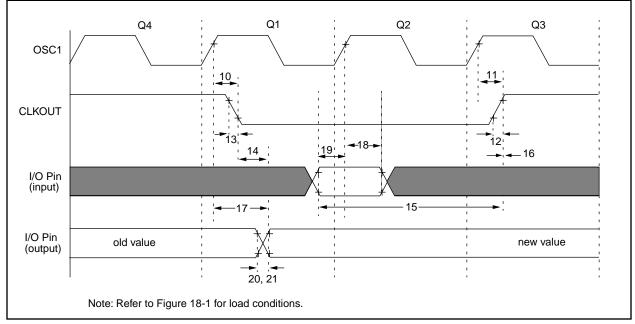

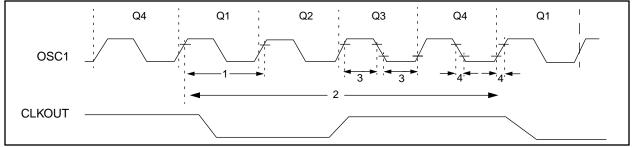

## FIGURE 18-3: CLKOUT AND I/O TIMING

| TABLE 18-3: CLKOUT AND I/O TIMING REQUIREMENTS |

|------------------------------------------------|

|------------------------------------------------|

| Parameter<br>No. | Sym      | Characteristic                                    |                          | Min | Тур†        | Мах | Units  | Conditions |

|------------------|----------|---------------------------------------------------|--------------------------|-----|-------------|-----|--------|------------|

| 10*              | TosH2ckL | OSC1 <sup>↑</sup> to CLKOUT↓                      |                          | _   | 75          | 200 | ns     | Note 1     |

| 11*              | TosH2ckH | OSC1 <sup>↑</sup> to CLKOUT <sup>↑</sup>          |                          | —   | 75          | 200 | ns     | Note 1     |

| 12*              | TckR     | CLKOUT rise time                                  |                          | _   | 35          | 100 | ns     | Note 1     |

| 13*              | TckF     | CLKOUT fall time                                  |                          | _   | 35          | 100 | ns     | Note 1     |

| 14*              | TckL2ioV | CLKOUT ↓ to Port out vali                         | _                        | _   | 0.5Tcy + 20 | ns  | Note 1 |            |

| 15*              | TioV2ckH | Port in valid before CLKOU                        | 0.25Tcy + 25             | _   | _           | ns  | Note 1 |            |

| 16*              | TckH2iol | Port in hold after CLKOUT                         | 0                        | _   | -           | ns  | Note 1 |            |

| 17*              | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to<br>Port out valid |                          | -   | 50          | 150 | ns     |            |

| 18*              | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to                   | PIC16 <b>C</b> 73/74     | 100 | -           |     | ns     |            |

|                  |          | Port input invalid (I/O in hold time)             | PIC16 <b>LC</b> 73/74    | 200 | _           | _   | ns     |            |

| 19*              | TioV2osH | Port input valid to OSC11                         | (I/O in setup time)      | 0   |             |     | ns     |            |

| 20*              | TioR     | Port output rise time                             | PIC16 <b>C</b> 73/74     | —   | 10          | 25  | ns     |            |

|                  |          |                                                   | PIC16 <b>LC</b> 73/74    | —   | _           | 60  | ns     |            |

| 21*              | TioF     | Port output fall time                             | PIC16 <b>C</b> 73/74     | _   | 10          | 25  | ns     |            |

|                  |          |                                                   | PIC16 <b>LC</b> 73/74    | —   | _           | 60  | ns     |            |

| 22††*            | Tinp     | INT pin high or low time                          | INT pin high or low time |     | _           | _   | ns     |            |

| 23††*            | Trbp     | RB7:RB4 change INT high                           | n or low time            | Тсү | —           | _   | ns     |            |

\* These parameters are characterized but not tested.

†Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

these parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

Applicable Devices

72

73

73A

74

74A

76

77

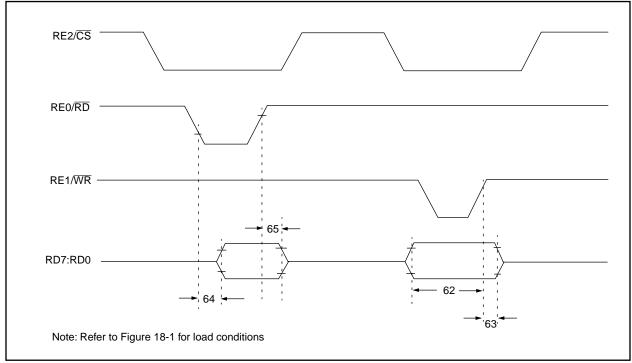

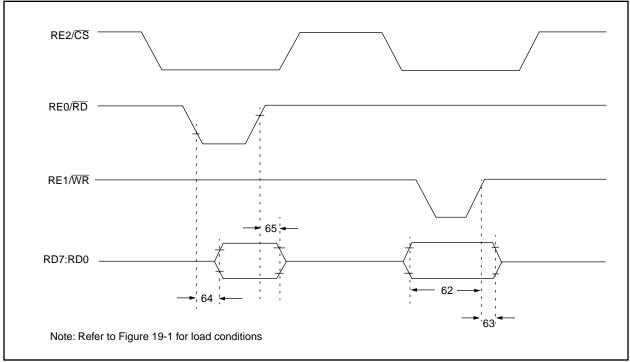

## FIGURE 18-7: PARALLEL SLAVE PORT TIMING (PIC16C74)

## TABLE 18-7: PARALLEL SLAVE PORT REQUIREMENTS (PIC16C74)

| Parameter<br>No. | Sym      | Characteristic                                                                         | Min                                                                       | Тур† | Max | Units | Conditions |  |

|------------------|----------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------|-----|-------|------------|--|

| 62               | TdtV2wrH | Data in valid before $\overline{WR}\uparrow$ or $\overline{CS}\uparrow$ (setup time    | 20                                                                        | —    | -   | ns    |            |  |

| 63*              | TwrH2dtl | $\uparrow$ or $\overline{CS}\uparrow$ to data–in invalid (hold time) PIC16 <b>C</b> 74 |                                                                           | 20   | —   | —     | ns         |  |

|                  |          |                                                                                        | PIC16 <b>LC</b> 74                                                        | 35   | —   | —     | ns         |  |