Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc74at-04-l |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 GENERAL DESCRIPTION

The PIC16C7X is a family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with integrated analog-to-digital (A/D) converters, in the PIC16CXX mid-range family.

All PIC16/17 microcontrollers employ an advanced RISC architecture. The PIC16CXX microcontroller family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches which require two cycles. A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The **PIC16C72** has 128 bytes of RAM and 22 I/O pins. In addition several peripheral features are available including: three timer/counters, one Capture/Compare/ PWM module and one serial port. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. Also a 5-channel high-speed 8-bit A/D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The PIC16C73/73A devices have 192 bytes of RAM, while the PIC16C76 has 368 byes of RAM. Each device has 22 I/O pins. In addition, several peripheral features are available including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. The Universal Syn-Asynchronous Receiver chronous Transmitter (USART) is also known as the Serial Communications Interface or SCI. Also a 5-channel high-speed 8-bit A/ D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The **PIC16C74/74A** devices have 192 bytes of RAM, while the **PIC16C77** has 368 bytes of RAM. Each device has 33 I/O pins. In addition several peripheral features are available including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. The Universal Synchronous Asynchronous Receiver Transmitter (USART) is also known as the Serial Communications Interface or SCI. An 8-bit Parallel Slave Port is provided. Also an 8-channel high-speed

8-bit A/D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The PIC16C7X family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) feature provides a power saving mode. The user can wake up the chip from SLEEP through several external and internal interrupts and resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lockup.

A UV erasable CERDIP packaged version is ideal for code development while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume.

The PIC16C7X family fits perfectly in applications ranging from security and remote sensors to appliance control and automotive. The EPROM technology makes customization of application programs (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16C7X very versatile even in areas where no microcontroller use has been considered before (e.g. timer functions, serial communication, capture and compare, PWM functions and coprocessor applications).

#### 1.1 Family and Upward Compatibility

Users familiar with the PIC16C5X microcontroller family will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for the PIC16C5X can be easily ported to the PIC16CXX family of devices (Appendix B).

#### 1.2 Development Support

PIC16C7X devices are supported by the complete line of Microchip Development tools.

Please refer to Section 16.0 for more details about Microchip's development tools.

NOTES:

## TABLE 3-3: PIC16C74/74A/77 PINOUT DESCRIPTION (Cont.'d)

| Pin Name          | DIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                            |

|-------------------|-------------|--------------|-------------|---------------|-----------------------|--------------------------------------------------------------------------------------------------------|

|                   |             |              |             |               |                       | PORTC is a bi-directional I/O port.                                                                    |

| RC0/T1OSO/T1CKI   | 15          | 16           | 32          | I/O           | ST                    | RC0 can also be the Timer1 oscillator output or a<br>Timer1 clock input.                               |

| RC1/T1OSI/CCP2    | 16          | 18           | 35          | I/O           | ST                    | RC1 can also be the Timer1 oscillator input or<br>Capture2 input/Compare2 output/PWM2 output.          |

| RC2/CCP1          | 17          | 19           | 36          | I/O           | ST                    | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                    |

| RC3/SCK/SCL       | 18          | 20           | 37          | I/O           | ST                    | RC3 can also be the synchronous serial clock input/<br>output for both SPI and I <sup>2</sup> C modes. |

| RC4/SDI/SDA       | 23          | 25           | 42          | I/O           | ST                    | RC4 can also be the SPI Data In (SPI mode) or data I/O ( $I^2$ C mode).                                |

| RC5/SDO           | 24          | 26           | 43          | I/O           | ST                    | RC5 can also be the SPI Data Out (SPI mode).                                                           |

| RC6/TX/CK         | 25          | 27           | 44          | I/O           | ST                    | RC6 can also be the USART Asynchronous Transmit or<br>Synchronous Clock.                               |

| RC7/RX/DT         | 26          | 29           | 1           | I/O           | ST                    | RC7 can also be the USART Asynchronous Receive or<br>Synchronous Data.                                 |

|                   |             |              |             |               |                       | PORTD is a bi-directional I/O port or parallel slave port when interfacing to a microprocessor bus.    |

| RD0/PSP0          | 19          | 21           | 38          | I/O           | ST/TTL <sup>(3)</sup> | when interfacing to a microprocessor bus.                                                              |

| RD1/PSP1          | 20          | 21           | 39          | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD2/PSP2          | 20          | 22           | 40          | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD3/PSP3          | 22          | 23           | 41          | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD4/PSP4          | 27          | 30           | 2           | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD5/PSP5          | 28          | 31           | 3           | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD6/PSP6          | 29          | 32           | 4           | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD7/PSP7          | 30          | 33           | 5           | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

|                   |             |              |             | 1/0           | OI/ITE                | PORTE is a bi-directional I/O port.                                                                    |

| RE0/RD/AN5        | 8           | 9            | 25          | I/O           | ST/TTL <sup>(3)</sup> | RE0 can also be read control for the parallel slave port,<br>or analog input5.                         |

| RE1/WR/AN6        | 9           | 10           | 26          | I/O           | ST/TTL <sup>(3)</sup> | RE1 can also be write control for the parallel slave port, or analog input6.                           |

| RE2/CS/AN7        | 10          | 11           | 27          | I/O           | ST/TTL <sup>(3)</sup> | RE2 can also be select control for the parallel slave port, or analog input7.                          |

| Vss               | 12,31       | 13,34        | 6,29        | Р             |                       | Ground reference for logic and I/O pins.                                                               |

| Vdd               | 11,32       | 12,35        | 7,28        | Р             | _                     | Positive supply for logic and I/O pins.                                                                |

| NC                | —           | 1,17,28,     | 12,13,      |               |                       | These pins are not internally connected. These pins should                                             |

|                   |             | 40           | 33,34       |               |                       | be left unconnected.                                                                                   |

| Legend: I = input | 0 = oi      | •            |             |               | put/output            | P = power                                                                                              |

|                   |             | lot used     |             |               | TL input              | ST = Schmitt Trigger input<br>external interrupt.                                                      |

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

This buffer is a Schmitt Trigger input when used in serial programming mode.

This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel

Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. The special function registers can be classified into two sets (core and peripheral). Those registers associated with the "core" functions are described in this section, and those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address              | Name    | Bit 7              | Bit 6              | Bit 5         | Bit 4          | Bit 3          | Bit 2            | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(3) |

|----------------------|---------|--------------------|--------------------|---------------|----------------|----------------|------------------|---------------|-----------|--------------------------|-------------------------------------|

| Bank 0               |         |                    |                    |               |                |                |                  |               |           |                          |                                     |

| 00h <sup>(1)</sup>   | INDF    | Addressing         | this location      | uses conten   | ts of FSR to   | address data   | a memory (n      | ot a physical | register) | 0000 0000                | 0000 0000                           |

| 01h                  | TMR0    | Timer0 mod         | dule's registe     | r             |                |                |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 02h <sup>(1)</sup>   | PCL     | Program Co         | ounter's (PC)      | Least Signif  | icant Byte     |                |                  |               |           | 0000 0000                | 0000 0000                           |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup> | RP0           | TO             | PD             | Z                | DC            | С         | 0001 1xxx                | 000q quuu                           |

| 04h <sup>(1)</sup>   | FSR     | Indirect dat       | a memory ac        | ldress pointe | r              |                |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 05h                  | PORTA   | _                  | _                  | PORTA Dat     | a Latch whe    | n written: PO  | RTA pins wh      | en read       |           | 0x 0000                  | 0u 0000                             |

| 06h                  | PORTB   | PORTB Da           | ta Latch whe       | n written: PC | RTB pins wl    | nen read       |                  |               |           | XXXX XXXX                | uuuu uuuu                           |

| 07h                  | PORTC   | PORTC Da           | ta Latch whe       | n written: PC | ORTC pins w    | hen read       |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 08h                  | —       | Unimpleme          | nted               |               |                |                |                  |               |           | —                        | —                                   |

| 09h                  | —       | Unimpleme          | nted               |               |                |                |                  |               |           | _                        | _                                   |

| 0Ah <sup>(1,2)</sup> | PCLATH  | —                  | —                  | —             | Write Buffe    | r for the uppe | er 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                              |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                | PEIE               | TOIE          | INTE           | RBIE           | TOIF             | INTF          | RBIF      | 0000 000x                | 0000 000u                           |

| 0Ch                  | PIR1    | —                  | ADIF               | —             | —              | SSPIF          | CCP1IF           | TMR2IF        | TMR1IF    | -0 0000                  | -0 0000                             |

| 0Dh                  | —       | Unimpleme          | nted               |               |                |                |                  | •             |           | —                        | _                                   |

| 0Eh                  | TMR1L   | Holding reg        | ister for the L    | east Signific | ant Byte of t  | he 16-bit TM   | R1 register      |               |           | xxxx xxxx                | uuuu uuuu                           |

| 0Fh                  | TMR1H   | Holding reg        | ister for the N    | Most Signific | ant Byte of th | ne 16-bit TMF  | R1 register      |               |           | xxxx xxxx                | uuuu uuuu                           |

| 10h                  | T1CON   | —                  | -                  | T1CKPS1       | T1CKPS0        | T1OSCEN        | T1SYNC           | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                             |

| 11h                  | TMR2    | Timer2 mod         | dule's registe     | r             |                |                |                  |               |           | 0000 0000                | 0000 0000                           |

| 12h                  | T2CON   | —                  | TOUTPS3            | TOUTPS2       | TOUTPS1        | TOUTPS0        | TMR2ON           | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                           |

| 13h                  | SSPBUF  | Synchronou         | us Serial Port     | Receive Bu    | ffer/Transmit  | Register       |                  |               |           | XXXX XXXX                | uuuu uuuu                           |

| 14h                  | SSPCON  | WCOL               | SSPOV              | SSPEN         | CKP            | SSPM3          | SSPM2            | SSPM1         | SSPM0     | 0000 0000                | 0000 0000                           |

| 15h                  | CCPR1L  | Capture/Co         | mpare/PWM          | Register (LS  | SB)            |                |                  | -             |           | xxxx xxxx                | uuuu uuuu                           |

| 16h                  | CCPR1H  | Capture/Co         | mpare/PWM          | Register (M   | SB)            |                |                  |               |           | XXXX XXXX                | uuuu uuuu                           |

| 17h                  | CCP1CON | —                  | —                  | CCP1X         | CCP1Y          | CCP1M3         | CCP1M2           | CCP1M1        | CCP1M0    | 00 0000                  | 00 0000                             |

| 18h                  | —       | Unimpleme          | nted               |               |                |                |                  |               |           | _                        | _                                   |

| 19h                  | —       | Unimpleme          | nted               |               |                |                |                  |               |           | —                        | —                                   |

| 1Ah                  | —       | Unimpleme          | nted               |               |                |                |                  |               |           | —                        | _                                   |

| 1Bh                  | _       | Unimpleme          | nted               |               |                |                |                  |               |           | _                        | _                                   |

| 1Ch                  | —       | Unimpleme          | nted               |               |                |                |                  |               |           | _                        | —                                   |

| 1Dh                  | _       | Unimpleme          | nted               |               |                |                |                  |               |           | —                        | —                                   |

| 1Eh                  | ADRES   | A/D Result         | Register           |               |                |                |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 1Fh                  | ADCON0  | ADCS1              | ADCS0              | CHS2          | CHS1           | CHS0           | GO/DONE          | _             | ADON      | 0000 00-0                | 0000 00-0                           |

TABLE 4-1: PIC16C72 SPECIAL FUNCTION REGISTER SUMMARY

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

4: The IRP and RP1 bits are reserved on the PIC16C72, always maintain these bits clear.

#### 4.2.2.1 STATUS REGISTER Applicable Devices 72|73|73A|74|74A|76|77

The STATUS register, shown in Figure 4-7, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- **Note 1:** For those devices that do not use bits IRP and RP1 (STATUS<7:6>), maintain these bits clear to ensure upward compatibility with future products.

- Note 2: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| R/W-0    | R/W-0                                            | R/W-0                                                                                     | R-1                                  | R-1                                       | R/W-x                                          | R/W-x                                      | R/W-x                       |                                                                                       |

|----------|--------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------|------------------------------------------------|--------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------|

| IRP      | RP1                                              | RP0                                                                                       | TO                                   | PD                                        | Z                                              | DC                                         | С                           | R = Readable bit                                                                      |

| bit7     |                                                  |                                                                                           |                                      |                                           |                                                |                                            | bit0                        | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 7:   | 1 = Bank 2                                       | ster Bank \$<br>2, 3 (100h<br>0, 1 (00h -                                                 | - 1FFh)                              | used for ir                               | ndirect addr                                   | essing)                                    |                             |                                                                                       |

| bit 6-5: | 11 = Bank<br>10 = Bank<br>01 = Bank<br>00 = Bank | : Register E<br>< 3 (180h -<br>< 2 (100h -<br>< 1 (80h - F<br>< 0 (00h - 7<br>k is 128 by | 1FFh)<br>17Fh)<br>Fh)<br>′Fh)        | ct bits (use                              | ed for direct                                  | addressin                                  | g)                          |                                                                                       |

| oit 4:   | •                                                |                                                                                           |                                      | struction,                                | or sleep ir                                    | struction                                  |                             |                                                                                       |

| bit 3:   | •                                                | r-down bit<br>power-up o<br>ecution of t                                                  | •                                    |                                           |                                                |                                            |                             |                                                                                       |

| bit 2:   |                                                  | sult of an a                                                                              |                                      |                                           | peration is z                                  |                                            |                             |                                                                                       |

| bit 1:   | 1 = A carr                                       | y-out from                                                                                | the 4th lo                           | w order bi                                | N, SUBLW, S<br>t of the resu<br>bit of the res | It occurred                                |                             | r borrow the polarity is reversed                                                     |

| bit 0:   | 1 = A carr<br>0 = No car<br>Note: For            | y-out from<br>rry-out fror<br>borrow the<br>berand. For                                   | the most<br>n the mos<br>polarity is | significant<br>t significar<br>s reversed |                                                | esult occuri<br>result occu<br>ion is exec | red<br>irred<br>uted by add | ding the two's complement of the either the high or low order bit o                   |

## FIGURE 4-7: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

٦

## FIGURE 11-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)

| R/W-0    | R/W-0                                                                | R/W-0                                                                   | R/W-0                                                                            | R/W-0                                                                        | R/W-0                                    | R/W-0                    | R/W-0                        |                                                                                                                           |

|----------|----------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------|--------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| WCOL     | SSPOV                                                                | SSPEN                                                                   | CKP                                                                              | SSPM3                                                                        | SSPM2                                    | SSPM1                    | SSPM0                        | R = Readable bit                                                                                                          |

| bit7     |                                                                      |                                                                         |                                                                                  |                                                                              |                                          |                          | bit0                         | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset                                      |

| bit 7:   | WCOL: W                                                              | rite Collisio                                                           | n Detect l                                                                       | oit                                                                          |                                          |                          |                              |                                                                                                                           |

|          | 1 = The S                                                            | SPBUF reg                                                               | jister is wr                                                                     |                                                                              | it is still tr                           | ansmitting               | the previou                  | us word                                                                                                                   |

| bit 6:   | SSPOV: R                                                             | eceive Ove                                                              | erflow Det                                                                       | ect bit                                                                      |                                          |                          |                              |                                                                                                                           |

|          | the data ir<br>BUF, even                                             | byte is rece<br>SSPSR re<br>if only train<br>new rece                   | egister is I                                                                     | ost. Overfl<br>data, to av                                                   | ow can on<br>oid setting                 | ly occur in<br>overflow. | slave mod<br>In master       | revious data. In case of overflow<br>e. The user must read the SSP<br>mode the overflow bit is not se<br>SSPBUF register. |

|          | In I <sup>2</sup> C mod                                              | <u>de</u>                                                               |                                                                                  |                                                                              |                                          |                          |                              |                                                                                                                           |

|          | 1 = A byte<br>in transmit<br>0 = No ove                              | mode. SS                                                                |                                                                                  |                                                                              |                                          |                          |                              | us byte. SSPOV is a "don't care                                                                                           |

| bit 5:   | SSPEN: S                                                             | ynchronou                                                               | s Serial P                                                                       | ort Enable                                                                   | bit                                      |                          |                              |                                                                                                                           |

|          | $\frac{\text{In SPI model}}{1 = \text{Enable}}$ $0 = \text{Disable}$ | es serial po                                                            |                                                                                  |                                                                              |                                          |                          | s serial por<br>pins         | t pins                                                                                                                    |

|          | 0 = Disabl                                                           | es the seria                                                            | ort and co                                                                       | nfigures th                                                                  | nese pins a                              | as I/O port              | pins                         | ial port pins<br>s input or output.                                                                                       |

| bit 4:   | CKP: Cloc                                                            | k Polarity                                                              | Select bit                                                                       |                                                                              |                                          |                          |                              |                                                                                                                           |

|          |                                                                      | ate for cloc                                                            |                                                                                  |                                                                              |                                          |                          |                              | receive on rising edge.<br>ceive on falling edge.                                                                         |

|          | $\frac{\ln l^2 C \mod SCK \text{ relea}}{1 = \text{Enable}}$         | se control<br>e clock                                                   | -11                                                                              |                                                                              | 4                                        |                          | . (: )                       |                                                                                                                           |

|          | 0 = Holds                                                            |                                                                         |                                                                                  | , ,                                                                          |                                          |                          | o time)                      |                                                                                                                           |

| bit 3-0: | 0001 = SF<br>0010 = SF<br>0011 = SF<br>0100 = SF<br>0101 = SF        | PI master n<br>PI master n<br>PI master n<br>PI master n<br>PI slave mo | node, cloc<br>node, cloc<br>node, cloc<br>node, cloc<br>ode, clock<br>ode, clock | k = Fosc/4<br>k = Fosc/1<br>k = Fosc/6<br>k = TMR2<br>= SCK pir<br>= SCK pir | l<br>6<br>64<br>output/2<br>1. SS pin co | ontrol enal              |                              | n be used as I/O pin.                                                                                                     |

|          | $0111 =  ^{2}(0)$<br>$1011 =  ^{2}(0)$<br>$1110 =  ^{2}(0)$          | C slave mo<br>C firmware<br>C slave mo                                  | de, 10-bit<br>controlled<br>de, 7-bit a                                          | address<br>I Master M<br>ddress wi                                           | th start an                              | d stop bit i             | nterrupts er<br>interrupts o |                                                                                                                           |

Г

### 11.4 <u>I<sup>2</sup>C<sup>™</sup> Overview</u>

This section provides an overview of the Inter-Integrated Circuit ( $I^2C$ ) bus, with Section 11.5 discussing the operation of the SSP module in  $I^2C$  mode.

The  $l^2C$  bus is a two-wire serial interface developed by the Philips Corporation. The original specification, or standard mode, was for data transfers of up to 100 Kbps. The enhanced specification (fast mode) is also supported. This device will communicate with both standard and fast mode devices if attached to the same bus. The clock will determine the data rate.

The  $l^2C$  interface employs a comprehensive protocol to ensure reliable transmission and reception of data. When transmitting data, one device is the "master" which initiates transfer on the bus and generates the clock signals to permit that transfer, while the other device(s) acts as the "slave." All portions of the slave protocol are implemented in the SSP module's hardware, except general call support, while portions of the master protocol need to be addressed in the PIC16CXX software. Table 11-3 defines some of the  $l^2C$  bus terminology. For additional information on the  $l^2C$  interface specification, refer to the Philips document "*The*  $l^2C$  bus and how to use it."#939839340011, which can be obtained from the Philips Corporation.

In the I<sup>2</sup>C interface protocol each device has an address. When a master wishes to initiate a data transfer, it first transmits the address of the device that it wishes to "talk" to. All devices "listen" to see if this is their address. Within this address, a bit specifies if the master wishes to read-from/write-to the slave device. The master and slave are always in opposite modes (transmitter/receiver) of operation during a data transfer. That is they can be thought of as operating in either of these two relations:

- Master-transmitter and Slave-receiver

- · Slave-transmitter and Master-receiver

In both cases the master generates the clock signal.

The output stages of the clock (SCL) and data (SDA) lines must have an open-drain or open-collector in order to perform the wired-AND function of the bus. External pull-up resistors are used to ensure a high level when no device is pulling the line down. The number of devices that may be attached to the I<sup>2</sup>C bus is limited only by the maximum bus loading specification of 400 pF.

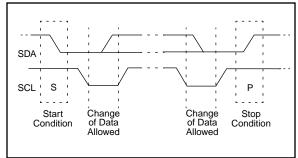

## 11.4.1 INITIATING AND TERMINATING DATA TRANSFER

During times of no data transfer (idle time), both the clock line (SCL) and the data line (SDA) are pulled high through the external pull-up resistors. The START and STOP conditions determine the start and stop of data transmission. The START condition is defined as a high to low transition of the SDA when the SCL is high. The STOP condition is defined as a low to high transition of the SDA when the SCL is high. The START and STOP conditions for starting and terminating data transfer. Due to the definition of the START and STOP conditions, when data is being transmitted, the SDA line can only change state when the SCL line is low.

#### FIGURE 11-14: START AND STOP CONDITIONS

| Term            | Description                                                                                                                                 |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Transmitter     | The device that sends the data to the bus.                                                                                                  |

| Receiver        | The device that receives the data from the bus.                                                                                             |

| Master          | The device which initiates the transfer, generates the clock and terminates the transfer.                                                   |

| Slave           | The device addressed by a master.                                                                                                           |

| Multi-master    | More than one master device in a system. These masters can attempt to control the bus at the same time without corrupting the message.      |

| Arbitration     | Procedure that ensures that only one of the master devices will control the bus. This ensure that the transfer data does not get corrupted. |

| Synchronization | Procedure where the clock signals of two or more devices are synchronized.                                                                  |

## TABLE 11-3: I<sup>2</sup>C BUS TERMINOLOGY

## FIGURE 12-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS 18h)

| R/W-0  | R/W-0                                                   | R/W-0                       | R/W-0          | U-0         | R-0         | R-0          | R-x                        |                                                                                      |

|--------|---------------------------------------------------------|-----------------------------|----------------|-------------|-------------|--------------|----------------------------|--------------------------------------------------------------------------------------|

| SPEN   | RX9                                                     | SREN                        | CREN           | _           | FERR        | OERR         | RX9D                       | R = Readable bit                                                                     |

| bit7   |                                                         |                             |                |             |             |              | bit0                       | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset |

|        | <b>SPEN</b> : Ser<br>1 = Serial p<br>0 = Serial p       | oort enable                 | d (Configur    | es RC7/R    | X/DT and    | RC6/TX/Cł    | <pre>&lt; pins as se</pre> | erial port pins)                                                                     |

|        | <b>RX9</b> : 9-bit I<br>1 = Selects<br>0 = Selects      | 9-bit rece                  | otion          |             |             |              |                            |                                                                                      |

| bit 5: | SREN: Sing                                              | gle Receive                 | e Enable bi    | t           |             |              |                            |                                                                                      |

|        | <u>Asynchron</u><br>Don't care                          | ous mode                    |                |             |             |              |                            |                                                                                      |

|        | Synchrono<br>1 = Enable<br>0 = Disable<br>This bit is c | s single rec<br>s single re | ceive<br>ceive | is comple   | ete.        |              |                            |                                                                                      |

|        | Synchrono<br>Unused in t                                |                             | <u>slave</u>   |             |             |              |                            |                                                                                      |

| bit 4: | CREN: Cor                                               | ntinuous Re                 | eceive Enal    | ble bit     |             |              |                            |                                                                                      |

|        | Asynchrone<br>1 = Enable<br>0 = Disable                 | s continuou                 |                |             |             |              |                            |                                                                                      |

|        | <u>Synchrono</u><br>1 = Enable<br>0 = Disable           | s continuou                 |                | until enabl | e bit CREN  | l is cleared | (CREN ove                  | errides SREN)                                                                        |

| bit 3: | Unimplem                                                | ented: Rea                  | ad as '0'      |             |             |              |                            |                                                                                      |

|        | FERR: Fran<br>1 = Framing<br>0 = No fran                | g error (Ca                 |                | ed by reac  | ling RCRE   | G register a | and receive                | next valid byte)                                                                     |

|        | <b>OERR</b> : Ove<br>1 = Overru<br>0 = No ove           | n error (Ca                 |                | d by clear  | ing bit CRI | EN)          |                            |                                                                                      |

| bit 0: | <b>RX9D</b> : 9th                                       | hit of receiv               | ) etch hav     | an ho nar   | ity hit)    |              |                            |                                                                                      |

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH. (Section 12.1).

- 2. Enable the asynchronous serial port by clearing bit SYNC, and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit RCIE.

- 4. If 9-bit reception is desired, then set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 7. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

### TABLE 12-7: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Address | Name  | Bit 7                | Bit 6    | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|----------------------|----------|------------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF     | RCIF       | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h     | RCSTA | SPEN                 | RX9      | SREN       | CREN  |       | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 1Ah     | RCREG | USART Rec            | eive Reg | gister     |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE     | RCIE       | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h     | TXSTA | CSRC                 | TX9      | TXEN       | SYNC  |       | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h     | SPBRG | Baud Rate (          | Generato | or Registe | r     |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

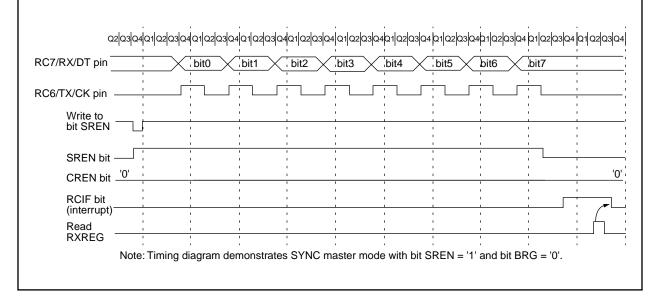

### FIGURE 12-14: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

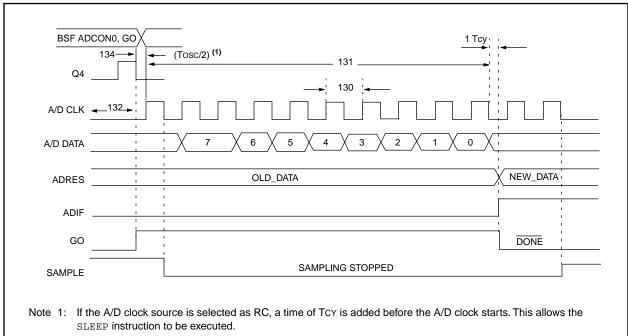

#### 13.4.1 FASTER CONVERSION - LOWER RESOLUTION TRADE-OFF

Not all applications require a result with 8-bits of resolution, but may instead require a faster conversion time. The A/D module allows users to make the trade-off of conversion speed to resolution. Regardless of the resolution required, the acquisition time is the same. To speed up the conversion, the clock source of the A/D module may be switched so that the TAD time violates the minimum specified time (see the applicable electrical specification). Once the TAD time violates the minimum specified time, all the following A/D result bits are not valid (see A/D Conversion Timing in the Electrical Specifications section.) The clock sources may only be switched between the three oscillator versions (cannot be switched from/to RC). The equation to determine the time before the oscillator can be switched is as follows:

Conversion time =  $2TAD + N \cdot TAD + (8 - N)(2TOSC)$ Where: N = number of bits of resolution required. Since the TAD is based from the device oscillator, the user must use some method (a timer, software loop, etc.) to determine when the A/D oscillator may be changed. Example 13-3 shows a comparison of time required for a conversion with 4-bits of resolution, versus the 8-bit resolution conversion. The example is for devices operating at 20 MHz and 16 MHz (The A/D clock is programmed for 32Tosc), and assumes that immediately after 6TAD, the A/D clock is programmed for 2Tosc.

The 2TOSC violates the minimum TAD time since the last 4-bits will not be converted to correct values.

| EXAMPLE 13-3: | 4-BIT vs. 8-BIT CON | /ERSION TIMES |

|---------------|---------------------|---------------|

|               |                     |               |

|                                 | - (1)                      | Reso    | lution  |

|---------------------------------|----------------------------|---------|---------|

|                                 | Freq. (MHz) <sup>(1)</sup> | 4-bit   | 8-bit   |

| TAD                             | 20                         | 1.6 μs  | 1.6 μs  |

|                                 | 16                         | 2.0 μs  | 2.0 μs  |

| Tosc                            | 20                         | 50 ns   | 50 ns   |

|                                 | 16                         | 62.5 ns | 62.5 ns |

| 2TAD + N • TAD + (8 - N)(2TOSC) | 20                         | 10 μs   | 16 μs   |

|                                 | 16                         | 12.5 μs | 20 µs   |

Note 1: PIC16C7X devices have a minimum TAD time of 1.6 µs.

| Address               | Name   | Bit 7                | Bit 6      | Bit 5   | Bit 4          | Bit 3    | Bit 2     | Bit 1       | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|-----------------------|--------|----------------------|------------|---------|----------------|----------|-----------|-------------|--------|--------------------------|---------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE       | TOIE    | INTE           | RBIE     | TOIF      | INTF        | RBIF   | 0000 000x                | 0000 000u                 |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF       | RCIF    | TXIF           | SSPIF    | CCP1IF    | TMR2IF      | TMR1IF | 0000 0000                | 0000 0000                 |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE       | RCIE    | TXIE           | SSPIE    | CCP1IE    | TMR2IE      | TMR1IE | 0000 0000                | 0000 0000                 |

| 0Dh                   | PIR2   | —                    | —          | _       | —              | _        | —         | —           | CCP2IF | 0                        | 0                         |

| 8Dh                   | PIE2   | _                    | _          | _       | —              | _        | —         | —           | CCP2IE | 0                        | 0                         |

| 1Eh                   | ADRES  | A/D Resu             | It Registe | er      |                |          |           |             |        | xxxx xxxx                | uuuu uuuu                 |

| 1Fh                   | ADCON0 | ADCS1                | ADCS0      | CHS2    | CHS1           | CHS0     | GO/DONE   | —           | ADON   | 0000 00-0                | 0000 00-0                 |

| 9Fh                   | ADCON1 | —                    | _          | _       | —              | _        | PCFG2     | PCFG1       | PCFG0  | 000                      | 000                       |

| 05h                   | PORTA  | _                    | _          | RA5     | RA4            | RA3      | RA2       | RA1         | RA0    | 0x 0000                  | 0u 0000                   |

| 85h                   | TRISA  | _                    | _          | PORTA I | Data Directior | Register | •         |             |        | 11 1111                  | 11 1111                   |

| 09h                   | PORTE  | —                    |            | —       | —              | —        | RE2       | RE1         | RE0    | xxx                      | uuu                       |

| 89h                   | TRISE  | IBF                  | OBF        | IBOV    | PSPMODE        | _        | PORTE Dat | a Directior | n Bits | 0000 -111                | 0000 -111                 |

| TABLE 13-3: SUMMARY OF A/D REGISTERS, PIC16C73/73A/74/74A/76 |

|--------------------------------------------------------------|

|--------------------------------------------------------------|

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC6C73/73A/76, always maintain these bits clear.

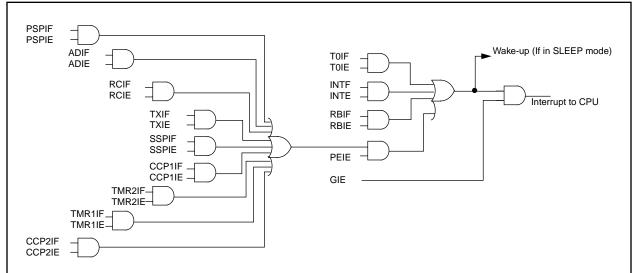

#### FIGURE 14-16: INTERRUPT LOGIC

The following table shows which devices have which interrupts.

| Device    | TOIF | INTF | RBIF | PSPIF | ADIF | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF | CCP2IF |

|-----------|------|------|------|-------|------|------|------|-------|--------|--------|--------|--------|

| PIC16C72  | Yes  | Yes  | Yes  | -     | Yes  | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C73  | Yes  | Yes  | Yes  | -     | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C73A | Yes  | Yes  | Yes  | -     | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C74  | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C74A | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C76  | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C77  | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

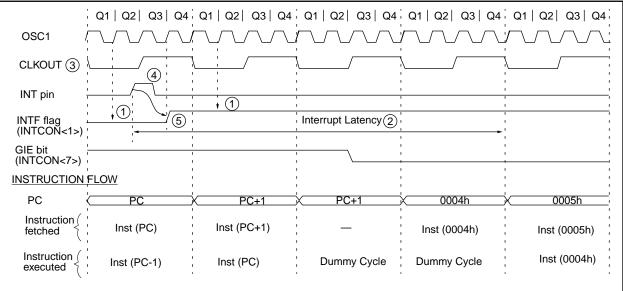

#### FIGURE 14-17: INT PIN INTERRUPT TIMING

Note 1: INTF flag is sampled here (every Q1).

- 2: Interrupt latency = 3-4 Tcy where Tcy = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

3: CLKOUT is available only in RC oscillator mode.

4: For minimum width of INT pulse, refer to AC specs.

5: INTF is enabled to be set anytime during the Q4-Q1 cycles.

# PIC16C7X

| IORWF             | Inclusive                                                                                                                                                            | e OR W v                | with f           |                      |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------|----------------------|--|--|

| Syntax:           | [ label ]                                                                                                                                                            | IORWF                   | f,d              |                      |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$                                                                                                     | 27                      |                  |                      |  |  |

| Operation:        | (W) .OR.                                                                                                                                                             | (f) $\rightarrow$ (de   | estination       | )                    |  |  |

| Status Affected:  | Z                                                                                                                                                                    |                         |                  |                      |  |  |

| Encoding:         | 00                                                                                                                                                                   | 0100                    | dfff             | ffff                 |  |  |

| Description:      | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is 0 the result is placed in the<br>W register. If 'd' is 1 the result is placed<br>back in register 'f'. |                         |                  |                      |  |  |

| Words:            | 1                                                                                                                                                                    |                         |                  |                      |  |  |

| Cycles:           | 1                                                                                                                                                                    |                         |                  |                      |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                   | Q2                      | Q3               | Q4                   |  |  |

|                   | Decode                                                                                                                                                               | Read<br>register<br>'f' | Process<br>data  | Write to destination |  |  |

| Example           | IORWF                                                                                                                                                                |                         | RESULT,          | 0                    |  |  |

|                   | Before In                                                                                                                                                            |                         |                  |                      |  |  |

|                   |                                                                                                                                                                      | RESULT<br>W             | = 0x13<br>= 0x91 | -                    |  |  |

|                   | After Inst                                                                                                                                                           |                         |                  | 3                    |  |  |

| MOVLW             | Move Literal to W                                                                          |  |  |  |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:           | [ <i>label</i> ] MOVLW k                                                                   |  |  |  |  |  |  |  |

| Operands:         | $0 \le k \le 255$                                                                          |  |  |  |  |  |  |  |

| Operation:        | $k \to (W)$                                                                                |  |  |  |  |  |  |  |

| Status Affected:  | None                                                                                       |  |  |  |  |  |  |  |

| Encoding:         | 11 00xx kkkk kkkk                                                                          |  |  |  |  |  |  |  |

| Description:      | The eight bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |  |  |  |  |  |  |  |

| Words:            | 1                                                                                          |  |  |  |  |  |  |  |

| Cycles:           | 1                                                                                          |  |  |  |  |  |  |  |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                |  |  |  |  |  |  |  |

|                   | Decode Read literal 'k' Process Write to data W                                            |  |  |  |  |  |  |  |

| Example           | MOVLW $0x5A$<br>After Instruction<br>W = 0x5A                                              |  |  |  |  |  |  |  |

| MOVF              | Move f                                                                                                                                                                                                                                                        |                         |                 |                      |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|----------------------|--|--|--|

| Syntax:           | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                     |                         |                 |                      |  |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$                                                                                                                                                                                              | 7                       |                 |                      |  |  |  |

| Operation:        | $(f) \rightarrow (de)$                                                                                                                                                                                                                                        | stination               | )               |                      |  |  |  |

| Status Affected:  | Z                                                                                                                                                                                                                                                             |                         |                 |                      |  |  |  |

| Encoding:         | 00                                                                                                                                                                                                                                                            | 1000                    | dfff            | ffff                 |  |  |  |

| Description:      | ption: The contents of register f is moved to a destination dependant upon the status of d. If d = 0, destination is W register. I d = 1, the destination is file register f itself. d = 1 is useful to test a file register since status flag Z is affected. |                         |                 |                      |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                             |                         |                 |                      |  |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                             |                         |                 |                      |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                                                                            | Q2                      | Q3              | Q4                   |  |  |  |

|                   | Decode                                                                                                                                                                                                                                                        | Read<br>register<br>'f' | Process<br>data | Write to destination |  |  |  |

| Example           | MOVF                                                                                                                                                                                                                                                          | ,                       | 0               |                      |  |  |  |

|                   | After Instruction<br>W = value in FSR register<br>Z = 1                                                                                                                                                                                                       |                         |                 |                      |  |  |  |

| MOVWF             | to f                                  |                         |                  |                       |  |  |  |  |

|-------------------|---------------------------------------|-------------------------|------------------|-----------------------|--|--|--|--|

| Syntax:           | [ label ]                             | MOVW                    | = f              |                       |  |  |  |  |

| Operands:         | $0 \le f \le 127$                     |                         |                  |                       |  |  |  |  |

| Operation:        | $(W) \rightarrow (f)$                 |                         |                  |                       |  |  |  |  |

| Status Affected:  | None                                  |                         |                  |                       |  |  |  |  |

| Encoding:         | 00                                    | 0000                    | lfff             | ffff                  |  |  |  |  |

| Description:      | Move data from W register to register |                         |                  |                       |  |  |  |  |

| Words:            | 1                                     |                         |                  |                       |  |  |  |  |

| Cycles:           | 1                                     |                         |                  |                       |  |  |  |  |

| Q Cycle Activity: | Q1                                    | Q2                      | Q3               | Q4                    |  |  |  |  |

|                   | Decode                                | Read<br>register<br>'f' | Process<br>data  | Write<br>register 'f' |  |  |  |  |

| Example           | MOVWF                                 | OPTIC                   | DN_REG           |                       |  |  |  |  |

|                   | Before Instruction                    |                         |                  |                       |  |  |  |  |

|                   |                                       | OPTION<br>W             | = 0xFl<br>= 0x4l |                       |  |  |  |  |

|                   | After Inst                            | ruction                 |                  |                       |  |  |  |  |

|                   |                                       | OPTION                  |                  |                       |  |  |  |  |

|                   |                                       | W                       | = 0x4l           | F                     |  |  |  |  |

## Applicable Devices 72 73 73A 74 74A 76 77

#### 17.1 DC Characteristics: PIC16C72-04 (Commercial, Industrial, Extended) PIC16C72-10 (Commercial, Industrial, Extended) PIC16C72-20 (Commercial, Industrial, Extended)

| DC CHARACTERISTICS             |                                                                   |       |                  | ing tem                   |                      | ure -4<br>-4         | litions (unless otherwise stated) $10^{\circ}C \leq TA \leq +125^{\circ}C$ for extended, $10^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial and $2C \leq TA \leq +70^{\circ}C$ for commercial |

|--------------------------------|-------------------------------------------------------------------|-------|------------------|---------------------------|----------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                   | Characteristic                                                    | Sym   | Min              | Тур†                      | Max                  | Units                | Conditions                                                                                                                                                                                        |

| D001<br>D001A                  | Supply Voltage                                                    | Vdd   | 4.0<br>4.5       | -                         | 6.0<br>5.5           | V<br>V               | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                                                           |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                            | Vdr   | -                | 1.5                       | -                    | V                    |                                                                                                                                                                                                   |

| D003                           | VDD start voltage to<br>ensure internal Power-<br>on Reset Signal | VPOR  | -                | Vss                       | -                    | V                    | See section on Power-on Reset for details                                                                                                                                                         |

| D004*                          | VDD rise rate to ensure<br>internal Power-on Reset<br>Signal      | SVDD  | 0.05             | -                         | -                    | V/ms                 | See section on Power-on Reset for details                                                                                                                                                         |

| D005                           | Brown-out Reset Voltage                                           | Bvdd  | 3.7              | 4.0                       | 4.3                  | V                    | BODEN bit in configuration word enabled                                                                                                                                                           |