Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 192 x 8                                                                     |

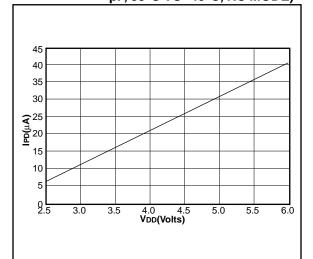

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | A/D 5x8b                                                                    |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-LCC (J-Lead)                                                             |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc74at-04i-l |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 GENERAL DESCRIPTION

The PIC16C7X is a family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with integrated analog-to-digital (A/D) converters, in the PIC16CXX mid-range family.

All PIC16/17 microcontrollers employ an advanced RISC architecture. The PIC16CXX microcontroller family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches which require two cycles. A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The **PIC16C72** has 128 bytes of RAM and 22 I/O pins. In addition several peripheral features are available including: three timer/counters, one Capture/Compare/ PWM module and one serial port. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. Also a 5-channel high-speed 8-bit A/D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The PIC16C73/73A devices have 192 bytes of RAM, while the PIC16C76 has 368 byes of RAM. Each device has 22 I/O pins. In addition, several peripheral features are available including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. The Universal Syn-Asynchronous Receiver chronous Transmitter (USART) is also known as the Serial Communications Interface or SCI. Also a 5-channel high-speed 8-bit A/ D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The **PIC16C74/74A** devices have 192 bytes of RAM, while the **PIC16C77** has 368 bytes of RAM. Each device has 33 I/O pins. In addition several peripheral features are available including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. The Universal Synchronous Asynchronous Receiver Transmitter (USART) is also known as the Serial Communications Interface or SCI. An 8-bit Parallel Slave Port is provided. Also an 8-channel high-speed

8-bit A/D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The PIC16C7X family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) feature provides a power saving mode. The user can wake up the chip from SLEEP through several external and internal interrupts and resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lockup.

A UV erasable CERDIP packaged version is ideal for code development while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume.

The PIC16C7X family fits perfectly in applications ranging from security and remote sensors to appliance control and automotive. The EPROM technology makes customization of application programs (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16C7X very versatile even in areas where no microcontroller use has been considered before (e.g. timer functions, serial communication, capture and compare, PWM functions and coprocessor applications).

## 1.1 Family and Upward Compatibility

Users familiar with the PIC16C5X microcontroller family will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for the PIC16C5X can be easily ported to the PIC16CXX family of devices (Appendix B).

## 1.2 Development Support

PIC16C7X devices are supported by the complete line of Microchip Development tools.

Please refer to Section 16.0 for more details about Microchip's development tools.

|            |                                                 | PIC16C710                           | PIC16C71            | PIC16C711                           | PIC16C715                           | PIC16C72                   | PIC16CR72 <sup>(1)</sup>   |  |  |  |  |  |

|------------|-------------------------------------------------|-------------------------------------|---------------------|-------------------------------------|-------------------------------------|----------------------------|----------------------------|--|--|--|--|--|

| Clock      | Maximum Frequency<br>of Operation (MHz)         | 20                                  | 20                  | 20                                  | 20                                  | 20                         | 20                         |  |  |  |  |  |

|            | EPROM Program Memory<br>(x14 words)             | 512                                 | 1K                  | 1K                                  | 2К                                  | 2К                         | —                          |  |  |  |  |  |

| lemory     | ROM Program Memory<br>(14K words)               | _                                   | _                   | _                                   | _                                   | _                          | 2К                         |  |  |  |  |  |

|            | Data Memory (bytes)                             | 36                                  | 36                  | 68                                  | 128                                 | 128                        | 128                        |  |  |  |  |  |

|            | Timer Module(s)                                 | TMR0                                | TMR0                | TMR0                                | TMR0                                | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2     |  |  |  |  |  |

| eripherals | Capture/Compare/<br>PWM Module(s)               | —                                   | _                   | —                                   | —                                   | 1                          | 1                          |  |  |  |  |  |

|            | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | _                                   | _                   | —                                   | —                                   | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C       |  |  |  |  |  |

|            | Parallel Slave Port                             | _                                   | —                   | —                                   | _                                   | _                          | —                          |  |  |  |  |  |

|            | A/D Converter (8-bit) Channels                  | 4                                   | 4                   | 4                                   | 4                                   | 5                          | 5                          |  |  |  |  |  |

|            | Interrupt Sources                               | 4                                   | 4                   | 4                                   | 4                                   | 8                          | 8                          |  |  |  |  |  |

|            | I/O Pins                                        | 13                                  | 13                  | 13                                  | 13                                  | 22                         | 22                         |  |  |  |  |  |

|            | Voltage Range (Volts)                           | 3.0-6.0                             | 3.0-6.0             | 3.0-6.0                             | 3.0-5.5                             | 2.5-6.0                    | 3.0-5.5                    |  |  |  |  |  |

| atures     | In-Circuit Serial Programming                   | Yes                                 | Yes                 | Yes                                 | Yes                                 | Yes                        | Yes                        |  |  |  |  |  |

|            | Brown-out Reset                                 | Yes                                 | —                   | Yes                                 | Yes                                 | Yes                        | Yes                        |  |  |  |  |  |

|            | Packages                                        | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC, SSOP |  |  |  |  |  |

## TABLE 1-1: PIC16C7XX FAMILY OF DEVCES

|             |                                                   | PIC16C73A                   | PIC16C74A                                 | PIC16C76                    | PIC16C77                                  |

|-------------|---------------------------------------------------|-----------------------------|-------------------------------------------|-----------------------------|-------------------------------------------|

| Clock       | Maximum Frequency of Oper-<br>ation (MHz)         | 20                          | 20                                        | 20                          | 20                                        |

| Memory      | EPROM Program Memory<br>(x14 words)               | 4K                          | 4K                                        | 8K                          | 8K                                        |

|             | Data Memory (bytes)                               | 192                         | 192                                       | 368                         | 368                                       |

|             | Timer Module(s)                                   | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    |

| Peripherals | Capture/Compare/PWM Mod-<br>ule(s)                | 2                           | 2                                         | 2                           | 2                                         |

|             | Serial Port(s) (SPI/I <sup>2</sup> C, US-<br>ART) | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               |

|             | Parallel Slave Port                               | —                           | Yes                                       | —                           | Yes                                       |

|             | A/D Converter (8-bit) Channels                    | 5                           | 8                                         | 5                           | 8                                         |

|             | Interrupt Sources                                 | 11                          | 12                                        | 11                          | 12                                        |

|             | I/O Pins                                          | 22                          | 33                                        | 22                          | 33                                        |

|             | Voltage Range (Volts)                             | 2.5-6.0                     | 2.5-6.0                                   | 2.5-6.0                     | 2.5-6.0                                   |

| eatures     | In-Circuit Serial Programming                     | Yes                         | Yes                                       | Yes                         | Yes                                       |

|             | Brown-out Reset                                   | Yes                         | Yes                                       | Yes                         | Yes                                       |

|             | Packages                                          | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C7XX Family devices use serial programming with clock pin RB6 and data pin RB7.

Note 1: Please contact your local Microchip sales office for availability of these devices.

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. The special function registers can be classified into two sets (core and peripheral). Those registers associated with the "core" functions are described in this section, and those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address              | Name    | Bit 7              | Bit 6                                                                    | Bit 5         | Bit 4          | Bit 3          | Bit 2            | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(3) |

|----------------------|---------|--------------------|--------------------------------------------------------------------------|---------------|----------------|----------------|------------------|---------------|-----------|--------------------------|-------------------------------------|

| Bank 0               |         |                    |                                                                          |               |                |                |                  |               |           |                          |                                     |

| 00h <sup>(1)</sup>   | INDF    | Addressing         | this location                                                            | uses conten   | ts of FSR to   | address data   | a memory (n      | ot a physical | register) | 0000 0000                | 0000 0000                           |

| 01h                  | TMR0    | Timer0 mod         | dule's registe                                                           | r             |                |                |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 02h <sup>(1)</sup>   | PCL     | Program Co         | ounter's (PC)                                                            | Least Signif  | icant Byte     |                |                  |               |           | 0000 0000                | 0000 0000                           |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(4)</sup> | RP1 <sup>(4)</sup>                                                       | RP0           | TO             | PD             | Z                | DC            | С         | 0001 1xxx                | 000q quuu                           |

| 04h <sup>(1)</sup>   | FSR     | Indirect dat       | a memory ac                                                              | ldress pointe | r              |                |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 05h                  | PORTA   | _                  | _                                                                        | PORTA Dat     | a Latch whe    | n written: PO  | RTA pins wh      | en read       |           | 0x 0000                  | 0u 0000                             |

| 06h                  | PORTB   | PORTB Da           | ta Latch whe                                                             | n written: PC | RTB pins wl    | nen read       |                  |               |           | XXXX XXXX                | uuuu uuuu                           |

| 07h                  | PORTC   | PORTC Da           | ta Latch whe                                                             | n written: PC | ORTC pins w    | hen read       |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 08h                  | —       | Unimpleme          | nted                                                                     |               |                |                |                  |               |           | —                        | —                                   |

| 09h                  | —       | Unimpleme          | nted                                                                     |               |                |                |                  |               |           | _                        | _                                   |

| 0Ah <sup>(1,2)</sup> | PCLATH  | —                  | —                                                                        | —             | Write Buffe    | r for the uppe | er 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                              |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                | PEIE                                                                     | TOIE          | INTE           | RBIE           | TOIF             | INTF          | RBIF      | 0000 000x                | 0000 000u                           |

| 0Ch                  | PIR1    | —                  | ADIF                                                                     | _             | —              | SSPIF          | CCP1IF           | TMR2IF        | TMR1IF    | -0 0000                  | -0 0000                             |

| 0Dh                  | —       | Unimpleme          | nplemented                                                               |               |                |                |                  |               |           | —                        | _                                   |

| 0Eh                  | TMR1L   | Holding reg        | ling register for the Least Significant Byte of the 16-bit TMR1 register |               |                |                |                  |               | xxxx xxxx | uuuu uuuu                |                                     |

| 0Fh                  | TMR1H   | Holding reg        | ister for the N                                                          | Most Signific | ant Byte of th | ne 16-bit TMF  | R1 register      |               |           | xxxx xxxx                | uuuu uuuu                           |

| 10h                  | T1CON   | —                  | -                                                                        | T1CKPS1       | T1CKPS0        | T1OSCEN        | T1SYNC           | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                             |

| 11h                  | TMR2    | Timer2 mod         | dule's registe                                                           | r             |                |                |                  |               |           | 0000 0000                | 0000 0000                           |

| 12h                  | T2CON   | —                  | TOUTPS3                                                                  | TOUTPS2       | TOUTPS1        | TOUTPS0        | TMR2ON           | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                           |

| 13h                  | SSPBUF  | Synchronou         | us Serial Port                                                           | Receive Bu    | ffer/Transmit  | Register       |                  |               |           | XXXX XXXX                | uuuu uuuu                           |

| 14h                  | SSPCON  | WCOL               | SSPOV                                                                    | SSPEN         | CKP            | SSPM3          | SSPM2            | SSPM1         | SSPM0     | 0000 0000                | 0000 0000                           |

| 15h                  | CCPR1L  | Capture/Co         | mpare/PWM                                                                | Register (LS  | SB)            |                |                  | -             |           | xxxx xxxx                | uuuu uuuu                           |

| 16h                  | CCPR1H  | Capture/Co         | mpare/PWM                                                                | Register (M   | SB)            |                |                  |               |           | XXXX XXXX                | uuuu uuuu                           |

| 17h                  | CCP1CON | —                  | —                                                                        | CCP1X         | CCP1Y          | CCP1M3         | CCP1M2           | CCP1M1        | CCP1M0    | 00 0000                  | 00 0000                             |

| 18h                  | —       | Unimpleme          | nted                                                                     |               |                |                |                  |               |           | _                        | _                                   |

| 19h                  | —       | Unimpleme          | nted                                                                     |               |                |                |                  |               |           | —                        | —                                   |

| 1Ah                  | —       | Unimpleme          | nted                                                                     |               |                |                |                  |               |           | —                        | _                                   |

| 1Bh                  | _       | Unimpleme          | nted                                                                     |               |                |                |                  |               |           | _                        | _                                   |

| 1Ch                  | —       | Unimpleme          | nted                                                                     |               |                |                |                  |               |           | _                        | —                                   |

| 1Dh                  | —       | Unimpleme          | nted                                                                     |               |                |                |                  |               |           | —                        | —                                   |

| 1Eh                  | ADRES   | A/D Result         | Register                                                                 |               |                |                |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 1Fh                  | ADCON0  | ADCS1              | ADCS0                                                                    | CHS2          | CHS1           | CHS0           | GO/DONE          | _             | ADON      | 0000 00-0                | 0000 00-0                           |

TABLE 4-1: PIC16C72 SPECIAL FUNCTION REGISTER SUMMARY

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

4: The IRP and RP1 bits are reserved on the PIC16C72, always maintain these bits clear.

## 4.3 PCL and PCLATH Applicable Devices 72/73/73A/74/74A/76/77

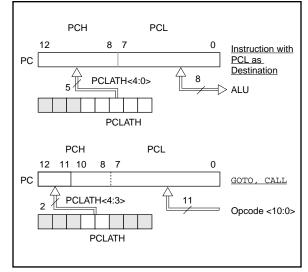

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any reset, the upper bits of the PC will be cleared. Figure 4-17 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 4-17: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note *"Implementing a Table Read"* (AN556).

#### 4.3.2 STACK

The PIC16CXX family has an 8 level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no status bits to indicate stack overflow or stack underflow conditions.

- Note 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address.

## 4.4 Program Memory Paging Applicable Devices 72|73|73A|74|74A|76|77

PIC16C7X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<4:3> bits are not required for the return instructions (which POPs the address from the stack).

Note: PIC16C7X devices with 4K or less of program memory ignore paging bit PCLATH<4>. The use of PCLATH<4> as a general purpose read/write bit is not recommended since this may affect upward compatibility with future products. Example 4-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the interrupt service routine (if interrupts are used).

#### EXAMPLE 4-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

| ORG 0x | 500      |                            |

|--------|----------|----------------------------|

| BSF    | pclath,3 | ;Select page 1 (800h-FFFh) |

| BCF    | pclath,4 | ;Only on >4K devices       |

| CALL   | SUB1_P1  | ;Call subroutine in        |

|        | :        | ;page 1 (800h-FFFh)        |

|        | :        |                            |

|        | :        |                            |

| ORG 0x | 900      |                            |

| SUB1_P | 1:       | ;called subroutine         |

|        | :        | ;page 1 (800h-FFFh)        |

|        | :        |                            |

| RETURN |          | ;return to Call subroutine |

|        |          | ;in page 0 (000h-7FFh)     |

|        |          |                            |

## 4.5 <u>Indirect Addressing, INDF and FSR</u> <u>Registers</u>

|    | •  | cabl |    |     |    |    |

|----|----|------|----|-----|----|----|

| 72 | 73 | 73A  | 74 | 74A | 76 | 77 |

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

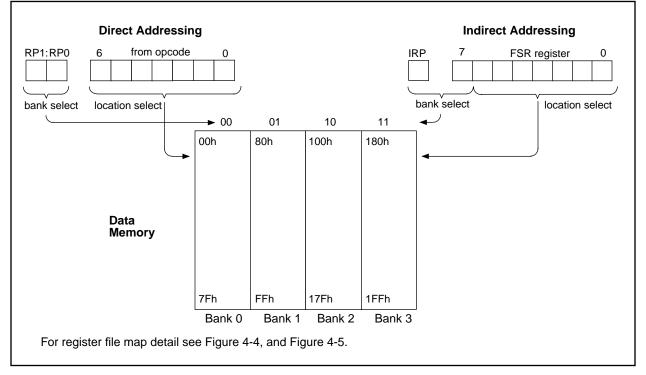

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself indirectly (FSR = '0') will read 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-18.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 4-2.

## EXAMPLE 4-2: INDIRECT ADDRESSING

| NEXT     | movwf<br>clrf<br>incf | INDF<br>FSR,F | <pre>;initialize pointer ;to RAM ;clear INDF register ;inc pointer ;all done? ;no clear next</pre> |

|----------|-----------------------|---------------|----------------------------------------------------------------------------------------------------|

| CONTINUE |                       |               |                                                                                                    |

|          | :                     |               | ;yes continue                                                                                      |

## FIGURE 4-18: DIRECT/INDIRECT ADDRESSING

## TABLE 5-1: PORTA FUNCTIONS

| Name         | Bit# | Buffer | Function                                                                       |

|--------------|------|--------|--------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF                                           |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0                                |

|              |      |        | Output is open drain type                                                      |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input |

Legend: TTL = TTL input, ST = Schmitt Trigger input

## TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5     | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|--------|-------|-------|-----------|-------------------------------|-------|-------|-------|-------|--------------------------|---------------------------|

| 05h     | PORTA  | —     | _     | RA5       | RA4                           | RA3   | RA2   | RA1   | RA0   | 0x 0000                  | 0u 0000                   |

| 85h     | TRISA  | —     | —     | PORTA Dat | PORTA Data Direction Register |       |       |       |       |                          | 11 1111                   |

| 9Fh     | ADCON1 | —     |       | —         | _                             | _     | PCFG2 | PCFG1 | PCFG0 | 000                      | 000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

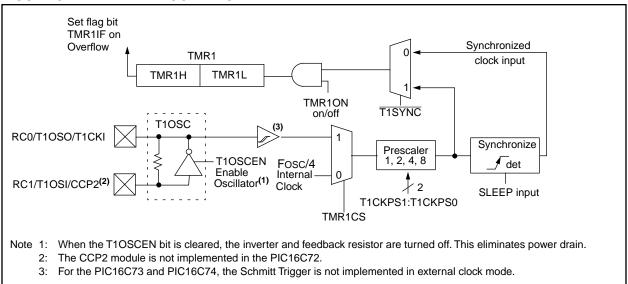

## 8.1 <u>Timer1 Operation in Timer Mode</u>

## Applicable Devices

Timer mode is selected by clearing the TMR1CS (T1CON<1>) bit. In this mode, the input clock to the timer is FOSC/4. The synchronize control bit T1SYNC (T1CON<2>) has no effect since the internal clock is always in sync.

## 8.2 <u>Timer1 Operation in Synchronized</u> Counter Mode Applicable Devices 72 73 73A 74 74A 76 77

Counter mode is selected by setting bit TMR1CS. In this mode the timer increments on every rising edge of clock input on pin RC1/T1OSI/CCP2 when bit T1OSCEN is set or pin RC0/T1OSO/T1CKI when bit T1OSCEN is cleared.

If T1SYNC is cleared, then the external clock input is synchronized with internal phase clocks. The synchronization is done after the prescaler stage. The prescaler stage is an asynchronous ripple-counter.

In this configuration, during SLEEP mode, Timer1 will not increment even if the external clock is present, since the synchronization circuit is shut off. The prescaler however will continue to increment.

#### 8.2.1 EXTERNAL CLOCK INPUT TIMING FOR SYNCHRONIZED COUNTER MODE

When an external clock input is used for Timer1 in synchronized counter mode, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of TMR1 after synchronization.

When the prescaler is 1:1, the external clock input is the same as the prescaler output. The synchronization of T1CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T1CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the appropriate electrical specifications, parameters 45, 46, and 47.

When a prescaler other than 1:1 is used, the external clock input is divided by the asynchronous ripplecounter type prescaler so that the prescaler output is symmetrical. In order for the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for T1CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T1CKI high and low time is that they do not violate the minimum pulse width requirements of 10 ns). Refer to the appropriate electrical specifica-tions, parameters 40, 42, 45, 46, and 47.

## FIGURE 8-2: TIMER1 BLOCK DIAGRAM

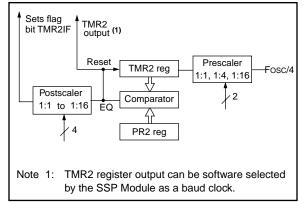

## 9.0 TIMER2 MODULE

## Applicable Devices 72|73|73A|74|74A|76|77

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time-base for PWM mode of the CCP module(s). The TMR2 register is readable and writable, and is cleared on any device reset.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon reset.

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

Timer2 can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Figure 9-2 shows the Timer2 control register.

## 9.1 <u>Timer2 Prescaler and Postscaler</u> Applicable Devices

72 73 73A 74 74A 76 77

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device reset (Power-on Reset, MCLR reset, Watchdog Timer reset, or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module which optionally uses it to generate shift clock.

### FIGURE 9-1: TIMER2 BLOCK DIAGRAM

|  | TABLE 10-5: | <b>REGISTERS ASSOCIATED WITH PWM AND TIMER2</b> |

|--|-------------|-------------------------------------------------|

|--|-------------|-------------------------------------------------|

| Address               | Name    | Bit 7                  | Bit 6                                                                                                                         | Bit 5         | Bit 4     | Bit 3     | Bit 2  | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|-----------------------|---------|------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------|-----------|-----------|--------|---------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                    | PEIE                                                                                                                          | TOIE          | INTE      | RBIE      | TOIF   | INTF    | RBIF    | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1    | PSPIF <sup>(1,2)</sup> | ADIF                                                                                                                          | TMR1IF        | 0000 0000 | 0000 0000 |        |         |         |                          |                                 |

| 0Dh <sup>(2)</sup>    | PIR2    | —                      | _                                                                                                                             | _             |           | _         | _      | _       | CCP2IF  | 0                        | 0                               |

| 8Ch                   | PIE1    | PSPIE <sup>(1,2)</sup> | SPIE <sup>(1,2)</sup> ADIE         RCIE <sup>(2)</sup> TXIE <sup>(2)</sup> SSPIE         CCP1IE         TMR2IE         TMR1IE |               |           |           |        |         |         |                          | 0000 0000                       |

| 8Dh <sup>(2)</sup>    | PIE2    | —                      | CCP2IE                                                                                                                        |               |           |           |        |         |         |                          | 0                               |

| 87h                   | TRISC   | PORTC Da               | ata Directio                                                                                                                  |               | 1111 1111 | 1111 1111 |        |         |         |                          |                                 |

| 11h                   | TMR2    | Timer2 mod             | dule's registe                                                                                                                | ər            |           |           |        |         |         | 0000 0000                | 0000 0000                       |

| 92h                   | PR2     | Timer2 mod             | dule's perioc                                                                                                                 | l register    |           |           |        |         |         | 1111 1111                | 1111 1111                       |

| 12h                   | T2CON   | —                      | TOUTPS3                                                                                                                       | TOUTPS2       | TOUTPS1   | TOUTPS0   | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000                | -000 0000                       |

| 15h                   | CCPR1L  | Capture/Co             | mpare/PWN                                                                                                                     | / register1 ( | LSB)      |           |        |         |         | xxxx xxxx                | uuuu uuuu                       |

| 16h                   | CCPR1H  | Capture/Co             | mpare/PWN                                                                                                                     | / register1 ( | (MSB)     |           |        |         |         | xxxx xxxx                | uuuu uuuu                       |

| 17h                   | CCP1CON | —                      | —                                                                                                                             | CCP1X         | CCP1Y     | CCP1M3    | CCP1M2 | CCP1M1  | CCP1M0  | 00 0000                  | 00 0000                         |

| 1Bh <b>(2)</b>        | CCPR2L  | Capture/Co             | mpare/PWN                                                                                                                     | / register2 ( | LSB)      |           |        |         |         | xxxx xxxx                | uuuu uuuu                       |

| 1Ch <sup>(2)</sup>    | CCPR2H  | Capture/Co             | mpare/PWN                                                                                                                     | / register2 ( | (MSB)     |           |        |         |         | xxxx xxxx                | uuuu uuuu                       |

| 1Dh <sup>(2)</sup>    | CCP2CON | —                      | —                                                                                                                             | CCP2X         | CCP2Y     | CCP2M3    | CCP2M2 | CCP2M1  | CCP2M0  | 00 0000                  | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PWM and Timer2.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

2: The PIC16C72 does not have a Parallel Slave Port, USART or CCP2 module, these bits are unimplemented, read as '0'.

## 14.0 SPECIAL FEATURES OF THE CPU Applicable Devices

72 73 73A 74 74A 76 77

What sets a microcontroller apart from other processors are special circuits to deal with the needs of realtime applications. The PIC16CXX family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- · Oscillator selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID locations

- · In-circuit serial programming

The PIC16CXX has a Watchdog Timer which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

## 14.1 Configuration Bits

Applicable Devices

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

#### FIGURE 14-1: CONFIGURATION WORD FOR PIC16C73/74

|           |                                                           | —                                   | —                                | —                     |          | _    | CP1 | CP0 | PWRTE | WDTE | FOSC1 | FOSC0 | Register: | CONFIG |

|-----------|-----------------------------------------------------------|-------------------------------------|----------------------------------|-----------------------|----------|------|-----|-----|-------|------|-------|-------|-----------|--------|

| bit13     |                                                           |                                     |                                  |                       |          |      |     |     |       |      |       | bit0  | Address   | 2007h  |

| bit 13-5: | Unimple                                                   | mented                              | I: Read                          | as '1'                |          |      |     |     |       |      |       |       |           |        |

| bit 4:    | CP1:CP0<br>11 = Coo<br>10 = Upp<br>01 = Upp<br>00 = All r | le prote<br>per half<br>per 3/4th   | ction of<br>of progin<br>of prog | f<br>ram me<br>gram m | emory    | •    |     | d   |       |      |       |       |           |        |

| bit 3:    | <b>PWRTE</b> :<br>1 = Powe<br>0 = Powe                    | r-up Tin                            | ner ena                          | bled                  | le bit   |      |     |     |       |      |       |       |           |        |

| bit 2:    | <b>WDTE</b> : W<br>1 = WDT<br>0 = WDT                     | enable                              | d                                | r Enable              | e bit    |      |     |     |       |      |       |       |           |        |

| bit 1-0:  | FOSC1:F<br>11 = RC<br>10 = HS<br>01 = XT<br>00 = LP 0     | oscillato<br>oscillato<br>oscillato | or<br>or<br>or                   | tor Sele              | ection b | vits |     |     |       |      |       |       |           |        |

## 14.2 Oscillator Configurations Applicable Devices 72/73/73A/74/74A/76/77

#### 14.2.1 OSCILLATOR TYPES

The PIC16CXX can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

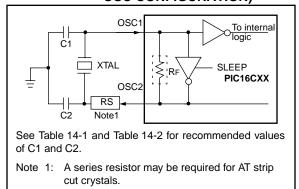

- 14.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

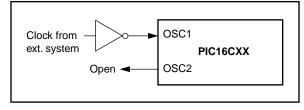

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 14-3). The PIC16CXX Oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1/ CLKIN pin (Figure 14-4).

#### FIGURE 14-3: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

### FIGURE 14-4: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

#### TABLE 14-1: CERAMIC RESONATORS

| Ranges Te | ested:                               |                                    |               |  |  |

|-----------|--------------------------------------|------------------------------------|---------------|--|--|

| Mode      | Freq                                 | OSC1                               | OSC2          |  |  |

| XT        | 455 kHz                              | 68 - 100 pF                        | 68 - 100 pF   |  |  |

|           | 2.0 MHz                              | 15 - 68 pF                         | 15 - 68 pF    |  |  |

|           | 4.0 MHz                              | 15 - 68 pF                         | 15 - 68 pF    |  |  |

| HS        | 8.0 MHz                              | 10 - 68 pF                         | 10 - 68 pF    |  |  |

|           | 16.0 MHz                             | 10 - 22 pF                         | 10 - 22 pF    |  |  |

|           | se values are f<br>as at bottom of p | i <b>or design guidar</b><br>bage. | nce only. See |  |  |

| Resonato  | rs Used:                             |                                    |               |  |  |

| 455 kHz   | Panasonic E                          | FO-A455K04B                        | ± 0.3%        |  |  |

| 2.0 MHz   | Murata Erie                          | Murata Erie CSA2.00MG ± 0.5%       |               |  |  |

| 4.0 MHz   | Murata Erie CSA4.00MG ± 0.5%         |                                    |               |  |  |

| 8.0 MHz   | Murata Erie                          | Murata Erie CSA8.00MT ± 0.5%       |               |  |  |

| 16.0 MHz  | Murata Erie                          | CSA16.00MX                         | ± 0.5%        |  |  |

| All reso  | onators used did                     | d not have built-in                | capacitors.   |  |  |

## TABLE 14-2:CAPACITOR SELECTION<br/>FOR CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |

|----------|-----------------|------------------|------------------|

| LP       | 32 kHz          | 33 pF            | 33 pF            |

|          | 200 kHz         | 15 pF            | 15 pF            |

| XT       | 200 kHz         | 47-68 pF         | 47-68 pF         |

|          | 1 MHz           | 15 pF            | 15 pF            |

|          | 4 MHz           | 15 pF            | 15 pF            |

| HS       | 4 MHz           | 15 pF            | 15 pF            |

|          | 8 MHz           | 15-33 pF         | 15-33 pF         |

|          | 20 MHz          | 15-33 pF         | 15-33 pF         |

These values are for design guidance only. See notes at bottom of page.

|         | Crystals Used          |              |

|---------|------------------------|--------------|

| 32 kHz  | Epson C-001R32.768K-A  | $\pm$ 20 PPM |

| 200 kHz | STD XTL 200.000KHz     | ± 20 PPM     |

| 1 MHz   | ECS ECS-10-13-1        | $\pm$ 50 PPM |

| 4 MHz   | ECS ECS-40-20-1        | $\pm$ 50 PPM |

| 8 MHz   | EPSON CA-301 8.000M-C  | $\pm$ 30 PPM |

| 20 MHz  | EPSON CA-301 20.000M-C | $\pm$ 30 PPM |

Note 1: Recommended values of C1 and C2 are identical to the ranges tested (Table 14-1).

- 2: Higher capacitance increases the stability of oscillator but also increases the start-up time.

- 3: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification.

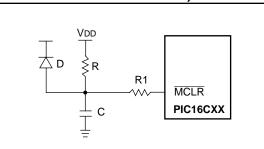

#### FIGURE 14-13: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

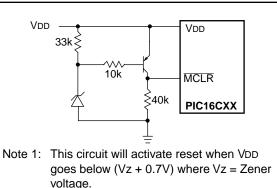

#### FIGURE 14-14: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- 2: Internal brown-out detection on the PIC16C72/73A/74A/76/77 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

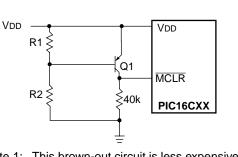

## FIGURE 14-15: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

- 2: Internal brown-out detection on the PIC16C72/73A/74A/76/77 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

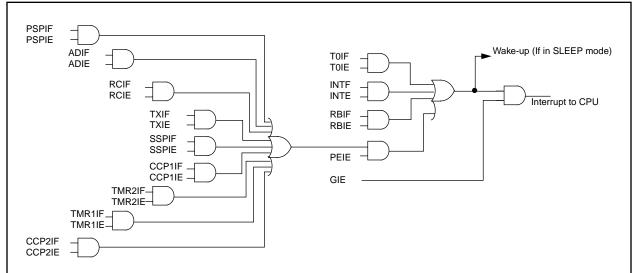

#### FIGURE 14-16: INTERRUPT LOGIC

The following table shows which devices have which interrupts.

| Device    | TOIF | INTF | RBIF | PSPIF | ADIF | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF | CCP2IF |

|-----------|------|------|------|-------|------|------|------|-------|--------|--------|--------|--------|

| PIC16C72  | Yes  | Yes  | Yes  | -     | Yes  | -    | -    | Yes   | Yes    | Yes    | Yes    | -      |

| PIC16C73  | Yes  | Yes  | Yes  | -     | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C73A | Yes  | Yes  | Yes  | -     | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C74  | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C74A | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C76  | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

| PIC16C77  | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes    |

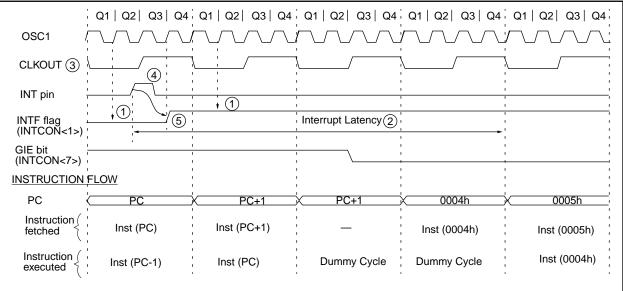

#### FIGURE 14-17: INT PIN INTERRUPT TIMING

Note 1: INTF flag is sampled here (every Q1).

- 2: Interrupt latency = 3-4 Tcy where Tcy = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

3: CLKOUT is available only in RC oscillator mode.

4: For minimum width of INT pulse, refer to AC specs.

5: INTF is enabled to be set anytime during the Q4-Q1 cycles.

## Applicable Devices 72 73 73A 74 74A 76 77

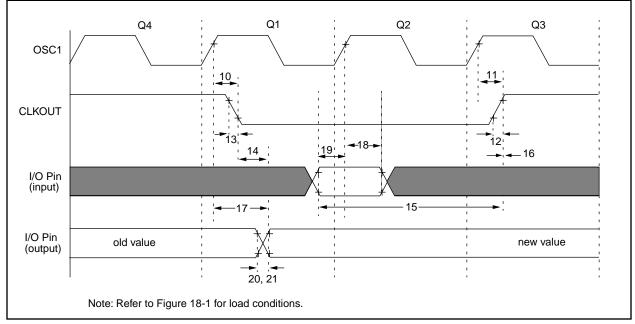

## FIGURE 18-3: CLKOUT AND I/O TIMING

| TABLE 18-3: CLKOUT AND I/O TIMING REQUIREMENTS |

|------------------------------------------------|

|------------------------------------------------|

| Parameter<br>No. | Sym      | Characteristic                                    |                                     | Min | Тур† | Мах         | Units | Conditions |

|------------------|----------|---------------------------------------------------|-------------------------------------|-----|------|-------------|-------|------------|

| 10*              | TosH2ckL | OSC1 <sup>↑</sup> to CLKOUT↓                      |                                     | _   | 75   | 200         | ns    | Note 1     |

| 11*              | TosH2ckH | OSC1 <sup>↑</sup> to CLKOUT <sup>↑</sup>          |                                     | —   | 75   | 200         | ns    | Note 1     |

| 12*              | TckR     | CLKOUT rise time                                  |                                     | _   | 35   | 100         | ns    | Note 1     |

| 13*              | TckF     | CLKOUT fall time                                  |                                     | _   | 35   | 100         | ns    | Note 1     |

| 14*              | TckL2ioV | CLKOUT ↓ to Port out vali                         | d                                   | _   | _    | 0.5Tcy + 20 | ns    | Note 1     |

| 15*              | TioV2ckH | Port in valid before CLKOU                        | id before CLKOUT ↑                  |     | _    | _           | ns    | Note 1     |

| 16*              | TckH2iol | Port in hold after CLKOUT                         | ort in hold after CLKOUT $\uparrow$ |     | _    | -           | ns    | Note 1     |

| 17*              | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to<br>Port out valid |                                     | -   | 50   | 150         | ns    |            |

| 18*              | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to                   | PIC16 <b>C</b> 73/74                | 100 | -    |             | ns    |            |

|                  |          | Port input invalid (I/O in hold time)             | PIC16 <b>LC</b> 73/74               | 200 | _    | _           | ns    |            |

| 19*              | TioV2osH | Port input valid to OSC11                         | (I/O in setup time)                 | 0   |      |             | ns    |            |

| 20*              | TioR     | Port output rise time                             | PIC16 <b>C</b> 73/74                | —   | 10   | 25          | ns    |            |

|                  |          |                                                   | PIC16LC73/74                        | —   | _    | 60          | ns    |            |

| 21*              | TioF     | Port output fall time                             | PIC16 <b>C</b> 73/74                | _   | 10   | 25          | ns    |            |

|                  |          |                                                   | PIC16 <b>LC</b> 73/74               | —   | _    | 60          | ns    |            |

| 22††*            | Tinp     | INT pin high or low time                          |                                     | Тсү | _    | _           | ns    |            |

| 23††*            | Trbp     | RB7:RB4 change INT high                           | n or low time                       | Тсү | —    | _           | ns    |            |

\* These parameters are characterized but not tested.

†Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

these parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

Applicable Devices 72 73 73A 74 74A 76 77

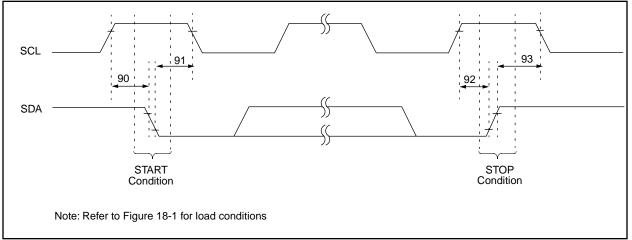

## FIGURE 18-9: I<sup>2</sup>C BUS START/STOP BITS TIMING

| Parameter<br>No. | Sym     | Characteristic  |              | Min  | Тур | Max | Units | Conditions                        |

|------------------|---------|-----------------|--------------|------|-----|-----|-------|-----------------------------------|

| 90               | TSU:STA | START condition | 100 kHz mode | 4700 | _   | _   | ns    | Only relevant for repeated START  |

|                  |         | Setup time      | 400 kHz mode | 600  |     | —   | 113   | condition                         |

| 91               | THD:STA | START condition | 100 kHz mode | 4000 |     | —   | ns    | After this period the first clock |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | 115   | pulse is generated                |

| 92               | TSU:STO | STOP condition  | 100 kHz mode | 4700 | —   | —   | ns    |                                   |

|                  |         | Setup time      | 400 kHz mode | 600  | —   | —   | 115   |                                   |

| 93               | THD:STO | STOP condition  | 100 kHz mode | 4000 | —   | —   | ns    |                                   |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | 113   |                                   |

## Applicable Devices 72 73 73A 74 74A 76 77

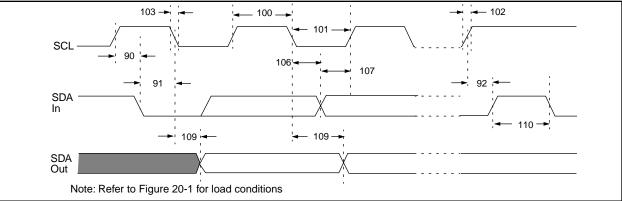

## FIGURE 20-14: I<sup>2</sup>C BUS DATA TIMING

## TABLE 20-10: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Parameter<br>No. | Sym     | Characteristic         |              | Min        | Мах  | Units | Conditions                                       |

|------------------|---------|------------------------|--------------|------------|------|-------|--------------------------------------------------|

| 100              | Thigh   | Clock high time        | 100 kHz mode | 4.0        | _    | μs    | Device must operate at a mini-<br>mum of 1.5 MHz |

|                  |         |                        | 400 kHz mode | 0.6        | _    | μs    | Device must operate at a mini-<br>mum of 10 MHz  |

|                  |         |                        | SSP Module   | 1.5Tcy     | —    |       |                                                  |

| 101              | TLOW    | Clock low time         | 100 kHz mode | 4.7        | —    | μs    | Device must operate at a mini-<br>mum of 1.5 MHz |

|                  |         |                        | 400 kHz mode | 1.3        | —    | μs    | Device must operate at a mini-<br>mum of 10 MHz  |

|                  |         |                        | SSP Module   | 1.5Tcy     | _    |       |                                                  |

| 102              | Tr      | SDA and SCL rise       | 100 kHz mode | -          | 1000 | ns    |                                                  |

|                  |         | time                   | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from<br>10 to 400 pF       |

| 103              | Tf      | SDA and SCL fall time  | 100 kHz mode | -          | 300  | ns    |                                                  |

|                  |         |                        | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from<br>10 to 400 pF       |

| 90               | TSU:STA | START condition        | 100 kHz mode | 4.7        | —    | μs    | Only relevant for repeated                       |

|                  |         | setup time             | 400 kHz mode | 0.6        | —    | μs    | START condition                                  |

| 91               | THD:STA | START condition hold   | 100 kHz mode | 4.0        | —    | μs    | After this period the first clock                |

|                  |         | time                   | 400 kHz mode | 0.6        | —    | μs    | pulse is generated                               |

| 106              | THD:DAT | Data input hold time   | 100 kHz mode | 0          | —    | ns    |                                                  |

|                  |         |                        | 400 kHz mode | 0          | 0.9  | μs    |                                                  |

| 107              | TSU:DAT | Data input setup time  | 100 kHz mode | 250        | —    | ns    | Note 2                                           |

|                  |         |                        | 400 kHz mode | 100        | —    | ns    |                                                  |

| 92               | TSU:STO | STOP condition setup   | 100 kHz mode | 4.7        | —    | μs    |                                                  |

|                  |         | time                   | 400 kHz mode | 0.6        | —    | μs    |                                                  |

| 109              | ΤΑΑ     | Output valid from      | 100 kHz mode | _          | 3500 | ns    | Note 1                                           |

|                  |         | clock                  | 400 kHz mode | _          | —    | ns    |                                                  |

| 110              | TBUF    | Bus free time          | 100 kHz mode | 4.7        | —    | μs    | Time the bus must be free                        |

|                  |         |                        | 400 kHz mode | 1.3        | —    | μs    | before a new transmission can start              |

|                  | Cb      | Bus capacitive loading |              |            | 400  | pF    |                                                  |

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

2: A fast-mode (400 kHz) I<sup>2</sup>C-bus device can be used in a standard-mode (100 kHz) I<sup>2</sup>C-bus system, but the requirement tsu;DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+tsu;DAT = 1000 + 250 = 1250 ns (according to the standard-mode I<sup>2</sup>C bus specification) before the SCL line is released.

# PIC16C7X

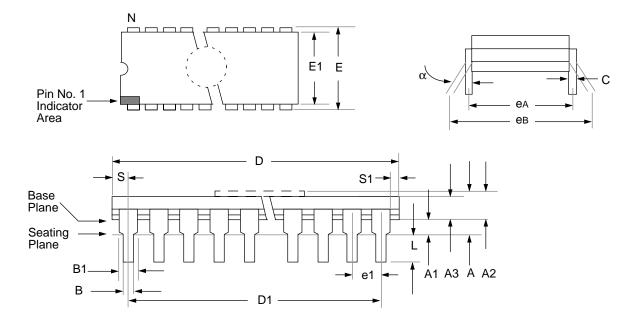

## 22.2 40-Lead Ceramic CERDIP Dual In-line with Window (600 mil) (JW)

|        | Pa     | ckage Group: ( | Ceramic CERDIP | Dual In-Line (C | DP)    |           |

|--------|--------|----------------|----------------|-----------------|--------|-----------|

|        |        | Millimeters    |                |                 | Inches |           |

| Symbol | Min    | Max            | Notes          | Min             | Max    | Notes     |

| α      | 0°     | 10°            |                | 0°              | 10°    |           |

| А      | 4.318  | 5.715          |                | 0.170           | 0.225  |           |

| A1     | 0.381  | 1.778          |                | 0.015           | 0.070  |           |

| A2     | 3.810  | 4.699          |                | 0.150           | 0.185  |           |

| A3     | 3.810  | 4.445          |                | 0.150           | 0.175  |           |

| В      | 0.355  | 0.585          |                | 0.014           | 0.023  |           |

| B1     | 1.270  | 1.651          | Typical        | 0.050           | 0.065  | Typical   |

| С      | 0.203  | 0.381          | Typical        | 0.008           | 0.015  | Typical   |

| D      | 51.435 | 52.705         |                | 2.025           | 2.075  |           |

| D1     | 48.260 | 48.260         | Reference      | 1.900           | 1.900  | Reference |

| E      | 15.240 | 15.875         |                | 0.600           | 0.625  |           |

| E1     | 12.954 | 15.240         |                | 0.510           | 0.600  |           |

| e1     | 2.540  | 2.540          | Reference      | 0.100           | 0.100  | Reference |

| eA     | 14.986 | 16.002         | Typical        | 0.590           | 0.630  | Typical   |

| eB     | 15.240 | 18.034         |                | 0.600           | 0.710  |           |

| L      | 3.175  | 3.810          |                | 0.125           | 0.150  |           |

| Ν      | 40     | 40             |                | 40              | 40     |           |

| S      | 1.016  | 2.286          |                | 0.040           | 0.090  |           |

| S1     | 0.381  | 1.778          |                | 0.015           | 0.070  |           |

## APPENDIX C: WHAT'S NEW

Added the following devices:

- PIC16C76

- PIC16C77

Removed the PIC16C710, PIC16C71, PIC16C711 from this datasheet.

Added PIC16C76 and PIC16C77 devices. The PIC16C76/77 devices have 368 bytes of data memory distributed in 4 banks and 8K of program memory in 4 pages. These two devices have an enhanced SPI that supports both clock phase and polarity. The USART has been enhanced.

When upgrading to the PIC16C76/77 please note that the upper 16 bytes of data memory in banks 1,2, and 3 are mapped into bank 0. This may require relocation of data memory usage in the user application code.

Added Q-cycle definitions to the Instruction Set Summary section.

## **APPENDIX D: WHAT'S CHANGED**

Minor changes, spelling and grammatical changes.

Added the following note to the USART section. This note applies to all devices except the PIC16C76 and PIC16C77.

For the PIC16C73/73A/74/74A the asynchronous high speed mode (BRGH = 1) may experience a high rate of receive errors. It is recommended that BRGH = 0. If you desire a higher baud rate than BRGH = 0 can support, refer to the device errata for additional information or use the PIC16C76/77.

Divided SPI section into SPI for the PIC16C76/77 and SPI for all other devices.

# PIC16C7X

| Registers                                                          |

|--------------------------------------------------------------------|

| FSR 20                                                             |

| Summary29<br>INDF                                                  |

| Summary                                                            |

| INTCON                                                             |

| Summary29<br>Maps                                                  |

| PIC16C7221                                                         |

| PIC16C73                                                           |

| PIC16C73A                                                          |

| PIC16C74                                                           |

| PIC16C76                                                           |

| PIC16C77                                                           |

| OPTION                                                             |

| Summary                                                            |

| PCL<br>Summary29                                                   |

| PCLATH                                                             |

| Summary                                                            |

| PORTB                                                              |

| Summary                                                            |

| Reset Conditions136<br>SSPBUF                                      |

| SCROF<br>Section                                                   |

| SSPCON                                                             |

| Diagram79                                                          |

| SSPSR                                                              |

| Section                                                            |

| SSPSTAT                                                            |

| Section                                                            |

| STATUS                                                             |

| Summary29                                                          |

| Summary                                                            |

| TMR0<br>Summary29                                                  |

| TRISB                                                              |

| Summary                                                            |

| Reset 129, 133                                                     |

| Reset Conditions for Special Registers                             |

| RP0 bit20, 30<br>RP1 bit                                           |

| RP1 bit                                                            |

| RX9D bit                                                           |

| S                                                                  |

| S                                                                  |

| SCK                                                                |

| SCL                                                                |

| SDI                                                                |

| SDO                                                                |

| Serial Communication Interface (SCI) Module, See USART<br>Services |

| One-Time-Programmable (OTP)7                                       |

| Quick-Turnaround-Production (QTP)7                                 |

| Serialized Quick-Turnaround Production (SQTP)7                     |

| Slave Mode                                                         |

| SCL                                                                |

| SLEEP                                                              |

| SMP                                                                |

| Software Simulator (MPSIM) 165                                     |

| SPBRG                                                              |

| SPBRG Register                                                                                                                                         | 26 28                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|                                                                                                                                                        |                      |

| Special Event Trigger                                                                                                                                  |                      |

| Special Features of the CPU                                                                                                                            | 129                  |

| Special Function Registers                                                                                                                             |                      |

| PIC16C72                                                                                                                                               | 23                   |

| PIC16C73                                                                                                                                               | 25. 27               |

| PIC16C73A                                                                                                                                              | 25 27                |

| PIC16C74                                                                                                                                               |                      |

|                                                                                                                                                        |                      |