Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 33                                                                           |

| Program Memory Size        | 7KB (4K x 14)                                                                |

| Program Memory Type        | ОТР                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 192 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                    |

| Data Converters            | A/D 5x8b                                                                     |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-QFP                                                                       |

| Supplier Device Package    | 44-MQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc74at-04i-pq |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0 General Description                                              | 5     |

|----------------------------------------------------------------------|-------|

| 2.0 PIC16C7X Device Varieties                                        | 7     |

| 3.0 Architectural Overview                                           | 9     |

| 4.0 Memory Organization                                              | 19    |

| 5.0 I/O Ports                                                        | 43    |

| 6.0 Overview of Timer Modules                                        | 57    |

| 7.0 Timer0 Module                                                    | 59    |

| 8.0 Timer1 Module                                                    | 65    |

| 9.0 Timer2 Module                                                    | 69    |

| 10.0 Capture/Compare/PWM Module(s)                                   |       |

| 11.0 Synchronous Serial Port (SSP) Module                            |       |

| 12.0 Universal Synchronous Asynchronous Receiver Transmitter (USART) | 99    |

| 13.0 Analog-to-Digital Converter (A/D) Module                        | . 117 |

| 14.0 Special Features of the CPU                                     |       |

| 15.0 Instruction Set Summary                                         | . 147 |

| 16.0 Development Support                                             |       |

| 17.0 Electrical Characteristics for PIC16C72                         |       |

| 18.0 Electrical Characteristics for PIC16C73/74                      |       |

| 19.0 Electrical Characteristics for PIC16C73A/74A                    |       |

| 20.0 Electrical Characteristics for PIC16C76/77                      | . 219 |

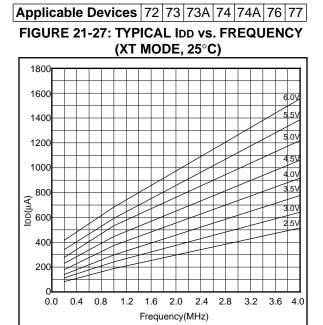

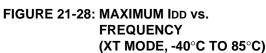

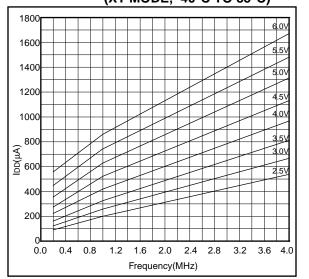

| 21.0 DC and AC Characteristics Graphs and Tables                     |       |

| 22.0 Packaging Information                                           | . 251 |

| Appendix A:                                                          |       |

| Appendix B: Compatibility                                            | . 263 |

| Appendix C: What's New                                               | . 264 |

| Appendix D: What's Changed                                           |       |

| Appendix E: PIC16/17 Microcontrollers                                | . 265 |

| Pin Compatibility                                                    |       |

| Index                                                                | . 273 |

| List of Examples                                                     | . 279 |

| List of Figures                                                      |       |

| List of Tables                                                       |       |

| Reader Response                                                      |       |

| PIC16C7X Product Identification System                               | . 287 |

For register and module descriptions in this data sheet, device legends show which devices apply to those sections. As an example, the legend below would mean that the following section applies only to the PIC16C72, PIC16C73A and PIC16C74A devices.

# Applicable Devices 72 73 73A 74 74A 76 77

12|13|13A|14|14A|16|11

# To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent an exceptional amount of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

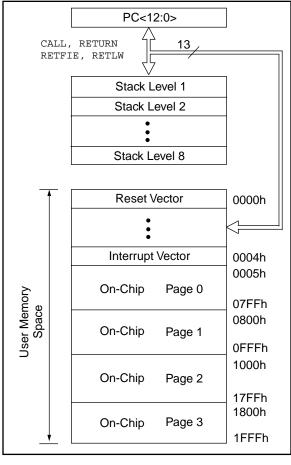

#### FIGURE 4-3: PIC16C76/77 PROGRAM MEMORY MAP AND STACK

### 4.2 Data Memory Organization

Applicable Devices

72

73

73

74

74

76

77

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

RP1:RP0 (STATUS<6:5>)

- = 00  $\rightarrow$  Bank0

- = 01  $\rightarrow$  Bank1

- =  $10 \rightarrow \text{Bank2}$

- = 11  $\rightarrow$  Bank3

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain special function registers. Some "high use" special function registers from one bank may be mirrored in another bank for code reduction and quicker access.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR (Section 4.5).

# FIGURE 4-13: PIR1 REGISTER PIC16C73/73A/74/74A/76/77 (ADDRESS 0Ch)

| 0<br>(1)                                             | R/W-0<br>ADIF                                                                                                                                                                                                                                                                                                                                                                                                |                        | R-0<br>RCIF                      |               | R-0<br>TXIF | R/W      |       |            | R/W-0<br>CCP1IF |    | 1        | 2/W-0<br>//R2IF |      | R/W<br>TMR | -      | D      |      | Read                  | doblo                      | hit           |                  |                                                                                   |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------|---------------|-------------|----------|-------|------------|-----------------|----|----------|-----------------|------|------------|--------|--------|------|-----------------------|----------------------------|---------------|------------------|-----------------------------------------------------------------------------------|

|                                                      | ADI                                                                                                                                                                                                                                                                                                                                                                                                          |                        | Keir                             |               |             | 001      |       |            |                 |    | <u> </u> | /11/211         |      |            | bit0   | W<br>U | / =  | Writa<br>Unim<br>read | able b<br>nplen<br>  as '( | oit<br>nenteo |                  |                                                                                   |

| 1                                                    | = A re                                                                                                                                                                                                                                                                                                                                                                                                       | ad                     | arallel<br>or a wr<br>d or wri   | ite o         | peratic     | n has    |       |            |                 |    |          |                 | eare | ed in      | soft   | war    | e)   |                       |                            |               |                  |                                                                                   |

| 1                                                    | ADIF: A/D Converter Interrupt Flag bit<br>1 = An A/D conversion completed (must be cleared in software)<br>0 = The A/D conversion is not complete                                                                                                                                                                                                                                                            |                        |                                  |               |             |          |       |            |                 |    |          |                 |      |            |        |        |      |                       |                            |               |                  |                                                                                   |

| 1                                                    | <b>RCIF</b> : USART Receive Interrupt Flag bit<br>1 = The USART receive buffer is full (cleared by reading RCREG)<br>0 = The USART receive buffer is empty                                                                                                                                                                                                                                                   |                        |                                  |               |             |          |       |            |                 |    |          |                 |      |            |        |        |      |                       |                            |               |                  |                                                                                   |

| 1                                                    | <b>TXIF</b> : USART Transmit Interrupt Flag bit<br>1 = The USART transmit buffer is empty (cleared by writing to TXREG)<br>0 = The USART transmit buffer is full                                                                                                                                                                                                                                             |                        |                                  |               |             |          |       |            |                 |    |          |                 |      |            |        |        |      |                       |                            |               |                  |                                                                                   |

| 1                                                    | <b>SSPIF</b> : Synchronous Serial Port Interrupt Flag bit<br>1 = The transmission/reception is complete (must be cleared in software)<br>0 = Waiting to transmit/receive                                                                                                                                                                                                                                     |                        |                                  |               |             |          |       |            |                 |    |          |                 |      |            |        |        |      |                       |                            |               |                  |                                                                                   |

| <u>C</u><br>1<br>0<br><u>C</u><br>1<br>0<br><u>P</u> | 0 = Waiting to transmit/receive<br><b>CCP1IF</b> : CCP1 Interrupt Flag bit<br><u>Capture Mode</u><br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred<br><u>Compare Mode</u><br>1 = A TMR1 register compare match occurred (must be cleared in software)<br>0 = No TMR1 register compare match occurred<br><u>PWM Mode</u><br>Unused in this mode |                        |                                  |               |             |          |       |            |                 |    |          |                 |      |            |        |        |      |                       |                            |               |                  |                                                                                   |

| 1                                                    | <b>TMR2IF</b> : TMR2 to PR2 Match Interrupt Flag bit<br>1 = TMR2 to PR2 match occurred (must be cleared in software)<br>0 = No TMR2 to PR2 match occurred                                                                                                                                                                                                                                                    |                        |                                  |               |             |          |       |            |                 |    |          |                 |      |            |        |        |      |                       |                            |               |                  |                                                                                   |

| 1                                                    | <b>TMR1IF</b> : TMR1 Overflow Interrupt Flag bit<br>1 = TMR1 register overflowed (must be cleared in software)<br>0 = TMR1 register did not overflow                                                                                                                                                                                                                                                         |                        |                                  |               |             |          |       |            |                 |    |          |                 |      |            |        |        |      |                       |                            |               |                  |                                                                                   |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                              |                        | 73A/76<br>evices,                |               |             |          |       |            |                 | S  | lav      | e Port          | im   | plen       | nente  | ed,    | this | s bit l               | ocat                       | ion is        | rese             | rved                                                                              |

| o<br>errupt<br>pal er                                | on thes                                                                                                                                                                                                                                                                                                                                                                                                      | e de<br>ts ge<br>it, G | evices,<br>et set wh<br>IE (INT) | alwa<br>nen a | ays mai     | intain t | his l | bit<br>n o | clear.          | ga | ardle    | ess of t        | he   | state      | of its | cor    | rre  | es                    | espondi                    | esponding e   | esponding enable | is bit location is rese<br>esponding enable bit or<br>lag bits are clear prior to |

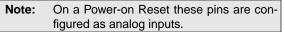

# 5.5 PORTE and TRISE Register Applicable Devices 72/73/73A/74/74A/76/77

PORTE has three pins RE0/RD/AN5, RE1/WR/AN6 and RE2/CS/AN7, which are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers.

I/O PORTE becomes control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs) and that register ADCON1 is configured for digital I/O. In this mode the input buffers are TTL.

Figure 5-9 shows the TRISE register, which also controls the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. The operation of these pins is selected by control bits in the ADCON1 register. When selected as an analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

# FIGURE 5-8: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

#### FIGURE 5-9: TRISE REGISTER (ADDRESS 89h)

| 5.0         | <b>D</b> 0                                                                                                                                                                                                                       | D AAA A     | <b>D</b> 444 a    |             |       | <b>D</b> 444 4 | <b>D</b> 444 4 |                                                                                                                                                  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|-------------|-------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| R-0         | R-0                                                                                                                                                                                                                              | R/W-0       | R/W-0             | U-0         | R/W-1 | R/W-1          | R/W-1          |                                                                                                                                                  |  |  |

| IBF<br>bit7 | OBF                                                                                                                                                                                                                              | IBOV        | PSPMODE           | _           | bit2  | bit1           | bit0<br>bit0   | <ul> <li>R = Readable bit</li> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>- n = Value at POR reset</li> </ul> |  |  |

| bit 7 :     |                                                                                                                                                                                                                                  |             |                   |             |       |                |                |                                                                                                                                                  |  |  |

| bit 6:      | <ul> <li>6: <b>OBF</b>: Output Buffer Full Status bit</li> <li>1 = The output buffer still holds a previously written word</li> <li>0 = The output buffer has been read</li> </ul>                                               |             |                   |             |       |                |                |                                                                                                                                                  |  |  |

| bit 5:      | <ul> <li>IBOV: Input Buffer Overflow Detect bit (in microprocessor mode)</li> <li>1 = A write occurred when a previously input word has not been read (must be cleared in software)</li> <li>0 = No overflow occurred</li> </ul> |             |                   |             |       |                |                |                                                                                                                                                  |  |  |

| bit 4:      | PSPMODE<br>1 = Paralle<br>0 = Genera                                                                                                                                                                                             | I slave por |                   | de Select b | bit   |                |                |                                                                                                                                                  |  |  |

| bit 3:      | Unimplem                                                                                                                                                                                                                         | ented: Re   | ad as '0'         |             |       |                |                |                                                                                                                                                  |  |  |

| bit 2:      | PORTE Data Direction Bits<br>Bit2: Direction Control bit for pin RE2/CS/AN7<br>1 = Input<br>0 = Output                                                                                                                           |             |                   |             |       |                |                |                                                                                                                                                  |  |  |

| bit 1:      | Bit1: Direction Control bit for pin RE1/WR/AN6<br>1 = Input<br>0 = Output                                                                                                                                                        |             |                   |             |       |                |                |                                                                                                                                                  |  |  |

| bit 0:      | <b>Bit0</b> : Direc<br>1 = Input<br>0 = Output                                                                                                                                                                                   |             | ol bit for pin RI | E0/RD/AN    | 5     |                |                |                                                                                                                                                  |  |  |

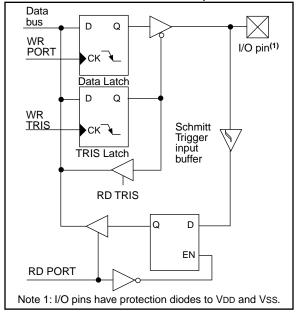

# 7.3 <u>Prescaler</u> Applicable Devices 72|73|73A|74|74A|76|77

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The PSA and PS2:PS0 bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

**Note:** Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

### FIGURE 7-6: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

NOTES:

#### FIGURE 10-1: CCP1CON REGISTER (ADDRESS 17h)/CCP2CON REGISTER (ADDRESS 1Dh)

| U-0      | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0    | R/W-0     | R/W-0  | R/W-0  | R/W-0  | R/W-0  |                                                                                      |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|--------|--------|--------|--------|--------------------------------------------------------------------------------------|--|--|

|          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CCPxX    | CCPxY     | CCPxM3 | CCPxM2 | CCPxM1 | CCPxM0 | R = Readable bit                                                                     |  |  |

| bit7     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |           |        |        |        | bit0   | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset |  |  |

| bit 7-6: | Unim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | plemente | d: Read a | s '0'  |        |        |        |                                                                                      |  |  |

| bit 5-4: | <b>CCPxX:CCPxY</b> : PWM Least Significant bits<br>Capture Mode: Unused<br>Compare Mode: Unused<br>PWM Mode: These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |           |        |        |        |        |                                                                                      |  |  |

| bit 3-0: | PWM Mode: These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL. CCPxM3:CCPxM0: CCPx Mode Select bits 0000 = Capture/Compare/PWM off (resets CCPx module) 0100 = Capture mode, every falling edge 0101 = Capture mode, every falling edge 0110 = Capture mode, every 4th rising edge 0111 = Capture mode, every 16th rising edge 1000 = Compare mode, set output on match (CCPxIF bit is set) 1001 = Compare mode, clear output on match (CCPxIF bit is set) 1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set, CCPx pin is unaffected) 1011 = Compare mode, trigger special event (CCPxIF bit is set; CCP1 resets TMR1; CCP2 resets TMR1 and starts an A/D conversion (if A/D module is enabled)) 11xx = PWM mode |          |           |        |        |        |        |                                                                                      |  |  |

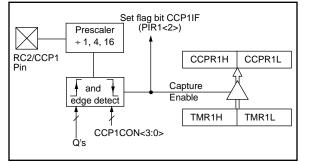

# 10.1 <u>Capture Mode</u>

Applicable Devices

72 73 73A 74 74A 76 77

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as:

- · Every falling edge

- · Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 10.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 is configured as an out-     |

|-------|----------------------------------------------|

|       | put, a write to the port can cause a capture |

|       | condition.                                   |

#### FIGURE 10-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 10.1.2 TIMER1 MODE SELECTION

Timer1 must be running in timer mode or synchronized counter mode for the CCP module to use the capture feature. In asynchronous counter mode, the capture operation may not work.

#### 10.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in operating mode.

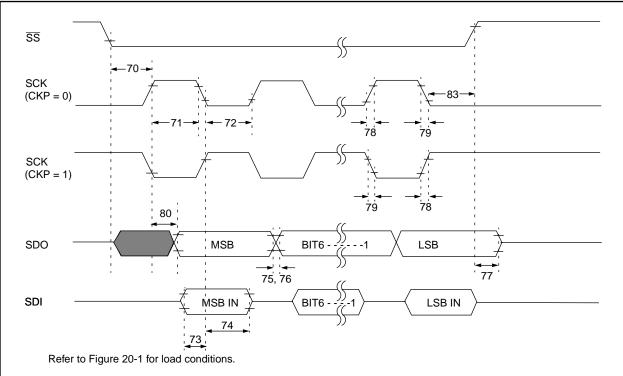

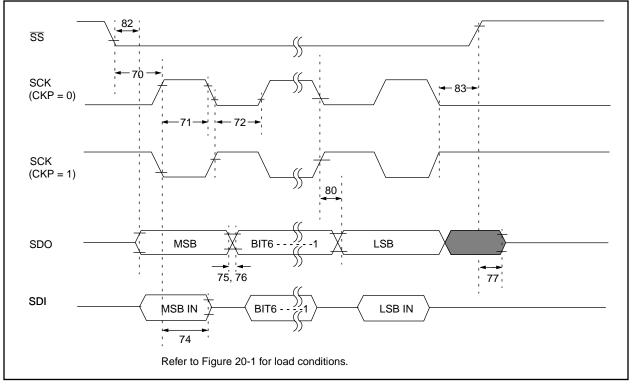

#### 11.3 SPI Mode for PIC16C76/77

Γ

This section contains register definitions and operational characteristics of the SPI module on the PIC16C76 and PIC16C77 only.

#### FIGURE 11-7: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h)(PIC16C76/77)

| R/W-0  | R/W-0                                                                                                                                                                                                                                                                                                                                               | R-0                     | R-0                          | R-0                                                    | R-0          | R-0          | R-0         |                                                                                      |  |  |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------|--------------------------------------------------------|--------------|--------------|-------------|--------------------------------------------------------------------------------------|--|--|--|

| SMP    | CKE                                                                                                                                                                                                                                                                                                                                                 | D/Ā                     | Р                            | S                                                      | R/W          | UA           | BF          | R = Readable bit                                                                     |  |  |  |

| bit7   |                                                                                                                                                                                                                                                                                                                                                     |                         |                              |                                                        |              |              | bit0        | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset |  |  |  |

| bit 7: | SMP: SPI data input sample phase         SPI Master Mode         1 = Input data sampled at end of data output time         0 = Input data sampled at middle of data output time         SPI Slave Mode         SMP must be cleared when SPI is used in slave mode         CKE: SPI Clask Edge Calent (Figure 44.44, Figure 44.42, and Figure 44.42) |                         |                              |                                                        |              |              |             |                                                                                      |  |  |  |

| bit 6: | <b>CKE</b> : SPI Clock Edge Select (Figure 11-11, Figure 11-12, and Figure 11-13)<br>$\frac{CKP = 0}{1 = \text{Data transmitted on rising edge of SCK}}$ $0 = \text{Data transmitted on falling edge of SCK}$ $\frac{CKP = 1}{1 = \text{Data transmitted on falling edge of SCK}}$ $0 = \text{Data transmitted on falling edge of SCK}$             |                         |                              |                                                        |              |              |             |                                                                                      |  |  |  |

| bit 5: | <ul> <li>D/A: Data/Address bit (I<sup>2</sup>C mode only)</li> <li>1 = Indicates that the last byte received or transmitted was data</li> <li>0 = Indicates that the last byte received or transmitted was address</li> </ul>                                                                                                                       |                         |                              |                                                        |              |              |             |                                                                                      |  |  |  |

| bit 4: | detecte<br>1 = Indi                                                                                                                                                                                                                                                                                                                                 | d last, SS<br>cates tha | SPEN is cl                   | eared)<br>t has been                                   | cleared whe  |              |             | lisabled, or when the Start bit is                                                   |  |  |  |

| bit 3: | detecte<br>1 = Indi                                                                                                                                                                                                                                                                                                                                 | d last, SS<br>cates tha | SPEN is clo<br>it a start bi | eared)<br>t has been                                   | cleared whe  |              |             | lisabled, or when the Stop bit is                                                    |  |  |  |

| bit 2: | <ul> <li>0 = Start bit was not detected last</li> <li>R/W: Read/Write bit information (I<sup>2</sup>C mode only)</li> <li>This bit holds the R/W bit information following the last address match. This bit is only valid from the address match to the next start bit, stop bit, or ACK bit.</li> <li>1 = Read</li> <li>0 = Write</li> </ul>       |                         |                              |                                                        |              |              |             |                                                                                      |  |  |  |

| bit 1: | 1 = Indi                                                                                                                                                                                                                                                                                                                                            | cates tha               | t the user                   | it I <sup>2</sup> C mode<br>needs to u<br>I to be upda | pdate the ad | dress in the | e SSPADD re | egister                                                                              |  |  |  |

| bit 0: | BF: Buf                                                                                                                                                                                                                                                                                                                                             | fer Full S              | tatus bit                    |                                                        |              |              |             |                                                                                      |  |  |  |

|        | <u>Receive</u> (SPI and I <sup>2</sup> C modes)<br>1 = Receive complete, SSPBUF is full<br>0 = Receive not complete, SSPBUF is empty                                                                                                                                                                                                                |                         |                              |                                                        |              |              |             |                                                                                      |  |  |  |

|        | 1 = Trar                                                                                                                                                                                                                                                                                                                                            |                         | rogress, S                   | SPBUF is t<br>PBUF is en                               |              |              |             |                                                                                      |  |  |  |

#### 12.4 USART Synchronous Slave Mode

# Applicable Devices 72 73 73A 74 74A 76 77

Synchronous slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 12.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the synchronous master and slave modes are identical except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

#### 12.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the synchronous master and slave modes is identical except in the case of the SLEEP mode. Also, bit SREN is a don't care in slave mode.

If receive is enabled, by setting bit CREN, prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Reception:

- 1. Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, then set enable bit RCIE.

- 3. If 9-bit reception is desired, then set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- 6. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

#### TABLE 15-2: PIC16CXX INSTRUCTION SET

| Mnemonic,  |        | Description                  | Cycles |       | 14-Bit | Opcode | 9        | Status   | Notes |

|------------|--------|------------------------------|--------|-------|--------|--------|----------|----------|-------|

| Operands   |        |                              |        | MSb   | I      |        | LSb      | Affected |       |

| BYTE-ORIE  | NTED   | FILE REGISTER OPERATIONS     |        |       |        |        |          |          |       |

| ADDWF      | f, d   | Add W and f                  | 1      | 00    | 0111   | dfff   | ffff     | C,DC,Z   | 1,2   |

| ANDWF      | f, d   | AND W with f                 | 1      | 00    | 0101   | dfff   | ffff     | Z        | 1,2   |

| CLRF       | f      | Clear f                      | 1      | 00    | 0001   | lfff   | ffff     | Z        | 2     |

| CLRW       | -      | Clear W                      | 1      | 00    | 0001   | 0xxx   | xxxx     | Z        |       |

| COMF       | f, d   | Complement f                 | 1      | 00    | 1001   | dfff   | ffff     | Z        | 1,2   |

| DECF       | f, d   | Decrement f                  | 1      | 00    | 0011   | dfff   | ffff     | Z        | 1,2   |

| DECFSZ     | f, d   | Decrement f, Skip if 0       | 1(2)   | 00    | 1011   | dfff   | ffff     |          | 1,2,3 |

| INCF       | f, d   | Increment f                  | 1      | 00    | 1010   | dfff   | ffff     | Z        | 1,2   |

| INCFSZ     | f, d   | Increment f, Skip if 0       | 1(2)   | 00    | 1111   | dfff   | ffff     |          | 1,2,3 |

| IORWF      | f, d   | Inclusive OR W with f        | 1      | 00    | 0100   | dfff   | ffff     | Z        | 1,2   |

| MOVF       | f, d   | Move f                       | 1      | 00    | 1000   | dfff   | ffff     | Z        | 1,2   |

| MOVWF      | f      | Move W to f                  | 1      | 00    | 0000   | lfff   | ffff     |          |       |

| NOP        | -      | No Operation                 | 1      | 00    | 0000   | 0xx0   | 0000     |          |       |

| RLF        | f, d   | Rotate Left f through Carry  | 1      | 00    | 1101   | dfff   | ffff     | С        | 1,2   |

| RRF        | f, d   | Rotate Right f through Carry | 1      | 00    | 1100   | dfff   | ffff     | С        | 1,2   |

| SUBWF      | f, d   | Subtract W from f            | 1      | 00    | 0010   | dfff   | ffff     | C,DC,Z   | 1,2   |

| SWAPF      | f, d   | Swap nibbles in f            | 1      | 00    | 1110   | dfff   | ffff     |          | 1,2   |

| XORWF      | f, d   | Exclusive OR W with f        | 1      | 00    | 0110   | dfff   | ffff     | Z        | 1,2   |

| BIT-ORIENT | ED FIL | E REGISTER OPERATIONS        |        |       |        |        |          | _        |       |

| BCF        | f, b   | Bit Clear f                  | 1      | 01    | 00bb   | bfff   | ffff     |          | 1,2   |

| BSF        | f, b   | Bit Set f                    | 1      | 01    | 01bb   | bfff   | ffff     |          | 1,2   |

| BTFSC      | f, b   | Bit Test f, Skip if Clear    | 1 (2)  | 01    | 10bb   | bfff   | ffff     |          | 3     |

| BTFSS      | f, b   | Bit Test f, Skip if Set      | 1 (2)  | 01    | 11bb   | bfff   | ffff     |          | 3     |

| LITERAL AI | ND CO  | NTROL OPERATIONS             |        |       |        |        |          |          |       |

| ADDLW      | k      | Add literal and W            | 1      | 11    | 111x   | kkkk   | kkkk     | C,DC,Z   |       |

| ANDLW      | k      | AND literal with W           | 1      | 11    | 1001   | kkkk   | kkkk     | Z        |       |

| CALL       | k      | Call subroutine              | 2      | 10    | 0kkk   | kkkk   | kkkk     |          |       |

| CLRWDT     | -      | Clear Watchdog Timer         | 1      | 00    | 0000   | 0110   | 0100     | TO,PD    |       |

| GOTO       | k      | Go to address                | 2      | 10    | 1kkk   | kkkk   | kkkk     |          |       |

| IORLW      | k      | Inclusive OR literal with W  | 1      | 11    | 1000   | kkkk   | kkkk     | Z        |       |

| MOVLW      | k      | Move literal to W            | 1      | 11    | 00xx   | kkkk   | kkkk     |          |       |

| RETFIE     | -      | Return from interrupt        | 2      | 00    | 0000   | 0000   | 1001     |          |       |

| RETLW      | k      | Return with literal in W     | 2      | 11    | 01xx   | kkkk   | kkkk     |          |       |

| RETURN     | -      | Return from Subroutine       | 2      | 00    | 0000   | 0000   | 1000     |          |       |

| SLEEP      | -      | Go into standby mode         | 1      | 00    | 0000   | 0110   | 0011     | TO, PD   |       |

|            |        | Subtract W from literal      | 1      | 11    | 110x   | kkkk   | 1-1-1-1- | C,DC,Z   |       |

| SUBLW      | k      |                              |        | L T T | TTOX   | KKKK   | кккк     | 0,DC,Z   |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| RETLW             | Return with Literal in W                                                                                                    |                           |                                     |                                      |  | RETURN                                                                                                    | Return f         | Return from Subroutine |                  |                       |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------------------|--------------------------------------|--|-----------------------------------------------------------------------------------------------------------|------------------|------------------------|------------------|-----------------------|--|--|--|

| Syntax:           | [ label ]                                                                                                                   | RETLW                     | k                                   |                                      |  | Syntax:                                                                                                   | [ label ]        | RETUR                  | N                |                       |  |  |  |

| Operands:         | $0 \le k \le 2$                                                                                                             | 55                        |                                     |                                      |  | Operands:                                                                                                 | None             |                        |                  |                       |  |  |  |

| Operation:        | $k \rightarrow (W);$                                                                                                        |                           |                                     |                                      |  | Operation:                                                                                                | $TOS \to PC$     |                        |                  |                       |  |  |  |

|                   | $TOS \to F$                                                                                                                 | $TOS \to PC$              |                                     |                                      |  | Status Affected:                                                                                          | None             | None                   |                  |                       |  |  |  |

| Status Affected:  | None                                                                                                                        |                           |                                     |                                      |  | Encoding:                                                                                                 | 00               | 0000                   | 0000             | 1000                  |  |  |  |

| Encoding:         | 11                                                                                                                          | 01xx                      | kkkk                                | kkkk                                 |  | Description:                                                                                              | Return fro       | m subrout              | ine. The st      | ack is                |  |  |  |

| Description:      | The W register is loaded with the eight<br>bit literal 'k'. The program counter is<br>loaded from the top of the stack (the |                           |                                     |                                      |  | POPed and the top of the stack (TOS) is loaded into the program counter. This is a two cycle instruction. |                  |                        |                  |                       |  |  |  |

|                   | return address). This is a two cycle<br>instruction.                                                                        |                           |                                     |                                      |  | Words:                                                                                                    | 1                |                        |                  |                       |  |  |  |

| Words:            | 1                                                                                                                           |                           |                                     |                                      |  | Cycles:                                                                                                   | 2                |                        |                  |                       |  |  |  |

| Cycles:           | 2                                                                                                                           |                           |                                     |                                      |  | Q Cycle Activity:                                                                                         | Q1               | Q2                     | Q3               | Q4                    |  |  |  |

| Q Cycle Activity: | 2<br>Q1                                                                                                                     | Q2                        | Q3                                  | Q4                                   |  | 1st Cycle                                                                                                 | Decode           | No-<br>Operation       | No-<br>Operation | Pop from<br>the Stack |  |  |  |

| 1st Cycle         | Decode                                                                                                                      | Read<br>literal 'k'       | No-<br>Operation                    | Write to W,<br>Pop from<br>the Stack |  | 2nd Cycle                                                                                                 | No-<br>Operation | No-<br>Operation       | No-<br>Operation | No-<br>Operation      |  |  |  |

| 2nd Cycle         | No-<br>Operation                                                                                                            | No-<br>Operation          | No-<br>Operation                    | No-<br>Operation                     |  | Example                                                                                                   | RETURN           |                        |                  |                       |  |  |  |

|                   | Operation                                                                                                                   | Operation                 | Operation                           | Operation                            |  |                                                                                                           | After Inte       | errupt                 |                  |                       |  |  |  |

| Example           | CALL TABL                                                                                                                   | ;offset                   | tains tabl<br>t value<br>7 has tabl |                                      |  |                                                                                                           |                  | PC =                   | TOS              |                       |  |  |  |

| TABLE             | ADDWF PC<br>RETLW k1<br>RETLW k2                                                                                            | ;W = off<br>;Begin t<br>; |                                     |                                      |  |                                                                                                           |                  |                        |                  |                       |  |  |  |

|                   | RETLW kn                                                                                                                    | ; End of                  | f table                             |                                      |  |                                                                                                           |                  |                        |                  |                       |  |  |  |

|                   | Before In                                                                                                                   |                           |                                     |                                      |  |                                                                                                           |                  |                        |                  |                       |  |  |  |

|                   |                                                                                                                             |                           | 0x07                                |                                      |  |                                                                                                           |                  |                        |                  |                       |  |  |  |

|                   | After Instruction<br>W = value of k8                                                                                        |                           |                                     |                                      |  |                                                                                                           |                  |                        |                  |                       |  |  |  |

| SUBWF             | Subtract W from f                                                                                                                                                                    |   |  |  |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|--|--|

| Syntax:           | [ <i>label</i> ] SUBWF f,d                                                                                                                                                           |   |  |  |  |  |  |  |

| Operands:         | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                   |   |  |  |  |  |  |  |

| Operation:        | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                |   |  |  |  |  |  |  |

| Status Affected:  | C, DC, Z                                                                                                                                                                             |   |  |  |  |  |  |  |

| Encoding:         | 00 0010 dfff ffff                                                                                                                                                                    |   |  |  |  |  |  |  |

| Description:      | Subtract (2's complement method) W reg-<br>ister from register 'f'. If 'd' is 0 the result is<br>stored in the W register. If 'd' is 1 the<br>result is stored back in register 'f'. |   |  |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                                    |   |  |  |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                                    |   |  |  |  |  |  |  |

| Q Cycle Activity: | Q1 Q2 Q3 Q4                                                                                                                                                                          |   |  |  |  |  |  |  |

|                   | Decode Read register 'f' Process Write to destination                                                                                                                                |   |  |  |  |  |  |  |

| Example 1:        | SUBWF REG1, I<br>Before Instruction<br>REG1 = 3                                                                                                                                      |   |  |  |  |  |  |  |

|                   | W = 2                                                                                                                                                                                |   |  |  |  |  |  |  |

|                   | C = ?<br>Z = ?                                                                                                                                                                       |   |  |  |  |  |  |  |

|                   | After Instruction                                                                                                                                                                    |   |  |  |  |  |  |  |

|                   | REG1 = 1<br>W = 2<br>C = 1; result is positive                                                                                                                                       |   |  |  |  |  |  |  |

|                   | Z = 0                                                                                                                                                                                |   |  |  |  |  |  |  |

| Example 2:        | Before Instruction                                                                                                                                                                   |   |  |  |  |  |  |  |

|                   | REG1 = 2<br>W = 2<br>C = ?<br>Z = ?                                                                                                                                                  |   |  |  |  |  |  |  |

|                   | After Instruction                                                                                                                                                                    |   |  |  |  |  |  |  |

|                   | REG1       =       0         W       =       2         C       =       1; result is zero         Z       =       1                                                                   |   |  |  |  |  |  |  |

| Example 3:        | Before Instruction                                                                                                                                                                   |   |  |  |  |  |  |  |

|                   | REG1 = 1<br>W = 2<br>C = ?<br>Z = ?                                                                                                                                                  |   |  |  |  |  |  |  |

|                   | After Instruction                                                                                                                                                                    |   |  |  |  |  |  |  |

|                   | $\begin{array}{rcl} REG1 &=& 0xFF \\ W &=& 2 \\ C &=& 0; \text{ result is negative} \\ Z &=& 0 \end{array}$                                                                          | • |  |  |  |  |  |  |

| SWAPF             | Swap Ni                                                                                                                                                               | bbles in             | f               |                      |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------|----------------------|--|--|--|--|--|

| Syntax:           | [label]                                                                                                                                                               | SWAPF                | i,d             |                      |  |  |  |  |  |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$                                                                                                                                        | 27                   |                 |                      |  |  |  |  |  |

| Operation:        | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                               |                      |                 |                      |  |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                  |                      |                 |                      |  |  |  |  |  |

| Encoding:         | 00                                                                                                                                                                    | 1110                 | dfff            | ffff                 |  |  |  |  |  |

| Description:      | The upper and lower nibbles of register<br>'f' are exchanged. If 'd' is 0 the result is<br>placed in W register. If 'd' is 1 the result<br>is placed in register 'f'. |                      |                 |                      |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                     |                      |                 |                      |  |  |  |  |  |

| Cycles:           | 1                                                                                                                                                                     |                      |                 |                      |  |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                    | Q2                   | Q3              | Q4                   |  |  |  |  |  |

|                   | Decode                                                                                                                                                                | Read<br>register 'f' | Process<br>data | Write to destination |  |  |  |  |  |

| Example           | SWAPF                                                                                                                                                                 | REG,                 | 0               |                      |  |  |  |  |  |

|                   | Before In                                                                                                                                                             | struction            |                 |                      |  |  |  |  |  |

|                   |                                                                                                                                                                       | REG1                 | = 0x            | A5                   |  |  |  |  |  |

|                   | After Inst                                                                                                                                                            | ruction              |                 |                      |  |  |  |  |  |

|                   |                                                                                                                                                                       | REG1<br>W            | •••             | :A5<br>:5A           |  |  |  |  |  |

| TRIS             | Load TRIS Register                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] TRIS f                                                                                                                                                             |  |  |  |  |  |  |  |  |

| Operands:        | $5 \le f \le 7$                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| Operation:       | (W) $\rightarrow$ TRIS register f;                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| Encoding:        | 00 0000 0110 0fff                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| Description:     | The instruction is supported for code<br>compatibility with the PIC16C5X prod-<br>ucts. Since TRIS registers are read-<br>able and writable, the user can directly<br>address them. |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| Example          |                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

|                  | To maintain upward compatibility<br>with future PIC16CXX products, do<br>not use this instruction.                                                                                  |  |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

# Applicable Devices 72 73 73A 74 74A 76 77

19.1 DC Characteristics: PIC16C73A/74A-04 (Commercial, Industrial, Extended) PIC16C73A/74A-10 (Commercial, Industrial, Extended) PIC16C73A/74A-20 (Commercial, Industrial, Extended)

| DC CHA                         |                                                                  | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq TA \leq +125^{\circ}$ C for extended, $-40^{\circ}$ C $\leq TA \leq +85^{\circ}$ C for industrial and $0^{\circ}$ C $\leq TA \leq +70^{\circ}$ C for commercial |                  |                           |                      |                      |                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------|----------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|