Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 33                                                                           |

| Program Memory Size        | 7KB (4K x 14)                                                                |

| Program Memory Type        | ОТР                                                                          |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 192 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                    |

| Data Converters            | A/D 5x8b                                                                     |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-TQFP                                                                      |

| Supplier Device Package    | 44-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc74at-04i-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0 General Description                                              | 5     |  |  |  |  |  |  |

|----------------------------------------------------------------------|-------|--|--|--|--|--|--|

| 2.0 PIC16C7X Device Varieties                                        | 7     |  |  |  |  |  |  |

| 3.0 Architectural Overview                                           | 9     |  |  |  |  |  |  |

| 4.0 Memory Organization                                              | 19    |  |  |  |  |  |  |

| 5.0 I/O Ports                                                        | 43    |  |  |  |  |  |  |

| 6.0 Overview of Timer Modules                                        | 57    |  |  |  |  |  |  |

| 7.0 Timer0 Module                                                    | 59    |  |  |  |  |  |  |

| 8.0 Timer1 Module                                                    | 65    |  |  |  |  |  |  |

| 9.0 Timer2 Module                                                    | 69    |  |  |  |  |  |  |

| 10.0 Capture/Compare/PWM Module(s)                                   |       |  |  |  |  |  |  |

| 11.0 Synchronous Serial Port (SSP) Module                            |       |  |  |  |  |  |  |

| 12.0 Universal Synchronous Asynchronous Receiver Transmitter (USART) | 99    |  |  |  |  |  |  |

| 13.0 Analog-to-Digital Converter (A/D) Module                        | . 117 |  |  |  |  |  |  |

| 14.0 Special Features of the CPU                                     |       |  |  |  |  |  |  |

| 15.0 Instruction Set Summary                                         | . 147 |  |  |  |  |  |  |

| 16.0 Development Support                                             |       |  |  |  |  |  |  |

| 17.0 Electrical Characteristics for PIC16C72                         |       |  |  |  |  |  |  |

| 18.0 Electrical Characteristics for PIC16C73/74                      |       |  |  |  |  |  |  |

| 19.0 Electrical Characteristics for PIC16C73A/74A                    |       |  |  |  |  |  |  |

| 20.0 Electrical Characteristics for PIC16C76/77                      | . 219 |  |  |  |  |  |  |

| 21.0 DC and AC Characteristics Graphs and Tables                     |       |  |  |  |  |  |  |

| 22.0 Packaging Information                                           | . 251 |  |  |  |  |  |  |

| Appendix A:                                                          |       |  |  |  |  |  |  |

| Appendix B: Compatibility                                            | . 263 |  |  |  |  |  |  |

| Appendix C: What's New                                               | . 264 |  |  |  |  |  |  |

| Appendix D: What's Changed                                           |       |  |  |  |  |  |  |

| Appendix E: PIC16/17 Microcontrollers                                | . 265 |  |  |  |  |  |  |

| Pin Compatibility                                                    |       |  |  |  |  |  |  |

| Index                                                                | . 273 |  |  |  |  |  |  |

| List of Examples                                                     | . 279 |  |  |  |  |  |  |

| ist of Figures                                                       |       |  |  |  |  |  |  |

| ist of Tables                                                        |       |  |  |  |  |  |  |

| Reader Response                                                      |       |  |  |  |  |  |  |

| PIC16C7X Product Identification System                               |       |  |  |  |  |  |  |

For register and module descriptions in this data sheet, device legends show which devices apply to those sections. As an example, the legend below would mean that the following section applies only to the PIC16C72, PIC16C73A and PIC16C74A devices.

## Applicable Devices 72 73 73A 74 74A 76 77

12|13|13A|14|14A|16|11

## To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent an exceptional amount of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

## 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXX uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture in which program and data are fetched from the same memory using the same bus. Separating program and data buses further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The table below lists program memory (EPROM) and data memory (RAM) for each PIC16C7X device.

| Device    | Program<br>Memory | Data Memory |

|-----------|-------------------|-------------|

| PIC16C72  | 2K x 14           | 128 x 8     |

| PIC16C73  | 4K x 14           | 192 x 8     |

| PIC16C73A | 4K x 14           | 192 x 8     |

| PIC16C74  | 4K x 14           | 192 x 8     |

| PIC16C74A | 4K x 14           | 192 x 8     |

| PIC16C76  | 8K x 14           | 368 x 8     |

| PIC16C77  | 8K x 14           | 386 x 8     |

The PIC16CXX can directly or indirectly address its register files or data memory. All special function registers, including the program counter, are mapped in the data memory. The PIC16CXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16CXX simple yet efficient. In addition, the learning curve is reduced significantly.

PIC16CXX devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between the data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow bit and a digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

## 4.2.2.1 STATUS REGISTER Applicable Devices 72|73|73A|74|74A|76|77

The STATUS register, shown in Figure 4-7, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- **Note 1:** For those devices that do not use bits IRP and RP1 (STATUS<7:6>), maintain these bits clear to ensure upward compatibility with future products.

- Note 2: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| R/W-0    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                     | R-1                           | R-1          | R/W-x         | R/W-x     | R/W-x |                                                                                       |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------|--------------|---------------|-----------|-------|---------------------------------------------------------------------------------------|--|

| IRP      | RP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RP0                                                                                       | TO                            | PD           | Z             | DC        | С     | R = Readable bit                                                                      |  |

| bit7     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                           |                               |              |               |           | bit0  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |

| bit 7:   | 1 = Bank 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ster Bank \$<br>2, 3 (100h<br>0, 1 (00h -                                                 | - 1FFh)                       | used for ir  | ndirect addr  | essing)   |       |                                                                                       |  |

| bit 6-5: | 11 = Bank<br>10 = Bank<br>01 = Bank<br>00 = Bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | : Register E<br>< 3 (180h -<br>< 2 (100h -<br>< 1 (80h - F<br>< 0 (00h - 7<br>k is 128 by | 1FFh)<br>17Fh)<br>Fh)<br>′Fh) | ct bits (use | ed for direct | addressin | g)    |                                                                                       |  |

| oit 4:   | TO: Time-out bit<br>1 = After power-up, CLRWDT instruction, or SLEEP instruction<br>0 = A WDT time-out occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                           |                               |              |               |           |       |                                                                                       |  |

| bit 3:   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | r-down bit<br>power-up o<br>ecution of t                                                  | •                             |              |               |           |       |                                                                                       |  |

| bit 2:   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | sult of an a                                                                              |                               |              | peration is z |           |       |                                                                                       |  |

| bit 1:   | <b>DC</b> : Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for borrow the polarity is reversed)<br>1 = A carry-out from the 4th low order bit of the result occurred<br>0 = No carry-out from the 4th low order bit of the result                                                                                                                                                                                                                                                                                                                       |                                                                                           |                               |              |               |           |       |                                                                                       |  |

| bit 0:   | <ul> <li>0 = No carry-out from the 4th low order bit of the result</li> <li>C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)</li> <li>1 = A carry-out from the most significant bit of the result occurred</li> <li>0 = No carry-out from the most significant bit of the result occurred</li> <li>Note: For borrow the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.</li> </ul> |                                                                                           |                               |              |               |           |       |                                                                                       |  |

## FIGURE 4-7: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

## FIGURE 4-13: PIR1 REGISTER PIC16C73/73A/74/74A/76/77 (ADDRESS 0Ch)

| 0<br>(1)                                             | R/W-0<br>ADIF                                                                                                                                                                                                                                                                                                                                                                                                                                       |                        | R-0<br>RCIF                      |               | R-0<br>TXIF | R/W      |       |            | R/W-0<br>CCP1IF |    | 1        | 2/W-0<br>//R2IF |      | R/W<br>TMR | -      | D      |      | Read                  | doblo                      | hit           |                  |                                                                                   |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------------|---------------|-------------|----------|-------|------------|-----------------|----|----------|-----------------|------|------------|--------|--------|------|-----------------------|----------------------------|---------------|------------------|-----------------------------------------------------------------------------------|

|                                                      | ADI                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        | Keir                             |               |             | 001      |       |            |                 |    | <u> </u> | /1//211         |      |            | bit0   | W<br>U | / =  | Writa<br>Unim<br>read | able b<br>nplen<br>  as '( | oit<br>nenteo |                  |                                                                                   |

| 1                                                    | = A re                                                                                                                                                                                                                                                                                                                                                                                                                                              | ad                     | arallel<br>or a wr<br>d or wri   | ite o         | peratic     | n has    |       |            |                 |    |          |                 | eare | ed in      | soft   | war    | e)   |                       |                            |               |                  |                                                                                   |

| 1                                                    | <ul> <li>ADIF: A/D Converter Interrupt Flag bit</li> <li>1 = An A/D conversion completed (must be cleared in software)</li> <li>0 = The A/D conversion is not complete</li> </ul>                                                                                                                                                                                                                                                                   |                        |                                  |               |             |          |       |            |                 |    |          |                 |      |            |        |        |      |                       |                            |               |                  |                                                                                   |

| 1                                                    | <b>RCIF</b> : USART Receive Interrupt Flag bit<br>1 = The USART receive buffer is full (cleared by reading RCREG)<br>0 = The USART receive buffer is empty                                                                                                                                                                                                                                                                                          |                        |                                  |               |             |          |       |            |                 |    |          |                 |      |            |        |        |      |                       |                            |               |                  |                                                                                   |

| 1                                                    | <ul> <li>TXIF: USART Transmit Interrupt Flag bit</li> <li>1 = The USART transmit buffer is empty (cleared by writing to TXREG)</li> <li>0 = The USART transmit buffer is full</li> </ul>                                                                                                                                                                                                                                                            |                        |                                  |               |             |          |       |            |                 |    |          |                 |      |            |        |        |      |                       |                            |               |                  |                                                                                   |

| 1                                                    | <b>SSPIF</b> : Synchronous Serial Port Interrupt Flag bit<br>1 = The transmission/reception is complete (must be cleared in software)<br>0 = Waiting to transmit/receive                                                                                                                                                                                                                                                                            |                        |                                  |               |             |          |       |            |                 |    |          |                 |      |            |        |        |      |                       |                            |               |                  |                                                                                   |

| <u>C</u><br>1<br>0<br><u>C</u><br>1<br>0<br><u>P</u> | <b>CCP1IF</b> : CCP1 Interrupt Flag bit <u>Capture Mode</u> 1 = A TMR1 register capture occurred (must be cleared in software)         0 = No TMR1 register capture occurred <u>Compare Mode</u> 1 = A TMR1 register compare match occurred (must be cleared in software)         0 = No TMR1 register compare match occurred (must be cleared in software)         0 = No TMR1 register compare match occurred <u>PWM Mode</u> Unused in this mode |                        |                                  |               |             |          |       |            |                 |    |          |                 |      |            |        |        |      |                       |                            |               |                  |                                                                                   |

| 1                                                    | = TMF                                                                                                                                                                                                                                                                                                                                                                                                                                               | R2 t                   | MR2 to<br>o PR2<br>R2 to P       | mate          | ch occu     | urred (  | mus   |            | -               | ed | l in     | softw           | are  | e)         |        |        |      |                       |                            |               |                  |                                                                                   |

| 1                                                    | <b>TMR1IF</b> : TMR1 Overflow Interrupt Flag bit<br>1 = TMR1 register overflowed (must be cleared in software)<br>0 = TMR1 register did not overflow                                                                                                                                                                                                                                                                                                |                        |                                  |               |             |          |       |            |                 |    |          |                 |      |            |        |        |      |                       |                            |               |                  |                                                                                   |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        | 73A/76<br>evices,                |               |             |          |       |            |                 | S  | lav      | e Port          | im   | plen       | nente  | ed,    | this | s bit l               | ocat                       | ion is        | rese             | rved                                                                              |

| o<br>errupt<br>pal er                                | on thes                                                                                                                                                                                                                                                                                                                                                                                                                                             | e de<br>ts ge<br>it, G | evices,<br>et set wh<br>IE (INT) | alwa<br>nen a | ays mai     | intain t | his l | bit<br>n o | clear.          | ga | ardle    | ess of t        | he   | state      | of its | cor    | rre  | es                    | espondi                    | esponding e   | esponding enable | is bit location is rese<br>esponding enable bit or<br>lag bits are clear prior to |

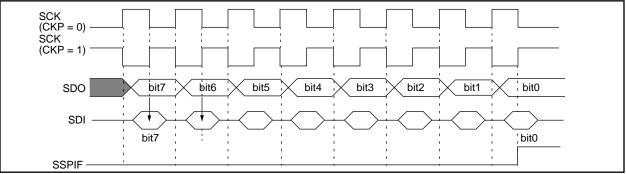

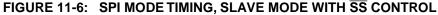

The  $\overline{SS}$  pin allows a synchronous slave mode. The SPI must be in slave mode (SSPCON<3:0> = 04h) and the TRISA<5> bit must be set the for synchronous slave mode to be enabled. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. If the  $\overline{SS}$  pin is taken low without resetting SPI mode, the transmission will continue from the

point at which it was taken high. External pull-up/ pull-down resistors may be desirable, depending on the application.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

|  | <b>TABLE 11-1:</b> | <b>REGISTERS ASSOCIATED WITH SPI OPERATION</b> |

|--|--------------------|------------------------------------------------|

|--|--------------------|------------------------------------------------|

| Address | Name    | Bit 7                  | Bit 6       | Bit 5               | Bit 4                         | Bit 3     | Bit 2    | Bit 1  | Bit 0  | Value<br>POF<br>BOF | ٦,   | all o | e on<br>ther<br>ets |

|---------|---------|------------------------|-------------|---------------------|-------------------------------|-----------|----------|--------|--------|---------------------|------|-------|---------------------|

| 0Bh,8Bh | INTCON  | GIE                    | PEIE        | TOIE                | INTE                          | RBIE      | TOIF     | INTF   | RBIF   | 0000 0              | 200x | 0000  | 000u                |

| 0Ch     | PIR1    | PSPIF <sup>(1,2)</sup> | ADIF        | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup>           | SSPIF     | CCP1IF   | TMR2IF | TMR1IF | 0000 0              | 0000 | 0000  | 0000                |

| 8Ch     | PIE1    | PSPIE <sup>(1,2)</sup> | ADIE        | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup>           | SSPIE     | CCP1IE   | TMR2IE | TMR1IE | 0000 0              | 0000 | 0000  | 0000                |

| 87h     | TRISC   | PORTC Da               | ta Directio | on Registe          | er                            |           |          |        |        | 1111 1              | 1111 | 1111  | 1111                |

| 13h     | SSPBUF  | Synchronou             | us Serial I | Port Rece           | ive Buffer                    | /Transmit | Register |        |        | xxxx x              | xxxx | uuuu  | uuuu                |

| 14h     | SSPCON  | WCOL                   | SSPOV       | SSPEN               | CKP                           | SSPM3     | SSPM2    | SSPM1  | SSPM0  | 0000 0              | 0000 | 0000  | 0000                |

| 85h     | TRISA   | _                      | _           | PORTA I             | PORTA Data Direction Register |           |          |        |        |                     | 1111 | 11    | 1111                |

| 94h     | SSPSTAT | —                      | —           | D/Ā                 | Р                             | S         | R/W      | UA     | BF     | 00 C                | 0000 | 00    | 0000                |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the SSP in SPI mode.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A, always maintain these bits clear.

2: The PIC16C72 does not have a Parallel Slave Port or USART, these bits are unimplemented, read as '0'.

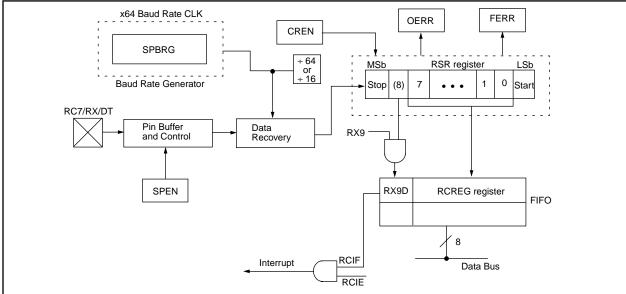

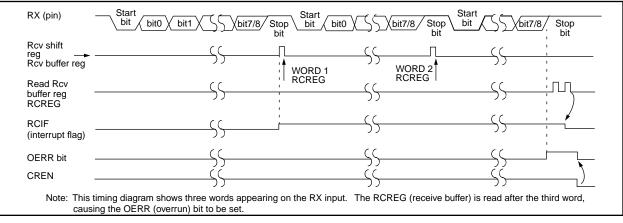

#### 12.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 12-10. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the receive (serial) shift register (RSR). After sampling the STOP bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a

#### FIGURE 12-10: USART RECEIVE BLOCK DIAGRAM

double buffered register, i.e. it is a two deep FIFO. It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte begin shifting to the RSR register. On the detection of the STOP bit of the third byte, if the RCREG register is still full then overrun error bit OERR (RCSTA<1>) will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited, so it is essential to clear error bit OERR if it is set. Framing error bit FERR (RCSTA<2>) is set if a stop bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG, will load bits RX9D and FERR with new values, therefore it is essential for the user to read the RCSTA register before reading RCREG register in order not to lose the old FERR and RX9D information.

TABLE 13-2: REGISTERS/BITS ASSOCIATED WITH A/D, PIC16C72

| Address | Name   | Bit 7   | Bit 6       | Bit 5 | Bit 4  | Bit 3      | Bit 2   | Bit 1   | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|--------|---------|-------------|-------|--------|------------|---------|---------|--------|--------------------------|---------------------------|

| 0Bh,8Bh | INTCON | GIE     | PEIE        | TOIE  | INTE   | RBIE       | T0IF    | INTF    | RBIF   | 0000 000x                | 0000 000u                 |

| 0Ch     | PIR1   | —       | ADIF        | -     | —      | SSPIF      | CCP1IF  | TMR2IF  | TMR1IF | -0 0000                  | -0 0000                   |

| 8Ch     | PIE1   | —       | ADIE        | -     | _      | SSPIE      | CCP1IE  | TMR2IE  | TMR1IE | -0 0000                  | -0 0000                   |

| 1Eh     | ADRES  | A/D Res | sult Regist | ter   |        |            |         |         |        | xxxx xxxx                | uuuu uuuu                 |

| 1Fh     | ADCON0 | ADCS1   | ADCS0       | CHS2  | CHS1   | CHS0       | GO/DONE | —       | ADON   | 0000 00-0                | 0000 00-0                 |

| 9Fh     | ADCON1 | —       | —           | _     | _      | _          | PCFG2   | PCFG1   | PCFG0  | 000                      | 000                       |

| 05h     | PORTA  | _       | _           | RA5   | RA4    | RA3        | RA2     | RA1     | RA0    | 0x 0000                  | 0u 0000                   |

| 85h     | TRISA  | _       |             | PORTA | Data D | irection F | 11 1111 | 11 1111 |        |                          |                           |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D conversion.

## 14.4 Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST), and Brown-out Reset (BOR) Applicable Devices 72 73 73 74 74 76 77

#### 14.4.1 POWER-ON RESET (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.5V - 2.1V). To take advantage of the POR, just tie the  $\overline{MCLR}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met. Brown-out Reset may be used to meet the startup conditions.

For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting.*"

#### 14.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only, from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature, and process variation. See DC parameters for details.

#### 14.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

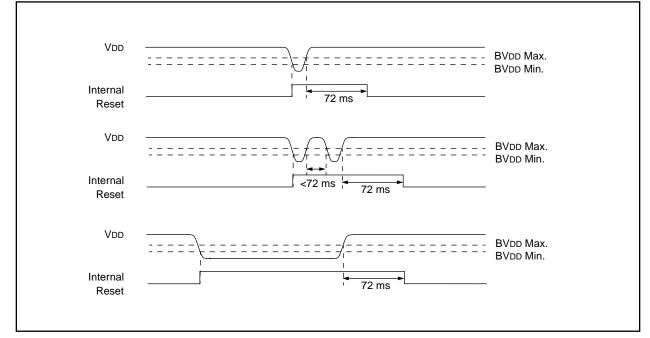

# 14.4.4 BROWN-OUT RESET (BOR) Applicable Devices 72 73 73 74 74 76 77

A configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V (3.8V - 4.2V range) for greater than parameter #35, the brown-out situation will reset the chip. A reset may not occur if VDD falls below 4.0V for less than parameter #35. The chip will remain in Brown-out Reset until VDD rises above BVDD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms. If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above BVDD, the Power-up Timer will execute a 72 ms time delay. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 14-9 shows typical brown-out situations.

### FIGURE 14-9: BROWN-OUT SITUATIONS

## 14.5 <u>Interrupts</u> Applicable Devices 72|73|73|74|74|76|77

The PIC16C7X family has up to 12 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |   |

|-------|------------------------------------------------|---|

|       | less of the status of their corresponding      | l |

|       | mask bit or the GIE bit.                       | l |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set regardless of the status of the GIE bit. The GIE bit is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 14-17). The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- Note: For the PIC16C73/74, if an interrupt occurs while the Global Interrupt Enable (GIE) bit is being cleared, the GIE bit may unintentionally be re-enabled by the user's Interrupt Service Routine (the RETFIE instruction). The events that would cause this to occur are:

- 1. An instruction clears the GIE bit while an interrupt is acknowledged.

- 2. The program branches to the Interrupt vector and executes the Interrupt Service Routine.

- The Interrupt Service Routine completes with the execution of the RET-FIE instruction. This causes the GIE bit to be set (enables interrupts), and the program returns to the instruction after the one which was meant to disable interrupts.

Perform the following to ensure that interrupts are globally disabled:

| LOOP | BCF   | INTCON, | GIE | ; | Disable global   |

|------|-------|---------|-----|---|------------------|

|      |       |         |     | ; | interrupt bit    |

|      | BTFSC | INTCON, | GIE | ; | Global interrupt |

|      |       |         |     | ; | disabled?        |

|      | GOTO  | LOOP    |     | ; | NO, try again    |

|      | :     |         |     | ; | Yes, continue    |

|      |       |         |     | ; | with program     |

|      |       |         |     | ; | flow             |

#### 14.5.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered: either rising if bit INTEDG (OPTION<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 14.8 for details on SLEEP mode.

#### 14.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>). (Section 7.0)

#### 14.5.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>). (Section 5.2)

| Note: | For the PIC16C73/74, if a change on the      |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|

|       | I/O pin should occur when the read opera-    |  |  |  |  |  |  |

|       | tion is being executed (start of the Q2      |  |  |  |  |  |  |

|       | cycle), then the RBIF interrupt flag may not |  |  |  |  |  |  |

|       | get set.                                     |  |  |  |  |  |  |

## 14.6 <u>Context Saving During Interrupts</u> Applicable Devices

## 72 73 73A 74 74A 76 77

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt i.e., W register and STATUS register. This will have to be implemented in software.

Example 14-1 stores and restores the STATUS, W, and PCLATH registers. The register, W\_TEMP, must be defined in each bank and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1).

The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Stores the PCLATH register.

- d) Executes the ISR code.

- e) Restores the STATUS register (and bank select bit).

- f) Restores the W and PCLATH registers.

### EXAMPLE 14-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

| MOVWF<br>SWAPF<br>CLRF | W_TEMP<br>STATUS,W<br>STATUS | ;Copy W to TEMP register, could be bank one or zero<br>;Swap status to be saved into W<br>;bank 0, regardless of current bank, Clears IRP,RP1,RP0 |

|------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| MOVWF                  | STATUS_TEMP                  | ;Save status to bank zero STATUS_TEMP register                                                                                                    |

| MOVF                   | PCLATH, W                    | ;Only required if using pages 1, 2 and/or 3                                                                                                       |

| MOVWF                  | PCLATH_TEMP                  | ;Save PCLATH into W                                                                                                                               |

| CLRF                   | PCLATH                       | ;Page zero, regardless of current page                                                                                                            |

| BCF                    | STATUS, IRP                  | ;Return to Bank 0                                                                                                                                 |

| MOVF                   | FSR, W                       | ;Copy FSR to W                                                                                                                                    |

| MOVWF                  | FSR_TEMP                     | ;Copy FSR from W to FSR_TEMP                                                                                                                      |

| :                      |                              |                                                                                                                                                   |

| :(ISR)                 |                              |                                                                                                                                                   |

| :                      |                              |                                                                                                                                                   |

| MOVF                   | PCLATH_TEMP, W               | ;Restore PCLATH                                                                                                                                   |

| MOVWF                  | PCLATH                       | ;Move W into PCLATH                                                                                                                               |

| SWAPF                  | STATUS_TEMP,W                | ;Swap STATUS_TEMP register into W                                                                                                                 |

|                        |                              | ;(sets bank to original state)                                                                                                                    |

| MOVWF                  | STATUS                       | ;Move W into STATUS register                                                                                                                      |

| SWAPF                  | W_TEMP,F                     | ;Swap W_TEMP                                                                                                                                      |

| SWAPF                  | W_TEMP,W                     | ;Swap W_TEMP into W                                                                                                                               |

|                        |                              |                                                                                                                                                   |

## Applicable Devices 72 73 73A 74 74A 76 77

## 18.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2p             | pS                                    | 3. Tcc:st       | (I <sup>2</sup> C specifications only) |

|-----------------------|---------------------------------------|-----------------|----------------------------------------|

| 2. TppS               |                                       | 4. Ts           | (I <sup>2</sup> C specifications only) |

| Т                     |                                       |                 |                                        |

| F                     | Frequency                             | Т               | Time                                   |

| Lowerca               | se letters (pp) and their meanings:   |                 |                                        |

| рр                    |                                       |                 |                                        |

| сс                    | CCP1                                  | osc             | OSC1                                   |

| ck                    | CLKOUT                                | rd              | RD                                     |

| CS                    | CS                                    | rw              | RD or WR                               |

| di                    | SDI                                   | SC              | SCK                                    |

| do                    | SDO                                   | SS              | SS                                     |

| dt                    | Data in                               | tO              | ТОСКІ                                  |

| io                    | I/O port                              | t1              | T1CKI                                  |

| mc                    | MCLR                                  | wr              | WR                                     |

|                       | se letters and their meanings:        |                 |                                        |

| S                     |                                       |                 |                                        |

| F                     | Fall                                  | P               | Period                                 |

| H                     | High                                  | R               | Rise                                   |

|                       | Invalid (Hi-impedance)                | V               | Valid                                  |

| L                     | Low                                   | Z               | Hi-impedance                           |

| I <sup>2</sup> C only |                                       |                 |                                        |

| AA                    | output access                         | High            | High                                   |

| BUF                   | Bus free                              | Low             | Low                                    |

| Tcc:st (              | I <sup>2</sup> C specifications only) |                 |                                        |

| CC                    |                                       |                 |                                        |

| HD                    | Hold                                  | SU              | Setup                                  |

| ST                    |                                       |                 |                                        |

| DAT                   | DATA input hold                       | STO             | STOP condition                         |

| STA                   | START condition                       |                 |                                        |

| FIGURE 1              | 8-1: LOAD CONDITIONS                  |                 |                                        |

|                       | Load condition 1                      | Loa             | d condition 2                          |

|                       | VDD/2                                 |                 |                                        |

|                       | Pin CL<br>Vss                         | Pin             |                                        |

|                       | $RL = 464\Omega$                      |                 | Vss                                    |

|                       |                                       | , but including | PORTD and PORTE outputs as             |

|                       | 15 pF for OSC2 output                 |                 |                                        |

|                       | Note: PORTD and PORTE are not imple   | emented on th   | e PIC16C73.                            |

|                       |                                       |                 |                                        |

Applicable Devices 72 73 73A 74 74A 76 77

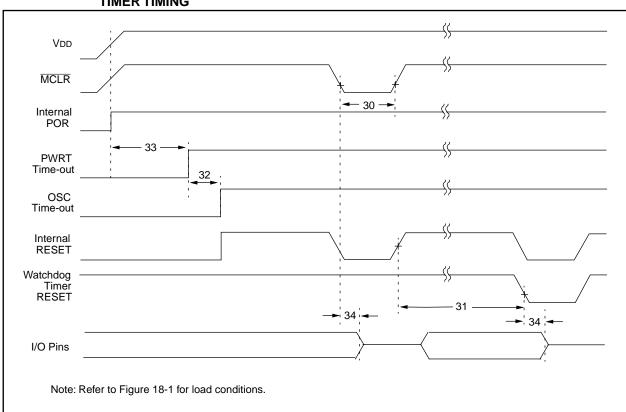

## FIGURE 18-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

## TABLE 18-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP<br/>TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†     | Max | Units | Conditions               |

|------------------|-------|--------------------------------------------------------|-----|----------|-----|-------|--------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                 | 100 | —        | _   | ns    | VDD = 5V, -40°C to +85°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +85°C |

| 32               | Tost  | Oscillation Start-up Timer Period                      | _   | 1024Tosc | —   | _     | Tosc = OSC1 period       |

| 33*              | Tpwrt | Power up Timer Period                                  | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +85°C |

| 34               | Tıoz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | —   | _        | 100 | ns    |                          |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Applicable Devices

72

73

73A

74

74A

76

77

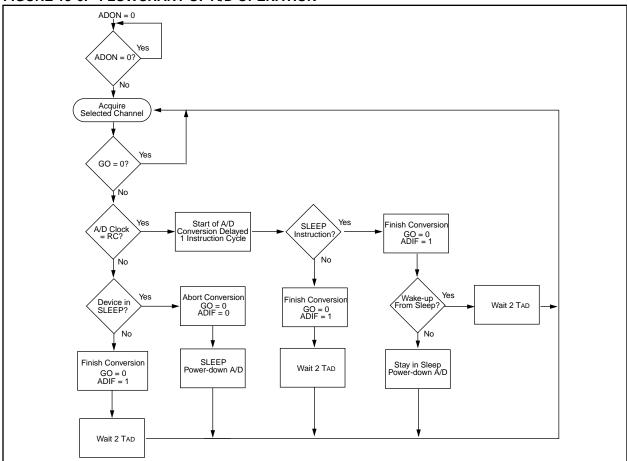

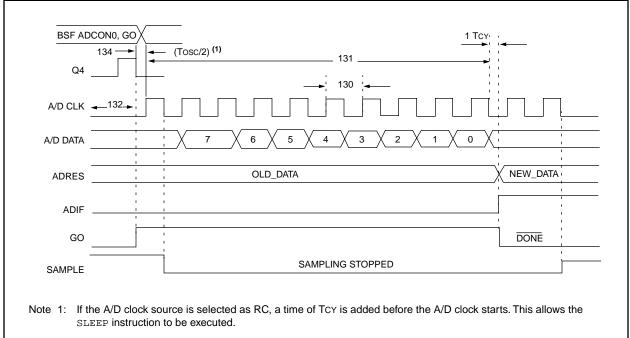

## FIGURE 19-14: A/D CONVERSION TIMING

## TABLE 19-14: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym  | Characteristic                  |                                | Min    | Тур†     | Мах | Units | Conditions                                                                                                                                                                                                                    |

|--------------|------|---------------------------------|--------------------------------|--------|----------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D clock period                | PIC16 <b>C</b> 73A/74A         | 1.6    | _        | _   | μs    | Tosc based, VREF ≥ 3.0V                                                                                                                                                                                                       |

|              |      |                                 | PIC16 <b>LC</b> 73A/74A        | 2.0    | —        | _   | μs    | Tosc based, VREF full range                                                                                                                                                                                                   |

|              |      |                                 | PIC16 <b>C</b> 73A/74A         | 2.0    | 4.0      | 6.0 | μs    | A/D RC Mode                                                                                                                                                                                                                   |

|              |      |                                 | PIC16 <b>LC</b> 73A/74A        | 3.0    | 6.0      | 9.0 | μs    | A/D RC Mode                                                                                                                                                                                                                   |

| 131          | TCNV | Conversion time (no<br>(Note 1) | ot including S/H time)         | _      | 9.5      |     | TAD   |                                                                                                                                                                                                                               |

| 132          | TACQ | Acquisition time                |                                | Note 2 | 20       | _   | μs    |                                                                                                                                                                                                                               |

|              |      |                                 |                                | 5*     | _        | _   | μs    | The minimum time is the amplifier<br>settling time. This may be used if<br>the "new" input voltage has not<br>changed by more than 1 LSb (i.e.,<br>20.0 mV @ 5.12V) from the last<br>sampled voltage (as stated on<br>CHOLD). |

| 134          | TGO  | Q4 to A/D clock sta             | rt                             | _      | Tosc/2 § | _   | _     | If the A/D clock source is selected<br>as RC, a time of TCY is added<br>before the A/D clock starts. This<br>allows the SLEEP instruction to be<br>executed.                                                                  |

| 135          | Tswc | Switching from con-             | vert $\rightarrow$ sample time | 1.5 §  | _        | _   | TAD   |                                                                                                                                                                                                                               |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 13.1 for min conditions.

\*

## Applicable Devices 72 73 73A 74 74A 76 77

## 20.1 DC Characteristics: PIC16C76/77-04 (Commercial, Industrial, Extended) PIC16C76/77-10 (Commercial, Industrial, Extended) PIC16C76/77-20 (Commercial, Industrial, Extended)

|               |                                                                  |               | Standa     | ard Op | eratin     | g Cond | litions (unless otherwise stated)                              |

|---------------|------------------------------------------------------------------|---------------|------------|--------|------------|--------|----------------------------------------------------------------|

|               | ARACTERISTICS                                                    |               | Operati    |        |            |        | $0^{\circ}C \leq TA \leq +125^{\circ}C$ for extended,          |

|               | ARACTERISTICS                                                    |               | -          | -      |            | -4     | $0^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial and      |

|               |                                                                  |               |            |        |            | 0°     | C $\leq$ TA $\leq$ +70°C for commercial                        |

| Param<br>No.  | Characteristic                                                   | Sym           | Min        | Тур†   | Max        | Units  | Conditions                                                     |

| D001<br>D001A | Supply Voltage                                                   | Vdd           | 4.0<br>4.5 |        | 6.0<br>5.5 | V<br>V | XT, RC and LP osc configuration<br>HS osc configuration        |

| D002*         | RAM Data Retention<br>Voltage (Note 1)                           | Vdr           | -          | 1.5    | -          | V      |                                                                |

| D003          | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR          | -          | Vss    | -          | V      | See section on Power-on Reset for details                      |

| D004*         | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | Svdd          | 0.05       | -      | -          | V/ms   | See section on Power-on Reset for details                      |

| D005          | Brown-out Reset Voltage                                          | Bvdd          | 3.7        | 4.0    | 4.3        | V      | BODEN bit in configuration word enabled                        |

|               |                                                                  |               | 3.7        | 4.0    | 4.4        | V      | Extended Range Only                                            |

| D010          | Supply Current (Note 2,5)                                        | IDD           | -          | 2.7    | 5          | mA     | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)  |

| D013          |                                                                  |               | -          | 10     | 20         | mA     | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V              |

| D015*         | Brown-out Reset Current<br>(Note 6)                              | $\Delta$ IBOR | -          | 350    | 425        | μA     | BOR enabled VDD = 5.0V                                         |

| D020          | Power-down Current                                               | IPD           | -          | 10.5   | 42         | μA     | VDD = $4.0V$ , WDT enabled, $-40^{\circ}C$ to $+85^{\circ}C$   |

| D021          | (Note 3,5)                                                       |               | -          | 1.5    | 16         | μA     | VDD = 4.0V, WDT disabled, $-0^{\circ}C$ to $+70^{\circ}C$      |

| D021A         |                                                                  |               | -          | 1.5    | 19         | μΑ     | VDD = $4.0V$ , WDT disabled, $-40^{\circ}C$ to $+85^{\circ}C$  |

| D021B         |                                                                  |               | -          | 2.5    | 19         | μA     | VDD = $4.0V$ , WDT disabled, $-40^{\circ}C$ to $+125^{\circ}C$ |

| D023*         | Brown-out Reset Current<br>(Note 6)                              | $\Delta$ IBOR | -          | 350    | 425        | μΑ     | BOR enabled VDD = 5.0V                                         |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

$\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

## Applicable Devices 72 73 73A 74 74A 76 77

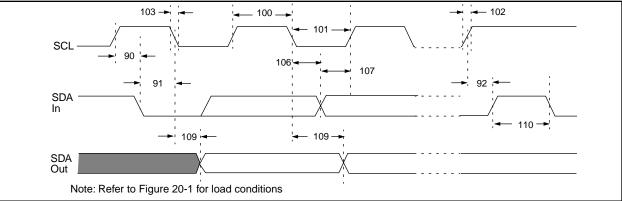

## FIGURE 20-14: I<sup>2</sup>C BUS DATA TIMING

## TABLE 20-10: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Parameter<br>No. | Sym     | Characteristic         |              | Min        | Мах  | Units | Conditions                                       |

|------------------|---------|------------------------|--------------|------------|------|-------|--------------------------------------------------|

| 100              | Thigh   | Clock high time        | 100 kHz mode | 4.0        | _    | μs    | Device must operate at a mini-<br>mum of 1.5 MHz |

|                  |         |                        | 400 kHz mode | 0.6        | _    | μs    | Device must operate at a mini-<br>mum of 10 MHz  |

|                  |         |                        | SSP Module   | 1.5Tcy     | —    |       |                                                  |

| 101              | TLOW    | Clock low time         | 100 kHz mode | 4.7        | —    | μs    | Device must operate at a mini-<br>mum of 1.5 MHz |

|                  |         |                        | 400 kHz mode | 1.3        | _    | μs    | Device must operate at a mini-<br>mum of 10 MHz  |

|                  |         |                        | SSP Module   | 1.5Tcy     | _    |       |                                                  |

| 102              | Tr      | SDA and SCL rise       | 100 kHz mode | -          | 1000 | ns    |                                                  |

|                  |         | time                   | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from<br>10 to 400 pF       |

| 103              | Tf      | SDA and SCL fall time  | 100 kHz mode | -          | 300  | ns    |                                                  |

|                  |         |                        | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from<br>10 to 400 pF       |

| 90               | TSU:STA | START condition        | 100 kHz mode | 4.7        | —    | μs    | Only relevant for repeated                       |

|                  |         | setup time             | 400 kHz mode | 0.6        | —    | μs    | START condition                                  |

| 91               | THD:STA | START condition hold   | 100 kHz mode | 4.0        | —    | μs    | After this period the first clock                |

|                  |         | time                   | 400 kHz mode | 0.6        | —    | μs    | pulse is generated                               |

| 106              | THD:DAT | Data input hold time   | 100 kHz mode | 0          | —    | ns    |                                                  |

|                  |         |                        | 400 kHz mode | 0          | 0.9  | μs    |                                                  |

| 107              | TSU:DAT | Data input setup time  | 100 kHz mode | 250        | —    | ns    | Note 2                                           |

|                  |         |                        | 400 kHz mode | 100        | —    | ns    |                                                  |

| 92               | TSU:STO | STOP condition setup   | 100 kHz mode | 4.7        | —    | μs    |                                                  |

|                  |         | time                   | 400 kHz mode | 0.6        | —    | μs    |                                                  |

| 109              | ΤΑΑ     | Output valid from      | 100 kHz mode | _          | 3500 | ns    | Note 1                                           |

|                  |         | clock                  | 400 kHz mode | _          | —    | ns    |                                                  |

| 110              | TBUF    | Bus free time          | 100 kHz mode | 4.7        | —    | μs    | Time the bus must be free                        |

|                  |         |                        | 400 kHz mode | 1.3        | —    | μs    | before a new transmission can start              |

|                  | Cb      | Bus capacitive loading |              |            | 400  | pF    |                                                  |

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

2: A fast-mode (400 kHz) I<sup>2</sup>C-bus device can be used in a standard-mode (100 kHz) I<sup>2</sup>C-bus system, but the requirement tsu;DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+tsu;DAT = 1000 + 250 = 1250 ns (according to the standard-mode I<sup>2</sup>C bus specification) before the SCL line is released.

Applicable Devices 72 73 73A 74 74A 76 77

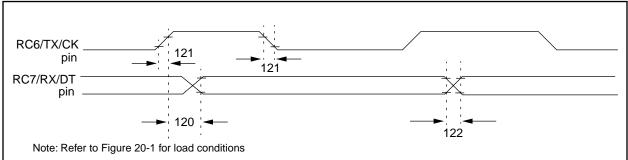

## FIGURE 20-15: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

## TABLE 20-11: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                                                |                                               | Min | Тур† | Max       | Units    | Conditions |

|--------------|----------|---------------------------------------------------------------|-----------------------------------------------|-----|------|-----------|----------|------------|

| 120          | TckH2dtV | SYNC XMIT (MASTER &<br>SLAVE)<br>Clock high to data out valid | PIC16 <b>C</b> 76/77<br>PIC16 <b>LC</b> 76/77 | _   | _    | 80<br>100 | ns<br>ns |            |

| 121          | Tckrf    | Clock out rise time and fall time                             | PIC16 <b>C</b> 76/77                          |     |      | 45        | ns       |            |

|              |          | (Master Mode)                                                 | PIC16 <b>LC</b> 76/77                         | —   |      | 50        | ns       |            |

| 122          | Tdtrf    | Data out rise time and fall time                              | PIC16 <b>C</b> 76/77                          | —   | -    | 45        | ns       |            |

|              |          |                                                               | PIC16 <b>LC</b> 76/77                         | —   | —    | 50        | ns       |            |

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

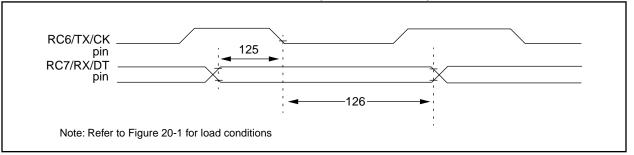

#### FIGURE 20-16: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

### TABLE 20-12: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                                 | Min | Тур† | Мах | Units | Conditions |

|------------------|----------|--------------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data setup before $CK \downarrow (DT setup time)$ | 15  | _    | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                 | 15  | —    | —   | ns    |            |

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16C7X

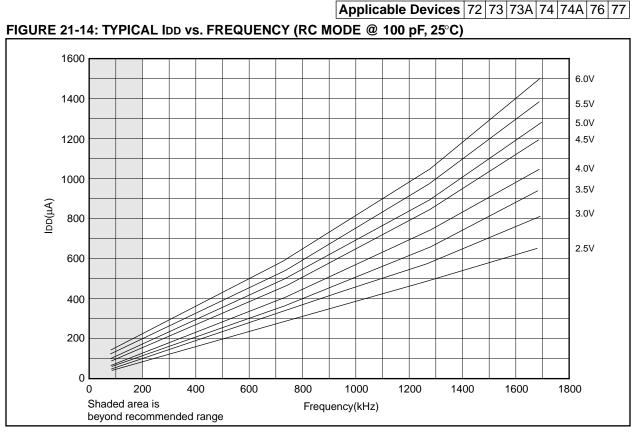

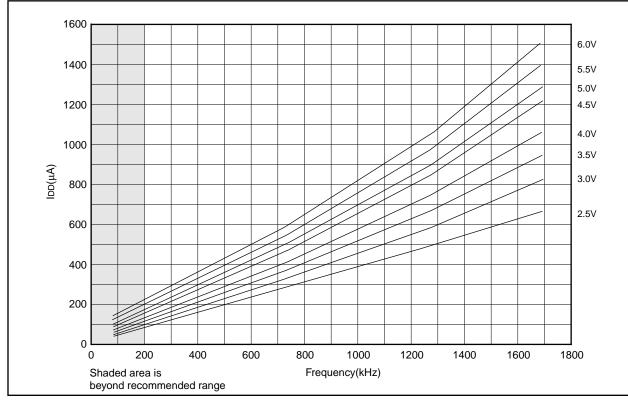

FIGURE 21-15: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 100 pF, -40°C TO 85°C)

Data based on matrix samples. See first page of this section for details.

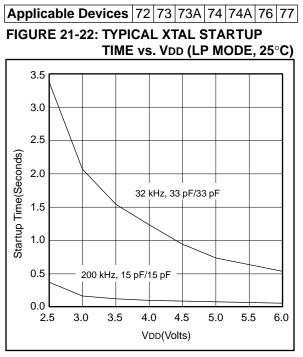

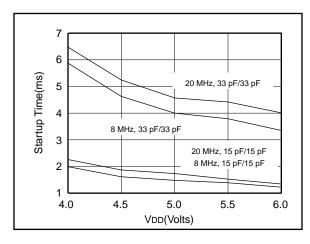

FIGURE 21-23: TYPICAL XTAL STARTUP TIME vs. Vdd (HS MODE, 25°C)

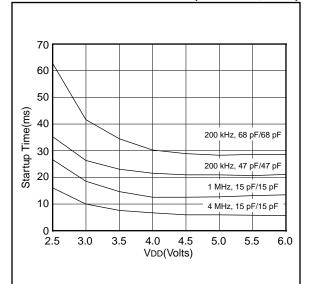

## FIGURE 21-24: TYPICAL XTAL STARTUP TIME vs. VDD (XT MODE, 25°C)

TABLE 21-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATORS

| Osc Type         | Crystal<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |