#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

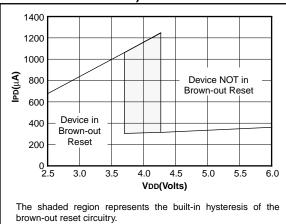

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                 |

| Data Converters            | A/D 5x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc76-04-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

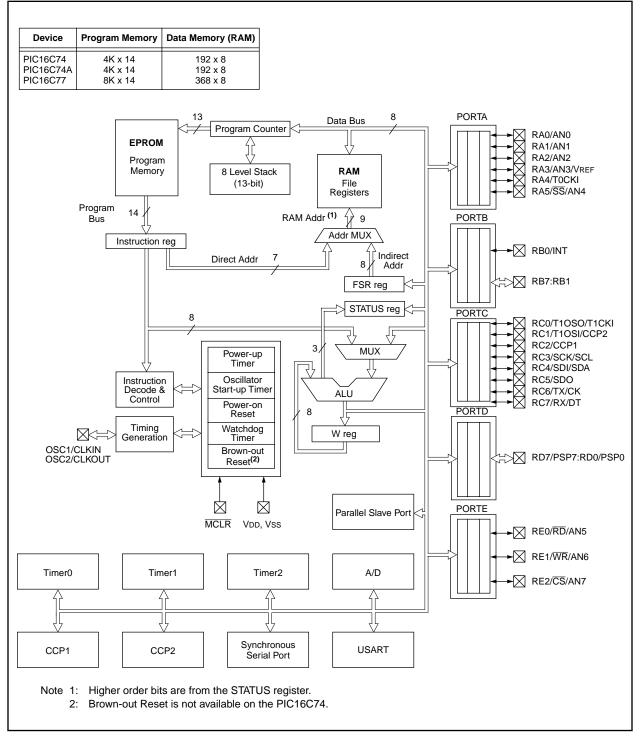

#### FIGURE 3-3: PIC16C74/74A/77 BLOCK DIAGRAM

# PIC16C7X

NOTES:

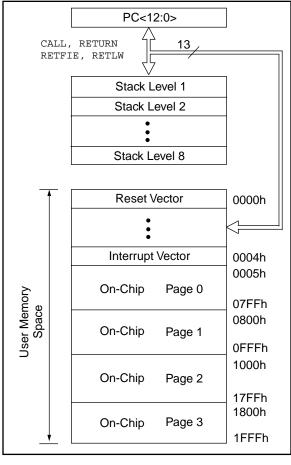

#### FIGURE 4-3: PIC16C76/77 PROGRAM MEMORY MAP AND STACK

## 4.2 Data Memory Organization

Applicable Devices 72 73 73 74 74 76 77

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

RP1:RP0 (STATUS<6:5>)

- = 00  $\rightarrow$  Bank0

- = 01  $\rightarrow$  Bank1

- =  $10 \rightarrow \text{Bank2}$

- = 11  $\rightarrow$  Bank3

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain special function registers. Some "high use" special function registers from one bank may be mirrored in another bank for code reduction and quicker access.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR (Section 4.5).

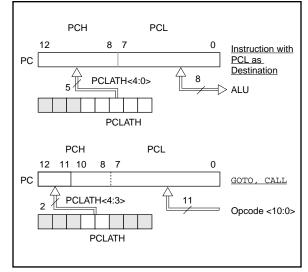

# 4.3 PCL and PCLATH Applicable Devices 72/73/73A/74/74A/76/77

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The upper bits (PC<12:8>) are not readable, but are indirectly writable through the PCLATH register. On any reset, the upper bits of the PC will be cleared. Figure 4-17 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 4-17: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note *"Implementing a Table Read"* (AN556).

#### 4.3.2 STACK

The PIC16CXX family has an 8 level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no status bits to indicate stack overflow or stack underflow conditions.

- Note 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address.

## 4.4 Program Memory Paging Applicable Devices 72|73|73A|74|74A|76|77

PIC16C7X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<4:3> bits are not required for the return instructions (which POPs the address from the stack).

Note: PIC16C7X devices with 4K or less of program memory ignore paging bit PCLATH<4>. The use of PCLATH<4> as a general purpose read/write bit is not recommended since this may affect upward compatibility with future products.

#### FIGURE 9-2: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

| U-0      | R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0                                                                                                     |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| <u> </u> | TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0 R = Readable bit                                                                 |  |

| bit7     | bit0<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset                                           |  |

| bit 7:   | Unimplemented: Read as '0'                                                                                                              |  |

| bit 6-3: | TOUTPS3:TOUTPS0: Timer2 Output Postscale Select bits<br>0000 = 1:1 Postscale<br>0001 = 1:2 Postscale<br>•<br>•<br>1111 = 1:16 Postscale |  |

| bit 2:   | TMR2ON: Timer2 On bit<br>1 = Timer2 is on<br>0 = Timer2 is off                                                                          |  |

| bit 1-0: | <b>T2CKPS1:T2CKPS0</b> : Timer2 Clock Prescale Select bits<br>00 = Prescaler is 1<br>01 = Prescaler is 4<br>1x = Prescaler is 16        |  |

#### **TABLE 9-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER**

| Address               | Name   | Bit 7                  | Bit 6          | Bit 5               | Bit 4               | Bit 3     | Bit 2  | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|-----------------------|--------|------------------------|----------------|---------------------|---------------------|-----------|--------|---------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                    | PEIE           | TOIE                | INTE                | RBIE      | TOIF   | INTF    | RBIF    | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1   | PSPIF <sup>(1,2)</sup> | ADIF           | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | SSPIF     | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000                | 0000 0000                       |

| 8Ch                   | PIE1   | PSPIE <sup>(1,2)</sup> | ADIE           | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup> | SSPIE     | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000                | 0000 0000                       |

| 11h                   | TMR2   | Timer2 mod             | lule's registe | r                   |                     |           |        |         |         | 0000 0000                | 0000 0000                       |

| 12h                   | T2CON  | _                      | TOUTPS3        | TOUTPS2             | TOUTPS1             | TOUTPS0   | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000                | -000 0000                       |

| 92h                   | PR2    | Timer2 Peri            | od Register    |                     | 1111 1111           | 1111 1111 |        |         |         |                          |                                 |

Legend:

x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

Note

1:

Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

2:

The PIC16C72 does not have a Parallel Slave Port or a USART, these bits are unimplemented, read as '0'.

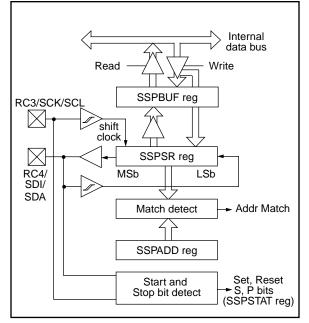

# 11.5 <u>SSP I<sup>2</sup>C Operation</u>

The SSP module in I<sup>2</sup>C mode fully implements all slave functions, except general call support, and provides interrupts on start and stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing. Two pins are used for data transfer. These are the RC3/SCK/SCL pin, which is the clock (SCL), and the RC4/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits. The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSP-CON<5>).

#### FIGURE 11-24: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  ${\rm I}^2{\rm C}$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Firmware controlled Master Mode, slave is idle

Selection of any I<sup>2</sup>C mode, with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits.

The SSPSTAT register gives the status of the data transfer. This information includes detection of a START or STOP bit, specifies if the received byte was data or address if the next byte is the completion of 10-bit address, and if this will be a read or write data transfer. The SSPSTAT register is read only.

The SSPBUF is the register to which transfer data is written to or read from. The SSPSR register shifts the data in or out of the device. In receive operations, the SSPBUF and SSPSR create a doubled buffered receiver. This allows reception of the next byte to begin before reading the last byte of received data. When the complete byte is received, it is transferred to the SSPBUF register and flag bit SSPIF is set. If another complete byte is received before the SSPBUF register is read, a receiver overflow has occurred and bit SSPOV (SSPCON<6>) is set and the byte in the SSPSR is lost.

The SSPADD register holds the slave address. In 10-bit mode, the user first needs to write the high byte of the address (1111 0 A9 A8 0). Following the high byte address match, the low byte of the address needs to be loaded (A7:A0).

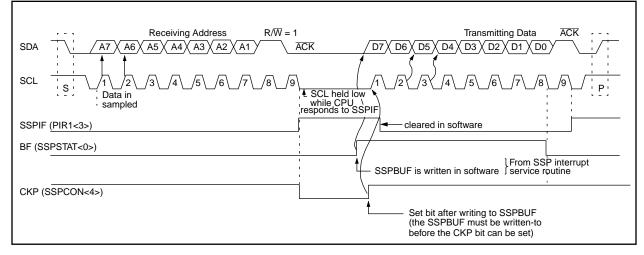

#### 11.5.1.3 TRANSMISSION

When the  $R\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The  $\overline{ACK}$  pulse will be sent on the ninth bit, and pin RC3/SCK/SCL is held low. The transmit data must be loaded into the SSP-BUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 11-26). An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software, and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP.

## FIGURE 11-26: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

| BAUD<br>RATE<br>(K) | Fosc = 2<br>KBAUD | 20 MHz<br>%<br>ERROR | SPBRG<br>value<br>(decimal) | 16 MHz<br>KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) | 10 MHz<br>KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) | 7.16 MH | z<br>%<br>ERROR | SPBRG<br>value<br>(decimal) |

|---------------------|-------------------|----------------------|-----------------------------|-----------------|------------|-----------------------------|-----------------|------------|-----------------------------|---------|-----------------|-----------------------------|

| 9.6                 | 9.615             | +0.16                | 129                         | 9.615           | +0.16      | 103                         | 9.615           | +0.16      | 64                          | 9.520   | -0.83           | 46                          |

| 19.2                | 19.230            | +0.16                | 64                          | 19.230          | +0.16      | 51                          | 18.939          | -1.36      | 32                          | 19.454  | +1.32           | 22                          |

| 38.4                | 37.878            | -1.36                | 32                          | 38.461          | +0.16      | 25                          | 39.062          | +1.7       | 15                          | 37.286  | -2.90           | 11                          |

| 57.6                | 56.818            | -1.36                | 21                          | 58.823          | +2.12      | 16                          | 56.818          | -1.36      | 10                          | 55.930  | -2.90           | 7                           |

| 115.2               | 113.636           | -1.36                | 10                          | 111.111         | -3.55      | 8                           | 125             | +8.51      | 4                           | 111.860 | -2.90           | 3                           |

| 250                 | 250               | 0                    | 4                           | 250             | 0          | 3                           | NA              | -          | -                           | NA      | -               | -                           |

| 625                 | 625               | 0                    | 1                           | NA              | -          | -                           | 625             | 0          | 0                           | NA      | -               | -                           |

| 1250                | 1250              | 0                    | 0                           | NA              | -          | -                           | NA              | -          | -                           | NA      | -               | -                           |

# TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD        | Fosc = 5 | .068 MHz   | SPBRG              | 4 MHz  |            | SPBRG              | 3.579 Mł | Ηz         | SPBRG              | 1 MHz  |            | SPBRG              | 32.768 | κHz        | SPBRG              |

|-------------|----------|------------|--------------------|--------|------------|--------------------|----------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) |

| 9.6         | 9.6      | 0          | 32                 | NA     | -          | -                  | 9.727    | +1.32      | 22                 | 8.928  | -6.99      | 6                  | NA     | -          | -                  |

| 19.2        | 18.645   | -2.94      | 16                 | 1.202  | +0.17      | 207                | 18.643   | -2.90      | 11                 | 20.833 | +8.51      | 2                  | NA     | -          | -                  |

| 38.4        | 39.6     | +3.12      | 7                  | 2.403  | +0.13      | 103                | 37.286   | -2.90      | 5                  | 31.25  | -18.61     | 1                  | NA     | -          | -                  |

| 57.6        | 52.8     | -8.33      | 5                  | 9.615  | +0.16      | 25                 | 55.930   | -2.90      | 3                  | 62.5   | +8.51      | 0                  | NA     | -          | -                  |

| 115.2       | 105.6    | -8.33      | 2                  | 19.231 | +0.16      | 12                 | 111.860  | -2.90      | 1                  | NA     | -          | -                  | NA     | -          | -                  |

| 250         | NA       | -          | -                  | NA     | -          | -                  | 223.721  | -10.51     | 0                  | NA     | -          | -                  | NA     | -          | -                  |

| 625         | NA       | -          | -                  | NA     | -          | -                  | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| 1250        | NA       | -          | -                  | NA     | -          | -                  | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

**Note:** For the PIC16C73/73A/74/74A, the asynchronous high speed mode (BRGH = 1) may experience a high rate of receive errors. It is recommended that BRGH = 0. If you desire a higher baud rate than BRGH = 0 can support, refer to the device errata for additional information, or use the PIC16C76/77.

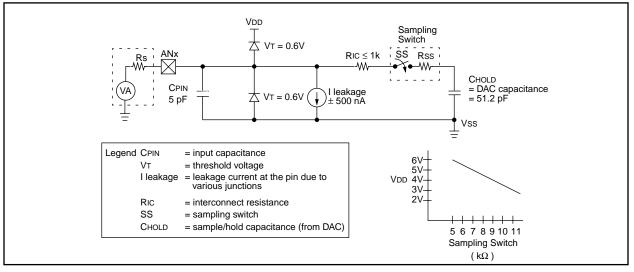

#### 13.1 A/D Acquisition Requirements

# Applicable Devices 72 73 73 74 74 76 77

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 13-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), Figure 13-4. The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 10 k $\Omega$ . After the analog input channel is selected (changed) this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 13-1 may be used. This equation calculates the acquisition time to within 1/2 LSb error is used (512 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified accuracy.

# EQUATION 13-1: A/D MINIMUM CHARGING TIME

$VHOLD = (VREF - (VREF/512)) \bullet (1 - e^{(-TCAP/CHOLD(RIC + RSS + RS))})$

Given: VHOLD = (VREF/512), for 1/2 LSb resolution

The above equation reduces to:

$TCAP = -(51.2 \text{ pF})(1 \text{ k}\Omega + \text{Rss} + \text{Rs}) \ln(1/511)$

Example 13-1 shows the calculation of the minimum required acquisition time TACQ. This calculation is based on the following system assumptions.

CHOLD = 51.2 pF

Rs = 10 kΩ

1/2 LSb error

#### FIGURE 13-4: ANALOG INPUT MODEL

$VDD = 5V \rightarrow Rss = 7 \text{ k}\Omega$

Temp (application system max.) = 50°C

VHOLD = 0 @ t = 0

- Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- Note 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **Note 3:** The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

- **Note 4:** After a conversion has completed, a 2.0TAD delay must complete before acquisition can begin again. During this time the holding capacitor is not connected to the selected A/D input channel.

#### EXAMPLE 13-1: CALCULATING THE MINIMUM REQUIRED ACQUISITION TIME

- TACQ = Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient

- TACQ =  $5 \mu s + TCAP + [(Temp 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$

- TCAP = -CHOLD (Ric + Rss + Rs) ln(1/511)-51.2 pF (1 k $\Omega$  + 7 k $\Omega$  + 10 k $\Omega$ ) ln(0.0020) -51.2 pF (18 k $\Omega$ ) ln(0.0020) -0.921 µs (-6.2364) 5.747 µs

- TACQ = 5 μs + 5.747 μs + [(50°C 25°C)(0.05 μs/°C)] 10.747 μs + 1.25 μs 11.997 μs

| TABLE 14-6: | STATUS BITS AND THEIR SIGNIFICANCE, PIC16C72/73A/74A/76/77 |

|-------------|------------------------------------------------------------|

|-------------|------------------------------------------------------------|

| POR | BOR | TO | PD |                                                         |  |  |  |  |

|-----|-----|----|----|---------------------------------------------------------|--|--|--|--|

| 0   | x   | 1  | 1  | Power-on Reset                                          |  |  |  |  |

| 0   | x   | 0  | x  | legal, TO is set on POR                                 |  |  |  |  |

| 0   | x   | x  | 0  | legal, PD is set on POR                                 |  |  |  |  |

| 1   | 0   | x  | x  | Brown-out Reset                                         |  |  |  |  |

| 1   | 1   | 0  | 1  | WDT Reset                                               |  |  |  |  |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |  |  |  |  |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |  |  |  |  |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |  |  |  |  |

#### TABLE 14-7: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register<br>PIC16C73/74 | PCON<br>Register<br>PIC16C72/73A/74A/76/77 |

|------------------------------------|-----------------------|--------------------|---------------------------------|--------------------------------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0-                              | 0x                                         |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | u-                              | uu                                         |

| MCLR Reset during SLEEP            | 000h                  | 0001 Ouuu          | u-                              | uu                                         |

| WDT Reset                          | 000h                  | 0000 luuu          | u-                              | uu                                         |

| WDT Wake-up                        | PC + 1                | uuu0 Ouuu          | u-                              | uu                                         |

| Brown-out Reset                    | 000h                  | 0001 luuu          | N/A                             | u0                                         |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | u-                              | uu                                         |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

| TABLE 14-8: | INITIALIZATION CONDITIONS FOR ALL REGISTERS |

|-------------|---------------------------------------------|

|-------------|---------------------------------------------|

| Register | Applicable Devices |    |     |    | es  |    | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT<br>or<br>Interrupt |                       |

|----------|--------------------|----|-----|----|-----|----|------------------------------------|--------------------------|------------------------------------|-----------------------|

| W        | 72                 | 73 | 73A | 74 | 74A | 76 | 77                                 | xxxx xxxx                | uuuu uuuu                          | uuuu uuuu             |

| INDF     | 72                 | 73 | 73A | 74 | 74A | 76 | 77                                 | N/A                      | N/A                                | N/A                   |

| TMR0     | 72                 | 73 | 73A | 74 | 74A | 76 | 77                                 | xxxx xxxx                | uuuu uuuu                          | uuuu uuuu             |

| PCL      | 72                 | 73 | 73A | 74 | 74A | 76 | 77                                 | 0000h                    | 0000h                              | PC + 1 <sup>(2)</sup> |

| STATUS   | 72                 | 73 | 73A | 74 | 74A | 76 | 77                                 | 0001 1xxx                | 000q quuu <b>(3)</b>               | uuuq quuu <b>(3)</b>  |

| FSR      | 72                 | 73 | 73A | 74 | 74A | 76 | 77                                 | xxxx xxxx                | uuuu uuuu                          | uuuu uuuu             |

| PORTA    | 72                 | 73 | 73A | 74 | 74A | 76 | 77                                 | 0x 0000                  | 0u 0000                            | uu uuuu               |

| PORTB    | 72                 | 73 | 73A | 74 | 74A | 76 | 77                                 | xxxx xxxx                | uuuu uuuu                          | uuuu uuuu             |

| PORTC    | 72                 | 73 | 73A | 74 | 74A | 76 | 77                                 | xxxx xxxx                | uuuu uuuu                          | uuuu uuuu             |

| PORTD    | 72                 | 73 | 73A | 74 | 74A | 76 | 77                                 | xxxx xxxx                | uuuu uuuu                          | uuuu uuuu             |

| PORTE    | 72                 | 73 | 73A | 74 | 74A | 76 | 77                                 | xxx                      | uuu                                | uuu                   |

| PCLATH   | 72                 | 73 | 73A | 74 | 74A | 76 | 77                                 | 0 0000                   | 0 0000                             | u uuuu                |

Legend: u = unchanged, x = unknown, -= unimplemented bit, read as '0', <math>q = value depends on condition

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 14-7 for reset value for specific condition.

## 14.5 <u>Interrupts</u> Applicable Devices 72|73|73|74|74|76|77

The PIC16C7X family has up to 12 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

| Note: | Individual interrupt flag bits are set regard- |   |

|-------|------------------------------------------------|---|

|       | less of the status of their corresponding      | l |

|       | mask bit or the GIE bit.                       | l |

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set regardless of the status of the GIE bit. The GIE bit is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs (Figure 14-17). The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

- Note: For the PIC16C73/74, if an interrupt occurs while the Global Interrupt Enable (GIE) bit is being cleared, the GIE bit may unintentionally be re-enabled by the user's Interrupt Service Routine (the RETFIE instruction). The events that would cause this to occur are:

- 1. An instruction clears the GIE bit while an interrupt is acknowledged.

- 2. The program branches to the Interrupt vector and executes the Interrupt Service Routine.

- The Interrupt Service Routine completes with the execution of the RET-FIE instruction. This causes the GIE bit to be set (enables interrupts), and the program returns to the instruction after the one which was meant to disable interrupts.

Perform the following to ensure that interrupts are globally disabled:

| LOOP | BCF   | INTCON, | GIE | ; | Disable global   |

|------|-------|---------|-----|---|------------------|

|      |       |         |     | ; | interrupt bit    |

|      | BTFSC | INTCON, | GIE | ; | Global interrupt |

|      |       |         |     | ; | disabled?        |

|      | GOTO  | LOOP    |     | ; | NO, try again    |

|      | :     |         |     | ; | Yes, continue    |

|      |       |         |     | ; | with program     |

|      |       |         |     | ; | flow             |

# 14.8 Power-down Mode (SLEEP) Applicable Devices 72/73/73A/74/74A/76/77

Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD, or Vss, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D, disable external clocks. Pull all I/O pins, that are hi-impedance inputs, high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level (VIHMC).

#### 14.8.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change, or some Peripheral Interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. SSP (Start/Stop) bit detect interrupt.

- 3. SSP transmit or receive in slave mode (SPI/ $l^2$ C).

- 4. CCP capture mode interrupt.

- 5. Parallel Slave Port read or write.

- 6. A/D conversion (when A/D clock source is RC).

- 7. Special event trigger (Timer1 in asynchronous mode using an external clock).

- 8. USART TX or RX (synchronous slave mode).

Other peripherals cannot generate interrupts since during SLEEP, no on-chip Q clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 14.8.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

# Applicable Devices 72 73 73A 74 74A 76 77

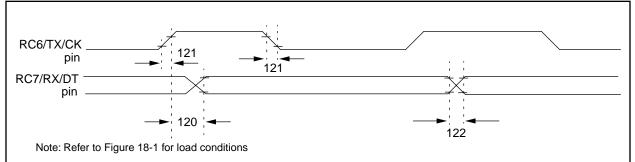

#### FIGURE 18-11: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 18-11: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Parameter<br>No. | Sym                                         | Characteristic                   |                       | Min | Тур† | Max | Units | Conditions |

|------------------|---------------------------------------------|----------------------------------|-----------------------|-----|------|-----|-------|------------|

| 120              | TckH2dtV                                    | SYNC XMIT (MASTER &<br>SLAVE)    | PIC16 <b>C</b> 73/74  | _   | _    | 80  | ns    |            |

|                  | Clock high to data out valid                | PIC16 <b>LC</b> 73/74            | _                     | —   | 100  | ns  |       |            |

| 121              | 121 Tckrf Clock out rise time and fall time |                                  | PIC16 <b>C</b> 73/74  | _   | —    | 45  | ns    |            |

|                  |                                             | (Master Mode)                    | PIC16 <b>LC</b> 73/74 | _   | —    | 50  | ns    |            |

| 122              | Tdtrf                                       | Data out rise time and fall time | PIC16 <b>C</b> 73/74  | _   | —    | 45  | ns    |            |

|                  |                                             |                                  | PIC16 <b>LC</b> 73/74 | _   | —    | 50  | ns    |            |

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

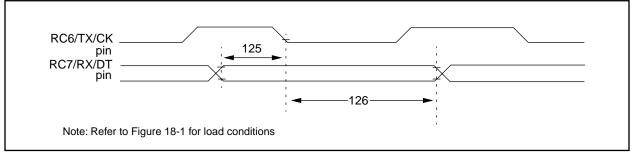

#### FIGURE 18-12: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 18-12: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                                 | Min | Тур† | Мах | Units | Conditions |

|------------------|----------|--------------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data setup before $CK \downarrow (DT setup time)$ | 15  |      | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                 | 15  | —    | —   | ns    |            |

+: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Applicable Devices

72

73

73A

74

76

77

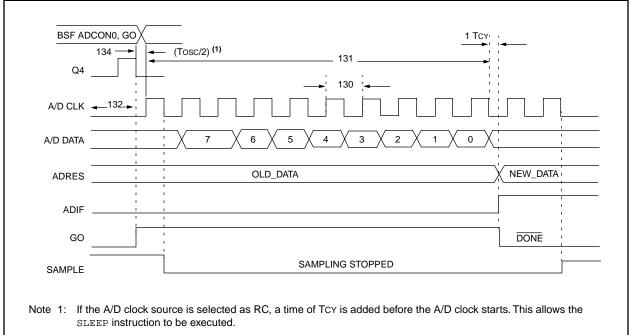

#### FIGURE 18-13: A/D CONVERSION TIMING

## TABLE 18-14: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym  | Characteristic                       |                      | Min    | Тур†     | Мах | Units | Conditions                                                                                                                                                                                                                 |

|--------------|------|--------------------------------------|----------------------|--------|----------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D clock period                     | PIC16 <b>C</b> 73/74 | 1.6    | —        |     | μs    | Tosc based, VREF ≥ 3.0V                                                                                                                                                                                                    |

|              |      |                                      | PIC16LC73/74         | 2.0    | —        |     | μs    | Tosc based, VREF full range                                                                                                                                                                                                |

|              |      |                                      | PIC16 <b>C</b> 73/74 | 2.0    | 4.0      | 6.0 | μs    | A/D RC Mode                                                                                                                                                                                                                |

|              |      |                                      | PIC16LC73/74         | 3.0    | 6.0      | 9.0 | μs    | A/D RC Mode                                                                                                                                                                                                                |

| 131          | TCNV | Conversion time (not inc<br>(Note 1) | luding S/H time)     | _      | 9.5      | —   | TAD   |                                                                                                                                                                                                                            |

| 132          | TACQ | Acquisition time                     |                      | Note 2 | 20       | _   | μs    |                                                                                                                                                                                                                            |

|              |      |                                      |                      | 5*     | _        | _   | μs    | The minimum time is the amplifier<br>settling time. This may be used if<br>the "new" input voltage has not<br>changed by more than 1 LSb (i.e.<br>20 mV @ 5.12V) from the last<br>sampled voltage (as stated on<br>CHOLD). |

| 134          | TGO  | Q4 to A/D clock start                |                      | _      | Tosc/2 § | _   | _     | If the A/D clock source is selected<br>as RC, a time of TCY is added<br>before the A/D clock starts. This<br>allows the SLEEP instruction to be<br>executed.                                                               |

| 135          | Tswc | Switching from convert               | → sample time        | 1.5 §  |          | _   | TAD   |                                                                                                                                                                                                                            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 13.1 for min conditions.

# Applicable Devices 72 73 73A 74 74A 76 77

## 19.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2p             | pS                                                | 3. Tcc:st       | (I <sup>2</sup> C specifications only) |

|-----------------------|---------------------------------------------------|-----------------|----------------------------------------|

| 2. TppS               |                                                   | 4. Ts           | (I <sup>2</sup> C specifications only) |

| Т                     |                                                   |                 |                                        |

| F                     | Frequency                                         | Т               | Time                                   |

| Lowerca               | ase letters (pp) and their meanings:              |                 |                                        |

| рр                    |                                                   |                 |                                        |

| сс                    | CCP1                                              | osc             | OSC1                                   |

| ck                    | CLKOUT                                            | rd              | RD                                     |

| CS                    | <u>CS</u>                                         | rw              | RD or WR                               |

| di                    | SDI                                               | sc              | SCK                                    |

| do                    | SDO                                               | SS              | SS                                     |

| dt                    | Data in                                           | tO              | ТОСКІ                                  |

| io                    | I/O port                                          | t1              | T1CKI                                  |

| mc                    | MCLR                                              | wr              | WR                                     |

| Upperca               | ase letters and their meanings:                   |                 |                                        |

| S                     |                                                   |                 |                                        |

| F                     | Fall                                              | Р               | Period                                 |

| н                     | High                                              | R               | Rise                                   |

| 1                     | Invalid (Hi-impedance)                            | V               | Valid                                  |

| L                     | Low                                               | Z               | Hi-impedance                           |

| I <sup>2</sup> C only |                                                   |                 |                                        |

| AA                    | output access                                     | High            | High                                   |

| BUF                   | Bus free                                          | Low             | Low                                    |

| Tcc:st (              | (I <sup>2</sup> C specifications only)            |                 |                                        |

| CC                    |                                                   |                 |                                        |

| HD                    | Hold                                              | SU              | Setup                                  |

| ST                    |                                                   |                 |                                        |

| DAT                   | DATA input hold                                   | STO             | STOP condition                         |

| STA                   | START condition                                   |                 |                                        |

| L                     | 9-1: LOAD CONDITIONS                              |                 |                                        |

|                       | Load condition 1                                  |                 | Load condition 2                       |

|                       |                                                   |                 |                                        |

|                       | VDD/2                                             |                 |                                        |

|                       | ✓ →                                               |                 |                                        |

|                       |                                                   |                 |                                        |

|                       | • • • • • • • • • • • • • • • • • • • •           | ſ               | "' ↓                                   |

|                       | Vss                                               |                 | Vss                                    |

|                       | $RL = 464\Omega$                                  |                 | -                                      |

|                       |                                                   |                 |                                        |

|                       | CL = 50 pF for all pins except OSC2, but in ports | ncluaing PORT   | D and FORTE outputs as                 |

|                       | 15 pF for OSC2 output                             |                 |                                        |

|                       | Note: PORTD and PORTE are not implement           | ted on the PIC1 | 6C73A.                                 |

Applicable Devices

72

73

73A

74

76

77

## 20.5 <u>Timing Diagrams and Specifications</u>

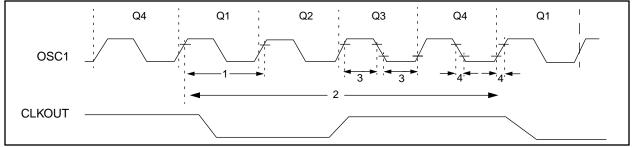

## FIGURE 20-2: EXTERNAL CLOCK TIMING

#### TABLE 20-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                   | Min | Тур† | Мах    | Units | Conditions                             |

|------------------|-------|----------------------------------|-----|------|--------|-------|----------------------------------------|

|                  | Fosc  | External CLKIN Frequency         | DC  |      | 4      | MHz   | XT and RC osc mode                     |

|                  |       | (Note 1)                         | DC  | _    | 4      | MHz   | HS osc mode (-04)                      |

|                  |       |                                  | DC  | _    | 10     | MHz   | HS osc mode (-10)                      |

|                  |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)                      |

|                  |       |                                  | DC  | _    | 200    | kHz   | LP osc mode                            |

|                  |       | Oscillator Frequency             | DC  |      | 4      | MHz   | RC osc mode                            |

|                  |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode                            |

|                  |       |                                  | 4   | _    | 20     | MHz   | HS osc mode                            |

|                  |       |                                  | 5   | —    | 200    | kHz   | LP osc mode                            |

| 1                | Tosc  | External CLKIN Period            | 250 | _    | —      | ns    | XT and RC osc mode                     |

|                  |       | (Note 1)                         | 250 | _    | _      | ns    | HS osc mode (-04)                      |

|                  |       |                                  | 100 | _    | _      | ns    | HS osc mode (-10)                      |

|                  |       |                                  | 50  | _    | _      | ns    | HS osc mode (-20)                      |

|                  |       |                                  | 5   | _    | _      | μs    | LP osc mode                            |

|                  |       | Oscillator Period                | 250 |      | _      | ns    | RC osc mode                            |

|                  |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode                            |

|                  |       |                                  | 250 | _    | 250    | ns    | HS osc mode (-04)                      |

|                  |       |                                  | 100 | —    | 250    | ns    | HS osc mode (-10)<br>HS osc mode (-20) |

|                  |       |                                  | 50  | —    | 250    | ns    |                                        |

|                  |       |                                  | 5   | _    | _      | μs    | LP osc mode                            |

| 2                | Тсү   | Instruction Cycle Time (Note 1)  | 200 | Тсү  | DC     | ns    | Tcy = 4/Fosc                           |

| 3                | TosL, | External Clock in (OSC1) High or | 100 | _    | _      | ns    | XT oscillator                          |

|                  | TosH  | Low Time                         | 2.5 | —    | _      | μs    | LP oscillator                          |

|                  |       |                                  | 15  | —    | _      | ns    | HS oscillator                          |

| 4                | TosR, | External Clock in (OSC1) Rise or | _   | _    | 25     | ns    | XT oscillator                          |

|                  | TosF  | Fall Time                        | _   | _    | 50     | ns    | LP oscillator                          |

|                  |       |                                  | _   | _    | 15     | ns    | HS oscillator                          |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

| PICSTART Low-Cost Development System    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIE1 Register                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PIE2 Register                           | 29, 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Pin Compatible Devices                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Pin Functions                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MCLR/VPP                                | 13, 14, 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OSC1/CLKIN                              | 13, 14, 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OSC2/CLKOUT                             | 13, 14, 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RA0/AN0                                 | 13, 14, 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RA1/AN1                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RA2/AN2                                 | 13, 14, 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RA3/AN3/VREF                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RA4/T0CKI                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RA5/AN4/SS                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RB0/INT                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RB1                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RB2                                     | 13. 14. 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RB3                                     | 13, 14, 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RB4                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RB5                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RB6                                     | , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RB7                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RC0/T1OSO/T1CKI                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RC1/T1OSI                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RC1/T1OSI/CCP2                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RC2/CCP1                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RC3/SCK/SCL                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RC4/SDI/SDA                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RC5/SDO                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RC6                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RC0/1A/CK14,                            | 10, 99-114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D07                                     | . 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RC7                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |