Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc76-04i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

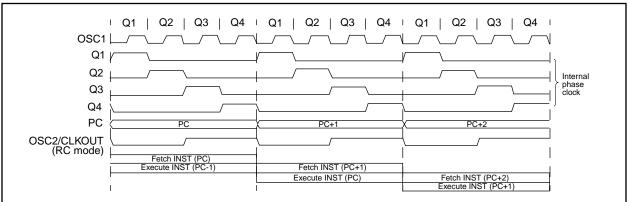

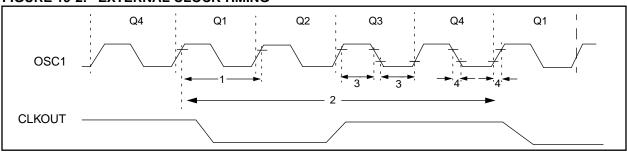

### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-4.

### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g. GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### FIGURE 3-4: CLOCK/INSTRUCTION CYCLE

### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

|                         | Тсу0        | Tcy1      | Tcy2      | Тсу3      | Tcy4        | Tcy5          |

|-------------------------|-------------|-----------|-----------|-----------|-------------|---------------|

| 1. MOVLW 55h            | Fetch 1     | Execute 1 |           |           |             |               |

| 2. MOVWF PORTB          |             | Fetch 2   | Execute 2 |           | _           |               |

| 3. CALL SUB_1           |             |           | Fetch 3   | Execute 3 |             |               |

| 4. BSF PORTA, BIT3 (F   | Forced NOP) |           |           | Fetch 4   | Flush       |               |

| 5. Instruction @ addres | s SUB_1     |           |           |           | Fetch SUB_1 | Execute SUB_1 |

|                         |             |           |           |           |             |               |

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

Example 4-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the interrupt service routine (if interrupts are used).

### EXAMPLE 4-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

| ORG 0x | 500      |                            |

|--------|----------|----------------------------|

| BSF    | pclath,3 | ;Select page 1 (800h-FFFh) |

| BCF    | pclath,4 | ;Only on >4K devices       |

| CALL   | SUB1_P1  | ;Call subroutine in        |

|        | :        | ;page 1 (800h-FFFh)        |

|        | :        |                            |

|        | :        |                            |

| ORG 0x | 900      |                            |

| SUB1_P | 1:       | ;called subroutine         |

|        | :        | ;page 1 (800h-FFFh)        |

|        | :        |                            |

| RETURN |          | ;return to Call subroutine |

|        |          | ;in page 0 (000h-7FFh)     |

|        |          |                            |

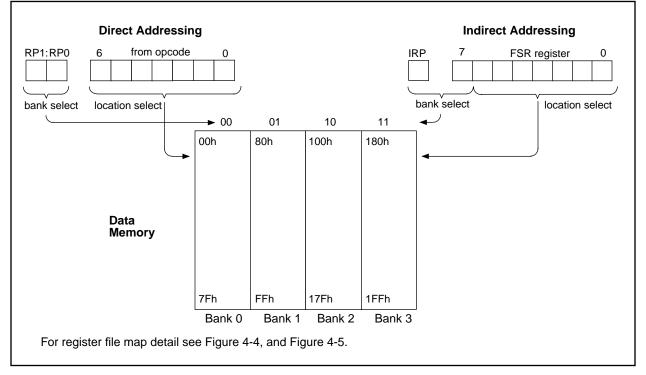

### 4.5 <u>Indirect Addressing, INDF and FSR</u> <u>Registers</u>

|    | •  | cabl |    |     |    |    |

|----|----|------|----|-----|----|----|

| 72 | 73 | 73A  | 74 | 74A | 76 | 77 |

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself indirectly (FSR = '0') will read 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-18.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 4-2.

### EXAMPLE 4-2: INDIRECT ADDRESSING

| NEXT     | movwf<br>clrf<br>incf | INDF<br>FSR,F | <pre>;initialize pointer ;to RAM ;clear INDF register ;inc pointer ;all done? ;no clear next</pre> |

|----------|-----------------------|---------------|----------------------------------------------------------------------------------------------------|

| CONTINUE |                       |               |                                                                                                    |

|          | :                     |               | ;yes continue                                                                                      |

### FIGURE 4-18: DIRECT/INDIRECT ADDRESSING

# 5.0 I/O PORTS Applicable Devices 72 73 73A 74 74A 76 77

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

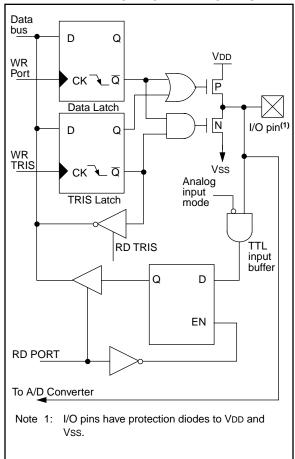

# 5.1 PORTA and TRISA Registers Applicable Devices 72 73 73A 74 74A 76 77

### PORTA is a 6-bit latch.

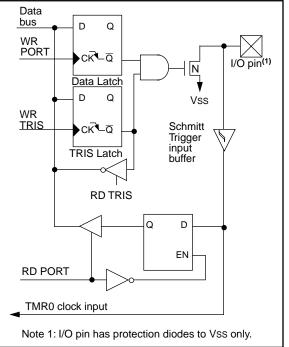

The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as output or input.

Setting a TRISA register bit puts the corresponding output driver in a hi-impedance mode. Clearing a bit in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

Note: On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

### EXAMPLE 5-1: INITIALIZING PORTA

| BCF   | STATUS, | RP0 | ; |                       |

|-------|---------|-----|---|-----------------------|

| BCF   | STATUS, | RP1 | ; | PIC16C76/77 only      |

| CLRF  | PORTA   |     | ; | Initialize PORTA by   |

|       |         |     | ; | clearing output       |

|       |         |     | ; | data latches          |

| BSF   | STATUS, | RP0 | ; | Select Bank 1         |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISA   |     | ; | Set RA<3:0> as inputs |

|       |         |     | ; | RA<5:4> as outputs    |

|       |         |     | ; | TRISA<7:6> are always |

|       |         |     | ; | read as '0'.          |

|       |         |     |   |                       |

### FIGURE 5-1: BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

### FIGURE 5-2: BLOCK DIAGRAM OF RA4/ T0CKI PIN

NOTES:

# 8.5 <u>Resetting Timer1 using a CCP Trigger</u> Output

# Applicable Devices

The CCP2 module is not implemented on the PIC16C72 device.

If the CCP1 or CCP2 module is configured in compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer1.

| Note: | The special event triggers from the CCP1 |

|-------|------------------------------------------|

|       | and CCP2 modules will not set interrupt  |

|       | flag bit TMR1IF (PIR1<0>).               |

Timer1 must be configured for either timer or synchronized counter mode to take advantage of this feature. If Timer1 is running in asynchronous counter mode, this reset operation may not work.

In the event that a write to Timer1 coincides with a special event trigger from CCP1 or CCP2, the write will take precedence.

In this mode of operation, the CCPRxH:CCPRxL registers pair effectively becomes the period register for Timer1.

### 8.6 Resetting of Timer1 Register Pair (TMR1H, TMR1L) Applicable Devices 72|73|73A|74|74A|76|77

TMR1H and TMR1L registers are not reset to 00h on a POR or any other reset except by the CCP1 and CCP2 special event triggers.

T1CON register is reset to 00h on a Power-on Reset or a Brown-out Reset, which shuts off the timer and leaves a 1:1 prescale. In all other resets, the register is unaffected.

### 8.7 <u>Timer1 Prescaler</u> Applicable Devices

72 73 73A 74 74A 76 77

The prescaler counter is cleared on writes to the TMR1H or TMR1L registers.

| Address               | Name   | Bit 7                  | Bit 6                                                                       | Bit 5               | Bit 4               | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|-----------------------|--------|------------------------|-----------------------------------------------------------------------------|---------------------|---------------------|---------|--------|--------|--------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                    | PEIE                                                                        | TOIE                | INTE                | RBIE    | TOIF   | INTF   | RBIF   | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1   | PSPIF <sup>(1,2)</sup> | ADIF                                                                        | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | SSPIF   | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 8Ch                   | PIE1   | PSPIE <sup>(1,2)</sup> | ADIE                                                                        | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup> | SSPIE   | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 0Eh                   | TMR1L  | Holding reg            | Holding register for the Least Significant Byte of the 16-bit TMR1 register |                     |                     |         |        |        |        |                          | uuuu uuuu                       |

| 0Fh                   | TMR1H  | Holding reg            | Holding register for the Most Significant Byte of the 16-bit TMR1 register  |                     |                     |         |        |        |        |                          | uuuu uuuu                       |

| 10h                   | T1CON  | _                      | _                                                                           | T1CKPS1             | T1CKPS0             | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 00 0000                  | uu uuuu                         |

### TABLE 8-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

2: The PIC16C72 does not have a Parallel Slave Port or a USART, these bits are unimplemented, read as '0'.

### 10.3 <u>PWM Mode</u>

Applicable Devices

In Pulse Width Modulation (PWM) mode, the CCPx pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

Note: Clearing the CCP1CON register will force the CCP1 PWM output latch to the default low level. This is not the PORTC I/O data latch.

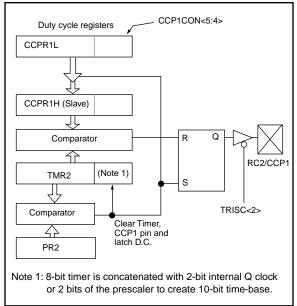

Figure 10-4 shows a simplified block diagram of the CCP module in PWM mode.

For a step by step procedure on how to set up the CCP module for PWM operation, see Section 10.3.3.

### FIGURE 10-4: SIMPLIFIED PWM BLOCK DIAGRAM

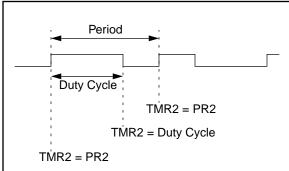

A PWM output (Figure 10-5) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

### FIGURE 10-5: PWM OUTPUT

### 10.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

PWM period = [(PR2) + 1] • 4 • TOSC • (TMR2 prescale value)

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

| Note: | The Timer2 postscaler (see Section 9.1) is   |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|

|       | not used in the determination of the PWM     |  |  |  |  |  |  |

|       | frequency. The postscaler could be used to   |  |  |  |  |  |  |

|       | have a servo update rate at a different fre- |  |  |  |  |  |  |

|       | quency than the PWM output.                  |  |  |  |  |  |  |

#### 10.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available: the CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

### PWM duty cycle = (CCPR1L:CCP1CON<5:4>) • Tosc • (TMR2 prescale value)

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2 concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

Maximum PWM resolution (bits) for a given PWM frequency:

$$= \frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log(2)} \quad \text{bits}$$

Note: If the PWM duty cycle value is longer than the PWM period the CCP1 pin will not be cleared.

### 11.3 SPI Mode for PIC16C76/77

Γ

This section contains register definitions and operational characteristics of the SPI module on the PIC16C76 and PIC16C77 only.

### FIGURE 11-7: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS 94h)(PIC16C76/77)

| R/W-0  | R/W-0                                                                                                                                                                                                                                                                                                                                                | R-0                                                         | R-0                                          | R-0                                                    | R-0            | R-0          | R-0          |                                                                                      |  |  |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------|----------------|--------------|--------------|--------------------------------------------------------------------------------------|--|--|--|--|--|

| SMP    | CKE                                                                                                                                                                                                                                                                                                                                                  | D/Ā                                                         | Р                                            | S                                                      | R/W            | UA           | BF           | R = Readable bit                                                                     |  |  |  |  |  |

| bit7   |                                                                                                                                                                                                                                                                                                                                                      |                                                             |                                              |                                                        |                |              | bit0         | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset |  |  |  |  |  |

| bit 7: | SMP: SPI data input sample phase         SPI Master Mode         1 = Input data sampled at end of data output time         0 = Input data sampled at middle of data output time         SPI Slave Mode         SMP must be cleared when SPI is used in slave mode                                                                                    |                                                             |                                              |                                                        |                |              |              |                                                                                      |  |  |  |  |  |

| bit 6: | $\frac{CKP = 0}{1 = Data}$ $0 = Data$ $\frac{CKP = 1}{1 = Data}$                                                                                                                                                                                                                                                                                     | <u>0</u><br>a transmi<br>a transmi<br><u>1</u><br>a transmi | itted on ris<br>itted on fal<br>itted on fal | ing edge of<br>ling edge o<br>ling edge o              | f SCK<br>f SCK | e 11-12, and | d Figure 11- | 13)                                                                                  |  |  |  |  |  |

| bit 5: | <ul> <li>0 = Data transmitted on rising edge of SCK</li> <li>D/Ā: Data/Address bit (I<sup>2</sup>C mode only)</li> <li>1 = Indicates that the last byte received or transmitted was data</li> <li>0 = Indicates that the last byte received or transmitted was address</li> </ul>                                                                    |                                                             |                                              |                                                        |                |              |              |                                                                                      |  |  |  |  |  |

| bit 4: | <ul> <li>P: Stop bit (I<sup>2</sup>C mode only. This bit is cleared when the SSP module is disabled, or when the Start bit is detected last, SSPEN is cleared)</li> <li>1 = Indicates that a stop bit has been detected last (this bit is '0' on RESET)</li> <li>0 = Stop bit was not detected last</li> </ul>                                       |                                                             |                                              |                                                        |                |              |              |                                                                                      |  |  |  |  |  |

| bit 3: | detecte<br>1 = Indi                                                                                                                                                                                                                                                                                                                                  | d last, SS<br>cates tha                                     | SPEN is clo<br>it a start bi                 | eared)<br>t has been                                   | cleared whe    |              |              | lisabled, or when the Stop bit is                                                    |  |  |  |  |  |

| bit 2: | <ul> <li>0 = Start bit was not detected last</li> <li><b>R/W</b>: Read/Write bit information (I<sup>2</sup>C mode only)</li> <li>This bit holds the R/W bit information following the last address match. This bit is only valid from the address match to the next start bit, stop bit, or ACK bit.</li> <li>1 = Read</li> <li>0 = Write</li> </ul> |                                                             |                                              |                                                        |                |              |              |                                                                                      |  |  |  |  |  |

| bit 1: | 1 = Indi                                                                                                                                                                                                                                                                                                                                             | cates tha                                                   | t the user                                   | it I <sup>2</sup> C mode<br>needs to u<br>I to be upda | pdate the ad   | dress in the | e SSPADD re  | egister                                                                              |  |  |  |  |  |

| bit 0: | BF: Buf                                                                                                                                                                                                                                                                                                                                              | fer Full S                                                  | tatus bit                                    |                                                        |                |              |              |                                                                                      |  |  |  |  |  |

|        | 1 = Rec<br>0 = Rec                                                                                                                                                                                                                                                                                                                                   | eive com<br>eive not                                        | complete,                                    | es)<br>PBUF is ful<br>SSPBUF is                        |                |              |              |                                                                                      |  |  |  |  |  |

|        | 1 = Trar                                                                                                                                                                                                                                                                                                                                             |                                                             | rogress, S                                   | SPBUF is t<br>PBUF is en                               |                |              |              |                                                                                      |  |  |  |  |  |

٦

### 11.5.1.2 RECEPTION

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no acknowledge ( $\overline{ACK}$ ) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set. An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

# FIGURE 11-25: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

| Receiving Address         R/W           SDA         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - | =0Receiving Data<br>' <sup>ACK</sup> /D7XD6XD5XD4XD3XD2XD1XE<br> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| SSPIF (PIR1<3>)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Cleared in software                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Bus Master<br>terminates<br>transfer |

| SSPOV (SSPCON<6>)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Bit SSPOV is set b                                               | ecause the SSPBUF register is still free and the second structure of the second second structure of the second sec |                                      |

### TABLE 12-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address | Name  | Bit 7                | Bit 6     | Bit 5   | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|-------|----------------------|-----------|---------|-----------|-----------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF      | RCIF    | TXIF      | SSPIF     | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA | SPEN                 | RX9       | SREN    | CREN      | _         | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                 |

| 19h     | TXREG | USART Tra            | ansmit Re | egister |           |           |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE      | RCIE    | TXIE      | SSPIE     | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA | CSRC                 | TX9       | TXEN    | SYNC      | _         | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | SPBRG | Baud Rate            | Generat   |         | 0000 0000 | 0000 0000 |        |        |        |                          |                           |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for Synchronous Master Transmission. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

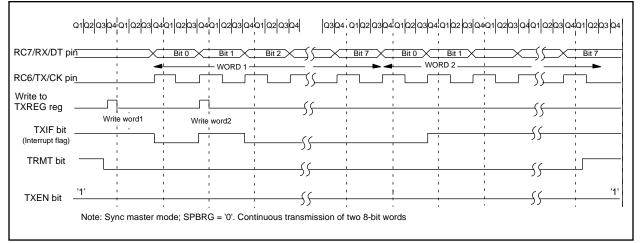

### FIGURE 12-12: SYNCHRONOUS TRANSMISSION

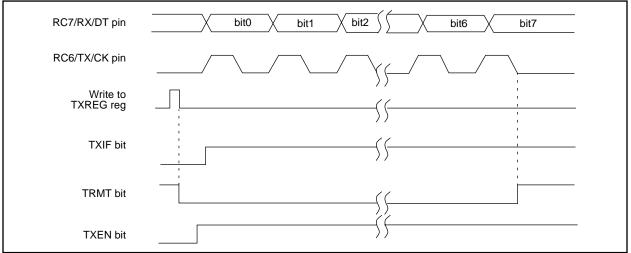

### FIGURE 12-13: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

### 12.4 USART Synchronous Slave Mode

# Applicable Devices 72 73 73A 74 74A 76 77

Synchronous slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

### 12.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the synchronous master and slave modes are identical except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

### 12.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the synchronous master and slave modes is identical except in the case of the SLEEP mode. Also, bit SREN is a don't care in slave mode.

If receive is enabled, by setting bit CREN, prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Reception:

- 1. Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, then set enable bit RCIE.

- 3. If 9-bit reception is desired, then set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- 6. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

### 14.4 Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST), and Brown-out Reset (BOR) Applicable Devices 72 73 73 74 74 76 77

### 14.4.1 POWER-ON RESET (POR)

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.5V - 2.1V). To take advantage of the POR, just tie the  $\overline{MCLR}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met. Brown-out Reset may be used to meet the startup conditions.

For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting.*"

#### 14.4.2 POWER-UP TIMER (PWRT)

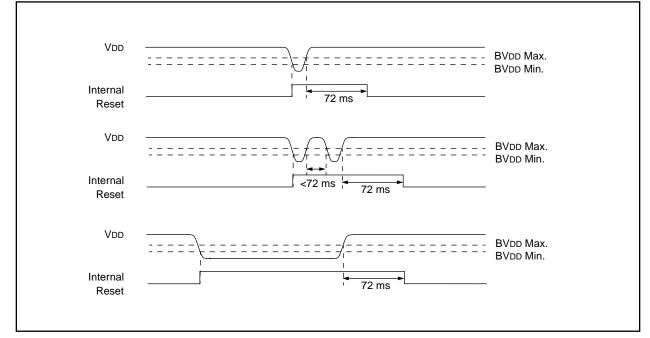

The Power-up Timer provides a fixed 72 ms nominal time-out on power-up only, from the POR. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as the PWRT is active. The PWRT's time delay allows VDD to rise to an acceptable level. A configuration bit is provided to enable/disable the PWRT.

The power-up time delay will vary from chip to chip due to VDD, temperature, and process variation. See DC parameters for details.

#### 14.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from SLEEP.

# 14.4.4 BROWN-OUT RESET (BOR) Applicable Devices 72 73 73 74 74 76 77

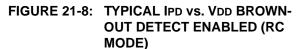

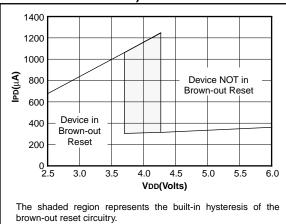

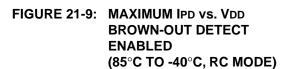

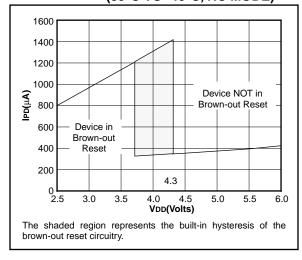

A configuration bit, BODEN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V (3.8V - 4.2V range) for greater than parameter #35, the brown-out situation will reset the chip. A reset may not occur if VDD falls below 4.0V for less than parameter #35. The chip will remain in Brown-out Reset until VDD rises above BVDD. The Power-up Timer will now be invoked and will keep the chip in RESET an additional 72 ms. If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above BVDD, the Power-up Timer will execute a 72 ms time delay. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 14-9 shows typical brown-out situations.

### FIGURE 14-9: BROWN-OUT SITUATIONS

### Applicable Devices 72 73 73A 74 74A 76 77

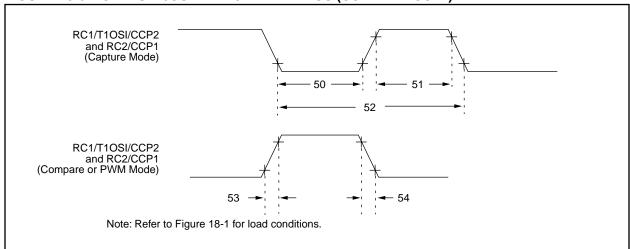

### FIGURE 18-6: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

### TABLE 18-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Parameter<br>No. | Sym                                     | Characteristic             |                      |                       | Min                   | Тур† | Max | Units | Conditions                        |

|------------------|-----------------------------------------|----------------------------|----------------------|-----------------------|-----------------------|------|-----|-------|-----------------------------------|

| 50*              | TccL                                    | CCP1 and CCP2              | No Prescaler         |                       | 0.5Tcy + 20           | —    | _   | ns    |                                   |

|                  |                                         | input low time             |                      | PIC16 <b>C</b> 73/74  | 10                    | _    | _   | ns    |                                   |

|                  |                                         |                            | With Prescaler       | PIC16 <b>LC</b> 73/74 | 20                    | —    | _   | ns    |                                   |

| 51*              | TccH                                    | CCP1 and CCP2              | No Prescaler         |                       | 0.5Tcy + 20           | —    | —   | ns    |                                   |

|                  |                                         | input high time            | With Prescaler       | PIC16 <b>C</b> 73/74  | 10                    |      | -   | ns    |                                   |

|                  |                                         |                            |                      | PIC16 <b>LC</b> 73/74 | 20                    | —    | _   | ns    |                                   |

| 52*              | TccP                                    | CCP1 and CCP2 input period |                      |                       | <u>3Tcy + 40</u><br>N | _    | _   | ns    | N = prescale value<br>(1,4 or 16) |

| 53*              | TccR                                    | CCP1 and CCP2 of           | output fall time     | PIC16 <b>C</b> 73/74  | _                     | 10   | 25  | ns    |                                   |

|                  |                                         |                            |                      | PIC16 <b>LC</b> 73/74 | _                     | 25   | 45  | ns    |                                   |

| 54*              | 54* TccF CCP1 and CCP2 output fall time |                            | PIC16 <b>C</b> 73/74 | _                     | 10                    | 25   | ns  |       |                                   |

|                  |                                         |                            |                      | PIC16 <b>LC</b> 73/74 | _                     | 25   | 45  | ns    |                                   |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# Applicable Devices 72 73 73A 74 74A 76 77

### 19.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2p             | pS                                                | 3. Tcc:st       | (I <sup>2</sup> C specifications only) |

|-----------------------|---------------------------------------------------|-----------------|----------------------------------------|

| 2. TppS               |                                                   | 4. Ts           | (I <sup>2</sup> C specifications only) |

| Т                     |                                                   |                 |                                        |

| F                     | Frequency                                         | Т               | Time                                   |

| Lowerca               | ase letters (pp) and their meanings:              |                 |                                        |

| рр                    |                                                   |                 |                                        |

| сс                    | CCP1                                              | osc             | OSC1                                   |

| ck                    | CLKOUT                                            | rd              | RD                                     |

| CS                    | <u>CS</u>                                         | rw              | RD or WR                               |

| di                    | SDI                                               | sc              | SCK                                    |

| do                    | SDO                                               | SS              | SS                                     |

| dt                    | Data in                                           | tO              | ТОСКІ                                  |

| io                    | I/O port                                          | t1              | T1CKI                                  |

| mc                    | MCLR                                              | wr              | WR                                     |

| Upperca               | ase letters and their meanings:                   |                 |                                        |

| S                     |                                                   |                 |                                        |

| F                     | Fall                                              | Р               | Period                                 |

| н                     | High                                              | R               | Rise                                   |

| 1                     | Invalid (Hi-impedance)                            | V               | Valid                                  |

| L                     | Low                                               | Z               | Hi-impedance                           |

| I <sup>2</sup> C only |                                                   |                 |                                        |

| AA                    | output access                                     | High            | High                                   |

| BUF                   | Bus free                                          | Low             | Low                                    |

| Tcc:st (              | (I <sup>2</sup> C specifications only)            |                 |                                        |

| CC                    |                                                   |                 |                                        |

| HD                    | Hold                                              | SU              | Setup                                  |

| ST                    |                                                   |                 |                                        |

| DAT                   | DATA input hold                                   | STO             | STOP condition                         |

| STA                   | START condition                                   |                 |                                        |

| L                     | 9-1: LOAD CONDITIONS                              |                 |                                        |

|                       | Load condition 1                                  |                 | Load condition 2                       |

|                       |                                                   |                 |                                        |

|                       | VDD/2                                             |                 |                                        |

|                       | ✓ →                                               |                 |                                        |

|                       |                                                   |                 |                                        |

|                       | • • • • • • • • • • • • • • • • • • • •           | ſ               | "' ↓                                   |

|                       | Vss                                               |                 | Vss                                    |

|                       | $RL = 464\Omega$                                  |                 | -                                      |

|                       |                                                   |                 |                                        |

|                       | CL = 50 pF for all pins except OSC2, but in ports | ncluaing PORT   | D and FORTE outputs as                 |

|                       | 15 pF for OSC2 output                             |                 |                                        |

|                       | Note: PORTD and PORTE are not implement           | ted on the PIC1 | 6C73A.                                 |

### Applicable Devices 72 73 73A 74 74A 76 77

### 19.5 <u>Timing Diagrams and Specifications</u>

### FIGURE 19-2: EXTERNAL CLOCK TIMING

### TABLE 19-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| arameter<br>No. | Sym      | Characteristic                   | Min | Тур† | Max    | Units | Conditions         |

|-----------------|----------|----------------------------------|-----|------|--------|-------|--------------------|

|                 | Fosc     | External CLKIN Frequency         | DC  | _    | 4      | MHz   | XT and RC osc mode |

|                 | (Note 1) |                                  | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|                 |          |                                  | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|                 |          |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|                 |          |                                  | DC  | _    | 200    | kHz   | LP osc mode        |

|                 |          | Oscillator Frequency             | DC  | _    | 4      | MHz   | RC osc mode        |

|                 |          | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode        |

|                 |          |                                  | 4   | _    | 20     | MHz   | HS osc mode        |

|                 |          |                                  | 5   | —    | 200    | kHz   | LP osc mode        |

| 1               | Tosc     | External CLKIN Period            | 250 | —    | —      | ns    | XT and RC osc mode |

|                 |          | (Note 1)                         | 250 | —    | —      | ns    | HS osc mode (-04)  |

|                 |          |                                  | 100 | —    | _      | ns    | HS osc mode (-10)  |

|                 |          |                                  | 50  | —    | —      | ns    | HS osc mode (-20)  |

|                 |          |                                  | 5   | _    | _      | μs    | LP osc mode        |

|                 |          | Oscillator Period                | 250 | _    | _      | ns    | RC osc mode        |

|                 |          | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode        |

|                 |          |                                  | 250 | _    | 250    | ns    | HS osc mode (-04)  |

|                 |          |                                  | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|                 |          |                                  | 50  | —    | 250    | ns    | HS osc mode (-20)  |

|                 |          |                                  | 5   | _    | —      | μs    | LP osc mode        |

| 2               | Тсү      | Instruction Cycle Time (Note 1)  | 200 | Тсү  | DC     | ns    | TCY = 4/FOSC       |

| 3               | TosL,    | External Clock in (OSC1) High or | 100 | _    | _      | ns    | XT oscillator      |

|                 | TosH     | Low Time                         | 2.5 | —    | _      | μs    | LP oscillator      |

|                 |          |                                  | 15  | _    | _      | ns    | HS oscillator      |

| 4               | TosR,    | External Clock in (OSC1) Rise or | _   | _    | 25     | ns    | XT oscillator      |

|                 | TosF     | Fall Time                        | _   | _    | 50     | ns    | LP oscillator      |

|                 |          |                                  | _   | _    | 15     | ns    | HS oscillator      |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

# Applicable Devices 72 73 73A 74 74A 76 77

# 20.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2              | ppS                                               | 3. Tcc:st      | (I <sup>2</sup> C specifications only) |

|-----------------------|---------------------------------------------------|----------------|----------------------------------------|

| 2. TppS               |                                                   | 4. Ts          | (I <sup>2</sup> C specifications only) |

| Т                     |                                                   |                |                                        |

| F                     | Frequency                                         | Т              | Time                                   |

| Lowerc                | case letters (pp) and their meanings:             |                |                                        |

| рр                    |                                                   |                |                                        |

| сс                    | CCP1                                              | osc            | OSC1                                   |

| ck                    |                                                   | rd             | RD                                     |

| CS                    | CS                                                | rw             | RD or WR                               |

| di                    | SDI                                               | SC             | SCK                                    |

| do                    | SDO                                               | SS             | SS                                     |

| dt                    | Data in                                           | t0             | TOCKI                                  |

| io                    | I/O port                                          | t1             | T1CKI                                  |

| mc                    | MCLR                                              | wr             | WR                                     |

|                       | case letters and their meanings:                  |                |                                        |

| S                     | <b>F</b> _1                                       |                | Period                                 |

| F                     | Fall                                              | P              |                                        |

| H                     | High                                              | R<br>V         | Rise<br>Valid                          |

|                       | Invalid (Hi-impedance)<br>Low                     | Z              | Hi-impedance                           |

|                       | LOW                                               | 2              | I II-IIIpedance                        |

| I <sup>2</sup> C only |                                                   |                |                                        |

| AA                    | output access                                     | High           | High                                   |

| BUF                   | Bus free                                          | Low            | Low                                    |

|                       | (I <sup>2</sup> C specifications only)            |                |                                        |

| CC                    |                                                   | 0.1            |                                        |

| HD                    | Hold                                              | SU             | Setup                                  |

| ST                    |                                                   | OTO            |                                        |

| DAT<br>STA            | DATA input hold<br>START condition                | STO            | STOP condition                         |

|                       |                                                   |                |                                        |

| FIGURE                | 20-1: LOAD CONDITIONS                             |                |                                        |

|                       | Load condition 1                                  |                | Load condition 2                       |

|                       | $VDD/2$ $RL$ $Pin$ $CL$ $Vss$ $RL = 464\Omega$    | F              | Din CL<br>VSS                          |

|                       |                                                   |                |                                        |

|                       | CL = 50 pF for all pins except OSC2, but in ports |                |                                        |

|                       | 15 pF for OSC2 output                             |                |                                        |

|                       | Note: PORTD and PORTE are not implement           | ed on the PIC1 | 16C76.                                 |

# PIC16C7X

Applicable Devices 72 73 73A 74 74A 76 77

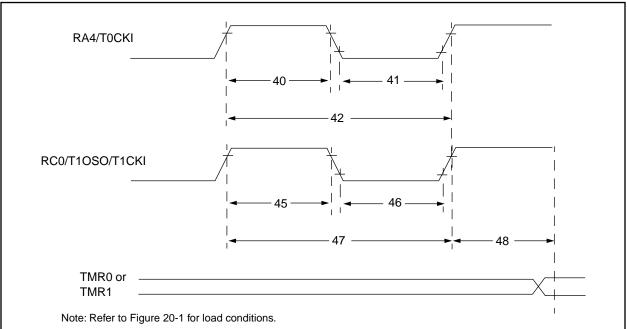

### TABLE 20-5: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym                | Characteristic                                 |                      |                                                  | Min                                              | Тур† | Max   | Units                             | Conditions                        |

|--------------|--------------------|------------------------------------------------|----------------------|--------------------------------------------------|--------------------------------------------------|------|-------|-----------------------------------|-----------------------------------|

| 40*          | Tt0H               | T0CKI High Pulse V                             | Vidth                | No Prescaler                                     | 0.5TCY + 20                                      | -    | —     | ns                                | Must also meet                    |

|              |                    |                                                |                      | With Prescaler                                   | 10                                               | -    | _     | ns                                | parameter 42                      |

| 41*          | Tt0L               | T0CKI Low Pulse W                              | /idth                | No Prescaler                                     | 0.5TCY + 20                                      | -    | —     | ns                                | Must also meet                    |

|              |                    |                                                |                      | With Prescaler                                   | 10                                               | -    | —     | ns                                | parameter 42                      |

| 42*          | Tt0P               | T0CKI Period                                   |                      | No Prescaler                                     | Tcy + 40                                         | -    | —     | ns                                |                                   |

|              |                    |                                                |                      | With Prescaler                                   | Greater of:<br>20 or <u>Tcy + 40</u><br>N        | -    | —     | ns                                | N = prescale valu<br>(2, 4,, 256) |

| 45*          | Tt1H               | T1CKI High Time                                | Synchronous, F       | Prescaler = 1                                    | 0.5TCY + 20                                      | - 1  | _     | ns                                | Must also meet                    |

|              |                    | L C                                            | Synchronous,         | PIC16 <b>C</b> 7X                                | 15                                               | - 1  | _     | ns                                | parameter 47                      |

|              |                    | Prescaler = 2,4,8                              | PIC16 <b>LC</b> 7X   | 25                                               | -                                                | —    | ns    |                                   |                                   |

|              |                    |                                                | Asynchronous         | PIC16 <b>C</b> 7X                                | 30                                               | -    | —     | ns                                |                                   |

|              |                    |                                                |                      | PIC16 <b>LC</b> 7X                               | 50                                               | -    | —     | ns                                |                                   |

| 46*          | Tt1L               | T1CKI Low Time                                 | Synchronous, F       | Prescaler = 1                                    | 0.5TCY + 20                                      | -    | —     | ns                                | Must also meet                    |

|              |                    |                                                | Synchronous,         | PIC16 <b>C</b> 7X                                | 15                                               | —    | —     | ns                                | parameter 47                      |

|              |                    |                                                | Prescaler =<br>2,4,8 | PIC16 <b>LC</b> 7X                               | 25                                               | -    | —     | ns                                |                                   |

|              |                    |                                                | Asynchronous         | PIC16 <b>C</b> 7X                                | 30                                               | —    | —     | ns                                |                                   |

|              |                    |                                                |                      | PIC16 <b>LC</b> 7X                               | 50                                               | —    | —     | ns                                |                                   |

| 47* Tt1P     | T1CKI input period | Synchronous                                    | PIC16 <b>C</b> 7X    | <u>Greater of:</u><br>30 OR <u>TCY + 40</u><br>N | -                                                |      | ns    | N = prescale valu<br>(1, 2, 4, 8) |                                   |

|              |                    |                                                |                      | PIC16 <b>LC</b> 7X                               | <u>Greater of:</u><br>50 OR <u>TCY + 40</u><br>N |      |       |                                   | N = prescale valu<br>(1, 2, 4, 8) |

|              |                    |                                                | Asynchronous         | PIC16 <b>C</b> 7X                                | 60                                               | - 1  | -     | ns                                |                                   |

|              |                    |                                                |                      | PIC16 <b>LC</b> 7X                               | 100                                              | -    | —     | ns                                |                                   |

|              | Ft1                | Timer1 oscillator inp<br>(oscillator enabled b |                      |                                                  | DC                                               | -    | 200   | kHz                               |                                   |

| 48           | TCKEZtmr           | 1 Delay from external                          | clock edge to tir    | ner increment                                    | 2Tosc                                            | _    | 7Tosc | —                                 |                                   |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

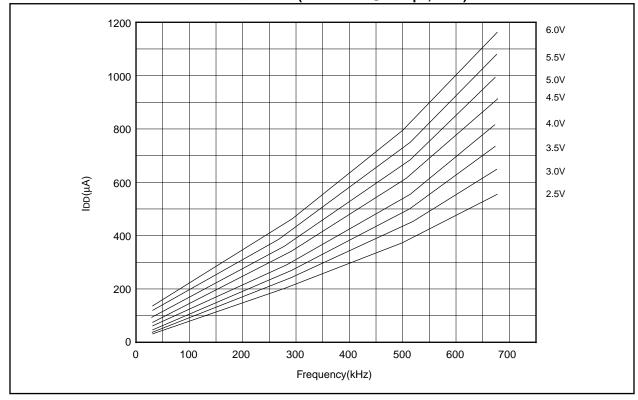

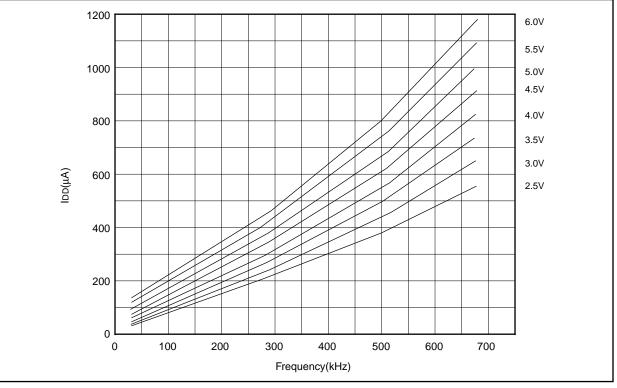

# Applicable Devices 72 73 73 74 74 76 77 FIGURE 21-16: TYPICAL IDD vs. FREQUENCY (RC MODE @ 300 pF, 25°C)

FIGURE 21-17: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 300 pF, -40°C TO 85°C)

Data based on matrix samples. See first page of this section for details.

# PIC16C7X

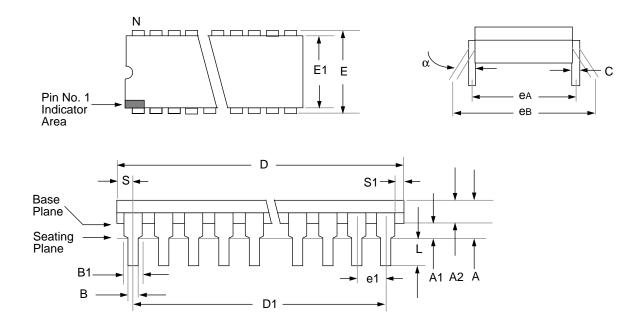

# 22.4 40-Lead Plastic Dual In-line (600 mil) (P)

| Package Group: Plastic Dual In-Line (PLA) |             |        |           |            |       |           |

|-------------------------------------------|-------------|--------|-----------|------------|-------|-----------|

|                                           | Millimeters |        |           |            |       |           |

| Symbol                                    | Min         | Мах    | Notes     | Min        | Max   | Notes     |

| α                                         | 0°          | 10°    |           | <b>0</b> ° | 10°   |           |

| А                                         | _           | 5.080  |           | _          | 0.200 |           |

| A1                                        | 0.381       | _      |           | 0.015      | -     |           |

| A2                                        | 3.175       | 4.064  |           | 0.125      | 0.160 |           |