Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | A/D 5x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc76t-04-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

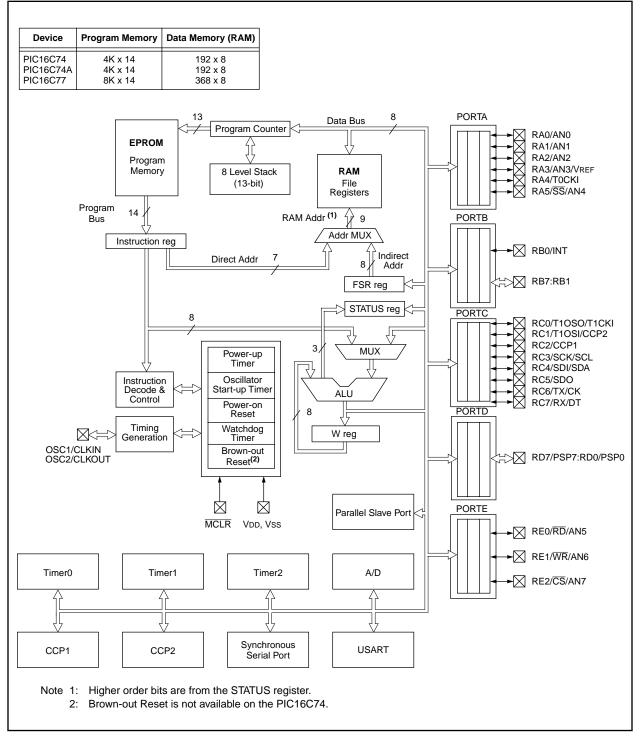

# FIGURE 3-3: PIC16C74/74A/77 BLOCK DIAGRAM

4.2.2.4 PIE1 REGISTER

Applicable Devices

72 73 73A 74 74A 76 77

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

This register contains the individual enable bits for the peripheral interrupts.

# FIGURE 4-10: PIE1 REGISTER PIC16C72 (ADDRESS 8Ch)

| U-0      | R/W-0                                                                                                                                                 | U-0       | U-0                                      | R/W-0      | R/W-0  | R/W-0  | R/W-0  |                                                                                                                        |  |  |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------------------|------------|--------|--------|--------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|          | ADIE                                                                                                                                                  | _         | —                                        | SSPIE      | CCP1IE | TMR2IE | TMR1IE | R = Readable bit                                                                                                       |  |  |  |  |  |  |

| bit7     |                                                                                                                                                       |           |                                          |            |        |        | bit0   | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>- n = Value at POR reset</li> </ul> |  |  |  |  |  |  |

| bit 7:   | Unimplemented: Read as '0'                                                                                                                            |           |                                          |            |        |        |        |                                                                                                                        |  |  |  |  |  |  |

| bit 6:   | ADIE: A/D Converter Interrupt Enable bit<br>1 = Enables the A/D interrupt<br>0 = Disables the A/D interrupt                                           |           |                                          |            |        |        |        |                                                                                                                        |  |  |  |  |  |  |

| bit 5-4: | Unimplemented: Read as '0'                                                                                                                            |           |                                          |            |        |        |        |                                                                                                                        |  |  |  |  |  |  |

| bit 3:   | <b>SSPIE</b> : Synchronous Serial Port Interrupt Enable bit<br>1 = Enables the SSP interrupt<br>0 = Disables the SSP interrupt                        |           |                                          |            |        |        |        |                                                                                                                        |  |  |  |  |  |  |

| bit 2:   | <b>CCP1IE</b> : 0<br>1 = Enabl<br>0 = Disab                                                                                                           | es the CC | P1 interru                               | pt         |        |        |        |                                                                                                                        |  |  |  |  |  |  |

| bit 1:   | <b>TMR2IE</b> : TMR2 to PR2 Match Interrupt Enable bit<br>1 = Enables the TMR2 to PR2 match interrupt<br>0 = Disables the TMR2 to PR2 match interrupt |           |                                          |            |        |        |        |                                                                                                                        |  |  |  |  |  |  |

| bit 0:   | 1 = Enabl                                                                                                                                             | es the TM | erflow Inte<br>R1 overflo<br>IR1 overflo | w interrup | ot     |        |        |                                                                                                                        |  |  |  |  |  |  |

# FIGURE 4-11: PIE1 REGISTER PIC16C73/73A/74/74A/76/77 (ADDRESS 8Ch)

| PSPIE <sup>(1)</sup> | ADIE                                                                                                                                       | RCIE                                  | TXIE       | SSPIE       | CCP1IE      | TMR2IE       | TMR1IE    | R      | = Readable bit                                                                                           |  |  |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------|-------------|-------------|--------------|-----------|--------|----------------------------------------------------------------------------------------------------------|--|--|--|--|

| bit7                 | 1                                                                                                                                          |                                       |            |             |             |              | bit0      | U      | <ul> <li>Writable bit</li> <li>Unimplemented bit,<br/>read as '0'</li> <li>Value at POR reset</li> </ul> |  |  |  |  |

| bit 7:               | 1 = Enabl                                                                                                                                  | Parallel S<br>es the PS<br>les the PS | P read/wr  | te interrup |             | Enable bit   |           |        |                                                                                                          |  |  |  |  |

| bit 6:               | ADIE: A/D Converter Interrupt Enable bit<br>1 = Enables the A/D interrupt<br>0 = Disables the A/D interrupt                                |                                       |            |             |             |              |           |        |                                                                                                          |  |  |  |  |

| bit 5:               | <b>RCIE</b> : USART Receive Interrupt Enable bit<br>1 = Enables the USART receive interrupt<br>0 = Disables the USART receive interrupt    |                                       |            |             |             |              |           |        |                                                                                                          |  |  |  |  |

| bit 4:               | <b>TXIE</b> : USART Transmit Interrupt Enable bit<br>1 = Enables the USART transmit interrupt<br>0 = Disables the USART transmit interrupt |                                       |            |             |             |              |           |        |                                                                                                          |  |  |  |  |

| bit 3:               | 1 = Enabl                                                                                                                                  | ynchronou<br>es the SS<br>les the SS  | P interrup | t           | pt Enable b | bit          |           |        |                                                                                                          |  |  |  |  |

| bit 2:               | 1 = Enabl                                                                                                                                  | CCP1 Inte<br>es the CC<br>les the CC  | P1 interru | pt          |             |              |           |        |                                                                                                          |  |  |  |  |

| bit 1:               | 1 = Enabl                                                                                                                                  | TMR2 to F<br>es the TM<br>les the TM  | R2 to PR2  | 2 match in  | •           |              |           |        |                                                                                                          |  |  |  |  |

| bit 0:               | 1 = Enabl                                                                                                                                  | TMR1 Ove<br>es the TM<br>les the TM   | R1 overflo | w interrup  | ot          |              |           |        |                                                                                                          |  |  |  |  |

| Note 1:              | PIC16C73                                                                                                                                   |                                       |            |             |             | Slave Port i | mplemente | ed, tl | his bit location is reserved                                                                             |  |  |  |  |

Example 4-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the interrupt service routine (if interrupts are used).

# EXAMPLE 4-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

| ORG 0x | 500      |                            |

|--------|----------|----------------------------|

| BSF    | pclath,3 | ;Select page 1 (800h-FFFh) |

| BCF    | pclath,4 | ;Only on >4K devices       |

| CALL   | SUB1_P1  | ;Call subroutine in        |

|        | :        | ;page 1 (800h-FFFh)        |

|        | :        |                            |

|        | :        |                            |

| ORG 0x | 900      |                            |

| SUB1_P | 1:       | ;called subroutine         |

|        | :        | ;page 1 (800h-FFFh)        |

|        | :        |                            |

| RETURN |          | ;return to Call subroutine |

|        |          | ;in page 0 (000h-7FFh)     |

|        |          |                            |

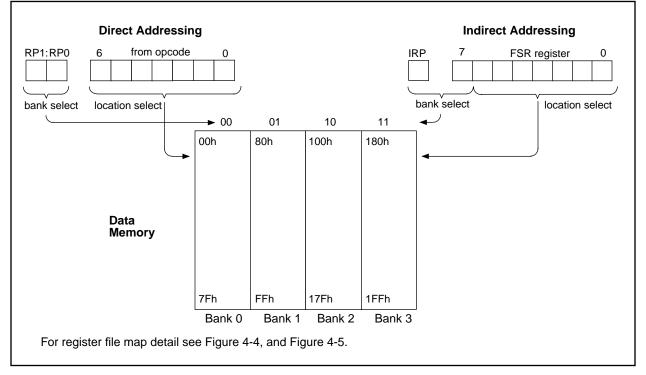

# 4.5 <u>Indirect Addressing, INDF and FSR</u> <u>Registers</u>

|    | •  | cabl |    |     |    |    |

|----|----|------|----|-----|----|----|

| 72 | 73 | 73A  | 74 | 74A | 76 | 77 |

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself indirectly (FSR = '0') will read 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-18.

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 4-2.

# EXAMPLE 4-2: INDIRECT ADDRESSING

| NEXT     | movwf<br>clrf<br>incf | INDF<br>FSR,F | <pre>;initialize pointer ;to RAM ;clear INDF register ;inc pointer ;all done? ;no clear next</pre> |

|----------|-----------------------|---------------|----------------------------------------------------------------------------------------------------|

| CONTINUE |                       |               |                                                                                                    |

|          | :                     |               | ;yes continue                                                                                      |

# FIGURE 4-18: DIRECT/INDIRECT ADDRESSING

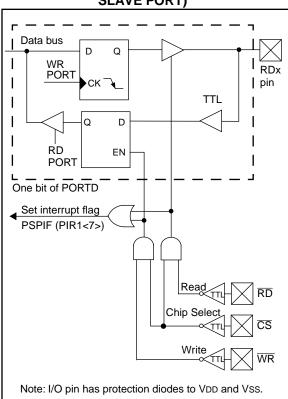

# 5.7 Parallel Slave Port Applicable Devices 72 73 73 74 74 76 77

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port when control bit PSPMODE (TRISE<4>) is set. In slave mode it is asynchronously readable and writable by the external world through  $\overline{RD}$  control input pin RE0/ $\overline{RD}$ /AN5 and  $\overline{WR}$  control input pin RE1/ $\overline{WR}$ /AN6.

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD/AN5 to be the RD input, RE1/ WR/AN6 to be the WR input and RE2/CS/AN7 to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set) and the A/D port configuration bits PCFG2:PCFG0 (ADCON1<2:0>) must be set, which will configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches, one for data-out (from the PIC16/17) and one for data input. The user writes 8-bit data to PORTD data latch and reads data from the port pin latch (note that they have the same address). In this mode, the TRISD register is ignored, since the microprocessor is controlling the direction of data flow.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$ lines are first detected low. When either the  $\overline{CS}$  or  $\overline{WR}$ lines become high (level triggered), then the Input Buffer Full status flag bit IBF (TRISE<7>) is set on the Q4 clock cycle, following the next Q2 cycle, to signal the write is complete (Figure 5-12). The interrupt flag bit PSPIF (PIR1<7>) is also set on the same Q4 clock cycle. IBF can only be cleared by reading the PORTD input latch. The input Buffer Overflow status flag bit IBOV (TRISE<5>) is set if a second write to the Parallel Slave Port is attempted when the previous byte has not been read out of the buffer.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The Output Buffer Full status flag bit OBF (TRISE<6>) is cleared immediately (Figure 5-13) indicating that the PORTD latch is waiting to be read by the external bus. When either the  $\overline{CS}$  or  $\overline{RD}$  pin becomes high (level triggered), the interrupt flag bit PSPIF is set on the Q4 clock cycle, following the next Q2 cycle, indicating that the read is complete. OBF remains low until data is written to PORTD by the user firmware.

When not in Parallel Slave Port mode, the IBF and OBF bits are held clear. However, if flag bit IBOV was previously set, it must be cleared in firmware.

An interrupt is generated and latched into flag bit PSPIF when a read or write operation is completed. PSPIF must be cleared by the user in firmware and the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

# FIGURE 5-11: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

NOTES:

#### FIGURE 9-2: T2CON: TIMER2 CONTROL REGISTER (ADDRESS 12h)

| U-0      | R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0                                                                                                     |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| <u> </u> | TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0 R = Readable bit                                                                 |  |

| bit7     | bit0<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset                                           |  |

| bit 7:   | Unimplemented: Read as '0'                                                                                                              |  |

| bit 6-3: | TOUTPS3:TOUTPS0: Timer2 Output Postscale Select bits<br>0000 = 1:1 Postscale<br>0001 = 1:2 Postscale<br>•<br>•<br>1111 = 1:16 Postscale |  |

| bit 2:   | TMR2ON: Timer2 On bit<br>1 = Timer2 is on<br>0 = Timer2 is off                                                                          |  |

| bit 1-0: | <b>T2CKPS1:T2CKPS0</b> : Timer2 Clock Prescale Select bits<br>00 = Prescaler is 1<br>01 = Prescaler is 4<br>1x = Prescaler is 16        |  |

#### **TABLE 9-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER**

| Address               | Name   | Bit 7                  | Bit 6          | Bit 5               | Bit 4               | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|-----------------------|--------|------------------------|----------------|---------------------|---------------------|---------|--------|---------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                    | PEIE           | TOIE                | INTE                | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1   | PSPIF <sup>(1,2)</sup> | ADIF           | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000                | 0000 0000                       |

| 8Ch                   | PIE1   | PSPIE <sup>(1,2)</sup> | ADIE           | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup> | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000                | 0000 0000                       |

| 11h                   | TMR2   | Timer2 mod             | lule's registe | r                   |                     |         |        |         |         | 0000 0000                | 0000 0000                       |

| 12h                   | T2CON  | _                      | TOUTPS3        | TOUTPS2             | TOUTPS1             | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000                | -000 0000                       |

| 92h                   | PR2    | Timer2 Period Register |                |                     |                     |         |        |         |         |                          | 1111 1111                       |

Legend:

x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

Note

1:

Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

2:

The PIC16C72 does not have a Parallel Slave Port or a USART, these bits are unimplemented, read as '0'.

### 11.5.2 MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is idle and both the S and P bits are clear.

In master mode the SCL and SDA lines are manipulated by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- START condition

- STOP condition

- Data transfer byte transmitted/received

Master mode of operation can be done with either the slave mode idle (SSPM3:SSPM0 = 1011) or with the slave active. When both master and slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

# 11.5.3 MULTI-MASTER MODE

In multi-master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

| Address                | Name    | Bit 7                | Bit 6              | Bit 5                  | Bit 4      | Bit 3      | Bit 2    | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other resets |

|------------------------|---------|----------------------|--------------------|------------------------|------------|------------|----------|--------|--------|-------------------------|---------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE               | TOIE                   | INTE       | RBIE       | TOIF     | INTF   | RBIF   | 0000 000x               | 0000 000u                 |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF               | RCIF                   | TXIF       | SSPIF      | CCP1IF   | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                 |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE               | RCIE                   | TXIE       | SSPIE      | CCP1IE   | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                 |

| 13h                    | SSPBUF  | Synchrono            | us Serial          | Port Rece              | eive Buffe | r/Transmit | Register |        |        | xxxx xxxx               | uuuu uuuu                 |

| 93h                    | SSPADD  | Synchrono            | us Serial          | Port (I <sup>2</sup> C | mode) Ad   | ldress Re  | gister   |        |        | 0000 0000               | 0000 0000                 |

| 14h                    | SSPCON  | WCOL                 | SSPOV              | SSPEN                  | CKP        | SSPM3      | SSPM2    | SSPM1  | SSPM0  | 0000 0000               | 0000 0000                 |

| 94h                    | SSPSTAT | SMP <sup>(2)</sup>   | CKE <sup>(2)</sup> | D/Ā                    | Р          | S          | R/W      | UA     | BF     | 0000 0000               | 0000 0000                 |

| 87h                    | TRISC   | PORTC Da             | ta Directi         | 1111 1111              | 1111 1111  |            |          |        |        |                         |                           |

# TABLE 11-5: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

$\label{eq:Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in SPI mode.$

Note 1: PSPIF and PSPIE are reserved on the PIC16C73/73A/76, always maintain these bits clear.

2: The SMP and CKE bits are implemented on the PIC16C76/77 only. All other PIC16C7X devices have these two bits unimplemented, read as '0'.

# 12.1.1 SAMPLING

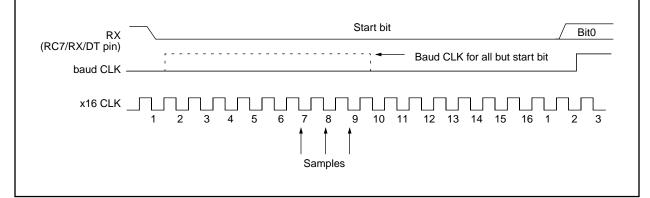

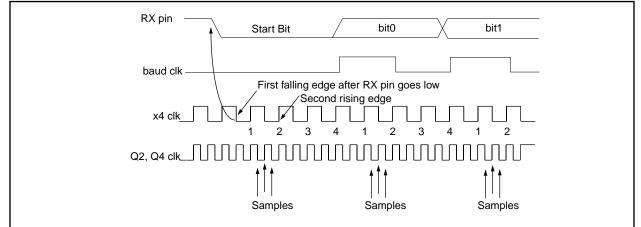

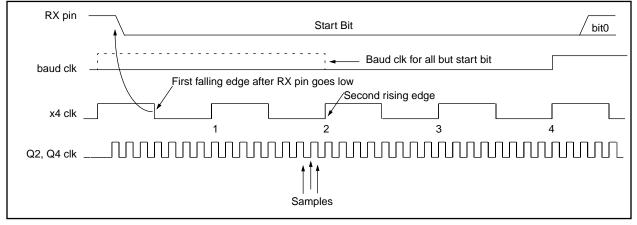

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin. If bit BRGH (TXSTA<2>) is clear (i.e., at the low baud rates), the sampling is done on the seventh, eighth and ninth falling edges of a x16 clock (Figure 12-3). If bit BRGH is set (i.e., at the high baud rates), the sampling is done on the 3 clock edges preceding the second rising edge after the first falling edge of a x4 clock (Figure 12-4 and Figure 12-5).

# FIGURE 12-3: RX PIN SAMPLING SCHEME. BRGH = 0 (PIC16C73/73A/74/74A)

# FIGURE 12-4: RX PIN SAMPLING SCHEME, BRGH = 1 (PIC16C73/73A/74/74A)

# TABLE 12-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Address | Name                               | Bit 7                | Bit 6     | Bit 5   | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|------------------------------------|----------------------|-----------|---------|-------|-------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1                               | PSPIF <sup>(1)</sup> | ADIF      | RCIF    | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA                              | SPEN                 | RX9       | SREN    | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                 |

| 19h     | TXREG                              | USART Tra            | ansmit Re | egister |       |       |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1                               | PSPIE <sup>(1)</sup> | ADIE      | RCIE    | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA                              | CSRC                 | TX9       | TXEN    | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | SPBRG Baud Rate Generator Register |                      |           |         |       |       |        |        |        | 0000 0000                | 0000 0000                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Transmission. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

# TABLE 12-11: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address | Name  | Bit 7                | Bit 6     | Bit 5     | Bit 4     | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|-------|----------------------|-----------|-----------|-----------|-------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF      | RCIF      | TXIF      | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA | SPEN                 | RX9       | SREN      | CREN      | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                 |

| 1Ah     | RCREG | USART Re             | eceive Re | egister   |           |       |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE      | RCIE      | TXIE      | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA | CSRC                 | TX9       | TXEN      | SYNC      | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | SPBRG | Baud Rate            | Generat   | 0000 0000 | 0000 0000 |       |        |        |        |                          |                           |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

# FIGURE 14-20: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| ; a1   a2   a3   a4 ; a1   a2   a<br>osc1/^_/_/_/_//                               | 23 Q4 Q1              | Q1  Q2  Q3  Q4 | ; q1   q2   q3   q4 ;<br>//////////////////////////////////// | Q1   Q2   Q3   Q4 ; | Q1   Q2   Q3   Q4;<br>∕──∕──∕─ |

|------------------------------------------------------------------------------------|-----------------------|----------------|---------------------------------------------------------------|---------------------|--------------------------------|

| CLKOUT(4) ,//                                                                      | Tost(2)               |                |                                                               | \'                  | '                              |

| INT pin                                                                            |                       |                |                                                               | 1<br>1<br>1         |                                |

| INTF flag<br>(INTCON<1>)                                                           | <b>`</b>              | 1              | Interrupt Latency<br>(Note 2)                                 |                     |                                |

| GIE bit<br>(INTCON<7>)                                                             | Processor in<br>SLEEP |                |                                                               | ו<br>ו<br>ו<br>ו    | 1<br>1<br>1                    |

| INSTRUCTION FLOW                                                                   |                       |                |                                                               | 1                   | 1                              |

| PC X PC X PC+1                                                                     | X PC+2                | PC+2           | PC + 2                                                        | X 0004h             | 0005h                          |

| Instruction $\begin{cases} \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $ | + 1)                  | Inst(PC + 2)   |                                                               | Inst(0004h)         | Inst(0005h)                    |

| Instruction<br>executed I Inst(PC - 1) SLEEP                                       |                       | Inst(PC + 1)   | Dummy cycle                                                   | Dummy cycle         | Inst(0004h)                    |

| Note 1. XT US or Descillator mode on                                               |                       |                |                                                               |                     |                                |

Note 1: XT, HS or LP oscillator mode assumed.

2: TOST = 1024TOSC (drawing not to scale) This delay will not be there for RC osc mode.

3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

# 14.9 <u>Program Verification/Code Protection</u>

Applicable Devices

72 73 73A 74 74A 76 77

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting windowed devices.              |

# 14.10 ID Locations

Applicable Devices

72 73 73A 74 74A 76 77

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

# 14.11 In-Circuit Serial Programming Applicable Devices 72/73/73A/74/74A/76/77

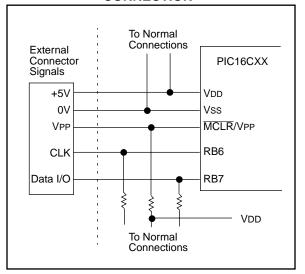

PIC16CXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed. The device is placed into a program/verify mode by holding the RB6 and RB7 pins low while raising the  $\overline{\text{MCLR}}$  (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After reset, to place the device into programming/verify mode, the program counter (PC) is at location 00h. A 6bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X Programming Specifications (Literature #DS30228).

# FIGURE 14-21: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| BTFSS             | Bit Test f, S                                                                                                                                              | Skip if S       | iet               |                  | CALL                                  | Call Sub                             | oroutine                                                            |                               |                  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|------------------|---------------------------------------|--------------------------------------|---------------------------------------------------------------------|-------------------------------|------------------|

| Syntax:           | [ <i>label</i> ] BTFS                                                                                                                                      | SS f,b          |                   |                  | Syntax:                               | [ <i>label</i> ] CALL k              |                                                                     |                               |                  |

| Operands:         | $0 \le f \le 127$                                                                                                                                          |                 |                   | Operands:        | $0 \le k \le 2047$                    |                                      |                                                                     |                               |                  |

|                   | 0 ≤ b < 7                                                                                                                                                  |                 |                   |                  | Operation:                            | (PC)+ 1-                             | ,                                                                   |                               |                  |

| Operation:        | skip if (f <b>)</b>                                                                                                                                        | •) = 1          |                   |                  |                                       | $k \rightarrow PC <$                 |                                                                     | <b>DO</b> 40                  |                  |

| Status Affected:  | None                                                                                                                                                       |                 |                   |                  |                                       |                                      | 1<4:3>) -                                                           | → PC<12:                      | :11>             |

| Encoding:         | 01 1                                                                                                                                                       | l1bb            | bfff              | ffff             | Status Affected:                      | None                                 | 1                                                                   |                               |                  |

| Description:      | If bit 'b' in regi                                                                                                                                         |                 |                   | ne next          | Encoding:                             | 10                                   | 0kkk                                                                | kkkk                          | kkkk             |

| Words:            | instruction is executed.<br>If bit 'b' is '1', then the next instruction is<br>discarded and a NOP is executed<br>instead, making this a 2Tcy instruction. |                 |                   | Description:     | (PC+1) is<br>eleven bit<br>into PC bi | pushed or<br>immediate<br>ts <10:0>. | t, return ac<br>nto the stac<br>address is<br>The upper<br>om PCLAT | k. The<br>s loaded<br>bits of |                  |

| Cycles:           | 1(2)                                                                                                                                                       |                 |                   |                  |                                       | is a two cy                          | cle instruc                                                         | ction.                        |                  |

| Q Cycle Activity: | Q1                                                                                                                                                         | Q2              | Q3                | Q4               | Words:                                | 1                                    |                                                                     |                               |                  |

| Q CYCIE ACTIVITY. |                                                                                                                                                            | Read            | Process           | No-              | Cycles:                               | 2                                    |                                                                     |                               |                  |

|                   |                                                                                                                                                            | egister 'f'     | data              | Operation        | Q Cycle Activity:                     | Q1                                   | Q2                                                                  | Q3                            | Q4               |

| If Skip:          | (2nd Cycle)                                                                                                                                                |                 |                   |                  | 1st Cycle                             | Decode                               | Read<br>literal 'k',                                                | Process<br>data               | Write to<br>PC   |

|                   | Q1                                                                                                                                                         | Q2              | Q3                | Q4               |                                       |                                      | Push PC<br>to Stack                                                 |                               |                  |

|                   | No-<br>Operation Op                                                                                                                                        | No-<br>peration | No-<br>Operation  | No-<br>Operation | 2nd Cycle                             | No-<br>Operation                     | No-<br>Operation                                                    | No-<br>Operation              | No-<br>Operation |

| Example           |                                                                                                                                                            |                 | FLAG,1<br>PROCESS | CODE             | Example                               | HERE                                 | CALL                                                                | THERE                         |                  |

|                   | TRUE •                                                                                                                                                     |                 |                   | _0022            |                                       | Before Ir                            | nstruction                                                          |                               |                  |

|                   | •                                                                                                                                                          |                 |                   |                  |                                       | After Ins                            |                                                                     | ddress HE                     | RE               |

|                   | Before Instru                                                                                                                                              | uction          |                   |                  |                                       |                                      |                                                                     | ddress TH                     | ERE              |

|                   | PC<br>After Instruc<br>if F<br>PC                                                                                                                          | ction<br>LAG<1> | address FA        |                  |                                       |                                      | TOS = A                                                             | ddress he                     | RE+1             |

|                   | PC                                                                                                                                                         |                 | address TI        | RUE              |                                       |                                      |                                                                     |                               |                  |

| RETLW             | Return with Literal in W                                                                                                    |                           | RETURN                              | Return f                             | rom Sub                                                                                                   | routine          |                  |                  |                       |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|-----------------------|--|

| Syntax:           | [ <i>label</i> ] RETLW k                                                                                                    |                           |                                     | Syntax:                              | [ label ]                                                                                                 | RETUR            | N                |                  |                       |  |

| Operands:         | $0 \le k \le 255$                                                                                                           |                           |                                     | Operands:                            | None                                                                                                      |                  |                  |                  |                       |  |

| Operation:        | $k \rightarrow (W);$                                                                                                        |                           |                                     |                                      | Operation:                                                                                                | $TOS \to PC$     |                  |                  |                       |  |

|                   | $TOS \to F$                                                                                                                 | С                         |                                     |                                      | Status Affected:                                                                                          | None             |                  |                  |                       |  |

| Status Affected:  | None                                                                                                                        |                           |                                     |                                      | Encoding:                                                                                                 | 00               | 0000             | 0000             | 1000                  |  |

| Encoding:         | 11                                                                                                                          | 01xx                      | kkkk                                | kkkk                                 | Description:                                                                                              | Return fro       | m subrout        | ine. The st      | ack is                |  |

| Description:      | The W register is loaded with the eight<br>bit literal 'k'. The program counter is<br>loaded from the top of the stack (the |                           |                                     |                                      | POPed and the top of the stack (TOS) is loaded into the program counter. This is a two cycle instruction. |                  |                  |                  |                       |  |

|                   | return add                                                                                                                  | ,                         | s is a two c                        | cycle                                | Words:                                                                                                    | 1                |                  |                  |                       |  |

| Words:            | 1                                                                                                                           |                           |                                     |                                      | Cycles:                                                                                                   | 2                |                  |                  |                       |  |

| Cycles:           | 2                                                                                                                           |                           |                                     |                                      | Q Cycle Activity:                                                                                         | Q1               | Q2               | Q3               | Q4                    |  |

| Q Cycle Activity: | 2<br>Q1                                                                                                                     | Q2                        | Q3                                  | Q4                                   | 1st Cycle                                                                                                 | Decode           | No-<br>Operation | No-<br>Operation | Pop from<br>the Stack |  |

| 1st Cycle         | Decode                                                                                                                      | Read<br>literal 'k'       | No-<br>Operation                    | Write to W,<br>Pop from<br>the Stack | 2nd Cycle                                                                                                 | No-<br>Operation | No-<br>Operation | No-<br>Operation | No-<br>Operation      |  |

| 2nd Cycle         | No-<br>Operation                                                                                                            | No-<br>Operation          | No-<br>Operation                    | No-<br>Operation                     | Example                                                                                                   | RETURN           |                  |                  |                       |  |

|                   | Operation                                                                                                                   | Operation                 | Operation                           | Operation                            |                                                                                                           | After Inte       | errupt           |                  |                       |  |

| Example           | CALL TABL                                                                                                                   | ;offset                   | tains tabl<br>t value<br>7 has tabl |                                      |                                                                                                           |                  | PC =             | TOS              |                       |  |

| TABLE             | ADDWF PC<br>RETLW k1<br>RETLW k2                                                                                            | ;W = off<br>;Begin t<br>; |                                     |                                      |                                                                                                           |                  |                  |                  |                       |  |

|                   | RETLW kn                                                                                                                    | ; End of                  | f table                             |                                      |                                                                                                           |                  |                  |                  |                       |  |

|                   | Before In                                                                                                                   |                           |                                     |                                      |                                                                                                           |                  |                  |                  |                       |  |

|                   | After Inst                                                                                                                  |                           | 0x07                                |                                      |                                                                                                           |                  |                  |                  |                       |  |

|                   |                                                                                                                             |                           | value of k                          | 8                                    |                                                                                                           |                  |                  |                  |                       |  |

Applicable Devices 72 73 73A 74 74A 76 77

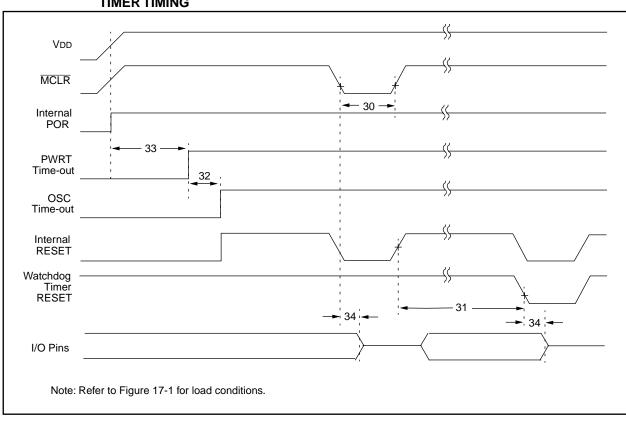

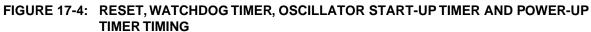

# FIGURE 17-5: BROWN-OUT RESET TIMING

# TABLE 17-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†     | Max | Units | Conditions                |

|------------------|-------|--------------------------------------------------------|-----|----------|-----|-------|---------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                 | 2   | _        | —   | μs    | VDD = 5V, -40°C to +125°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +125°C |

| 32               | Tost  | Oscillation Start-up Timer Period                      | _   | 1024Tosc |     | —     | Tosc = OSC1 period        |

| 33*              | Tpwrt | Power-up Timer Period                                  | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +125°C |

| 34               | Tıoz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | _   | _        | 2.1 | μs    |                           |

| 35               | TBOR  | Brown-out Reset pulse width                            | 100 | _        | —   | μs    | $VDD \le BVDD (D005)$     |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# Applicable Devices 72 73 73A 74 74A 76 77

# 18.2 DC Characteristics: PIC16LC73/74-04 (Commercial, Industrial)

| DC CHA                | ARACTERISTICS                                                    |      | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq TA \leq +85^{\circ}$ C for industrial and $0^{\circ}$ C $\leq TA \leq +70^{\circ}$ C for commercial |                   |                  |                |                                                                                                                                                                                              |  |

|-----------------------|------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.          | Characteristic                                                   | Sym  | Min                                                                                                                                                                                                    | Тур†              | Мах              | Units          | Conditions                                                                                                                                                                                   |  |

| D001                  | Supply Voltage                                                   | Vdd  | 3.0                                                                                                                                                                                                    | -                 | 6.0              | V              | LP, XT, RC osc configuration (DC - 4 MHz)                                                                                                                                                    |  |

| D002*                 | RAM Data Retention<br>Voltage (Note 1)                           | Vdr  | -                                                                                                                                                                                                      | 1.5               | -                | V              |                                                                                                                                                                                              |  |

| D003                  | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR | -                                                                                                                                                                                                      | Vss               | -                | V              | See section on Power-on Reset for details                                                                                                                                                    |  |

| D004*                 | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | Svdd | 0.05                                                                                                                                                                                                   | -                 | -                | V/ms           | See section on Power-on Reset for details                                                                                                                                                    |  |

| D010                  | Supply Current (Note 2,5)                                        | IDD  | -                                                                                                                                                                                                      | 2.0               | 3.8              | mA             | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                                                                                |  |

| D010A                 |                                                                  |      | -                                                                                                                                                                                                      | 22.5              | 48               | μA             | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                                                                                                              |  |

| D020<br>D021<br>D021A | Power-down Current<br>(Note 3,5)                                 | IPD  |                                                                                                                                                                                                        | 7.5<br>0.9<br>0.9 | 30<br>13.5<br>18 | μΑ<br>μΑ<br>μΑ | VDD = $3.0V$ , WDT enabled, $-40^{\circ}C$ to $+85^{\circ}C$<br>VDD = $3.0V$ , WDT disabled, $0^{\circ}C$ to $+70^{\circ}C$<br>VDD = $3.0V$ , WDT disabled, $-40^{\circ}C$ to $+85^{\circ}C$ |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

$\overline{\text{MCLR}}$  = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and VSS.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

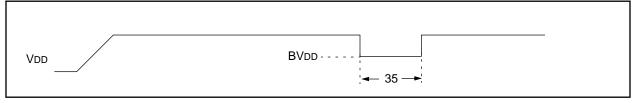

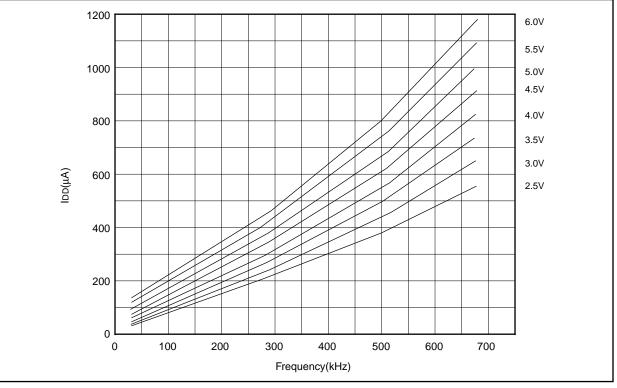

# Applicable Devices 72 73 73 74 74 76 77 FIGURE 21-16: TYPICAL IDD vs. FREQUENCY (RC MODE @ 300 pF, 25°C)

FIGURE 21-17: MAXIMUM IDD vs. FREQUENCY (RC MODE @ 300 pF, -40°C TO 85°C)

Data based on matrix samples. See first page of this section for details.

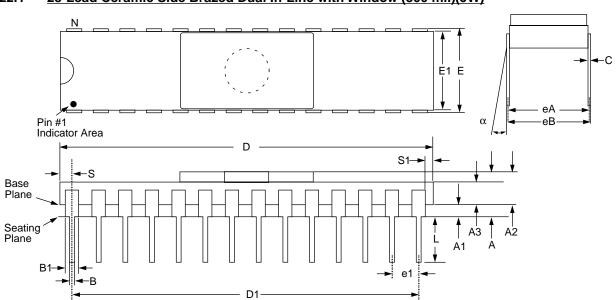

# 22.0 PACKAGING INFORMATION

# 22.1 28-Lead Ceramic Side Brazed Dual In-Line with Window (300 mil)(JW)

| Package Group: Ceramic Side Brazed Dual In-Line (CER) |            |             |           |        |       |       |  |  |

|-------------------------------------------------------|------------|-------------|-----------|--------|-------|-------|--|--|

| Cumhal                                                |            | Millimeters |           | Inches |       |       |  |  |

| Symbol                                                | Min        | Мах         | Notes     | Min    | Max   | Notes |  |  |

| α                                                     | <b>0</b> ° | 10°         |           | 0°     | 10°   |       |  |  |

| А                                                     | 3.937      | 5.030       |           | 0.155  | 0.198 |       |  |  |

| A1                                                    | 1.016      | 1.524       |           | 0.040  | 0.060 |       |  |  |

| A2                                                    | 2.921      | 3.506       |           | 0.115  | 0.138 |       |  |  |

| A3                                                    | 1.930      | 2.388       |           | 0.076  | 0.094 |       |  |  |

| В                                                     | 0.406      | 0.508       |           | 0.016  | 0.020 |       |  |  |

| B1                                                    | 1.219      | 1.321       | Typical   | 0.048  | 0.052 |       |  |  |

| С                                                     | 0.228      | 0.305       | Typical   | 0.009  | 0.012 |       |  |  |

| D                                                     | 35.204     | 35.916      |           | 1.386  | 1.414 |       |  |  |

| D1                                                    | 32.893     | 33.147      | Reference | 1.295  | 1.305 |       |  |  |

| E                                                     | 7.620      | 8.128       |           | 0.300  | 0.320 |       |  |  |

| E1                                                    | 7.366      | 7.620       |           | 0.290  | 0.300 |       |  |  |

| e1                                                    | 2.413      | 2.667       | Typical   | 0.095  | 0.105 |       |  |  |

| eA                                                    | 7.366      | 7.874       | Reference | 0.290  | 0.310 |       |  |  |

| eB                                                    | 7.594      | 8.179       |           | 0.299  | 0.322 |       |  |  |

| L                                                     | 3.302      | 4.064       |           | 0.130  | 0.160 |       |  |  |

| Ν                                                     | 28         | 28          |           | 28     | 28    |       |  |  |

| S                                                     | 1.143      | 1.397       |           | 0.045  | 0.055 |       |  |  |

| S1                                                    | 0.533      | 0.737       |           | 0.021  | 0.029 |       |  |  |

# E.3 PIC16C15X Family of Devices

|             |                                         | PIC16C154                           | PIC16CR154                          | PIC16C156                           | PIC16CR156                          | PIC16C158                           | PIC16CR158                          |

|-------------|-----------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz) | 20                                  | 20                                  | 20                                  | 20                                  | 20                                  | 20                                  |

|             | EPROM Program Memory<br>(x12 words)     | 512                                 |                                     | 1K                                  |                                     | 2К                                  |                                     |

| Memory      | ROM Program Memory<br>(x12 words)       | —                                   | 512                                 | —                                   | 1K                                  | —                                   | 2К                                  |

|             | RAM Data Memory (bytes)                 | 25                                  | 25                                  | 25                                  | 25                                  | 73                                  | 73                                  |

| Peripherals | Timer Module(s)                         | TMR0                                | TMR0                                | TMR0                                | TMR0                                | TMR0                                | TMR0                                |

|             | I/O Pins                                | 12                                  | 12                                  | 12                                  | 12                                  | 12                                  | 12                                  |

|             | Voltage Range (Volts)                   | 3.0-5.5                             | 2.5-5.5                             | 3.0-5.5                             | 2.5-5.5                             | 3.0-5.5                             | 2.5-5.5                             |

| Features    | Number of Instructions                  | 33                                  | 33                                  | 33                                  | 33                                  | 33                                  | 33                                  |

|             | Packages                                | 18-pin DIP,<br>SOIC;<br>20-pin SSOP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability.

# E.4 PIC16C5X Family of Devices

|             |                                         | PIC16C52            | PIC16C54                            | PIC16C54A                           | PIC16CR54A                          | PIC16C55                     | PIC16C56                            |

|-------------|-----------------------------------------|---------------------|-------------------------------------|-------------------------------------|-------------------------------------|------------------------------|-------------------------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz) | 4                   | 20                                  | 20                                  | 20                                  | 20                           | 20                                  |

|             | EPROM Program Memory<br>(x12 words)     | 384                 | 512                                 | 512                                 | —                                   | 512                          | 1K                                  |

| Memory      | ROM Program Memory<br>(x12 words)       | -                   | —                                   | —                                   | 512                                 | —                            | —                                   |

|             | RAM Data Memory (bytes)                 | 25                  | 25                                  | 25                                  | 25                                  | 24                           | 25                                  |

| Peripherals | Timer Module(s)                         | TMR0                | TMR0                                | TMR0                                | TMR0                                | TMR0                         | TMR0                                |

|             | I/O Pins                                | 12                  | 12                                  | 12                                  | 12                                  | 20                           | 12                                  |

|             | Voltage Range (Volts)                   | 2.5-6.25            | 2.5-6.25                            | 2.0-6.25                            | 2.0-6.25                            | 2.5-6.25                     | 2.5-6.25                            |

| Features    | Number of Instructions                  | 33                  | 33                                  | 33                                  | 33                                  | 33                           | 33                                  |

|             | Packages                                | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin DIP,<br>SOIC,<br>SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP |

|             |                                         | PIC16C57                     | PIC16CR57B                | PIC16C58A                        | PIC16CR58A                       |

|-------------|-----------------------------------------|------------------------------|---------------------------|----------------------------------|----------------------------------|

| Clock       | Maximum Frequency<br>of Operation (MHz) | 20                           | 20                        | 20                               | 20                               |

|             | EPROM Program Memory<br>(x12 words)     | 2K                           | -                         | 2К                               | —                                |

| Memory      | ROM Program Memory<br>(x12 words)       | -                            | 2К                        | —                                | 2K                               |

|             | RAM Data Memory (bytes)                 | 72                           | 72                        | 73                               | 73                               |

| Peripherals | Timer Module(s)                         | TMR0                         | TMR0                      | TMR0                             | TMR0                             |

|             | I/O Pins                                | 20                           | 20                        | 12                               | 12                               |

|             | Voltage Range (Volts)                   | 2.5-6.25                     | 2.5-6.25                  | 2.0-6.25                         | 2.5-6.25                         |

| Features    | Number of Instructions                  | 33                           | 33                        | 33                               | 33                               |

|             | Packages                                | 28-pin DIP,<br>SOIC,<br>SSOP | 28-pin DIP, SOIC,<br>SSOP | 18-pin DIP, SOIC;<br>20-pin SSOP | 18-pin DIP, SOIC;<br>20-pin SSOP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer (except PIC16C52), selectable code protect and high I/O current capability.

# PIC16C7X

| Figure 20-9:   | SPI Master Mode Timing (CKE = 0)232         |

|----------------|---------------------------------------------|

| Figure 20-10:  | SPI Master Mode Timing (CKE = 1)232         |

| Figure 20-11:  | SPI Slave Mode Timing (CKE = $0$ )          |

|                |                                             |

| Figure 20-12:  | SPI Slave Mode Timing (CKE = 1)             |

| Figure 20-13:  | I <sup>2</sup> C Bus Start/Stop Bits Timing |

| Figure 20-14:  | I <sup>2</sup> C Bus Data Timing236         |

|                |                                             |

| Figure 20-15:  | USART Synchronous Transmission              |

|                | (Master/Slave) Timing237                    |

| Figure 20-16:  | USART Synchronous Receive                   |

| 0              | (Master/Slave) Timing 237                   |

| Figure 20 17:  |                                             |

| Figure 20-17:  | A/D Conversion Timing                       |

| Figure 21-1:   | Typical IPD vs. VDD (WDT Disabled,          |

|                | RC Mode)241                                 |

| Figure 21-2:   | Maximum IPD vs. VDD (WDT                    |

| rigaro Er E.   |                                             |

| -              | Disabled, RC Mode)                          |

| Figure 21-3:   | Typical IPD vs. VDD @ 25°C (WDT             |

|                | Enabled, RC Mode)242                        |

| Figure 21-4:   | Maximum IPD vs. VDD (WDT                    |

| rigulo 21 4.   |                                             |

|                | Enabled, RC Mode)242                        |