Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                |

| Data Converters            | A/D 8x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc77-04-l |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral Modules for controlling the desired operation of the device. These registers are implemented as static RAM. The special function registers can be classified into two sets (core and peripheral). Those registers associated with the "core" functions are described in this section, and those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address              | Name    | Bit 7                                                                       | Bit 6              | Bit 5         | Bit 4          | Bit 3          | Bit 2            | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(3) |

|----------------------|---------|-----------------------------------------------------------------------------|--------------------|---------------|----------------|----------------|------------------|---------------|-----------|--------------------------|-------------------------------------|

| Bank 0               | D       |                                                                             |                    |               |                |                |                  |               |           |                          |                                     |

| 00h <sup>(1)</sup>   | INDF    | Addressing                                                                  | this location      | uses conten   | ts of FSR to   | address data   | a memory (n      | ot a physical | register) | 0000 0000                | 0000 0000                           |

| 01h                  | TMR0    | Timer0 mod                                                                  | dule's registe     | r             |                |                |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 02h <sup>(1)</sup>   | PCL     | Program Co                                                                  | ounter's (PC)      | Least Signif  | icant Byte     |                |                  |               |           | 0000 0000                | 0000 0000                           |

| 03h <sup>(1)</sup>   | STATUS  | IRP <sup>(4)</sup>                                                          | RP1 <sup>(4)</sup> | RP0           | TO             | PD             | Z                | DC            | С         | 0001 1xxx                | 000q quuu                           |

| 04h <sup>(1)</sup>   | FSR     | Indirect dat                                                                | a memory ac        | ldress pointe | r              |                |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 05h                  | PORTA   | _                                                                           | _                  | PORTA Dat     | a Latch whe    | n written: PO  | RTA pins wh      | en read       |           | 0x 0000                  | 0u 0000                             |

| 06h                  | PORTB   | PORTB Da                                                                    | ta Latch whe       | n written: PC | RTB pins wl    | nen read       |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 07h                  | PORTC   | PORTC Da                                                                    | ta Latch whe       | n written: PC | ORTC pins w    | hen read       |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 08h                  | —       | Unimpleme                                                                   | nted               |               |                |                |                  |               |           | —                        | —                                   |

| 09h                  | —       | Unimpleme                                                                   | nted               |               |                |                |                  |               |           | _                        | _                                   |

| 0Ah <sup>(1,2)</sup> | PCLATH  | —                                                                           | —                  | —             | Write Buffer   | r for the uppe | er 5 bits of the | e Program C   | ounter    | 0 0000                   | 0 0000                              |

| 0Bh <sup>(1)</sup>   | INTCON  | GIE                                                                         | PEIE               | TOIE          | INTE           | RBIE           | TOIF             | INTF          | RBIF      | 0000 000x                | 0000 000u                           |

| 0Ch                  | PIR1    | —                                                                           | ADIF               | —             | —              | SSPIF          | CCP1IF           | TMR2IF        | TMR1IF    | -0 0000                  | -0 0000                             |

| 0Dh                  | —       | Unimpleme                                                                   | nted               |               |                |                |                  | •             |           | —                        | _                                   |

| 0Eh                  | TMR1L   | Holding register for the Least Significant Byte of the 16-bit TMR1 register |                    |               |                |                |                  |               | xxxx xxxx | uuuu uuuu                |                                     |

| 0Fh                  | TMR1H   | Holding reg                                                                 | ister for the N    | Most Signific | ant Byte of th | ne 16-bit TMF  | R1 register      |               |           | xxxx xxxx                | uuuu uuuu                           |

| 10h                  | T1CON   | —                                                                           | -                  | T1CKPS1       | T1CKPS0        | T1OSCEN        | T1SYNC           | TMR1CS        | TMR10N    | 00 0000                  | uu uuuu                             |

| 11h                  | TMR2    | Timer2 mod                                                                  | dule's registe     | r             |                |                |                  |               |           | 0000 0000                | 0000 0000                           |

| 12h                  | T2CON   | —                                                                           | TOUTPS3            | TOUTPS2       | TOUTPS1        | TOUTPS0        | TMR2ON           | T2CKPS1       | T2CKPS0   | -000 0000                | -000 0000                           |

| 13h                  | SSPBUF  | Synchronou                                                                  | us Serial Port     | Receive Bu    | ffer/Transmit  | Register       |                  |               |           | XXXX XXXX                | uuuu uuuu                           |

| 14h                  | SSPCON  | WCOL                                                                        | SSPOV              | SSPEN         | CKP            | SSPM3          | SSPM2            | SSPM1         | SSPM0     | 0000 0000                | 0000 0000                           |

| 15h                  | CCPR1L  | Capture/Co                                                                  | mpare/PWM          | Register (LS  | SB)            |                |                  | -             |           | xxxx xxxx                | uuuu uuuu                           |

| 16h                  | CCPR1H  | Capture/Co                                                                  | mpare/PWM          | Register (M   | SB)            |                |                  |               |           | XXXX XXXX                | uuuu uuuu                           |

| 17h                  | CCP1CON | —                                                                           | —                  | CCP1X         | CCP1Y          | CCP1M3         | CCP1M2           | CCP1M1        | CCP1M0    | 00 0000                  | 00 0000                             |

| 18h                  | —       | Unimpleme                                                                   | nted               |               |                |                |                  |               |           | _                        | _                                   |

| 19h                  | —       | Unimpleme                                                                   | nted               |               |                |                |                  |               |           | —                        | —                                   |

| 1Ah                  | —       | Unimplemented                                                               |                    |               |                |                |                  | —             | _         |                          |                                     |

| 1Bh                  | _       | Unimplemented                                                               |                    |               |                |                |                  |               |           | _                        | _                                   |

| 1Ch                  | —       | Unimpleme                                                                   | nted               |               |                |                |                  |               |           | _                        | —                                   |

| 1Dh                  | —       | Unimpleme                                                                   | nted               |               |                |                |                  |               |           | —                        | —                                   |

| 1Eh                  | ADRES   | A/D Result                                                                  | Register           |               |                |                |                  |               |           | xxxx xxxx                | uuuu uuuu                           |

| 1Fh                  | ADCON0  | ADCS1                                                                       | ADCS0              | CHS2          | CHS1           | CHS0           | GO/DONE          | _             | ADON      | 0000 00-0                | 0000 00-0                           |

TABLE 4-1: PIC16C72 SPECIAL FUNCTION REGISTER SUMMARY

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: These registers can be addressed from either bank.

2: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

3: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

4: The IRP and RP1 bits are reserved on the PIC16C72, always maintain these bits clear.

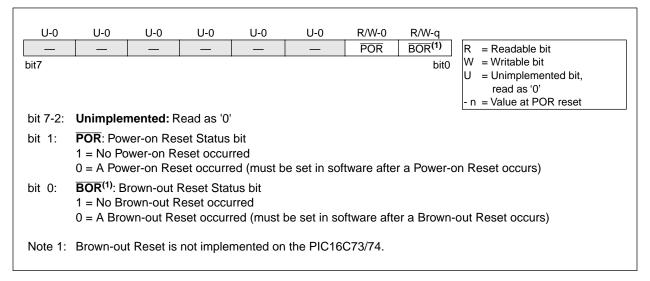

# 4.2.2.8 PCON REGISTER Applicable Devices 72/73/73A/74/74A/76/77

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR) to an external  $\overline{\text{MCLR}}$  Reset or WDT Reset. Those devices with brown-out detection circuitry contain an additional bit to differentiate a Brown-out Reset condition from a Power-on Reset condition.

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the Configuration word).

# FIGURE 4-16: PCON REGISTER (ADDRESS 8Eh)

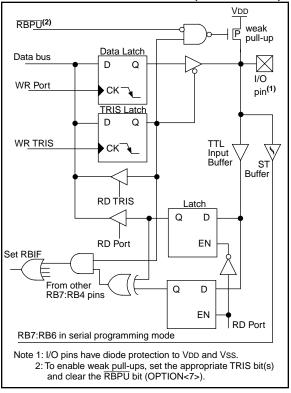

# TABLE 5-3: PORTB FUNCTIONS

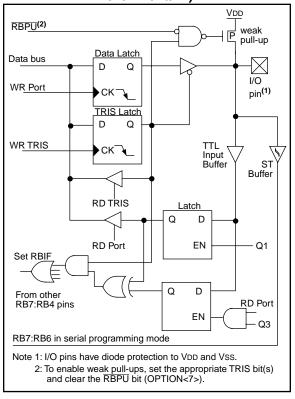

### FIGURE 5-5: BLOCK DIAGRAM OF RB7:RB4 PINS (PIC16C72/ 73A/74A/76/77)

| Name    | Bit# | Buffer                | Function                                                                                                            |

|---------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0 | TTL/ST <sup>(1)</sup> | Input/output pin or external interrupt input. Internal software programmable weak pull-up.                          |

| RB1     | bit1 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB2     | bit2 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB3     | bit3 | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                      |

| RB4     | bit4 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB5     | bit5 | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                           |

| RB6     | bit6 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming clock. |

| RB7     | bit7 | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming data.  |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

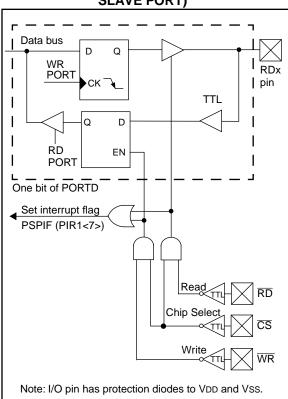

# 5.7 Parallel Slave Port Applicable Devices 72 73 73 74 74 76 77

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port when control bit PSPMODE (TRISE<4>) is set. In slave mode it is asynchronously readable and writable by the external world through  $\overline{RD}$  control input pin RE0/ $\overline{RD}$ /AN5 and  $\overline{WR}$  control input pin RE1/ $\overline{WR}$ /AN6.

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD/AN5 to be the RD input, RE1/ WR/AN6 to be the WR input and RE2/CS/AN7 to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set) and the A/D port configuration bits PCFG2:PCFG0 (ADCON1<2:0>) must be set, which will configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches, one for data-out (from the PIC16/17) and one for data input. The user writes 8-bit data to PORTD data latch and reads data from the port pin latch (note that they have the same address). In this mode, the TRISD register is ignored, since the microprocessor is controlling the direction of data flow.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$ lines are first detected low. When either the  $\overline{CS}$  or  $\overline{WR}$ lines become high (level triggered), then the Input Buffer Full status flag bit IBF (TRISE<7>) is set on the Q4 clock cycle, following the next Q2 cycle, to signal the write is complete (Figure 5-12). The interrupt flag bit PSPIF (PIR1<7>) is also set on the same Q4 clock cycle. IBF can only be cleared by reading the PORTD input latch. The input Buffer Overflow status flag bit IBOV (TRISE<5>) is set if a second write to the Parallel Slave Port is attempted when the previous byte has not been read out of the buffer.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The Output Buffer Full status flag bit OBF (TRISE<6>) is cleared immediately (Figure 5-13) indicating that the PORTD latch is waiting to be read by the external bus. When either the  $\overline{CS}$  or  $\overline{RD}$  pin becomes high (level triggered), the interrupt flag bit PSPIF is set on the Q4 clock cycle, following the next Q2 cycle, indicating that the read is complete. OBF remains low until data is written to PORTD by the user firmware.

When not in Parallel Slave Port mode, the IBF and OBF bits are held clear. However, if flag bit IBOV was previously set, it must be cleared in firmware.

An interrupt is generated and latched into flag bit PSPIF when a read or write operation is completed. PSPIF must be cleared by the user in firmware and the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

## FIGURE 5-11: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

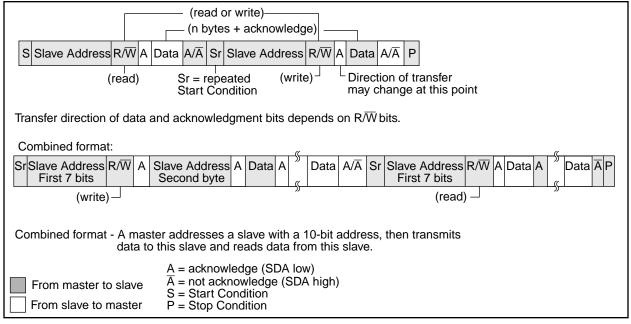

# 11.4 <u>I<sup>2</sup>C<sup>™</sup> Overview</u>

This section provides an overview of the Inter-Integrated Circuit ( $I^2C$ ) bus, with Section 11.5 discussing the operation of the SSP module in  $I^2C$  mode.

The  $l^2C$  bus is a two-wire serial interface developed by the Philips Corporation. The original specification, or standard mode, was for data transfers of up to 100 Kbps. The enhanced specification (fast mode) is also supported. This device will communicate with both standard and fast mode devices if attached to the same bus. The clock will determine the data rate.

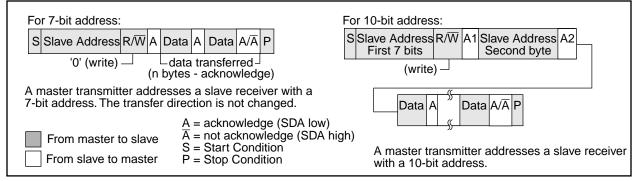

The  $l^2C$  interface employs a comprehensive protocol to ensure reliable transmission and reception of data. When transmitting data, one device is the "master" which initiates transfer on the bus and generates the clock signals to permit that transfer, while the other device(s) acts as the "slave." All portions of the slave protocol are implemented in the SSP module's hardware, except general call support, while portions of the master protocol need to be addressed in the PIC16CXX software. Table 11-3 defines some of the  $l^2C$  bus terminology. For additional information on the  $l^2C$  interface specification, refer to the Philips document "*The*  $l^2C$  bus and how to use it."#939839340011, which can be obtained from the Philips Corporation.

In the I<sup>2</sup>C interface protocol each device has an address. When a master wishes to initiate a data transfer, it first transmits the address of the device that it wishes to "talk" to. All devices "listen" to see if this is their address. Within this address, a bit specifies if the master wishes to read-from/write-to the slave device. The master and slave are always in opposite modes (transmitter/receiver) of operation during a data transfer. That is they can be thought of as operating in either of these two relations:

- Master-transmitter and Slave-receiver

- · Slave-transmitter and Master-receiver

In both cases the master generates the clock signal.

The output stages of the clock (SCL) and data (SDA) lines must have an open-drain or open-collector in order to perform the wired-AND function of the bus. External pull-up resistors are used to ensure a high level when no device is pulling the line down. The number of devices that may be attached to the I<sup>2</sup>C bus is limited only by the maximum bus loading specification of 400 pF.

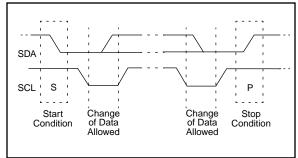

# 11.4.1 INITIATING AND TERMINATING DATA TRANSFER

During times of no data transfer (idle time), both the clock line (SCL) and the data line (SDA) are pulled high through the external pull-up resistors. The START and STOP conditions determine the start and stop of data transmission. The START condition is defined as a high to low transition of the SDA when the SCL is high. The STOP condition is defined as a low to high transition of the SDA when the SCL is high. The START and STOP conditions for starting and terminating data transfer. Due to the definition of the START and STOP conditions, when data is being transmitted, the SDA line can only change state when the SCL line is low.

# FIGURE 11-14: START AND STOP CONDITIONS

| Term            | Description                                                                                                                                 |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Transmitter     | The device that sends the data to the bus.                                                                                                  |

| Receiver        | The device that receives the data from the bus.                                                                                             |

| Master          | The device which initiates the transfer, generates the clock and terminates the transfer.                                                   |

| Slave           | The device addressed by a master.                                                                                                           |

| Multi-master    | More than one master device in a system. These masters can attempt to control the bus at the same time without corrupting the message.      |

| Arbitration     | Procedure that ensures that only one of the master devices will control the bus. This ensure that the transfer data does not get corrupted. |

| Synchronization | Procedure where the clock signals of two or more devices are synchronized.                                                                  |

# TABLE 11-3: I<sup>2</sup>C BUS TERMINOLOGY

Figure 11-19 and Figure 11-20 show Master-transmitter and Master-receiver data transfer sequences.

When a master does not wish to relinquish the bus (by generating a STOP condition), a repeated START condition (Sr) must be generated. This condition is identical to the start condition (SDA goes high-to-low while

SCL is high), but occurs after a data transfer acknowledge pulse (not the bus-free state). This allows a master to send "commands" to the slave and then receive the requested information or to address a different slave device. This sequence is shown in Figure 11-21.

# FIGURE 11-19: MASTER-TRANSMITTER SEQUENCE

# FIGURE 11-20: MASTER-RECEIVER SEQUENCE

| For 7-bit address:         | Fc                                                                                                                                                 | or 10-bit address:                                                |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| S Slave Address R/W A D    | ata A Data A P S                                                                                                                                   | Slave Address R/W A1 Slave Address A2<br>First 7 bits Second byte |

|                            | data transferred-<br>rtes - acknowledge)                                                                                                           | (write)                                                           |

| A master reads a slave imm | ediately after the first byte.                                                                                                                     |                                                                   |

| From master to slave       | $\begin{array}{l} A = acknowledge (SDA low) \\ \overline{A} = not acknowledge (SDA high) \\ S = Start Condition \\ P = Stop Condition \end{array}$ | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $           |

# FIGURE 11-21: COMBINED FORMAT

# 13.8 Use of the CCP Trigger Applicable Devices 72 73 73A 74 74A 76 77

**Note:** In the PIC16C72, the "special event trigger" is implemented in the CCP1 module.

An A/D conversion can be started by the "special event trigger" of the CCP2 module (CCP1 on the PIC16C72 only). This requires that the CCP2M3:CCP2M0 bits (CCP2CON<3:0>) be programmed as 1011 and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving the ADRES to the desired location). The appropriate analog input channel must be selected and the minimum acquisition done before the "special event trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), then the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

# 13.9 Connection Considerations Applicable Devices 72/73/73A/74/74A/76/77

If the input voltage exceeds the rail values (VSS or VDD) by greater than 0.2V, then the accuracy of the conversion is out of specification.

An external RC filter is sometimes added for anti-aliasing of the input signal. The R component should be selected to ensure that the total source impedance is kept under the 10 k $\Omega$  recommended specification. Any external components connected (via hi-impedance) to an analog input pin (capacitor, zener diode, etc.) should have very little leakage current at the pin.

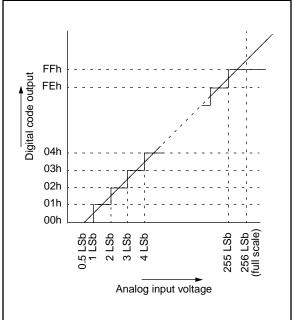

# 13.10 Transfer Function Applicable Devices 72 73 73 74 74 76 77

The ideal transfer function of the A/D converter is as follows: the first transition occurs when the analog input voltage (VAIN) is Analog VREF/256 (Figure 13-5).

# FIGURE 13-5: A/D TRANSFER FUNCTION

# 13.11 References

A very good reference for understanding A/D converters is the "Analog-Digital Conversion Handbook" third edition, published by Prentice Hall (ISBN 0-13-03-2848-0).

# 14.8 Power-down Mode (SLEEP) Applicable Devices 727373A7474A7677

Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD, or Vss, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D, disable external clocks. Pull all I/O pins, that are hi-impedance inputs, high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

#### 14.8.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change, or some Peripheral Interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. SSP (Start/Stop) bit detect interrupt.

- 3. SSP transmit or receive in slave mode (SPI/ $l^2$ C).

- 4. CCP capture mode interrupt.

- 5. Parallel Slave Port read or write.

- 6. A/D conversion (when A/D clock source is RC).

- 7. Special event trigger (Timer1 in asynchronous mode using an external clock).

- 8. USART TX or RX (synchronous slave mode).

Other peripherals cannot generate interrupts since during SLEEP, no on-chip Q clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

### 14.8.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

| BTFSS             | Bit Test                                                                                                                                                   | f, Skip if S                                | Set                |                  | CALL                                                                                                                                                               |          | Call Sub                | routine                       |                          |                  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------|-------------------------------|--------------------------|------------------|

| Syntax:           | [ <i>label</i> ] B1                                                                                                                                        | TFSS f,b                                    |                    |                  | Syntax:                                                                                                                                                            |          | [ <i>label</i> ] CALL k |                               |                          |                  |

| Operands:         | $0 \le f \le 127$                                                                                                                                          |                                             | Operands:          |                  | $0 \le k \le 2047$                                                                                                                                                 |          |                         |                               |                          |                  |

|                   | 0 ≤ b < 7                                                                                                                                                  |                                             |                    |                  | Operation:                                                                                                                                                         |          | (PC)+ 1-                | → TOS,                        |                          |                  |

| Operation:        | skip if (f<                                                                                                                                                | :b>) = 1                                    |                    |                  |                                                                                                                                                                    |          | $k \rightarrow PC <$    | ,                             | DO 40                    |                  |

| Status Affected:  | None                                                                                                                                                       |                                             |                    |                  | <b>.</b>                                                                                                                                                           |          |                         | 1<4:3>) -                     | → PC<12                  | :11>             |

| Encoding:         | 01                                                                                                                                                         | 11bb                                        | bfff               | ffff             | Status Affe                                                                                                                                                        | ected:   | None                    |                               | 1                        |                  |

| Description:      |                                                                                                                                                            | register 'f' i                              |                    | he next          | Encoding:                                                                                                                                                          |          | 10                      | 0kkk                          | kkkk                     | kkkk             |

|                   | instruction is executed.<br>If bit 'b' is '1', then the next instruction is<br>discarded and a NOP is executed<br>instead, making this a 2Tcy instruction. |                                             | Descriptior        | n:               | Call Subroutine. First, return address<br>(PC+1) is pushed onto the stack. The<br>eleven bit immediate address is loaded<br>into PC bits <10:0>. The upper bits of |          |                         | k. The<br>s loaded<br>bits of |                          |                  |

| Words:            | 1                                                                                                                                                          |                                             |                    |                  |                                                                                                                                                                    |          | is a two cy             |                               | rom PCLAT<br>ction.      | H. CALL          |

| Cycles:           | 1(2)                                                                                                                                                       |                                             |                    |                  | Words:                                                                                                                                                             |          | 1                       |                               |                          |                  |

| Q Cycle Activity: | Q1                                                                                                                                                         | Q2                                          | Q3                 | Q4               | Cycles:                                                                                                                                                            |          | 2                       |                               |                          |                  |

|                   | Decode                                                                                                                                                     | Read<br>register 'f'                        | Process<br>data    | No-<br>Operation | Q Cycle Ad                                                                                                                                                         | ctivity: | Q1                      | Q2                            | Q3                       | Q4               |

| If Skip:          | (2nd Cyc                                                                                                                                                   | le)                                         |                    |                  | 15                                                                                                                                                                 | st Cycle | Decode                  | Read<br>literal 'k',          | Process<br>data          | Write to<br>PC   |

| ·                 | Q1                                                                                                                                                         | Q2                                          | Q3                 | Q4               |                                                                                                                                                                    |          |                         | Push PC<br>to Stack           |                          |                  |

|                   | No-<br>Operation                                                                                                                                           | No-<br>Operation                            | No-<br>Operation   | No-<br>Operation | 2n                                                                                                                                                                 | d Cycle  | No-<br>Operation        | No-<br>Operation              | No-<br>Operation         | No-<br>Operation |

| Example           | HERE<br>FALSE                                                                                                                                              | BTFSC<br>GOTO                               | FLAG,1<br>PROCESS_ | _CODE            | Example                                                                                                                                                            |          | HERE<br>Before Ir       | CALL                          | THERE                    |                  |

|                   | TRUE                                                                                                                                                       | •                                           |                    |                  |                                                                                                                                                                    |          | Delote II               |                               | ।<br>∖ddress н≘          | RE               |

|                   |                                                                                                                                                            | •                                           |                    |                  |                                                                                                                                                                    |          | After Inst              | truction                      |                          |                  |

|                   | Before In                                                                                                                                                  |                                             |                    |                  |                                                                                                                                                                    |          |                         |                               | Address TH<br>Address HE |                  |

|                   | After Inst                                                                                                                                                 | ruction<br>if FLAG<1:<br>PC =<br>if FLAG<1: | address F          | ALSE             |                                                                                                                                                                    |          |                         | 103 = 7                       |                          | RE+1             |

# PIC16C7X

| XORLW             | Exclusive OR Literal with W |                                                                                                                              |                 |               |  |  |  |

|-------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|--|--|--|

| Syntax:           | [label]                     | XORL                                                                                                                         | V k             |               |  |  |  |

| Operands:         | $0 \le k \le 2$             | 55                                                                                                                           |                 |               |  |  |  |

| Operation:        | (W) .XO                     | $R.k \rightarrow (N)$                                                                                                        | N)              |               |  |  |  |

| Status Affected:  | Z                           |                                                                                                                              |                 |               |  |  |  |

| Encoding:         | 11                          | 1010                                                                                                                         | kkkk            | kkkk          |  |  |  |

| Description:      | XOR'ed v                    | The contents of the W register are<br>XOR'ed with the eight bit literal 'k'.<br>The result is placed in the W regis-<br>ter. |                 |               |  |  |  |

| Words:            | 1                           |                                                                                                                              |                 |               |  |  |  |

| Cycles:           | 1                           |                                                                                                                              |                 |               |  |  |  |

| Q Cycle Activity: | Q1                          | Q2                                                                                                                           | Q3              | Q4            |  |  |  |

|                   | Decode                      | Read<br>literal 'k'                                                                                                          | Process<br>data | Write to<br>W |  |  |  |

| Example:          | XORLW                       | 0xAF                                                                                                                         |                 |               |  |  |  |

|                   | Before II                   | nstructio                                                                                                                    | n               |               |  |  |  |

|                   | W = 0xB5                    |                                                                                                                              |                 |               |  |  |  |

|                   | After Ins                   | truction                                                                                                                     |                 |               |  |  |  |

|                   |                             | W =                                                                                                                          | 0x1A            |               |  |  |  |

|                   |                             |                                                                                                                              |                 |               |  |  |  |

| XORWF             | Exclusiv                                                    | e OR W                                                                                                                                                                             | with f          |                      |  |  |  |

|-------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|--|--|--|

| Syntax:           | [label]                                                     | XORWF                                                                                                                                                                              | f,d             |                      |  |  |  |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$                              | 7                                                                                                                                                                                  |                 |                      |  |  |  |

| Operation:        | (W) .XOF                                                    | $R.\left(f\right)\to(o$                                                                                                                                                            | destinatio      | on)                  |  |  |  |

| Status Affected:  | Z                                                           |                                                                                                                                                                                    |                 |                      |  |  |  |

| Encoding:         | 00                                                          | 0110                                                                                                                                                                               | dfff            | ffff                 |  |  |  |

| Description:      | register wi<br>result is st                                 | Exclusive OR the contents of the W<br>register with register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd' is<br>1 the result is stored back in register 'f'. |                 |                      |  |  |  |

| Words:            | 1                                                           |                                                                                                                                                                                    |                 |                      |  |  |  |

| Cycles:           | 1                                                           |                                                                                                                                                                                    |                 |                      |  |  |  |

| Q Cycle Activity: | Q1                                                          | Q2                                                                                                                                                                                 | Q3              | Q4                   |  |  |  |

|                   | Decode                                                      | Read<br>register<br>'f'                                                                                                                                                            | Process<br>data | Write to destination |  |  |  |

| Example           | XORWF                                                       |                                                                                                                                                                                    | 1               |                      |  |  |  |

|                   | Before In                                                   | struction                                                                                                                                                                          |                 |                      |  |  |  |

|                   | $\begin{array}{rcl} REG &=& 0xAF \\ W &=& 0xB5 \end{array}$ |                                                                                                                                                                                    |                 |                      |  |  |  |

|                   | After Inst                                                  | ruction                                                                                                                                                                            |                 |                      |  |  |  |

|                   |                                                             | REG<br>W                                                                                                                                                                           | = 0x<br>= 0x    | 1A<br>B5             |  |  |  |

# 17.2 DC Characteristics: PIC16LC72-04 (Commercial, Industrial)

| DC CHA                | itions (unless otherwise stated)<br>$0^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial and<br>$C \leq TA \leq +70^{\circ}C$ for commercial |               |             |                   |              |                |                                                                                                                                                                         |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|-------------------|--------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.          | Characteristic                                                                                                                                | Sym           | Min         | Тур†              | Max          | Units          | Conditions                                                                                                                                                              |

| D001                  | Supply Voltage                                                                                                                                | Vdd           | 2.5         | -                 | 6.0          | V              | LP, XT, RC osc configuration (DC - 4 MHz)                                                                                                                               |

| D002*                 | RAM Data Retention Volt-<br>age (Note 1)                                                                                                      | Vdr           | -           | 1.5               | -            | V              |                                                                                                                                                                         |

| D003                  | VDD start voltage to<br>ensure internal Power-on<br>Reset signal                                                                              | VPOR          | -           | Vss               | -            | V              | See section on Power-on Reset for details                                                                                                                               |

| D004*                 | VDD rise rate to ensure<br>internal Power-on Reset<br>signal                                                                                  | Svdd          | 0.05        | -                 | -            | V/ms           | See section on Power-on Reset for details                                                                                                                               |

| D005                  | Brown-out Reset Voltage                                                                                                                       | Bvdd          | 3.7         | 4.0               | 4.3          | V              | BODEN bit in configuration word enabled                                                                                                                                 |

| D010                  | Supply Current<br>(Note 2,5)                                                                                                                  | IDD           | -           | 2.0               | 3.8          | mA             | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                                                           |

| D010A                 |                                                                                                                                               |               | -           | 22.5              | 48           | μA             | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                                                                                         |

| D015*                 | Brown-out Reset Current (Note 6)                                                                                                              | $\Delta$ IBOR | -           | 350               | 425          | μA             | BOR enabled VDD = 5.0V                                                                                                                                                  |

| D020<br>D021<br>D021A | Power-down Current<br>(Note 3,5)                                                                                                              | IPD           | -<br>-<br>- | 7.5<br>0.9<br>0.9 | 30<br>5<br>5 | μΑ<br>μΑ<br>μΑ | $VDD = 3.0V, WDT enabled, -40^{\circ}C to +85^{\circ}C$ $VDD = 3.0V, WDT disabled, 0^{\circ}C to +70^{\circ}C$ $VDD = 3.0V, WDT disabled, -40^{\circ}C to +85^{\circ}C$ |

| D023*                 | Brown-out Reset Current<br>(Note 6)                                                                                                           | $\Delta$ IBOR | -           | 350               | 425          | μA             | BOR enabled VDD = 5.0V                                                                                                                                                  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption. The test conditions for all IDD measurements in active operation mode are:

$OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD <math>\overline{MCLR} = VDD; WDT$  enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

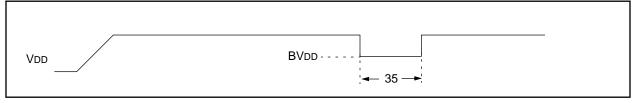

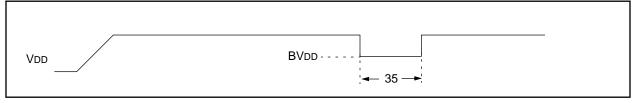

### FIGURE 17-5: BROWN-OUT RESET TIMING

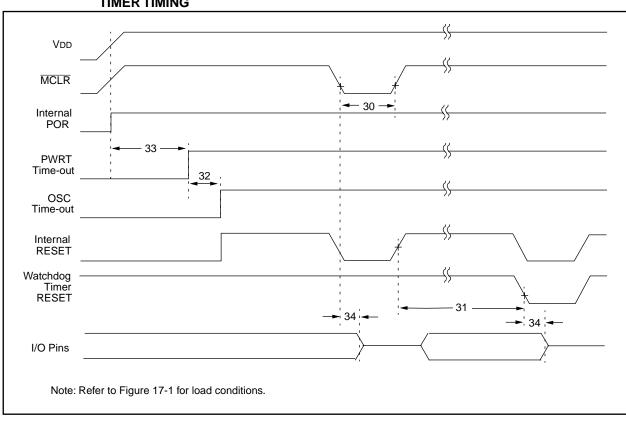

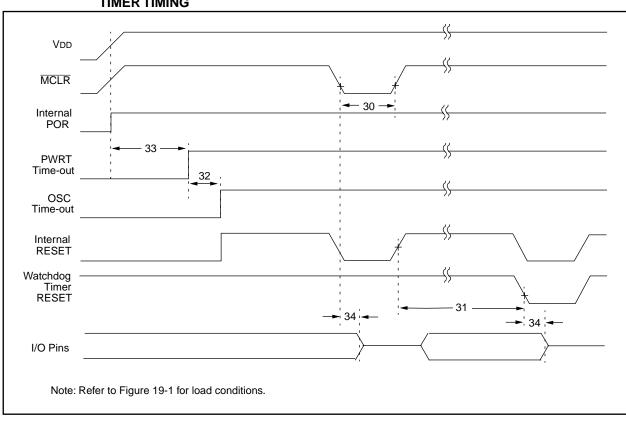

# TABLE 17-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†     | Мах | Units | Conditions                |

|------------------|-------|--------------------------------------------------------|-----|----------|-----|-------|---------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                 | 2   | —        | —   | μs    | VDD = 5V, -40°C to +125°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +125°C |

| 32               | Tost  | Oscillation Start-up Timer Period                      | _   | 1024Tosc | —   | —     | Tosc = OSC1 period        |

| 33*              | Tpwrt | Power-up Timer Period                                  | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +125°C |

| 34               | Tıoz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | _   | —        | 2.1 | μs    |                           |

| 35               | TBOR  | Brown-out Reset pulse width                            | 100 | _        | —   | μs    | $VDD \le BVDD (D005)$     |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# 18.0 ELECTRICAL CHARACTERISTICS FOR PIC16C73/74

### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                                    | 55 to +125°C                       |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage temperature                                                                                                               | 65°C to +150°C                     |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                                                | 0.3V to (VDD + 0.3V)               |

| Voltage on VDD with respect to Vss                                                                                                | 0.3 to +7.5V                       |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                      | 0 to +14V                          |

| Voltage on RA4 with respect to Vss                                                                                                | 0 to +14V                          |

| Total power dissipation (Note 1)                                                                                                  | 1.0W                               |

| Maximum current out of Vss pin                                                                                                    | 300 mA                             |

| Maximum current into VDD pin                                                                                                      | 250 mA                             |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                                      |                                    |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                                                    |                                    |

| Maximum output current sunk by any I/O pin                                                                                        | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                                                     | 25 mA                              |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                                               | 200 mA                             |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                                            | 200 mA                             |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                                                       | 200 mA                             |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                                                    | 200 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\Sigma$ IOH} + $\Sigma$ {(VDD -                   | Voh) x Ioh} + $\Sigma$ (Vol x Iol) |

| Note $0$ , $\lambda$ (alternative balance) (as a table $\overline{\mathbf{MOLD}}$ are inducting summation matching the $0$ or $0$ |                                    |

- **Note 2:** Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

- Note 3: PORTD and PORTE are not implemented on the PIC16C73.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# TABLE 18-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C73-04<br>PIC16C74-04                                                                                                                          | PIC16C73-10<br>PIC16C74-10                                                                                                                         | PIC16C73-20<br>PIC16C74-20                                                                                                                         | PIC16LC73-04<br>PIC16LC74-04                                                                 | JW Devices                                                                                                                                         |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                            | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 3.0V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 13.5 μA max. at 3V<br>Freq: 4 MHz max. | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                           |

| хт  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                            | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 3.0V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 13.5 μA max. at 3V<br>Freq: 4 MHz max. | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                           |

| HS  | VDD:         4.5V to 5.5V           IDD:         13.5 mA typ. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         4 MHz max. | VDD:         4.5V to 5.5V           IDD:         15 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         10 MHz max. | VDD:         4.5V to 5.5V           IDD:         30 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         20 MHz max. | Not recommended for<br>use in HS mode                                                        | VDD:         4.5V to 5.5V           IDD:         30 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         20 MHz max. |

| LP  | VDD: 4.0V to 6.0V<br>IDD: 52.5 μA typ. at<br>32 kHz, 4.0V<br>IPD: 0.9 μA typ. at 4.0V<br>Freq: 200 kHz max.                                         | Not recommended for<br>use in LP mode                                                                                                              | Not recommended for<br>use in LP mode                                                                                                              | VDD: 3.0V to 6.0V<br>IDD: 48 μA max. at<br>32 kHz 3.0V                                       |                                                                                                                                                    |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

|       |                                            | Standa                                                    | rd Opera                              | ting  | Conditio  | ons (un | less otherwise stated)                                                |  |

|-------|--------------------------------------------|-----------------------------------------------------------|---------------------------------------|-------|-----------|---------|-----------------------------------------------------------------------|--|

|       |                                            |                                                           | ing tempe                             | -     |           | •       | $\leq$ TA $\leq$ +125°C for extended,                                 |  |

|       | ARACTERISTICS                              | $-40^{\circ}$ C $\leq$ TA $\leq$ +85°C for industrial and |                                       |       |           |         |                                                                       |  |

|       | ARACTERISTICS                              |                                                           | $\leq$ TA $\leq$ +70°C for commercial |       |           |         |                                                                       |  |

|       |                                            | Operati                                                   | ing voltage                           | e Vdi | D range a | as desc | ribed in DC spec Section 19.1 and                                     |  |

|       |                                            | Section                                                   | i 19.2.                               |       |           |         |                                                                       |  |

| Param | Characteristic                             | Sym                                                       | Min                                   | Тур   | Max       | Units   | Conditions                                                            |  |

| No.   |                                            |                                                           |                                       | †     |           |         |                                                                       |  |

|       | Output High Voltage                        |                                                           |                                       |       |           |         |                                                                       |  |

| D090  | I/O ports (Note 3)                         | Voн                                                       | Vdd - 0.7                             | -     | -         | V       | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С                          |  |

| D090A |                                            |                                                           | Vdd - 0.7                             | -     | -         | V       | IOH = -2.5 mA, VDD = 4.5V,<br>-40°С to +125°С                         |  |

| D092  | OSC2/CLKOUT (RC osc config)                |                                                           | Vdd - 0.7                             | -     | -         | V       | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                          |  |

| D092A |                                            |                                                           | Vdd - 0.7                             | -     | -         | V       | IOH = -1.0 mA, VDD = 4.5V,<br>-40°С to +125°С                         |  |

| D150* | Open-Drain High Voltage                    | Vod                                                       | -                                     | -     | 14        | V       | RA4 pin                                                               |  |

|       | Capacitive Loading Specs on<br>Output Pins |                                                           |                                       |       |           |         |                                                                       |  |

| D100  | OSC2 pin                                   | Cosc2                                                     | -                                     | -     | 15        | pF      | In XT, HS and LP modes when exter<br>nal clock is used to drive OSC1. |  |

| D101  | All I/O pins and OSC2 (in RC               | Сю                                                        | -                                     | -     | 50        | pF      |                                                                       |  |

| D102  | mode) SCL, SDA in I <sup>2</sup> C mode    | Св                                                        | -                                     | -     | 400       | pF      |                                                                       |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C7X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

# FIGURE 19-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

### FIGURE 19-5: BROWN-OUT RESET TIMING

# TABLE 19-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†     | Max | Units | Conditions                |

|------------------|-------|--------------------------------------------------------|-----|----------|-----|-------|---------------------------|