Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 368 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                |

| Data Converters            | A/D 8x8b                                                                 |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc77-04-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 GENERAL DESCRIPTION

The PIC16C7X is a family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with integrated analog-to-digital (A/D) converters, in the PIC16CXX mid-range family.

All PIC16/17 microcontrollers employ an advanced RISC architecture. The PIC16CXX microcontroller family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches which require two cycles. A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The **PIC16C72** has 128 bytes of RAM and 22 I/O pins. In addition several peripheral features are available including: three timer/counters, one Capture/Compare/ PWM module and one serial port. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. Also a 5-channel high-speed 8-bit A/D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The PIC16C73/73A devices have 192 bytes of RAM, while the PIC16C76 has 368 byes of RAM. Each device has 22 I/O pins. In addition, several peripheral features are available including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. The Universal Syn-Asynchronous Receiver chronous Transmitter (USART) is also known as the Serial Communications Interface or SCI. Also a 5-channel high-speed 8-bit A/ D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The **PIC16C74/74A** devices have 192 bytes of RAM, while the **PIC16C77** has 368 bytes of RAM. Each device has 33 I/O pins. In addition several peripheral features are available including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. The Universal Synchronous Asynchronous Receiver Transmitter (USART) is also known as the Serial Communications Interface or SCI. An 8-bit Parallel Slave Port is provided. Also an 8-channel high-speed

8-bit A/D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The PIC16C7X family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) feature provides a power saving mode. The user can wake up the chip from SLEEP through several external and internal interrupts and resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lockup.

A UV erasable CERDIP packaged version is ideal for code development while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume.

The PIC16C7X family fits perfectly in applications ranging from security and remote sensors to appliance control and automotive. The EPROM technology makes customization of application programs (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16C7X very versatile even in areas where no microcontroller use has been considered before (e.g. timer functions, serial communication, capture and compare, PWM functions and coprocessor applications).

# 1.1 Family and Upward Compatibility

Users familiar with the PIC16C5X microcontroller family will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for the PIC16C5X can be easily ported to the PIC16CXX family of devices (Appendix B).

# 1.2 Development Support

PIC16C7X devices are supported by the complete line of Microchip Development tools.

Please refer to Section 16.0 for more details about Microchip's development tools.

| Address              | Name    | Bit 7                | Bit 6                         | Bit 5                     | Bit 4            | Bit 3        | Bit 2           | Bit 1         | Bit 0    | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(2) |

|----------------------|---------|----------------------|-------------------------------|---------------------------|------------------|--------------|-----------------|---------------|----------|--------------------------|-------------------------------------|

| Bank 1               |         |                      |                               |                           |                  |              |                 |               |          |                          |                                     |

| 80h <sup>(4)</sup>   | INDF    | Addressing           | this location                 | uses conter               | nts of FSR to ac | dress data   | memory (not     | a physical re | egister) | 0000 0000                | 0000 0000                           |

| 81h                  | OPTION  | RBPU                 | INTEDG                        | TOCS                      | TOSE             | PSA          | PS2             | PS1           | PS0      | 1111 1111                | 1111 1111                           |

| 82h <sup>(4)</sup>   | PCL     | Program Co           | ounter's (PC)                 | Least Signif              | ficant Byte      |              |                 |               |          | 0000 0000                | 0000 0000                           |

| 83h <b>(4)</b>       | STATUS  | IRP                  | RP1                           | RP0                       | TO               | PD           | Z               | DC            | С        | 0001 1xxx                | 000q quuu                           |

| 84h <sup>(4)</sup>   | FSR     | Indirect data        | a memory ac                   | dress pointe              | er               |              |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 85h                  | TRISA   | _                    | PORTA Data Direction Register |                           |                  |              |                 |               |          | 11 1111                  | 11 1111                             |

| 86h                  | TRISB   | PORTB Dat            | ta Direction F                | Register                  |                  |              |                 |               |          | 1111 1111                | 1111 1111                           |

| 87h                  | TRISC   | PORTC Dat            | ta Direction I                | Register                  |                  |              |                 |               |          | 1111 1111                | 1111 1111                           |

| 88h <b>(5)</b>       | TRISD   | PORTD Dat            | TD Data Direction Register    |                           |                  |              |                 |               |          | 1111 1111                | 1111 1111                           |

| 89h <b>(5)</b>       | TRISE   | IBF                  | OBF                           | IBOV                      | PSPMODE          | _            | PORTE Dat       | a Direction E | Bits     | 0000 -111                | 0000 -111                           |

| 8Ah <sup>(1,4)</sup> | PCLATH  | _                    | —                             | _                         | Write Buffer fo  | or the upper | 5 bits of the l | Program Cou   | Inter    | 0 0000                   | 0 0000                              |

| 8Bh <sup>(4)</sup>   | INTCON  | GIE                  | PEIE                          | TOIE                      | INTE             | RBIE         | TOIF            | INTF          | RBIF     | 0000 000x                | 0000 000u                           |

| 8Ch                  | PIE1    | PSPIE <sup>(3)</sup> | ADIE                          | RCIE                      | TXIE             | SSPIE        | CCP1IE          | TMR2IE        | TMR1IE   | 0000 0000                | 0000 0000                           |

| 8Dh                  | PIE2    | _                    | _                             | —                         | _                | _            | —               | —             | CCP2IE   | 0                        | 0                                   |

| 8Eh                  | PCON    | _                    | —                             | _                         | _                | _            | _               | POR           | BOR      | dd                       | uu                                  |

| 8Fh                  | _       | Unimpleme            | nted                          | •                         |                  | •            |                 | •             | •        | _                        | _                                   |

| 90h                  | _       | Unimpleme            | nted                          |                           |                  |              |                 |               |          | _                        | _                                   |

| 91h                  | _       | Unimpleme            | nted                          |                           |                  |              |                 |               |          | -                        | _                                   |

| 92h                  | PR2     | Timer2 Peri          | od Register                   |                           |                  |              |                 |               |          | 1111 1111                | 1111 1111                           |

| 93h                  | SSPADD  | Synchronou           | us Serial Por                 | t (I <sup>2</sup> C mode) | Address Regis    | ter          |                 |               |          | 0000 0000                | 0000 0000                           |

| 94h                  | SSPSTAT | SMP                  | CKE                           | D/Ā                       | Р                | S            | R/W             | UA            | BF       | 0000 0000                | 0000 0000                           |

| 95h                  | _       | Unimpleme            | nted                          | •                         |                  |              |                 |               | •        | _                        | _                                   |

| 96h                  | _       | Unimpleme            | nted                          |                           |                  |              |                 |               |          | _                        | _                                   |

| 97h                  | _       | Unimpleme            | nted                          |                           |                  |              |                 |               |          | _                        | _                                   |

| 98h                  | TXSTA   | CSRC                 | ТХ9                           | TXEN                      | SYNC             | _            | BRGH            | TRMT          | TX9D     | 0000 -010                | 0000 -010                           |

| 99h                  | SPBRG   | Baud Rate            | Generator R                   | egister                   |                  |              |                 |               |          | 0000 0000                | 0000 0000                           |

| 9Ah                  | _       | Unimpleme            | nted                          |                           |                  |              |                 |               |          | _                        | _                                   |

| 9Bh                  | _       | Unimpleme            | nted                          |                           |                  |              |                 |               |          | _                        | _                                   |

| 9Ch                  | _       | Unimpleme            | nted                          |                           |                  |              |                 |               |          | _                        | _                                   |

| 9Dh                  | -       | Unimpleme            | nted                          |                           |                  |              |                 |               |          | _                        | —                                   |

| 9Eh                  | -       | Unimpleme            | nted                          |                           |                  |              |                 |               |          | -                        | —                                   |

| 9Fh                  | ADCON1  | _                    | _                             | _                         | _                | _            | PCFG2           | PCFG1         | PCFG0    | 000                      | 000                                 |

# TABLE 4-3: PIC16C76/77 SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the PIC16C76, always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD and PORTE are not physically implemented on the PIC16C76, read as '0'.

NOTES:

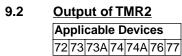

# 9.0 TIMER2 MODULE

# Applicable Devices 72|73|73A|74|74A|76|77

Timer2 is an 8-bit timer with a prescaler and a postscaler. It can be used as the PWM time-base for PWM mode of the CCP module(s). The TMR2 register is readable and writable, and is cleared on any device reset.

The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

The Timer2 module has an 8-bit period register PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon reset.

The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, (PIR1<1>)).

Timer2 can be shut off by clearing control bit TMR2ON (T2CON<2>) to minimize power consumption.

Figure 9-2 shows the Timer2 control register.

# 9.1 <u>Timer2 Prescaler and Postscaler</u> Applicable Devices

72 73 73A 74 74A 76 77

The prescaler and postscaler counters are cleared when any of the following occurs:

- a write to the TMR2 register

- a write to the T2CON register

- any device reset (Power-on Reset, MCLR reset, Watchdog Timer reset, or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module which optionally uses it to generate shift clock.

# FIGURE 9-1: TIMER2 BLOCK DIAGRAM

# 11.0 SYNCHRONOUS SERIAL PORT (SSP) MODULE

# 11.1 SSP Module Overview

The Synchronous Serial Port (SSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

The SSP module in  $I^2C$  mode works the same in all PIC16C7X devices that have an SSP module. However the SSP Module in SPI mode has differences between the PIC16C76/77 and the other PIC16C7X devices.

The register definitions and operational description of SPI mode has been split into two sections because of the differences between the PIC16C76/77 and the other PIC16C7X devices. The default reset values of both the SPI modules is the same regardless of the device:

| 11.2 | SPI Mode for PIC16C72/73/73A/74/74A | 78 |

|------|-------------------------------------|----|

| 11.3 | SPI Mode for PIC16C76/77            | 83 |

| 11.4 | I2C <sup>™</sup> Overview           | 89 |

| 11.5 | SSP I2C Operation                   | 93 |

Refer to Application Note AN578, "Use of the SSP Module in the  $l^2C$  Multi-Master Environment."

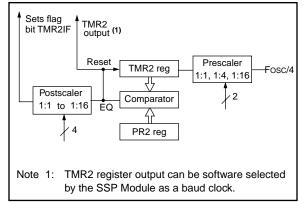

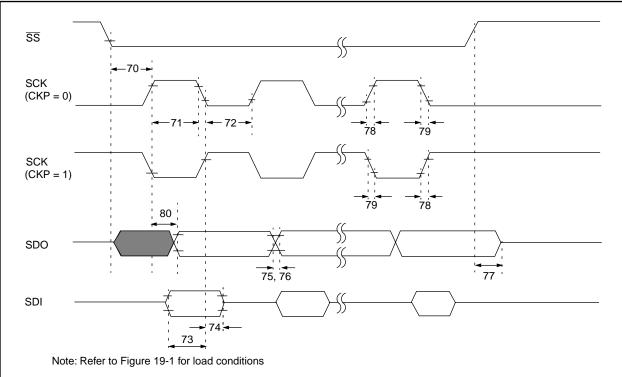

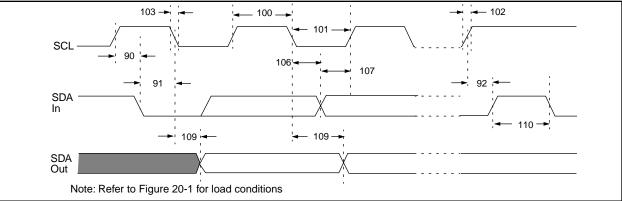

# FIGURE 11-13: SPI MODE TIMING (SLAVE MODE WITH CKE = 1) (PIC16C76/77)

| <b>TABLE 11-2:</b> | <b>REGISTERS ASSOCIATED WITH SPI OPERATION (F</b> | PIC16C76/77) |  |

|--------------------|---------------------------------------------------|--------------|--|

|                    |                                                   |              |  |

| Address               | Name    | Bit 7                | Bit 6       | Bit 5      | Bit 4                         | Bit 3     | Bit 2      | Bit 1  | Bit 0  | Value<br>PC<br>BC | ,    | all o | e on<br>other<br>sets |

|-----------------------|---------|----------------------|-------------|------------|-------------------------------|-----------|------------|--------|--------|-------------------|------|-------|-----------------------|

| 0Bh,8Bh.<br>10Bh,18Bh | INTCON  | GIE                  | PEIE        | TOIE       | INTE                          | RBIE      | TOIF       | INTF   | RBIF   | 0000              | 000x | 0000  | 000u                  |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup> | ADIF        | RCIF       | TXIF                          | SSPIF     | CCP1IF     | TMR2IF | TMR1IF | 0000              | 0000 | 0000  | 0000                  |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup> | ADIE        | RCIE       | TXIE                          | SSPIE     | CCP1IE     | TMR2IE | TMR1IE | 0000              | 0000 | 0000  | 0000                  |

| 87h                   | TRISC   | PORTC Da             | ta Directio | on Registe | er                            |           |            |        |        | 1111              | 1111 | 1111  | 1111                  |

| 13h                   | SSPBUF  | Synchronou           | us Serial F | Port Recei | ve Buff                       | er/Transm | it Registe | r      |        | xxxx              | xxxx | uuuu  | uuuu                  |

| 14h                   | SSPCON  | WCOL                 | SSPOV       | SSPEN      | СКР                           | SSPM3     | SSPM2      | SSPM1  | SSPM0  | 0000              | 0000 | 0000  | 0000                  |

| 85h                   | TRISA   | —                    | —           | PORTA [    | PORTA Data Direction Register |           |            |        |        | 11                | 1111 | 11    | 1111                  |

| 94h                   | SSPSTAT | SMP                  | CKE         | D/Ā        | Р                             | S         | R/W        | UA     | BF     | 0000              | 0000 | 0000  | 0000                  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the SSP in SPI mode. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C76, always maintain these bits clear.

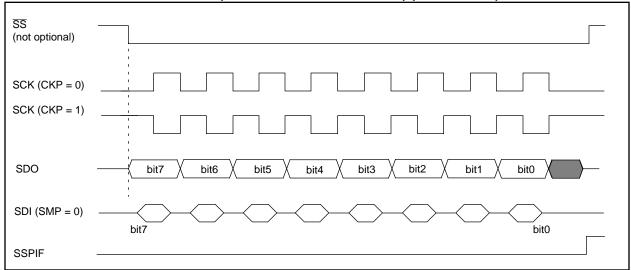

# 11.4.4 MULTI-MASTER

The  $I^2C$  protocol allows a system to have more than one master. This is called multi-master. When two or more masters try to transfer data at the same time, arbitration and synchronization occur.

### 11.4.4.1 ARBITRATION

Arbitration takes place on the SDA line, while the SCL line is high. The master which transmits a high when the other master transmits a low loses arbitration (Figure 11-22), and turns off its data output stage. A master which lost arbitration can generate clock pulses until the end of the data byte where it lost arbitration. When the master devices are addressing the same device, arbitration continues into the data.

# FIGURE 11-22: MULTI-MASTER ARBITRATION (TWO MASTERS)

Masters that also incorporate the slave function, and have lost arbitration must immediately switch over to slave-receiver mode. This is because the winning master-transmitter may be addressing it.

Arbitration is not allowed between:

- A repeated START condition

- A STOP condition and a data bit

- A repeated START condition and a STOP condition

Care needs to be taken to ensure that these conditions do not occur.

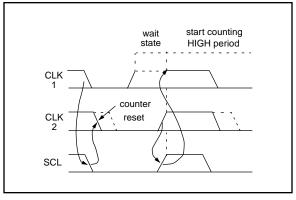

# 11.2.4.2 Clock Synchronization

Clock synchronization occurs after the devices have started arbitration. This is performed using a wired-AND connection to the SCL line. A high to low transition on the SCL line causes the concerned devices to start counting off their low period. Once a device clock has gone low, it will hold the SCL line low until its SCL high state is reached. The low to high transition of this clock may not change the state of the SCL line, if another device clock is still within its low period. The SCL line is held low by the device with the longest low period. Devices with shorter low periods enter a high wait-state, until the SCL line comes high. When the SCL line comes high, all devices start counting off their high periods. The first device to complete its high period will pull the SCL line low. The SCL line high time is determined by the device with the shortest high period, Figure 11-23.

# FIGURE 11-23: CLOCK SYNCHRONIZATION

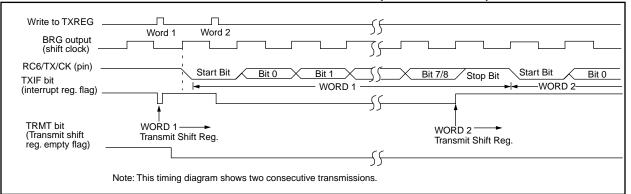

Steps to follow when setting up an Asynchronous Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH. (Section 12.1)

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

# FIGURE 12-8: ASYNCHRONOUS MASTER TRANSMISSION

# FIGURE 12-9: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

# TABLE 12-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address | Name  | Bit 7                | Bit 6    | Bit 5      | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|----------------------|----------|------------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF     | RCIF       | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h     | RCSTA | SPEN                 | RX9      | SREN       | CREN  | —     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                       |

| 19h     | TXREG | USART Trar           | nsmit Re | gister     |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE     | RCIE       | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h     | TXSTA | CSRC                 | TX9      | TXEN       | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h     | SPBRG | Baud Rate (          | Generato | r Register | r     |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

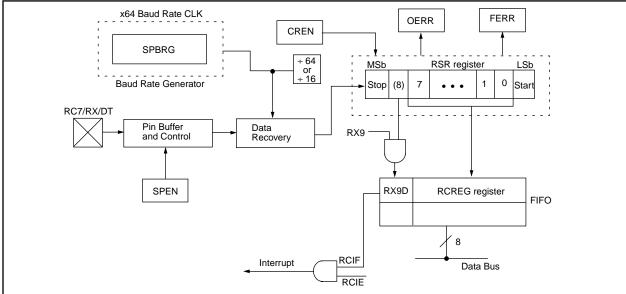

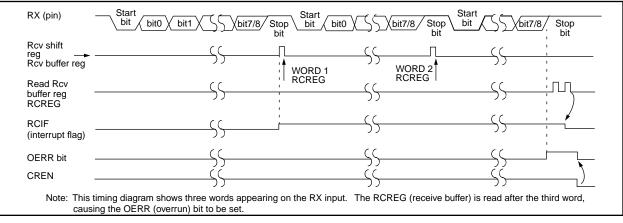

### 12.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 12-10. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the receive (serial) shift register (RSR). After sampling the STOP bit, the received data in the RSR is transferred to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit which is cleared by the hardware. It is cleared when the RCREG register has been read and is empty. The RCREG is a

### FIGURE 12-10: USART RECEIVE BLOCK DIAGRAM

double buffered register, i.e. it is a two deep FIFO. It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte begin shifting to the RSR register. On the detection of the STOP bit of the third byte, if the RCREG register is still full then overrun error bit OERR (RCSTA<1>) will be set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit OERR has to be cleared in software. This is done by resetting the receive logic (CREN is cleared and then set). If bit OERR is set, transfers from the RSR register to the RCREG register are inhibited, so it is essential to clear error bit OERR if it is set. Framing error bit FERR (RCSTA<2>) is set if a stop bit is detected as clear. Bit FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG, will load bits RX9D and FERR with new values, therefore it is essential for the user to read the RCSTA register before reading RCREG register in order not to lose the old FERR and RX9D information.

# 13.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

# Applicable Devices

The analog-to-digital (A/D) converter module has five inputs for the PIC16C72/73/73A/76, and eight for the PIC16C74/74A/77.

The A/D allows conversion of an analog input signal to a corresponding 8-bit digital number (refer to Application Note AN546 for use of A/D Converter). The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltage is software selectable to either the device's positive supply voltage (VDD) or the voltage level on the RA3/AN3/VREF pin. The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The A/D module has three registers. These registers are:

- A/D Result Register (ADRES)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

The ADCON0 register, shown in Figure 13-1, controls the operation of the A/D module. The ADCON1 register, shown in Figure 13-2, configures the functions of the port pins. The port pins can be configured as analog inputs (RA3 can also be a voltage reference) or as digital I/O.

| R/W-0                                                                                | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0                                                                                                 | R/W-0                                                                            | R/W-0      | R/W-0                                | U-0         | R/W-0     |                                                                                       |  |  |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------|--------------------------------------|-------------|-----------|---------------------------------------------------------------------------------------|--|--|

| ADCS1                                                                                | ADCS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CHS2                                                                                                  | CHS1                                                                             | CHS0       | GO/DONE                              | _           | ADON      | R = Readable bit                                                                      |  |  |

| bit7                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |                                                                                  |            |                                      |             | bit0      | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |  |

| bit 7-6:                                                                             | 00 = Fos<br>01 = Fos<br>10 = Fos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | c/2<br>c/8<br>c/32                                                                                    |                                                                                  |            | Select bits                          | ·)          |           |                                                                                       |  |  |

| bit 5-3:                                                                             | 000 = cha<br>001 = cha<br>010 = cha<br>011 = cha<br>100 = cha<br>101 = cha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | annel 0, (F<br>annel 1, (F<br>annel 2, (F<br>annel 3, (F<br>annel 4, (F<br>annel 5, (F<br>annel 6, (F | RĂO/ANO)<br>RA1/AN1)<br>RA2/AN2)<br>RA3/AN3)<br>RA5/AN4)<br>RE0/AN5)<br>RE0/AN5) | [1)        | ts                                   |             |           |                                                                                       |  |  |

| bit 2:                                                                               | GO/DON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | E: A/D Co                                                                                             | nversion S                                                                       | Status bit |                                      |             |           |                                                                                       |  |  |

|                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | onversion                                                                                             |                                                                                  |            | this bit starts t<br>bit is automati |             |           | are when the A/D conversion                                                           |  |  |

| bit 1:                                                                               | Unimpler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | nented: F                                                                                             | Read as '0                                                                       | ,          |                                      |             |           |                                                                                       |  |  |

| bit 0:                                                                               | <b>ADON</b> : $A/A = A/D c $ | onverter n                                                                                            |                                                                                  |            | d consumes no                        | o operating | g current |                                                                                       |  |  |

| <b>Note 1:</b> A/D channels 5, 6, and 7 are implemented on the PIC16C74/74A/77 only. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       |                                                                                  |            |                                      |             |           |                                                                                       |  |  |

# FIGURE 13-1: ADCON0 REGISTER (ADDRESS 1Fh)

# 14.8 Power-down Mode (SLEEP) Applicable Devices 727373A7474A7677

Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD, or Vss, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D, disable external clocks. Pull all I/O pins, that are hi-impedance inputs, high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

#### 14.8.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change, or some Peripheral Interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. SSP (Start/Stop) bit detect interrupt.

- 3. SSP transmit or receive in slave mode (SPI/ $l^2$ C).

- 4. CCP capture mode interrupt.

- 5. Parallel Slave Port read or write.

- 6. A/D conversion (when A/D clock source is RC).

- 7. Special event trigger (Timer1 in asynchronous mode using an external clock).

- 8. USART TX or RX (synchronous slave mode).

Other peripherals cannot generate interrupts since during SLEEP, no on-chip Q clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

### 14.8.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

| NOP               | No Oper       | ation            |                  |                  |  |  |  |  |  |

|-------------------|---------------|------------------|------------------|------------------|--|--|--|--|--|

| Syntax:           | [ label ]     | NOP              |                  |                  |  |  |  |  |  |

| Operands:         | None          |                  |                  |                  |  |  |  |  |  |

| Operation:        | No operation  |                  |                  |                  |  |  |  |  |  |

| Status Affected:  | None          |                  |                  |                  |  |  |  |  |  |

| Encoding:         | 00            | 0000             | 0xx0             | 0000             |  |  |  |  |  |

| Description:      | No operation. |                  |                  |                  |  |  |  |  |  |

| Words:            | 1             |                  |                  |                  |  |  |  |  |  |

| Cycles:           | 1             |                  |                  |                  |  |  |  |  |  |

| Q Cycle Activity: | Q1            | Q2               | Q3               | Q4               |  |  |  |  |  |

|                   | Decode        | No-<br>Operation | No-<br>Operation | No-<br>Operation |  |  |  |  |  |

| Example           | NOP           |                  |                  |                  |  |  |  |  |  |

| RETFIE                       | Return from Interrupt                                                                        |                                                            |                                                           |                            |  |  |  |  |

|------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------|----------------------------|--|--|--|--|

| Syntax:                      | [ label ]                                                                                    | RETFIE                                                     |                                                           |                            |  |  |  |  |

| Operands:                    | None                                                                                         |                                                            |                                                           |                            |  |  |  |  |

| Operation:                   | $\begin{array}{l} \text{TOS} \rightarrow \text{PC}, \\ 1 \rightarrow \text{GIE} \end{array}$ |                                                            |                                                           |                            |  |  |  |  |

| Status Affected:             | None                                                                                         |                                                            |                                                           |                            |  |  |  |  |

| Encoding:                    | 00                                                                                           | 0000                                                       | 0000                                                      | 1001                       |  |  |  |  |

|                              | •                                                                                            | · ·                                                        | ) is load                                                 |                            |  |  |  |  |

|                              | PC. Interru<br>Global Inte                                                                   | upts are er<br>errupt Ena<br><7>). This i                  | ble bit, GIE                                              | setting                    |  |  |  |  |

| Words:                       | PC. Interru<br>Global Inte<br>(INTCON<                                                       | upts are er<br>errupt Ena<br><7>). This i                  | habled by s<br>ble bit, GIE                               | setting                    |  |  |  |  |

| Words:<br>Cycles:            | PC. Interru<br>Global Inte<br>(INTCON-<br>instruction                                        | upts are er<br>errupt Ena<br><7>). This i                  | habled by s<br>ble bit, GIE                               | setting                    |  |  |  |  |

|                              | PC. Interru<br>Global Inte<br>(INTCON-<br>instruction                                        | upts are er<br>errupt Ena<br><7>). This i                  | habled by s<br>ble bit, GIE                               | setting                    |  |  |  |  |

| Cycles:                      | PC. Interru<br>Global Inte<br>(INTCON-<br>instruction<br>1<br>2                              | upts are er<br>errupt Ena<br><7>). This i                  | nabled by s<br>ble bit, GIE<br>is a two cy                | setting<br>cle<br>Q4       |  |  |  |  |

| Cycles:<br>Q Cycle Activity: | PC. Interru<br>Global Inte<br>(INTCON-<br>instruction<br>1<br>2<br>Q1                        | upts are er<br>errupt Ena<br><7>). This i<br><br>Q2<br>No- | abled by s<br>ble bit, GIE<br>s a two cy<br>Q3<br>Set the | setting<br><u>=</u><br>cle |  |  |  |  |

After Interrupt PC = TOS GIE = 1

| OPTION                 | Load Op                                                                                                                                                                                                                                            | tion Reg | gister |  |  |  |  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|--|--|--|--|

| Syntax:                | [ label ]                                                                                                                                                                                                                                          | OPTION   | ٧      |  |  |  |  |

| Operands:              | None                                                                                                                                                                                                                                               |          |        |  |  |  |  |

| Operation:             | $(W) \to OPTION$                                                                                                                                                                                                                                   |          |        |  |  |  |  |

| Status Affected:       | None                                                                                                                                                                                                                                               |          |        |  |  |  |  |

| Encoding:              | 00 0000 0110 0010                                                                                                                                                                                                                                  |          |        |  |  |  |  |

| Description:<br>Words: | The contents of the W register are<br>loaded in the OPTION register. This<br>instruction is supported for code com-<br>patibility with PIC16C5X products.<br>Since OPTION is a readable/writable<br>register, the user can directly address<br>it. |          |        |  |  |  |  |

| Cycles:                | 1                                                                                                                                                                                                                                                  |          |        |  |  |  |  |

| Example                | ·                                                                                                                                                                                                                                                  |          |        |  |  |  |  |

|                        | To maintain upward compatibility<br>with future PIC16CXX products, do<br>not use this instruction.                                                                                                                                                 |          |        |  |  |  |  |

|                        |                                                                                                                                                                                                                                                    |          |        |  |  |  |  |

# Applicable Devices 72 73 73A 74 74A 76 77

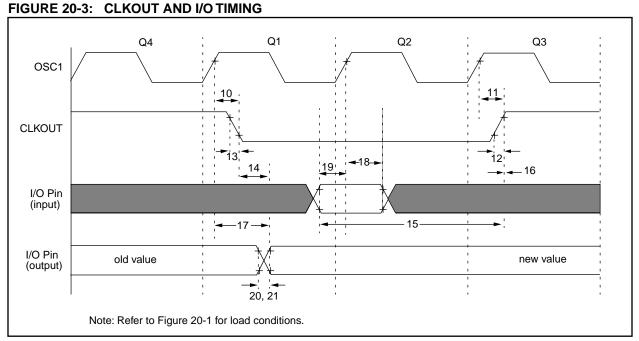

#### 17.4 **Timing Parameter Symbology**

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2p             | pS                                      | 3. TCC:ST | (I <sup>2</sup> C specifications only) |

|-----------------------|-----------------------------------------|-----------|----------------------------------------|

| 2. TppS               |                                         | 4. Ts     | (I <sup>2</sup> C specifications only) |

| т                     |                                         |           |                                        |

| F                     | Frequency                               | Т         | Time                                   |

| Lowerca               | ase letters (pp) and their meanings:    |           |                                        |

| рр                    |                                         |           |                                        |

| CC                    | CCP1                                    | OSC       | OSC1                                   |

| ck                    | CLKOUT                                  | rd        | RD                                     |

| CS                    | CS                                      | rw        | $\overline{RD}$ or $\overline{WR}$     |

| di                    | SDI                                     | SC        | SCK                                    |

| do                    | SDO                                     | SS        | SS                                     |

| dt                    | Data in                                 | tO        | TOCKI                                  |

| io                    | I/O port                                | t1        | T1CKI                                  |

| mc                    | MCLR                                    | wr        | WR                                     |

| Upperca               | ase letters and their meanings:         |           |                                        |

| S                     |                                         |           |                                        |

| F                     | Fall                                    | P         | Period                                 |

| Н                     | High                                    | R         | Rise                                   |

| I                     | Invalid (Hi-impedance)                  | V         | Valid                                  |

| L                     | Low                                     | Z         | Hi-impedance                           |

| I <sup>2</sup> C only |                                         |           |                                        |

| AA                    | output access                           | High      | High                                   |

| BUF                   | Bus free                                | Low       | Low                                    |

| Tcc:st (              | (I <sup>2</sup> C specifications only)  | I         |                                        |

| CC                    |                                         |           |                                        |

| HD                    | Hold                                    | SU        | Setup                                  |

| ST                    |                                         |           | Comp                                   |

| DAT                   | DATA input hold                         | STO       | STOP condition                         |

| STA                   | START condition                         |           |                                        |

|                       |                                         |           |                                        |

| FIGURE 1              | 17-1: LOAD CONDITIONS                   |           |                                        |

|                       | Load condition 1                        |           | Load condition 2                       |

|                       | N = = /0                                |           |                                        |

|                       |                                         |           |                                        |

|                       | J                                       |           |                                        |

|                       | $\leq$ RL                               |           |                                        |

|                       | $ \leq $                                | N         |                                        |

|                       | I → I                                   |           | X                                      |

|                       |                                         | F         |                                        |

|                       | • • • • • • • • • • • • • • • • • • • • | ,         | ···· ↓                                 |

|                       | Vss                                     |           | Vss                                    |

|                       | $RL$ = 464 $\Omega$                     |           |                                        |

|                       |                                         |           |                                        |

|                       | $C_L = 50 \text{ pF}$ for all pins ex   | cept 0502 |                                        |

15 pF for OSC2 output

# Applicable Devices 72 73 73A 74 74A 76 77

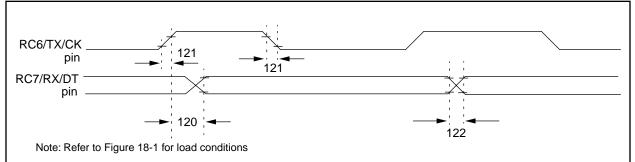

# FIGURE 18-11: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

# TABLE 18-11: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                    |                       | Min | Тур† | Max | Units | Conditions |

|------------------|----------|-----------------------------------|-----------------------|-----|------|-----|-------|------------|

| 120              | TckH2dtV | SYNC XMIT (MASTER &<br>SLAVE)     | PIC16 <b>C</b> 73/74  | _   | _    | 80  | ns    |            |

|                  |          | Clock high to data out valid      | PIC16 <b>LC</b> 73/74 | _   | —    | 100 | ns    |            |

| 121              | Tckrf    | Clock out rise time and fall time | PIC16 <b>C</b> 73/74  | _   | —    | 45  | ns    |            |

|                  |          | (Master Mode)                     | PIC16 <b>LC</b> 73/74 | _   | —    | 50  | ns    |            |

| 122              | Tdtrf    | Data out rise time and fall time  | PIC16 <b>C</b> 73/74  | _   | —    | 45  | ns    |            |

|                  |          |                                   | PIC16 <b>LC</b> 73/74 | _   | —    | 50  | ns    |            |

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

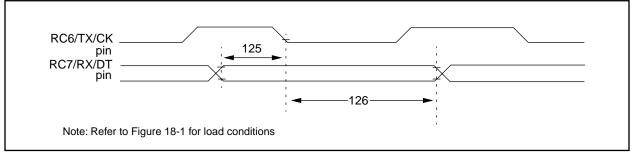

# FIGURE 18-12: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

# TABLE 18-12: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                                 | Min | Тур† | Мах | Units | Conditions |

|------------------|----------|--------------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data setup before $CK \downarrow (DT setup time)$ | 15  |      | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                 | 15  | —    | —   | ns    |            |