Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                 |

| Data Converters            | A/D 8x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-QFP                                                                    |

| Supplier Device Package    | 44-MQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc77-04-pq |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 GENERAL DESCRIPTION

The PIC16C7X is a family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with integrated analog-to-digital (A/D) converters, in the PIC16CXX mid-range family.

All PIC16/17 microcontrollers employ an advanced RISC architecture. The PIC16CXX microcontroller family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with the separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches which require two cycles. A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The **PIC16C72** has 128 bytes of RAM and 22 I/O pins. In addition several peripheral features are available including: three timer/counters, one Capture/Compare/ PWM module and one serial port. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. Also a 5-channel high-speed 8-bit A/D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The PIC16C73/73A devices have 192 bytes of RAM, while the PIC16C76 has 368 byes of RAM. Each device has 22 I/O pins. In addition, several peripheral features are available including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. The Universal Syn-Asynchronous Receiver chronous Transmitter (USART) is also known as the Serial Communications Interface or SCI. Also a 5-channel high-speed 8-bit A/ D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The **PIC16C74/74A** devices have 192 bytes of RAM, while the **PIC16C77** has 368 bytes of RAM. Each device has 33 I/O pins. In addition several peripheral features are available including: three timer/counters, two Capture/Compare/PWM modules and two serial ports. The Synchronous Serial Port can be configured as either a 3-wire Serial Peripheral Interface (SPI) or the two-wire Inter-Integrated Circuit (I<sup>2</sup>C) bus. The Universal Synchronous Asynchronous Receiver Transmitter (USART) is also known as the Serial Communications Interface or SCI. An 8-bit Parallel Slave Port is provided. Also an 8-channel high-speed

8-bit A/D is provided. The 8-bit resolution is ideally suited for applications requiring low-cost analog interface, e.g. thermostat control, pressure sensing, etc.

The PIC16C7X family has special features to reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) feature provides a power saving mode. The user can wake up the chip from SLEEP through several external and internal interrupts and resets.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lockup.

A UV erasable CERDIP packaged version is ideal for code development while the cost-effective One-Time-Programmable (OTP) version is suitable for production in any volume.

The PIC16C7X family fits perfectly in applications ranging from security and remote sensors to appliance control and automotive. The EPROM technology makes customization of application programs (transmitter codes, motor speeds, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low cost, low power, high performance, ease of use and I/O flexibility make the PIC16C7X very versatile even in areas where no microcontroller use has been considered before (e.g. timer functions, serial communication, capture and compare, PWM functions and coprocessor applications).

# 1.1 Family and Upward Compatibility

Users familiar with the PIC16C5X microcontroller family will realize that this is an enhanced version of the PIC16C5X architecture. Please refer to Appendix A for a detailed list of enhancements. Code written for the PIC16C5X can be easily ported to the PIC16CXX family of devices (Appendix B).

# 1.2 Development Support

PIC16C7X devices are supported by the complete line of Microchip Development tools.

Please refer to Section 16.0 for more details about Microchip's development tools.

# 2.0 PIC16C7X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC16C7X Product Identification System section at the end of this data sheet. When placing orders, please use that page of the data sheet to specify the correct part number.

For the PIC16C7X family, there are two device "types" as indicated in the device number:

- 1. **C**, as in PIC16**C**74. These devices have EPROM type memory and operate over the standard voltage range.

- 2. LC, as in PIC16LC74. These devices have EPROM type memory and operate over an extended voltage range.

## 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART<sup>®</sup> Plus and PRO MATE<sup>®</sup> II programmers both support programming of the PIC16C7X.

## 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

# 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

# 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random, or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password, or ID number.

| Pin Name                | DIP<br>Pin# | PLCC<br>Pin#      | QFP<br>Pin# | l/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                              |

|-------------------------|-------------|-------------------|-------------|---------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN              | 13          | 14                | 30          | I             | ST/CMOS <sup>(4)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                    |

| OSC2/CLKOUT             | 14          | 15                | 31          | 0             | _                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp                | 1           | 2                 | 18          | I/P           | ST                     | Master clear (reset) input or programming voltage input.<br>This pin is an active low reset to the device.                                                                                               |

|                         |             |                   |             |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                      |

| RA0/AN0                 | 2           | 3                 | 19          | I/O           | TTL                    | RA0 can also be analog input0                                                                                                                                                                            |

| RA1/AN1                 | 3           | 4                 | 20          | I/O           | TTL                    | RA1 can also be analog input1                                                                                                                                                                            |

| RA2/AN2                 | 4           | 5                 | 21          | I/O           | TTL                    | RA2 can also be analog input2                                                                                                                                                                            |

| RA3/AN3/Vref            | 5           | 6                 | 22          | I/O           | TTL                    | RA3 can also be analog input3 or analog reference voltage                                                                                                                                                |

| RA4/T0CKI               | 6           | 7                 | 23          | I/O           | ST                     | RA4 can also be the clock input to the Timer0 timer/ counter. Output is open drain type.                                                                                                                 |

| RA5/ <del>SS</del> /AN4 | 7           | 8                 | 24          | I/O           | TTL                    | RA5 can also be analog input4 or the slave select for the synchronous serial port.                                                                                                                       |

|                         |             |                   |             |               |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                            |

| RB0/INT                 | 33          | 36                | 8           | I/O           | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                              |

| RB1                     | 34          | 37                | 9           | I/O           | TTL                    |                                                                                                                                                                                                          |

| RB2                     | 35          | 38                | 10          | I/O           | TTL                    |                                                                                                                                                                                                          |

| RB3                     | 36          | 39                | 11          | I/O           | TTL                    |                                                                                                                                                                                                          |

| RB4                     | 37          | 41                | 14          | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                 |

| RB5                     | 38          | 42                | 15          | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                 |

| RB6                     | 39          | 43                | 16          | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming clock.                                                                                                                                                       |

| RB7                     | 40          | 44                | 17          | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming data.                                                                                                                                                        |

| Legend: I = input       | 0 = 0       | utput<br>lot used |             |               | put/output             | P = power<br>ST = Schmitt Trigger input                                                                                                                                                                  |

| TABLE 3-3: PIC16C/4//4A/// PINOUT DESCRIPTION | TABLE 3-3: | PIC16C74/74A/77 PINOUT DESCRIPTION |

|-----------------------------------------------|------------|------------------------------------|

|-----------------------------------------------|------------|------------------------------------|

— = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

# 10.0 CAPTURE/COMPARE/PWM MODULE(s)

Applicable Devices

72

73

73A

74

74A

76

77

CCP1

72

73

73A

74

74A

76

77

CCP2

Each CCP (Capture/Compare/PWM) module contains a 16-bit register which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave Duty Cycle register. Both the CCP1 and CCP2 modules are identical in operation, with the exception of the operation of the special event trigger. Table 10-1 and Table 10-2 show the resources and interactions of the CCP module(s). In the following sections, the operation of a CCP module is described with respect to CCP1. CCP2 operates the same as CCP1, except where noted.

## CCP1 module:

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

## CCP2 module:

Capture/Compare/PWM Register2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. All are readable and writable.

For use of the CCP modules, refer to the Embedded Control Handbook, "Using the CCP Modules" (AN594).

## TABLE 10-1: CCP MODE - TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

# TABLE 10-2: INTERACTION OF TWO CCP MODULES

| CCPx Mode | CCPy Mode | Interaction                                                                           |

|-----------|-----------|---------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time-base.                                                                  |

| Capture   | Compare   | The compare should be configured for the special event trigger, which clears TMR1.    |

| Compare   | Compare   | The compare(s) should be configured for the special event trigger, which clears TMR1. |

| PWM       | PWM       | The PWMs will have the same frequency, and update rate (TMR2 interrupt).              |

| PWM       | Capture   | None                                                                                  |

| PWM       | Compare   | None                                                                                  |

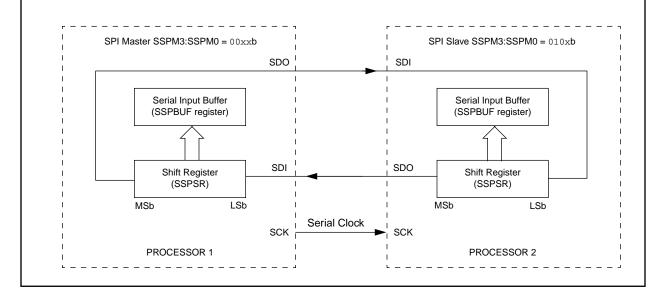

To enable the serial port, SSP enable bit SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear enable bit SSPEN, re-initialize SSPCON register, and then set enable bit SSPEN. This configures the SDI, SDO, SCK, and SS pins as serial port pins. For the pins to behave as the serial port function, they must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- SDI must have TRISC<4> set

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- <u>SS</u> must have TRISA<5> set (if implemented)

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value. An example would be in master mode where you are only sending data (to a display driver), then both SDI and SS could be used as general purpose outputs by clearing their corresponding TRIS register bits.

Figure 11-4 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge, and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- · Master sends dummy data Slave sends data

# FIGURE 11-4: SPI MASTER/SLAVE CONNECTION

The master can initiate the data transfer at any time because it controls the SCK. The master determines when the slave (Processor 2) is to broadcast data by the software protocol.

In master mode the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SCK output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and status bits appropriately set). This could be useful in receiver applications as a "line activity monitor" mode.

In slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched interrupt flag bit SSPIF (PIR1<3>) is set.

The clock polarity is selected by appropriately programming bit CKP (SSPCON<4>). This then would give waveforms for SPI communication as shown in Figure 11-5 and Figure 11-6 where the MSB is transmitted first. In master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or TCY)

- Fosc/16 (or 4 TCY)

- Fosc/64 (or 16 TCY)

- Timer2 output/2

This allows a maximum bit clock frequency (at 20 MHz) of 5 MHz. When in slave mode the external clock must meet the minimum high and low times.

In sleep mode, the slave can transmit and receive data and wake the device from sleep.

#### 11.5.2 MASTER MODE

Master mode of operation is supported in firmware using interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is idle and both the S and P bits are clear.

In master mode the SCL and SDA lines are manipulated by clearing the corresponding TRISC<4:3> bit(s). The output level is always low, irrespective of the value(s) in PORTC<4:3>. So when transmitting data, a '1' data bit must have the TRISC<4> bit set (input) and a '0' data bit must have the TRISC<4> bit cleared (output). The same scenario is true for the SCL line with the TRISC<3> bit.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- START condition

- STOP condition

- Data transfer byte transmitted/received

Master mode of operation can be done with either the slave mode idle (SSPM3:SSPM0 = 1011) or with the slave active. When both master and slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

#### 11.5.3 MULTI-MASTER MODE

In multi-master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the SSP module is disabled. The STOP (P) and START (S) bits will toggle based on the START and STOP conditions. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle and both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and a low level is present, the device needs to release the SDA and SCL lines (set TRISC<4:3>). There are two stages where this arbitration can be lost, these are:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, communication to the device may be in progress. If addressed an ACK pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

| Address                | Name    | Bit 7                | Bit 6                                                    | Bit 5                  | Bit 4    | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOR | Value on all other resets |

|------------------------|---------|----------------------|----------------------------------------------------------|------------------------|----------|-----------|--------|--------|--------|-------------------------|---------------------------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE                                                     | TOIE                   | INTE     | RBIE      | TOIF   | INTF   | RBIF   | 0000 000x               | 0000 000u                 |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                                     | RCIF                   | TXIF     | SSPIF     | CCP1IF | TMR2IF | TMR1IF | 0000 0000               | 0000 0000                 |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                                     | RCIE                   | TXIE     | SSPIE     | CCP1IE | TMR2IE | TMR1IE | 0000 0000               | 0000 0000                 |

| 13h                    | SSPBUF  | Synchrono            | Synchronous Serial Port Receive Buffer/Transmit Register |                        |          |           |        |        |        | xxxx xxxx               | uuuu uuuu                 |

| 93h                    | SSPADD  | Synchrono            | us Serial                                                | Port (I <sup>2</sup> C | mode) Ad | ldress Re | gister |        |        | 0000 0000               | 0000 0000                 |

| 14h                    | SSPCON  | WCOL                 | SSPOV                                                    | SSPEN                  | CKP      | SSPM3     | SSPM2  | SSPM1  | SSPM0  | 0000 0000               | 0000 0000                 |

| 94h                    | SSPSTAT | SMP <sup>(2)</sup>   | CKE <sup>(2)</sup>                                       | D/Ā                    | Р        | S         | R/W    | UA     | BF     | 0000 0000               | 0000 0000                 |

| 87h                    | TRISC   | PORTC Da             | ta Directi                                               | on registe             | er       |           |        |        |        | 1111 1111               | 1111 1111                 |

# TABLE 11-5: REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

$\label{eq:Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in SPI mode.$

Note 1: PSPIF and PSPIE are reserved on the PIC16C73/73A/76, always maintain these bits clear.

2: The SMP and CKE bits are implemented on the PIC16C76/77 only. All other PIC16C7X devices have these two bits unimplemented, read as '0'.

## 12.4 USART Synchronous Slave Mode

# Applicable Devices 72 73 73A 74 74A 76 77

Synchronous slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 12.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the synchronous master and slave modes are identical except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

#### 12.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the synchronous master and slave modes is identical except in the case of the SLEEP mode. Also, bit SREN is a don't care in slave mode.

If receive is enabled, by setting bit CREN, prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Reception:

- 1. Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, then set enable bit RCIE.

- 3. If 9-bit reception is desired, then set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- 6. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

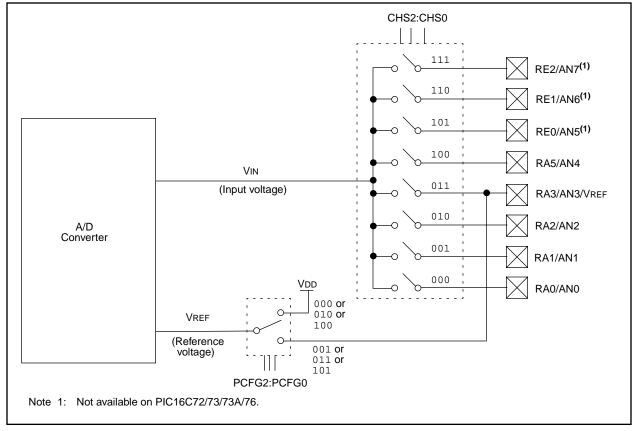

The ADRES register contains the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRES register, the GO/DONE bit (ADCON0<2>) is cleared, and A/D interrupt flag bit ADIF is set. The block diagrams of the A/D module are shown in Figure 13-3.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 13.1. After this acquisition time has elapsed the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins / voltage reference / and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- Clear ADIF bit

- Set ADIE bit

- Set GIE bit

# FIGURE 13-3: A/D BLOCK DIAGRAM

- 3. Wait the required acquisition time.

- 4. Start conversion:Set GO/DONE bit (ADCON0)

- 5. Wait for A/D conversion to complete, by either:

Polling for the GO/DONE bit to be cleared

- OR

- Waiting for the A/D interrupt

- Read A/D Result register (ADRES), clear bit ADIF if required.

- 7. For next conversion, go to step 1 or step 2 as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 2TAD is required before next acquisition starts.

# 14.3 <u>Reset</u> Applicable Devices 72|73|73A|74|74A|76|77

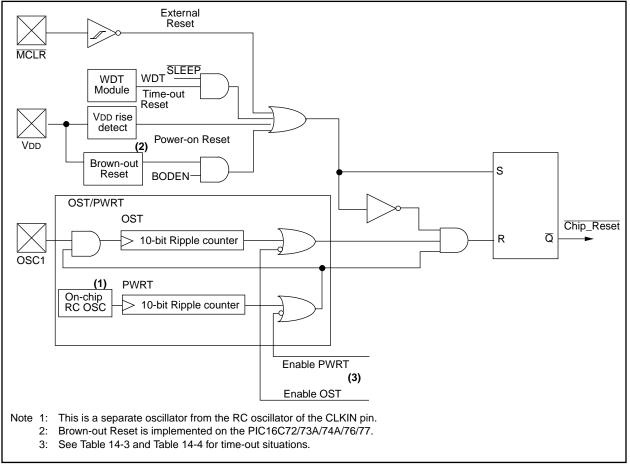

The PIC16CXX differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- MCLR reset during SLEEP

- WDT Reset (normal operation)

- Brown-out Reset (BOR) (PIC16C72/73A/74A/76/ 77)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged in any other reset. Most other registers are reset to a "reset state" on Power-on Reset (POR), on the  $\overline{\text{MCLR}}$  and WDT Reset, on  $\overline{\text{MCLR}}$  reset during SLEEP, and Brownout Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different reset situations as indicated in Table 14-5 and Table 14-6. These bits are used in software to determine the nature of the reset. See Table 14-8 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 14-8.

The PIC16C72/73A/74A/76/77 have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

| NOP               | No Operation |                  |                  |                  |  |  |

|-------------------|--------------|------------------|------------------|------------------|--|--|

| Syntax:           | [ label ]    | NOP              |                  |                  |  |  |

| Operands:         | None         |                  |                  |                  |  |  |

| Operation:        | No operation |                  |                  |                  |  |  |

| Status Affected:  | None         |                  |                  |                  |  |  |

| Encoding:         | 00           | 0000             | 0xx0             | 0000             |  |  |

| Description:      | No operat    | ion.             |                  |                  |  |  |

| Words:            | 1            |                  |                  |                  |  |  |

| Cycles:           | 1            |                  |                  |                  |  |  |

| Q Cycle Activity: | Q1           | Q2               | Q3               | Q4               |  |  |

|                   | Decode       | No-<br>Operation | No-<br>Operation | No-<br>Operation |  |  |

| Example           | NOP          |                  |                  |                  |  |  |

| RETFIE                       | Return from Interrupt                                                 |                                                            |                                                           |                            |  |  |

|------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------|----------------------------|--|--|

| Syntax:                      | [ label ]                                                             | RETFIE                                                     |                                                           |                            |  |  |

| Operands:                    | None                                                                  |                                                            |                                                           |                            |  |  |

| Operation:                   | $TOS \rightarrow PC$ ,<br>1 $\rightarrow GIE$                         |                                                            |                                                           |                            |  |  |

| Status Affected:             | None                                                                  |                                                            |                                                           |                            |  |  |

| Encoding:                    | 00                                                                    | 0000                                                       | 0000                                                      | 1001                       |  |  |

|                              | •                                                                     | ```                                                        | ) is load                                                 |                            |  |  |

|                              | PC. Interru<br>Global Inte                                            | upts are er<br>errupt Ena<br><7>). This i                  | ble bit, GIE                                              | setting                    |  |  |

| Words:                       | PC. Interru<br>Global Inte<br>(INTCON<                                | upts are er<br>errupt Ena<br><7>). This i                  | habled by s<br>ble bit, GIE                               | setting                    |  |  |

| Words:<br>Cycles:            | PC. Interru<br>Global Inte<br>(INTCON-<br>instruction                 | upts are er<br>errupt Ena<br><7>). This i                  | habled by s<br>ble bit, GIE                               | setting                    |  |  |

|                              | PC. Interru<br>Global Inte<br>(INTCON-<br>instruction                 | upts are er<br>errupt Ena<br><7>). This i                  | habled by s<br>ble bit, GIE                               | setting                    |  |  |

| Cycles:                      | PC. Interru<br>Global Inte<br>(INTCON-<br>instruction<br>1<br>2       | upts are er<br>errupt Ena<br><7>). This i                  | nabled by s<br>ble bit, GIE<br>is a two cy                | setting<br>cle<br>Q4       |  |  |

| Cycles:<br>Q Cycle Activity: | PC. Interru<br>Global Inte<br>(INTCON-<br>instruction<br>1<br>2<br>Q1 | upts are er<br>errupt Ena<br><7>). This i<br><br>Q2<br>No- | abled by s<br>ble bit, GIE<br>s a two cy<br>Q3<br>Set the | setting<br><u>=</u><br>cle |  |  |

After Interrupt PC = TOS GIE = 1

| OPTION                 | Load Op                                                                                                                                                                                                                                            | tion Reg | gister |      |  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|------|--|

| Syntax:                | [ label ]                                                                                                                                                                                                                                          | OPTION   | ٧      |      |  |

| Operands:              | None                                                                                                                                                                                                                                               |          |        |      |  |

| Operation:             | $(W) \rightarrow OPTION$                                                                                                                                                                                                                           |          |        |      |  |

| Status Affected:       | None                                                                                                                                                                                                                                               |          |        |      |  |

| Encoding:              | 00                                                                                                                                                                                                                                                 | 0000     | 0110   | 0010 |  |

| Description:<br>Words: | The contents of the W register are<br>loaded in the OPTION register. This<br>instruction is supported for code com-<br>patibility with PIC16C5X products.<br>Since OPTION is a readable/writable<br>register, the user can directly address<br>it. |          |        |      |  |

| Cycles:                | 1                                                                                                                                                                                                                                                  |          |        |      |  |

| Example                | ·                                                                                                                                                                                                                                                  |          |        |      |  |

|                        | To maintain upward compatibility<br>with future PIC16CXX products, do<br>not use this instruction.                                                                                                                                                 |          |        |      |  |

|                        |                                                                                                                                                                                                                                                    |          |        |      |  |

# Applicable Devices 72 73 73A 74 74A 76 77

# 17.5 <u>Timing Diagrams and Specifications</u>

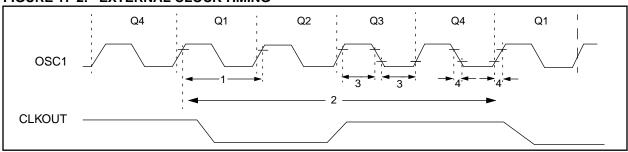

# FIGURE 17-2: EXTERNAL CLOCK TIMING

## TABLE 17-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                   | Min | Тур† | Max    | Units | Conditions         |

|------------------|-------|----------------------------------|-----|------|--------|-------|--------------------|

|                  | Fosc  | External CLKIN Frequency         | DC  | _    | 4      | MHz   | XT and RC osc mode |

|                  |       | (Note 1)                         | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|                  |       |                                  | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|                  |       |                                  | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|                  |       |                                  | DC  | _    | 200    | kHz   | LP osc mode        |

|                  |       | Oscillator Frequency             | DC  | _    | 4      | MHz   | RC osc mode        |

|                  |       | (Note 1)                         | 0.1 | _    | 4      | MHz   | XT osc mode        |

|                  |       |                                  | 4   | _    | 20     | MHz   | HS osc mode        |

|                  |       |                                  | 5   | —    | 200    | kHz   | LP osc mode        |

| 1                | Tosc  | External CLKIN Period            | 250 | —    | —      | ns    | XT and RC osc mode |

|                  |       | (Note 1)                         | 250 | —    | —      | ns    | HS osc mode (-04)  |

|                  |       |                                  | 100 | —    | —      | ns    | HS osc mode (-10)  |

|                  |       |                                  | 50  | —    | —      | ns    | HS osc mode (-20)  |

|                  |       |                                  | 5   | _    | _      | μs    | LP osc mode        |

|                  |       | Oscillator Period                | 250 |      | —      | ns    | RC osc mode        |

|                  |       | (Note 1)                         | 250 | _    | 10,000 | ns    | XT osc mode        |

|                  |       |                                  | 250 | _    | 250    | ns    | HS osc mode (-04)  |

|                  |       |                                  | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|                  |       |                                  | 50  | —    | 250    | ns    | HS osc mode (-20)  |

|                  |       |                                  | 5   | —    | —      | μs    | LP osc mode        |

| 2                | Тсү   | Instruction Cycle Time (Note 1)  | 200 | —    | DC     | ns    | TCY = 4/FOSC       |

| 3                | TosL, | External Clock in (OSC1) High or | 100 | _    | _      | ns    | XT oscillator      |

|                  | TosH  | Low Time                         |     | —    | _      | μs    | LP oscillator      |

|                  |       |                                  | 15  |      |        | ns    | HS oscillator      |

| 4                | TosR, | External Clock in (OSC1) Rise or | —   |      | 25     | ns    | XT oscillator      |

|                  | TosF  | Fall Time                        |     | _    | 50     | ns    | LP oscillator      |

|                  |       |                                  |     | _    | 15     | ns    | HS oscillator      |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

# PIC16C7X

# Applicable Devices 72 73 73A 74 74A 76 77

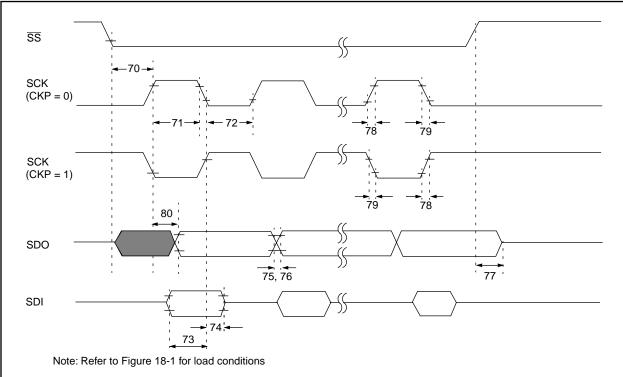

# TABLE 18-8: SPI MODE REQUIREMENTS

| Parameter<br>No. | Sym                   | Characteristic                                                        | Min      | Тур† | Max | Units | Conditions |

|------------------|-----------------------|-----------------------------------------------------------------------|----------|------|-----|-------|------------|

| 70               | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ input | Тсү      | —    | -   | ns    |            |

| 71               | TscH                  | SCK input high time (slave mode)                                      | TCY + 20 | _    | _   | ns    |            |

| 72               | TscL                  | SCK input low time (slave mode)                                       | TCY + 20 | _    | _   | ns    |            |

| 73               | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge                              | 50       | _    | _   | ns    |            |

| 74               | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                               | 50       | _    | -   | ns    |            |

| 75               | TdoR                  | SDO data output rise time                                             | _        | 10   | 25  | ns    |            |

| 76               | TdoF                  | SDO data output fall time                                             | _        | 10   | 25  | ns    |            |

| 77               | TssH2doZ              | SS↑ to SDO output hi-impedance                                        | 10       | _    | 50  | ns    |            |

| 78               | TscR                  | SCK output rise time (master mode)                                    | _        | 10   | 25  | ns    |            |

| 79               | TscF                  | SCK output fall time (master mode)                                    | _        | 10   | 25  | ns    |            |

| 80               | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge                                  | _        | _    | 50  | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# Applicable Devices 72 73 73A 74 74A 76 77

# 19.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2p             | pS                                                | 3. Tcc:st      | (I <sup>2</sup> C specifications only) |  |  |

|-----------------------|---------------------------------------------------|----------------|----------------------------------------|--|--|

| 2. TppS               |                                                   | 4. Ts          | (I <sup>2</sup> C specifications only) |  |  |

| Т                     |                                                   |                |                                        |  |  |

| F                     | Frequency                                         | Т              | Time                                   |  |  |

| Lowerca               | ase letters (pp) and their meanings:              |                |                                        |  |  |

| рр                    |                                                   |                |                                        |  |  |

| сс                    | CCP1                                              | osc            | OSC1                                   |  |  |

| ck                    | CLKOUT                                            | rd             | RD                                     |  |  |

| CS                    | CS                                                | rw             | RD or WR                               |  |  |

| di                    | SDI                                               | sc             | SCK                                    |  |  |

| do                    | SDO                                               | SS             | SS                                     |  |  |

| dt                    | Data in                                           | tO             | ТОСКІ                                  |  |  |

| io                    | I/O port                                          | t1             | T1CKI                                  |  |  |

| mc                    | MCLR                                              | wr             | WR                                     |  |  |

| Upperca               | ase letters and their meanings:                   | ·              |                                        |  |  |

| S                     |                                                   |                |                                        |  |  |

| F                     | Fall                                              | P              | Period                                 |  |  |

| н                     | High                                              | R              | Rise                                   |  |  |

| 1                     | Invalid (Hi-impedance)                            | V              | Valid                                  |  |  |

| L                     | Low                                               | Z              | Hi-impedance                           |  |  |

| I <sup>2</sup> C only |                                                   |                |                                        |  |  |

| AA                    | output access                                     | High           | High                                   |  |  |

| BUF                   | Bus free                                          | Low            | Low                                    |  |  |

| Tcc:st (              | (I <sup>2</sup> C specifications only)            | Į.             |                                        |  |  |

| CC                    | · · · · · · · · · · · · · · · · · · ·             |                |                                        |  |  |

| HD                    | Hold                                              | SU             | Setup                                  |  |  |

| ST                    |                                                   |                |                                        |  |  |

| DAT                   | DATA input hold                                   | STO            | STOP condition                         |  |  |

| STA                   | START condition                                   |                |                                        |  |  |

| L                     | 9-1: LOAD CONDITIONS                              |                |                                        |  |  |

|                       | Load condition 1                                  |                | Load condition 2                       |  |  |

|                       |                                                   |                |                                        |  |  |

| VDD/2<br>RL           |                                                   |                |                                        |  |  |

|                       | ↓                                                 |                |                                        |  |  |

|                       |                                                   |                |                                        |  |  |

|                       | • • • • • • • • • • • • • • • • • • • •           | I              | <sup>…</sup> ↓                         |  |  |

|                       | Vss                                               |                | Vss                                    |  |  |

|                       | $RL = 464\Omega$                                  |                |                                        |  |  |

|                       |                                                   |                |                                        |  |  |

|                       | CL = 50 pF for all pins except OSC2, but in ports |                |                                        |  |  |

|                       | 15 pF for OSC2 output                             |                |                                        |  |  |

|                       | Note: PORTD and PORTE are not implement           | ed on the PIC1 | 6C73A.                                 |  |  |

# PIC16C7X

Applicable Devices

72

73

73A

74

74A

76

77

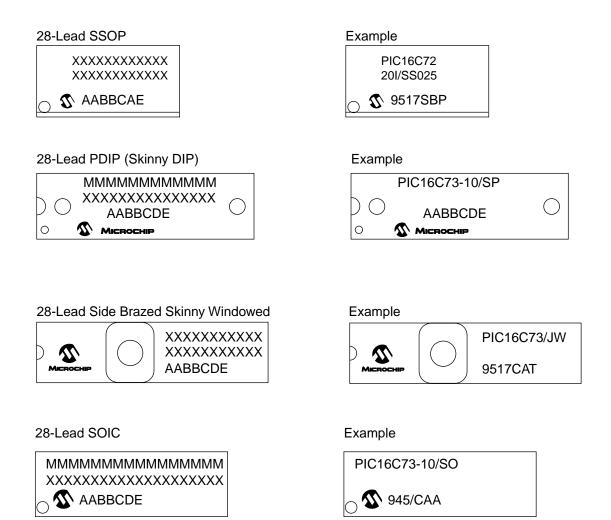

# 22.10 Package Marking Information

| Legend: | MMM                                                                                                                                                                                                          | Microchip part number information                                                                                           |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

|         | XXX                                                                                                                                                                                                          | Customer specific information*                                                                                              |

|         | AA                                                                                                                                                                                                           | Year code (last 2 digits of calender year)                                                                                  |

|         | BB                                                                                                                                                                                                           | Week code (week of January 1 is week '01')                                                                                  |

|         | С                                                                                                                                                                                                            | Facility code of the plant at which wafer is manufactured.<br>C = Chandler, Arizona, U.S.A.<br>S = Tempe, Arizona, U.S.A.   |

|         | D <sub>1</sub><br>E                                                                                                                                                                                          | Mask revision number for microcontroller<br>Assembly code of the plant or country of origin in which<br>part was assembled. |

| Note:   | In the event the full Microchip part number cannot be marked on one<br>line, it will be carried over to the next line thus limiting the number of<br>available characters for customer specific information. |                                                                                                                             |

\* Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask revision number, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

# U

| UA                                  |

|-------------------------------------|

| Asynchronous Mode106                |

| Asynchronous Receiver108            |

| Asynchronous Reception              |

| Asynchronous Transmission 107       |

| Asynchronous Transmitter 106        |

| Baud Rate Generator (BRG) 101       |

| Receive Block Diagram 108           |

| Sampling104                         |

| Synchronous Master Mode 110         |

| Synchronous Master Reception 112    |

| Synchronous Master Transmission 110 |

| Synchronous Slave Mode 114          |

| Synchronous Slave Reception 114     |

| Synchronous Slave Transmit 114      |

| Transmit Block Diagram 106          |

| UV Erasable Devices7                |

# W

| W Register                             |     |  |

|----------------------------------------|-----|--|

| ALU                                    | 9   |  |

| Wake-up from SLEEP                     | 145 |  |

| Watchdog Timer (WDT) 129, 133, 136     |     |  |

| WCOL                                   |     |  |

| WDT                                    |     |  |

| Block Diagram                          | 144 |  |

| Period                                 | 144 |  |

| Programming Considerations             |     |  |

| Timeout                                |     |  |

| Word                                   | 129 |  |

| WR pin                                 |     |  |

| Write Collision Detect bit, WCOL79, 84 |     |  |

# Х

| XMIT_MODE |  |

|-----------|--|

| 7         |  |

| Z bit |     | ) |

|-------|-----|---|

| Zero  | bit | ) |

# LIST OF EXAMPLES

| Evernale 2.1   | Instruction Dinaling Flow             |

|----------------|---------------------------------------|

| Example 3-1:   | Instruction Pipeline Flow17           |

| Example 4-1:   | Call of a Subroutine in Page 1        |

| <b>F</b> 1 4 0 | from Page 041                         |

| Example 4-2:   | Indirect Addressing41                 |

| Example 5-1:   | Initializing PORTA43                  |

| Example 5-2:   | Initializing PORTB45                  |

| Example 5-3:   | Initializing PORTC48                  |

| Example 5-4:   | Read-Modify-Write Instructions        |

|                | on an I/O Port53                      |

| Example 7-1:   | Changing Prescaler (Timer0→WDT)63     |

| Example 7-2:   | Changing Prescaler (WDT→Timer0)63     |

| Example 8-1:   | Reading a 16-bit Free-Running Timer67 |

| Example 10-1:  | Changing Between Capture              |

|                | Prescalers73                          |

| Example 10-2:  | PWM Period and Duty Cycle             |

|                | Calculation                           |

| Example 11-1:  | Loading the SSPBUF (SSPSR)            |

| •              | Register                              |

| Example 11-2:  | Loading the SSPBUF (SSPSR)            |

|                | Register (PIC16C76/77)85              |

| Example 12-1:  | Calculating Baud Rate Error101        |

| Equation 13-1: | A/D Minimum Charging Time120          |

| Example 13-1:  | Calculating the Minimum Required      |

|                | Acquisition Time120                   |

| Example 13-2:  | A/D Conversion122                     |

| Example 13-3:  | 4-bit vs. 8-bit Conversion Times      |

| Example 14-1:  | Saving STATUS, W, and PCLATH          |

|                | Registers in RAM143                   |