Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                 |

| Data Converters            | A/D 8x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LCC (J-Lead)                                                           |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc77-04i-l |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|            |                                                 | PIC16C710                           | PIC16C71            | PIC16C711                           | PIC16C715                           | PIC16C72                   | PIC16CR72 <sup>(1)</sup>   |

|------------|-------------------------------------------------|-------------------------------------|---------------------|-------------------------------------|-------------------------------------|----------------------------|----------------------------|

| Clock      | Maximum Frequency<br>of Operation (MHz)         | 20                                  | 20                  | 20                                  | 20                                  | 20                         | 20                         |

|            | EPROM Program Memory<br>(x14 words)             | 512                                 | 1K                  | 1K                                  | 2К                                  | 2К                         | —                          |

| lemory     | ROM Program Memory<br>(14K words)               | _                                   | _                   | _                                   | _                                   | _                          | 2К                         |

|            | Data Memory (bytes)                             | 36                                  | 36                  | 68                                  | 128                                 | 128                        | 128                        |

|            | Timer Module(s)                                 | TMR0                                | TMR0                | TMR0                                | TMR0                                | TMR0,<br>TMR1,<br>TMR2     | TMR0,<br>TMR1,<br>TMR2     |

| eripherals | Capture/Compare/<br>PWM Module(s)               | —                                   | _                   | —                                   | —                                   | 1                          | 1                          |

|            | Serial Port(s)<br>(SPI/I <sup>2</sup> C, USART) | _                                   | —                   | —                                   | —                                   | SPI/I <sup>2</sup> C       | SPI/I <sup>2</sup> C       |

|            | Parallel Slave Port                             | _                                   | —                   | —                                   | _                                   | _                          | —                          |

|            | A/D Converter (8-bit) Channels                  | 4                                   | 4                   | 4                                   | 4                                   | 5                          | 5                          |

|            | Interrupt Sources                               | 4                                   | 4                   | 4                                   | 4                                   | 8                          | 8                          |

|            | I/O Pins                                        | 13                                  | 13                  | 13                                  | 13                                  | 22                         | 22                         |

|            | Voltage Range (Volts)                           | 3.0-6.0                             | 3.0-6.0             | 3.0-6.0                             | 3.0-5.5                             | 2.5-6.0                    | 3.0-5.5                    |

| atures     | In-Circuit Serial Programming                   | Yes                                 | Yes                 | Yes                                 | Yes                                 | Yes                        | Yes                        |

|            | Brown-out Reset                                 | Yes                                 | —                   | Yes                                 | Yes                                 | Yes                        | Yes                        |

|            | Packages                                        | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 28-pin SDIP,<br>SOIC, SSOP | 28-pin SDIP,<br>SOIC, SSOP |

# TABLE 1-1: PIC16C7XX FAMILY OF DEVCES

|             |                                                   | PIC16C73A                   | PIC16C74A                                 | PIC16C76                    | PIC16C77                                  |

|-------------|---------------------------------------------------|-----------------------------|-------------------------------------------|-----------------------------|-------------------------------------------|

| Clock       | Maximum Frequency of Oper-<br>ation (MHz)         | 20                          | 20                                        | 20                          | 20                                        |

| Memory      | EPROM Program Memory<br>(x14 words)               | 4K                          | 4K                                        | 8K                          | 8K                                        |

|             | Data Memory (bytes)                               | 192                         | 192                                       | 368                         | 368                                       |

|             | Timer Module(s)                                   | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    | TMR0,<br>TMR1,<br>TMR2      | TMR0,<br>TMR1,<br>TMR2                    |

| Peripherals | Capture/Compare/PWM Mod-<br>ule(s)                | 2                           | 2                                         | 2                           | 2                                         |

|             | Serial Port(s) (SPI/I <sup>2</sup> C, US-<br>ART) | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               | SPI/I <sup>2</sup> C, USART | SPI/I <sup>2</sup> C, USART               |

|             | Parallel Slave Port                               | —                           | Yes                                       | —                           | Yes                                       |

|             | A/D Converter (8-bit) Channels                    | 5                           | 8                                         | 5                           | 8                                         |

|             | Interrupt Sources                                 | 11                          | 12                                        | 11                          | 12                                        |

|             | I/O Pins                                          | 22                          | 33                                        | 22                          | 33                                        |

|             | Voltage Range (Volts)                             | 2.5-6.0                     | 2.5-6.0                                   | 2.5-6.0                     | 2.5-6.0                                   |

| eatures     | In-Circuit Serial Programming                     | Yes                         | Yes                                       | Yes                         | Yes                                       |

|             | Brown-out Reset                                   | Yes                         | Yes                                       | Yes                         | Yes                                       |

|             | Packages                                          | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP | 28-pin SDIP,<br>SOIC        | 40-pin DIP;<br>44-pin PLCC,<br>MQFP, TQFP |

All PIC16/17 Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16C7XX Family devices use serial programming with clock pin RB6 and data pin RB7.

Note 1: Please contact your local Microchip sales office for availability of these devices.

# FIGURE 4-4: PIC16C72 REGISTER FILE MAP

| File<br>Address   | 3                     |                     | File<br>Address |

|-------------------|-----------------------|---------------------|-----------------|

| 00h               | INDF <sup>(1)</sup>   | INDF <sup>(1)</sup> | 80h             |

| 01h               | TMR0                  | OPTION              | 81h             |

| 02h               | PCL                   | PCL                 |                 |

| 03h               | STATUS                | STATUS              |                 |

| 04h               | FSR                   | FSR                 |                 |

| 05h               | PORTA                 | TRISA               | 85h             |

| 06h               | PORTB                 | TRISB               | 86h             |

| 07h               | PORTC                 | TRISC               |                 |

| 08h               |                       |                     |                 |

| 09h               |                       |                     | 89h             |

| 0Ah               | PCLATH                | PCLATH              | 8Ah             |

| 0Bh               | INTCON                | INTCON              | 8Bh             |

| 0Ch               | PIR1                  | PIE1                | 8Ch             |

| 0Dh               |                       |                     | 8Dh             |

| 0Eh               | TMR1L                 | PCON                | 8Eh             |

| 0Fh               | TMR1H                 |                     | 8Fh             |

| 10h               | T1CON                 |                     | 90h             |

| 11h               | TMR2                  |                     | 91h             |

| 12h               | T2CON                 | PR2                 | 92h             |

| 13h               | SSPBUF                | SSPADD              | 93h             |

| 14h               | SSPCON                | SSPSTAT             |                 |

| 15h               | CCPR1L                |                     | 95h             |

| 16h               | CCPR1H                |                     | 96h             |

| 17h               | CCP1CON               |                     | 97h             |

| 18h               |                       |                     | 98h             |

| 19h               |                       |                     | 99h             |

| 1Ah               |                       |                     | 9Ah             |

| 1Bh               |                       |                     | 9Bh             |

| 1Ch               |                       |                     | 9Ch             |

| 1Dh               |                       |                     | 9Dh             |

| 1Eh               | ADRES                 |                     | 9Eh             |

| 1Fh               | ADCON0                | ADCON1              | 9Fh             |

| 20h               |                       |                     | A0h             |

|                   | General<br>Purpose    | General<br>Purpose  |                 |

|                   | Register              | Register            |                 |

|                   | U U                   |                     | BFh             |

|                   |                       |                     | C0h             |

|                   |                       |                     |                 |

| 1                 |                       |                     |                 |

|                   |                       |                     |                 |

| 7Fh               |                       |                     | FFh             |

|                   | Bank 0                | Bank 1              |                 |

|                   |                       |                     |                 |

|                   | nimplemented data     | a memory locations  | s, read as      |

| '0'.<br>Note 1: 1 | Not a physical regis  | stor                |                 |

|                   | tot a priysical regit | лот.                |                 |

|                   |                       |                     |                 |

#### FIGURE 4-5: PIC16C73/73A/74/74A REGISTER FILE MAP

|                                                   | REGIST                                                        | ER FILE MA                     | F               |  |  |  |

|---------------------------------------------------|---------------------------------------------------------------|--------------------------------|-----------------|--|--|--|

| File<br>Addres                                    | SS                                                            | _                              | File<br>Address |  |  |  |

| 00h                                               | INDF <sup>(1)</sup>                                           | INDF <sup>(1)</sup>            | 80h             |  |  |  |

| 01h                                               | TMR0                                                          | OPTION                         |                 |  |  |  |

| 02h                                               | PCL                                                           | PCL                            | 82h             |  |  |  |

| 03h                                               | STATUS                                                        | STATUS                         | 83h             |  |  |  |

| 04h                                               | FSR                                                           | FSR                            |                 |  |  |  |

| 05h                                               | PORTA                                                         | TRISA                          | 85h             |  |  |  |

| 06h                                               | PORTB                                                         | TRISB                          | 86h             |  |  |  |

| 07h                                               | PORTC                                                         | TRISC                          |                 |  |  |  |

| 08h                                               | PORTD <sup>(2)</sup>                                          | TRISD <sup>(2)</sup>           |                 |  |  |  |

| 09h                                               | PORTE <sup>(2)</sup>                                          | TRISE <sup>(2)</sup>           | 89h             |  |  |  |

| 0Ah                                               | PCLATH                                                        | PCLATH                         | 8Ah             |  |  |  |

| 0Bh                                               | INTCON                                                        | INTCON                         | 8Bh             |  |  |  |

| 0Ch                                               | PIR1                                                          | PIE1                           | 8Ch             |  |  |  |

| 0Dh                                               | PIR2                                                          | PIE2                           | 8Dh             |  |  |  |

| 0Eh                                               | TMR1L                                                         | PCON                           | 8Eh             |  |  |  |

| 0Fh                                               | TMR1H                                                         |                                | 8Fh             |  |  |  |

| 10h                                               | T1CON                                                         |                                | 90h             |  |  |  |

| 11h                                               | TMR2                                                          |                                | 91h             |  |  |  |

| 12h                                               | T2CON                                                         | PR2                            |                 |  |  |  |

| 13h                                               | SSPBUF                                                        | SSPADD                         | 93h             |  |  |  |

| 14h                                               | SSPCON                                                        | SSPSTAT                        | 94h             |  |  |  |

| 15h                                               | CCPR1L                                                        |                                | 95h             |  |  |  |

| 16h                                               | CCPR1H                                                        |                                | 96h             |  |  |  |

| 17h                                               | CCP1CON                                                       |                                | 97h             |  |  |  |

| 18h                                               | RCSTA                                                         | TXSTA                          |                 |  |  |  |

| 19h                                               | TXREG                                                         | SPBRG                          | 99h             |  |  |  |

| 1Ah                                               | RCREG                                                         |                                | 9Ah             |  |  |  |

| 1Bh                                               | CCPR2L                                                        |                                | 9Bh             |  |  |  |

| 1Ch                                               | CCPR2H                                                        |                                | 9Ch             |  |  |  |

| 1Dh                                               | CCP2CON                                                       |                                | 9Dh             |  |  |  |

| 1Eh                                               | ADRES                                                         |                                | 9Eh             |  |  |  |

| 1Fh                                               | ADCON0                                                        | ADCON1                         | 9Fh             |  |  |  |

| 20h                                               |                                                               |                                | A0h             |  |  |  |

|                                                   | General<br>Purpose<br>Register                                | General<br>Purpose<br>Register |                 |  |  |  |

| 7Fh                                               |                                                               |                                | FFh             |  |  |  |

|                                                   | Bank 0                                                        | Bank 1                         |                 |  |  |  |

| Unimplemented data memory locations, read as '0'. |                                                               |                                |                 |  |  |  |

| Note 1:<br>2:                                     | Not a physical reg<br>These registers ar<br>mented on the PIC | e not physically               |                 |  |  |  |

|                                                   |                                                               |                                |                 |  |  |  |

| Address              | Name    | Bit 7                | Bit 6                                                                                          | Bit 5                     | Bit 4           | Bit 3        | Bit 2           | Bit 1         | Bit 0  | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(2) |

|----------------------|---------|----------------------|------------------------------------------------------------------------------------------------|---------------------------|-----------------|--------------|-----------------|---------------|--------|--------------------------|-------------------------------------|

| Bank 1               |         |                      |                                                                                                |                           |                 |              |                 |               |        |                          |                                     |

| 80h <sup>(4)</sup>   | INDF    | Addressing           | Addressing this location uses contents of FSR to address data memory (not a physical register) |                           |                 |              |                 |               |        |                          | 0000 0000                           |

| 81h                  | OPTION  | RBPU                 | INTEDG                                                                                         | TOCS                      | TOSE            | PSA          | PS2             | PS1           | PS0    | 1111 1111                | 1111 1111                           |

| 82h <sup>(4)</sup>   | PCL     | Program Co           | ounter's (PC)                                                                                  | Least Signif              | ficant Byte     |              |                 |               |        | 0000 0000                | 0000 0000                           |

| 83h <b>(4)</b>       | STATUS  | IRP                  | RP1                                                                                            | RP0                       | TO              | PD           | Z               | DC            | С      | 0001 1xxx                | 000q quuu                           |

| 84h <sup>(4)</sup>   | FSR     | Indirect data        | a memory ac                                                                                    | dress pointe              | er              |              |                 |               |        | xxxx xxxx                | uuuu uuuu                           |

| 85h                  | TRISA   | _                    | _                                                                                              | PORTA Dat                 | ta Direction Re | gister       |                 |               |        | 11 1111                  | 11 1111                             |

| 86h                  | TRISB   | PORTB Dat            | ta Direction F                                                                                 | Register                  |                 |              |                 |               |        | 1111 1111                | 1111 1111                           |

| 87h                  | TRISC   | PORTC Dat            | ta Direction I                                                                                 | Register                  |                 |              |                 |               |        | 1111 1111                | 1111 1111                           |

| 88h <b>(5)</b>       | TRISD   | PORTD Dat            | ta Direction F                                                                                 | Register                  |                 |              |                 |               |        | 1111 1111                | 1111 1111                           |

| 89h <b>(5)</b>       | TRISE   | IBF                  | OBF                                                                                            | IBOV                      | PSPMODE         | _            | PORTE Dat       | a Direction E | Bits   | 0000 -111                | 0000 -111                           |

| 8Ah <sup>(1,4)</sup> | PCLATH  | _                    | —                                                                                              | _                         | Write Buffer fo | or the upper | 5 bits of the l | Program Cou   | Inter  | 0 0000                   | 0 0000                              |

| 8Bh <sup>(4)</sup>   | INTCON  | GIE                  | PEIE                                                                                           | TOIE                      | INTE            | RBIE         | TOIF            | INTF          | RBIF   | 0000 000x                | 0000 000u                           |

| 8Ch                  | PIE1    | PSPIE <sup>(3)</sup> | ADIE                                                                                           | RCIE                      | TXIE            | SSPIE        | CCP1IE          | TMR2IE        | TMR1IE | 0000 0000                | 0000 0000                           |

| 8Dh                  | PIE2    | _                    | _                                                                                              | —                         | _               | _            | —               | —             | CCP2IE | 0                        | 0                                   |

| 8Eh                  | PCON    | _                    | —                                                                                              | _                         | _               | _            | _               | POR           | BOR    | dd                       | uu                                  |

| 8Fh                  | _       | Unimpleme            | nted                                                                                           | •                         |                 | •            |                 | •             | •      | _                        | _                                   |

| 90h                  | _       | Unimpleme            | nted                                                                                           |                           |                 |              |                 |               |        | _                        | _                                   |

| 91h                  | _       | Unimpleme            | nted                                                                                           |                           |                 |              |                 |               |        | -                        | _                                   |

| 92h                  | PR2     | Timer2 Peri          | od Register                                                                                    |                           |                 |              |                 |               |        | 1111 1111                | 1111 1111                           |

| 93h                  | SSPADD  | Synchronou           | us Serial Por                                                                                  | t (I <sup>2</sup> C mode) | Address Regis   | ter          |                 |               |        | 0000 0000                | 0000 0000                           |

| 94h                  | SSPSTAT | SMP                  | CKE                                                                                            | D/Ā                       | Р               | S            | R/W             | UA            | BF     | 0000 0000                | 0000 0000                           |

| 95h                  | _       | Unimpleme            | nted                                                                                           | •                         |                 |              |                 |               | •      | _                        | _                                   |

| 96h                  | _       | Unimpleme            | nted                                                                                           |                           |                 |              |                 |               |        | _                        | _                                   |

| 97h                  | _       | Unimpleme            | nted                                                                                           |                           |                 |              |                 |               |        | _                        | _                                   |

| 98h                  | TXSTA   | CSRC                 | ТХ9                                                                                            | TXEN                      | SYNC            | _            | BRGH            | TRMT          | TX9D   | 0000 -010                | 0000 -010                           |

| 99h                  | SPBRG   | Baud Rate            | Baud Rate Generator Register                                                                   |                           |                 |              |                 |               |        | 0000 0000                | 0000 0000                           |

| 9Ah                  | _       | Unimpleme            | nted                                                                                           |                           |                 |              |                 |               |        | _                        | _                                   |

| 9Bh                  | _       | Unimplemented        |                                                                                                |                           |                 |              |                 |               | _      | _                        |                                     |

| 9Ch                  | _       | Unimpleme            | nted                                                                                           |                           |                 |              |                 |               |        | _                        | _                                   |

| 9Dh                  | -       | Unimpleme            | nted                                                                                           |                           |                 |              |                 |               |        | _                        | —                                   |

| 9Eh                  | -       | Unimpleme            | nted                                                                                           |                           |                 |              |                 |               |        | -                        | —                                   |

| 9Fh                  | ADCON1  | _                    | _                                                                                              | _                         | _               | _            | PCFG2           | PCFG1         | PCFG0  | 000                      | 000                                 |

# TABLE 4-3: PIC16C76/77 SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the PIC16C76, always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD and PORTE are not physically implemented on the PIC16C76, read as '0'.

#### 4.2.2.3 INTCON REGISTER

Applicable Devices

72 73 73A 74 74A 76 77

The INTCON Register is a readable and writable register which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts.

# FIGURE 4-9: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

**Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

| R/W-0   | R/W-0     | R/W-0                                      | R/W-0       | R/W-0        | R/W-0           | R/W-0       | R/W-x        | <b></b>                                                                                                              |

|---------|-----------|--------------------------------------------|-------------|--------------|-----------------|-------------|--------------|----------------------------------------------------------------------------------------------------------------------|

| GIE     | PEIE      | TOIE                                       | INTE        | RBIE         | TOIF            | INTF        | RBIF         | R = Readable bit                                                                                                     |

| bit7    |           |                                            |             |              |                 |             | bit0         | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |

| bit 7:  |           | obal Interi<br>es all un-r<br>les all inte | nasked in   |              |                 |             |              |                                                                                                                      |

| bit 6:  |           | ipheral Int<br>es all un-r<br>les all peri | nasked pe   | ripheral ir  | iterrupts       |             |              |                                                                                                                      |

| bit 5:  |           | R0 Overflo<br>es the TM<br>les the TM      | R0 interru  | pt           | bit             |             |              |                                                                                                                      |

| bit 4:  |           | 0/INT Exte<br>es the RB<br>les the RE      | 0/INT exte  | ernal interr | upt             |             |              |                                                                                                                      |

| bit 3:  | 1 = Enabl | Port Char<br>es the RB<br>les the RE       | port char   | ge interru   | pt              |             |              |                                                                                                                      |

| bit 2:  | 1 = TMR0  | R0 Overflo<br>) register h<br>) register c | has overflo | wed (mus     | t be cleare     | d in softwa | are)         |                                                                                                                      |

| bit 1:  |           |                                            | ternal inte | errupt occu  | urred (must     | be cleare   | d in softwa  | re)                                                                                                                  |

| bit 0:  |           | st one of t                                | he RB7:R    | B4 pins cł   |                 |             | e cleared in | software)                                                                                                            |

| Note 1: | may be u  |                                            | ally re-ena | bled by th   | <b>e</b> RETFIE |             |              | it is being cleared, the GIE bit<br>'s Interrupt Service Routine.                                                    |

| global  |           | GIE (INTCO                                 |             |              |                 |             |              | corresponding enable bit or the rupt flag bits are clear prior to                                                    |

NOTES:

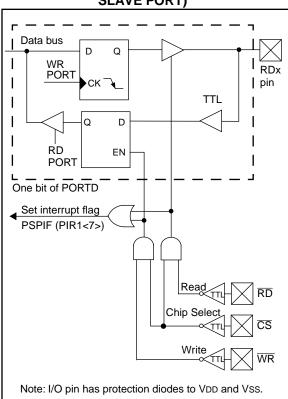

# 5.7 Parallel Slave Port Applicable Devices 72 73 73 74 74 76 77

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port when control bit PSPMODE (TRISE<4>) is set. In slave mode it is asynchronously readable and writable by the external world through  $\overline{RD}$  control input pin RE0/ $\overline{RD}$ /AN5 and  $\overline{WR}$  control input pin RE1/ $\overline{WR}$ /AN6.

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD/AN5 to be the RD input, RE1/ WR/AN6 to be the WR input and RE2/CS/AN7 to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set) and the A/D port configuration bits PCFG2:PCFG0 (ADCON1<2:0>) must be set, which will configure pins RE2:RE0 as digital I/O.

There are actually two 8-bit latches, one for data-out (from the PIC16/17) and one for data input. The user writes 8-bit data to PORTD data latch and reads data from the port pin latch (note that they have the same address). In this mode, the TRISD register is ignored, since the microprocessor is controlling the direction of data flow.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$ lines are first detected low. When either the  $\overline{CS}$  or  $\overline{WR}$ lines become high (level triggered), then the Input Buffer Full status flag bit IBF (TRISE<7>) is set on the Q4 clock cycle, following the next Q2 cycle, to signal the write is complete (Figure 5-12). The interrupt flag bit PSPIF (PIR1<7>) is also set on the same Q4 clock cycle. IBF can only be cleared by reading the PORTD input latch. The input Buffer Overflow status flag bit IBOV (TRISE<5>) is set if a second write to the Parallel Slave Port is attempted when the previous byte has not been read out of the buffer.

A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low. The Output Buffer Full status flag bit OBF (TRISE<6>) is cleared immediately (Figure 5-13) indicating that the PORTD latch is waiting to be read by the external bus. When either the  $\overline{CS}$  or  $\overline{RD}$  pin becomes high (level triggered), the interrupt flag bit PSPIF is set on the Q4 clock cycle, following the next Q2 cycle, indicating that the read is complete. OBF remains low until data is written to PORTD by the user firmware.

When not in Parallel Slave Port mode, the IBF and OBF bits are held clear. However, if flag bit IBOV was previously set, it must be cleared in firmware.

An interrupt is generated and latched into flag bit PSPIF when a read or write operation is completed. PSPIF must be cleared by the user in firmware and the interrupt can be disabled by clearing the interrupt enable bit PSPIE (PIE1<7>).

#### FIGURE 5-11: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

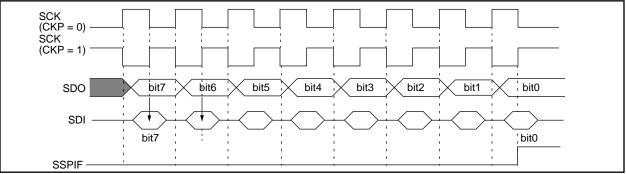

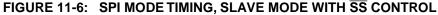

The  $\overline{SS}$  pin allows a synchronous slave mode. The SPI must be in slave mode (SSPCON<3:0> = 04h) and the TRISA<5> bit must be set the for synchronous slave mode to be enabled. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. If the  $\overline{SS}$  pin is taken low without resetting SPI mode, the transmission will continue from the

point at which it was taken high. External pull-up/ pull-down resistors may be desirable, depending on the application.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

|  | <b>TABLE 11-1:</b> | <b>REGISTERS ASSOCIATED WITH SPI OPERATION</b> |

|--|--------------------|------------------------------------------------|

|--|--------------------|------------------------------------------------|

| Address | Name    | Bit 7                  | Bit 6       | Bit 5               | Bit 4                         | Bit 3     | Bit 2    | Bit 1  | Bit 0  | Value<br>POF<br>BOF | ٦,   | all o | e on<br>ther<br>ets |

|---------|---------|------------------------|-------------|---------------------|-------------------------------|-----------|----------|--------|--------|---------------------|------|-------|---------------------|

| 0Bh,8Bh | INTCON  | GIE                    | PEIE        | TOIE                | INTE                          | RBIE      | TOIF     | INTF   | RBIF   | 0000 0              | 200x | 0000  | 000u                |

| 0Ch     | PIR1    | PSPIF <sup>(1,2)</sup> | ADIF        | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup>           | SSPIF     | CCP1IF   | TMR2IF | TMR1IF | 0000 0              | 0000 | 0000  | 0000                |

| 8Ch     | PIE1    | PSPIE <sup>(1,2)</sup> | ADIE        | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup>           | SSPIE     | CCP1IE   | TMR2IE | TMR1IE | 0000 0              | 0000 | 0000  | 0000                |

| 87h     | TRISC   | PORTC Da               | ta Directio | on Registe          | er                            |           |          |        |        | 1111 1              | 1111 | 1111  | 1111                |

| 13h     | SSPBUF  | Synchronou             | us Serial I | Port Rece           | ive Buffer                    | /Transmit | Register |        |        | xxxx x              | xxxx | uuuu  | uuuu                |

| 14h     | SSPCON  | WCOL                   | SSPOV       | SSPEN               | CKP                           | SSPM3     | SSPM2    | SSPM1  | SSPM0  | 0000 0              | 0000 | 0000  | 0000                |

| 85h     | TRISA   | _                      | _           | PORTA I             | PORTA Data Direction Register |           |          |        |        | 11 1                | 1111 | 11    | 1111                |

| 94h     | SSPSTAT | —                      | —           | D/Ā                 | Р                             | S         | R/W      | UA     | BF     | 00 C                | 0000 | 00    | 0000                |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the SSP in SPI mode.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A, always maintain these bits clear.

2: The PIC16C72 does not have a Parallel Slave Port or USART, these bits are unimplemented, read as '0'.

# 11.5 <u>SSP I<sup>2</sup>C Operation</u>

The SSP module in I<sup>2</sup>C mode fully implements all slave functions, except general call support, and provides interrupts on start and stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing. Two pins are used for data transfer. These are the RC3/SCK/SCL pin, which is the clock (SCL), and the RC4/SDI/SDA pin, which is the data (SDA). The user must configure these pins as inputs or outputs through the TRISC<4:3> bits. The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSP-CON<5>).

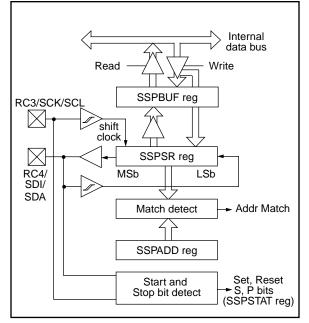

#### FIGURE 11-24: SSP BLOCK DIAGRAM (I<sup>2</sup>C MODE)

The SSP module has five registers for  ${\rm I}^2{\rm C}$  operation. These are the:

- SSP Control Register (SSPCON)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address), with start and stop bit interrupts enabled

- I<sup>2</sup>C Firmware controlled Master Mode, slave is idle

Selection of any I<sup>2</sup>C mode, with the SSPEN bit set, forces the SCL and SDA pins to be open drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits.

The SSPSTAT register gives the status of the data transfer. This information includes detection of a START or STOP bit, specifies if the received byte was data or address if the next byte is the completion of 10-bit address, and if this will be a read or write data transfer. The SSPSTAT register is read only.

The SSPBUF is the register to which transfer data is written to or read from. The SSPSR register shifts the data in or out of the device. In receive operations, the SSPBUF and SSPSR create a doubled buffered receiver. This allows reception of the next byte to begin before reading the last byte of received data. When the complete byte is received, it is transferred to the SSPBUF register and flag bit SSPIF is set. If another complete byte is received before the SSPBUF register is read, a receiver overflow has occurred and bit SSPOV (SSPCON<6>) is set and the byte in the SSPSR is lost.

The SSPADD register holds the slave address. In 10-bit mode, the user first needs to write the high byte of the address (1111 0 A9 A8 0). Following the high byte address match, the low byte of the address needs to be loaded (A7:A0).

#### 11.5.1.3 TRANSMISSION

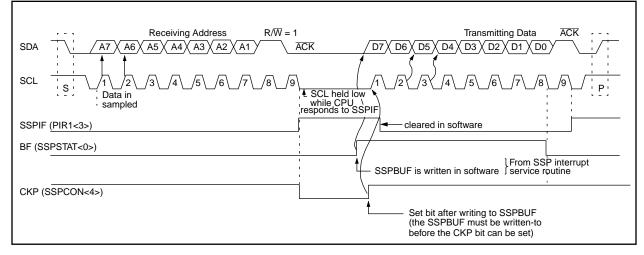

When the  $R\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R\overline{W}$  bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The  $\overline{ACK}$  pulse will be sent on the ninth bit, and pin RC3/SCK/SCL is held low. The transmit data must be loaded into the SSP-BUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP (SSPCON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 11-26). An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF must be cleared in software, and the SSPSTAT register is used to determine the status of the byte. Flag bit SSPIF is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then the data transfer is complete. When the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then pin RC3/SCK/SCL should be enabled by setting bit CKP.

# FIGURE 11-26: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

# 16.0 DEVELOPMENT SUPPORT

# 16.1 <u>Development Tools</u>

The PIC16/17 microcontrollers are supported with a full range of hardware and software development tools:

- PICMASTER/PICMASTER CE Real-Time In-Circuit Emulator

- ICEPIC Low-Cost PIC16C5X and PIC16CXXX In-Circuit Emulator

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- PICDEM-1 Low-Cost Demonstration Board

- PICDEM-2 Low-Cost Demonstration Board

- PICDEM-3 Low-Cost Demonstration Board

- MPASM Assembler

- MPLAB-SIM Software Simulator

- MPLAB-C (C Compiler)

- Fuzzy logic development system (*fuzzy*TECH<sup>®</sup>–MP)

# 16.2 <u>PICMASTER: High Performance</u> <u>Universal In-Circuit Emulator with</u> <u>MPLAB IDE</u>

The PICMASTER Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for all microcontrollers in the PIC12C5XX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX families. PICMASTER is supplied with the MPLAB<sup>TM</sup> Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable target probes allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the PICMASTER allows expansion to support all new Microchip microcontrollers.

The PICMASTER Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC compatible 386 (and higher) machine platform and Microsoft Windows<sup>®</sup> 3.x environment were chosen to best make these features available to you, the end user.

A CE compliant version of PICMASTER is available for European Union (EU) countries.

# 16.3 ICEPIC: Low-cost PIC16CXXX In-Circuit Emulator

ICEPIC is a low-cost in-circuit emulator solution for the Microchip PIC16C5X and PIC16CXXX families of 8-bit OTP microcontrollers.

ICEPIC is designed to operate on PC-compatible machines ranging from 286-AT<sup>®</sup> through Pentium<sup>™</sup> based machines under Windows 3.x environment. ICEPIC features real time, non-intrusive emulation.

# 16.4 PRO MATE II: Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for displaying error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In standalone mode the PRO MATE II can read, verify or program PIC16C5X, PIC16CXXX, PIC17CXX and PIC14000 devices. It can also set configuration and code-protect bits in this mode.

# 16.5 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. PICSTART Plus is not recommended for production programming.

PICSTART Plus supports all PIC12C5XX, PIC14000, PIC16C5X, PIC16CXXX and PIC17CXX devices with up to 40 pins. Larger pin count devices such as the PIC16C923 and PIC16C924 may be supported with an adapter socket.

#### 16.6 <u>PICDEM-1 Low-Cost PIC16/17</u> <u>Demonstration Board</u>

The PICDEM-1 is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The users can program the sample microcontrollers provided with the PICDEM-1 board, on a PRO MATE II or PICSTART-16B programmer, and easily test firmware. The user can also connect the PICDEM-1 board to the PICMASTER emulator and download the firmware to the emulator for testing. Additional prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push-button switches and eight LEDs connected to PORTB.

#### 16.7 <u>PICDEM-2 Low-Cost PIC16CXX</u> Demonstration Board

The PICDEM-2 is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-2 board, on a PRO MATE II programmer or PICSTART-16C, and easily test firmware. The PICMASTER emulator may also be used with the PICDEM-2 board to test firmware. Additional prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push-button switches, a potentiometer for simulated analog input, a Serial EEPROM to demonstrate usage of the I<sup>2</sup>C bus and separate headers for connection to an LCD module and a keypad.

# 16.8 <u>PICDEM-3 Low-Cost PIC16CXXX</u> Demonstration Board

The PICDEM-3 is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with a LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-3 board, on a PRO MATE II programmer or PICSTART Plus with an adapter socket, and easily test firmware. The PICMASTER emulator may also be used with the PICDEM-3 board to test firmware. Additional prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include an RS-232 interface, push-button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM-3 board is an LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM-3 provides an additional RS-232 interface and Windows 3.1 software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

# 16.9 <u>MPLAB Integrated Development</u> <u>Environment Software</u>

The MPLAB IDE Software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a windows based application which contains:

- A full featured editor

- Three operating modes

- editor

- emulator

- simulator

- A project manager

- Customizable tool bar and key mapping

- A status bar with project information

Extensive on-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC16/17 tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- Transfer data dynamically via DDE (soon to be replaced by OLE)

- Run up to four emulators on the same PC

The ability to use MPLAB with Microchip's simulator allows a consistent platform and the ability to easily switch from the low cost simulator to the full featured emulator with minimal retraining due to development tools.

#### 16.10 Assembler (MPASM)

The MPASM Universal Macro Assembler is a PChosted symbolic assembler. It supports all microcontroller series including the PIC12C5XX, PIC14000, PIC16C5X, PIC16CXXX, and PIC17CXX families.

MPASM offers full featured Macro capabilities, conditional assembly, and several source and listing formats. It generates various object code formats to support Microchip's development tools as well as third party programmers.

MPASM allows full symbolic debugging from PICMASTER, Microchip's Universal Emulator System.

# Applicable Devices 72 73 73A 74 74A 76 77

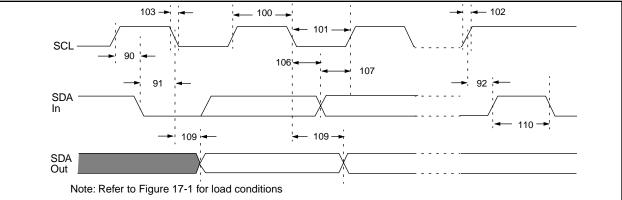

# FIGURE 17-10: I<sup>2</sup>C BUS DATA TIMING

# TABLE 17-9: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Parameter<br>No. | Sym     | Characteristic         |              | Min        | Max  | Units | Conditions                                       |

|------------------|---------|------------------------|--------------|------------|------|-------|--------------------------------------------------|

| 100              | Тнідн   | Clock high time        | 100 kHz mode | 4.0        | _    | μs    | Device must operate at a mini-<br>mum of 1.5 MHz |

|                  |         |                        | 400 kHz mode | 0.6        | _    | μs    | Device must operate at a mini-<br>mum of 10 MHz  |

|                  |         |                        | SSP Module   | 1.5TCY     | —    |       |                                                  |

| 101              | TLOW    | Clock low time         | 100 kHz mode | 4.7        | _    | μs    | Device must operate at a mini-<br>mum of 1.5 MHz |

|                  |         |                        | 400 kHz mode | 1.3        | _    | μs    | Device must operate at a mini-<br>mum of 10 MHz  |

|                  |         |                        | SSP Module   | 1.5Tcy     | _    |       |                                                  |

| 102              | Tr      | SDA and SCL rise       | 100 kHz mode | —          | 1000 | ns    |                                                  |

|                  |         | time                   | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from<br>10 to 400 pF       |

| 103              | Tf      | SDA and SCL fall time  | 100 kHz mode | _          | 300  | ns    |                                                  |

|                  |         |                        | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from<br>10 to 400 pF       |

| 90               | TSU:STA | START condition        | 100 kHz mode | 4.7        | —    | μs    | Only relevant for repeated                       |

|                  |         | setup time             | 400 kHz mode | 0.6        | —    | μs    | START condition                                  |

| 91               | THD:STA | START condition hold   | 100 kHz mode | 4.0        | —    | μs    | After this period the first clock                |

|                  |         | time                   | 400 kHz mode | 0.6        | —    | μs    | pulse is generated                               |

| 106              | THD:DAT | Data input hold time   | 100 kHz mode | 0          | —    | ns    |                                                  |

|                  |         |                        | 400 kHz mode | 0          | 0.9  | μs    |                                                  |

| 107              | TSU:DAT | Data input setup time  | 100 kHz mode | 250        | —    | ns    | Note 2                                           |

|                  |         |                        | 400 kHz mode | 100        | —    | ns    |                                                  |

| 92               | TSU:STO | STOP condition setup   | 100 kHz mode | 4.7        | —    | μs    |                                                  |

|                  |         | time                   | 400 kHz mode | 0.6        | —    | μs    |                                                  |

| 109              | ΤΑΑ     | Output valid from      | 100 kHz mode | —          | 3500 | ns    | Note 1                                           |

|                  |         | clock                  | 400 kHz mode |            | —    | ns    |                                                  |

| 110              | TBUF    | Bus free time          | 100 kHz mode | 4.7        | —    | μs    | Time the bus must be free                        |

|                  |         |                        | 400 kHz mode | 1.3        |      | μs    | before a new transmission can start              |

|                  | Cb      | Bus capacitive loading |              | _          | 400  | pF    |                                                  |

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

2: A fast-mode (400 kHz) I<sup>2</sup>C-bus device can be used in a standard-mode (100 kHz)S I<sup>2</sup>C-bus system, but the requirement tsu;DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+tsu;DAT = 1000 + 250 = 1250 ns (according to the standard-mode I<sup>2</sup>C bus specification) before the SCL line is released.

# Applicable Devices 72 73 73A 74 74A 76 77

# TABLE 17-10:A/D CONVERTER CHARACTERISTICS:<br/>PIC16C72-04 (Commercial, Industrial, Extended)<br/>PIC16C72-10 (Commercial, Industrial, Extended)<br/>PIC16C72-20 (Commercial, Industrial, Extended)<br/>PIC16LC72-04 (Commercial, Industrial)

| Param<br>No. | Sym  | Characteristic                                 |                    | Min       | Тур†       | Max        | Units                                                                                        | Conditions                                                                                                  |

|--------------|------|------------------------------------------------|--------------------|-----------|------------|------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| A01          | Nr   | Resolution                                     |                    |           | —          | 8-bits     | bit                                                                                          | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A02          | Eabs | Total Absolute error                           |                    | —         | —          | <±1        | LSb                                                                                          | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A03          | EIL  | Integral linearity error                       |                    | _         | —          | <±1        | LSb                                                                                          | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A04          | EDL  | Differential linearity error                   |                    | _         | —          | <±1        | LSb                                                                                          | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A05          | EFS  | Full scale error                               | —                  | —         | <±1        | LSb        | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$ |                                                                                                             |

| A06          | EOFF | Offset error                                   |                    | _         | —          | <±1        | LSb                                                                                          | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                |

| A10          | —    | Monotonicity                                   |                    | —         | guaranteed | _          | _                                                                                            | $VSS \leq VAIN \leq VREF$                                                                                   |

| A20          | Vref | Reference voltage                              |                    | 3.0V      | —          | VDD + 0.3  | V                                                                                            |                                                                                                             |

| A25          | VAIN | Analog input voltage                           |                    | Vss - 0.3 | —          | Vref + 0.3 | V                                                                                            |                                                                                                             |

| A30          | Zain | Recommended impedance of analog voltage source |                    |           | _          | 10.0       | kΩ                                                                                           |                                                                                                             |

| A40          | IAD  | A/D conversion current (VDD)                   | PIC16 <b>C</b> 72  | —         | 180        | _          | μΑ                                                                                           | Average current consump-                                                                                    |

|              |      |                                                | PIC16 <b>LC</b> 72 | —         | 90         | —          | μA                                                                                           | tion when A/D is on.<br>(Note 1)                                                                            |

| A50          | IREF | VREF input current (Note 2)                    |                    | 10        | _          | 1000       | μA                                                                                           | During VAIN acquisition.<br>Based on differential of<br>VHOLD to VAIN to charge<br>CHOLD, see Section 13.1. |

|              |      |                                                |                    | —         | —          | 10         | μA                                                                                           | During A/D Conversion cycle                                                                                 |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

Applicable Devices 72 73 73A 74 74A 76 77

# 18.0 ELECTRICAL CHARACTERISTICS FOR PIC16C73/74

#### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                                    | 55 to +125°C                       |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage temperature                                                                                                               | 65°C to +150°C                     |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                                                | 0.3V to (VDD + 0.3V)               |

| Voltage on VDD with respect to Vss                                                                                                | 0.3 to +7.5V                       |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                      | 0 to +14V                          |

| Voltage on RA4 with respect to Vss                                                                                                | 0 to +14V                          |

| Total power dissipation (Note 1)                                                                                                  | 1.0W                               |

| Maximum current out of Vss pin                                                                                                    | 300 mA                             |

| Maximum current into VDD pin                                                                                                      | 250 mA                             |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                                      |                                    |

| Output clamp current, loк (Vo < 0 or Vo > VDD)                                                                                    | ±20 mA                             |

| Maximum output current sunk by any I/O pin                                                                                        | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                                                     | 25 mA                              |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                                               | 200 mA                             |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                                            | 200 mA                             |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                                                       | 200 mA                             |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                                                    | 200 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\Sigma$ IOH} + $\Sigma$ {(VDD -                   | Voh) x Ioh} + $\Sigma$ (Vol x Iol) |

| Note $0$ , $\lambda$ (alternative balance) (as a table $\overline{\mathbf{MOLD}}$ are inducting summation matching the $0$ or $0$ |                                    |

- **Note 2:** Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

- Note 3: PORTD and PORTE are not implemented on the PIC16C73.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# TABLE 18-1: CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C73-04<br>PIC16C74-04                                                                                                                          | PIC16C73-10<br>PIC16C74-10                                                                                                                         | PIC16C73-20<br>PIC16C74-20                                                                                                                         | PIC16LC73-04<br>PIC16LC74-04                                                                               | JW Devices                                                                                                                                         |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                            | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 3.0V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 13.5 μA max. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                           |

| хт  | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                            | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freq: 4 MHz max.                                                        | VDD: 3.0V to 6.0V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 13.5 μA max. at 3V<br>Freq: 4 MHz max.               | VDD: 4.0V to 6.0V<br>IDD: 5 mA max. at 5.5V<br>IPD: 21 μA max. at 4V<br>Freq: 4 MHz max.                                                           |