Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                 |

| Data Converters            | A/D 8x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc77-04i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**NOTES:**

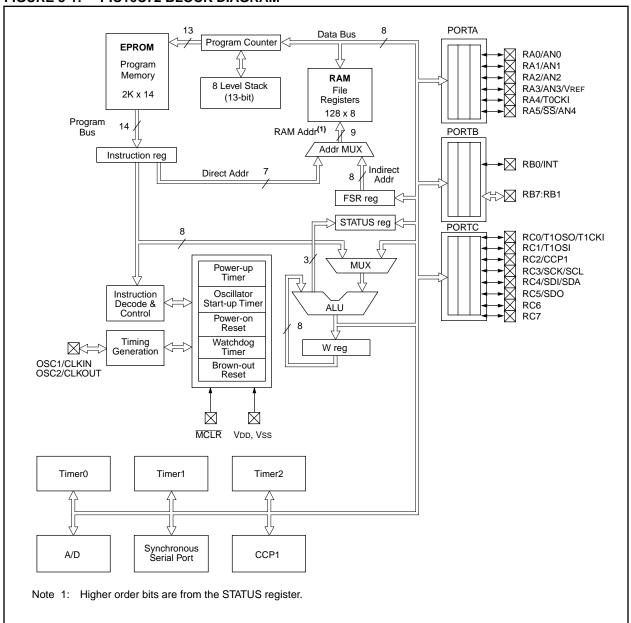

FIGURE 3-1: PIC16C72 BLOCK DIAGRAM

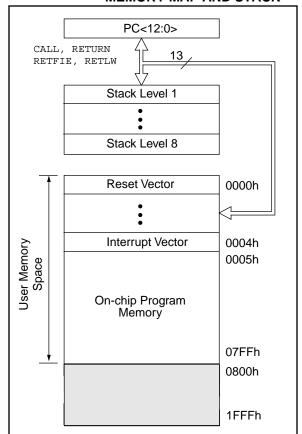

### 4.0 MEMORY ORGANIZATION

Applicable Devices 72 73 73 A 74 74 A 76 77

### 4.1 **Program Memory Organization**

The PIC16C7X family has a 13-bit program counter capable of addressing an 8K x 14 program memory space. The amount of program memory available to each device is listed below:

| Device    | Program<br>Memory | Address Range |

|-----------|-------------------|---------------|

| PIC16C72  | 2K x 14           | 0000h-07FFh   |

| PIC16C73  | 4K x 14           | 0000h-0FFFh   |

| PIC16C73A | 4K x 14           | 0000h-0FFFh   |

| PIC16C74  | 4K x 14           | 0000h-0FFFh   |

| PIC16C74A | 4K x 14           | 0000h-0FFFh   |

| PIC16C76  | 8K x 14           | 0000h-1FFFh   |

| PIC16C77  | 8K x 14           | 0000h-1FFFh   |

For those devices with less than 8K program memory, accessing a location above the physically implemented address will cause a wraparound.

The reset vector is at 0000h and the interrupt vector is at 0004h.

FIGURE 4-1: PIC16C72 PROGRAM MEMORY MAP AND STACK

FIGURE 4-2: PIC16C73/73A/74/74A

PROGRAM MEMORY MAP

AND STACK

#### **5.0 I/O PORTS**

Applicable Devices 72 73 73 A 74 74 A 76 77

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

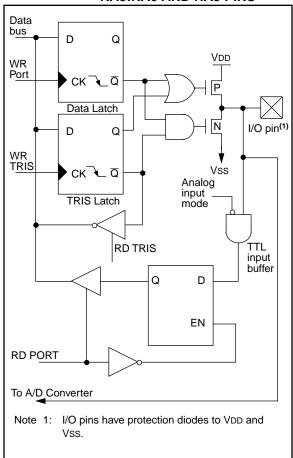

#### 5.1 PORTA and TRISA Registers

**Applicable Devices** 72 73 73A 74 74A 76 77

PORTA is a 6-bit latch.

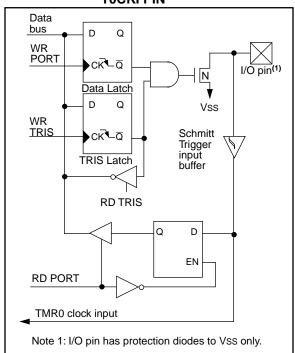

The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as output or input.

Setting a TRISA register bit puts the corresponding output driver in a hi-impedance mode. Clearing a bit in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin.

Other PORTA pins are multiplexed with analog inputs and analog VREF input. The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

**Note:** On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### **EXAMPLE 5-1: INITIALIZING PORTA**

```

BCF

STATUS, RPO

BCF

STATUS, RP1

; PIC16C76/77 only

CLRF

PORTA

; Initialize PORTA by

; clearing output

; data latches

BSF

STATUS, RPO

; Select Bank 1

; Value used to

MOVLW

; initialize data

; direction

MOVWE TRISA

; Set RA<3:0> as inputs

; RA<5:4> as outputs

; TRISA<7:6> are always

; read as '0'.

```

# FIGURE 5-1: BLOCK DIAGRAM OF RA3:RA0 AND RA5 PINS

FIGURE 5-2: BLOCK DIAGRAM OF RA4/ TOCKI PIN

# 6.0 OVERVIEW OF TIMER MODULES

**Applicable Devices** 72 | 73 | 73 A | 74 | 74 A | 76 | 77

The PIC16C72, PIC16C73/73A, PIC16C74/74A, PIC16C76/77 each have three timer modules.

Each module can generate an interrupt to indicate that an event has occurred (i.e. timer overflow). Each of these modules is explained in full detail in the following sections. The timer modules are:

- Timer0 Module (Section 7.0)

- Timer1 Module (Section 8.0)

- Timer2 Module (Section 9.0)

#### 6.1 Timer0 Overview

**Applicable Devices** 72 73 73A 74 74A 76 77

The Timer0 module is a simple 8-bit overflow counter. The clock source can be either the internal system clock (Fosc/4) or an external clock. When the clock source is an external clock, the Timer0 module can be selected to increment on either the rising or falling edge.

The Timer0 module also has a programmable prescaler option. This prescaler can be assigned to either the Timer0 module or the Watchdog Timer. Bit PSA (OPTION<3>) assigns the prescaler, and bits PS2:PS0 (OPTION<2:0>) determine the prescaler value. Timer0 can increment at the following rates: 1:1 (when prescaler assigned to Watchdog timer), 1:2, 1:4, 1:8, 1:16, 1:32, 1:64, 1:128, and 1:256 (Timer0 only).

Synchronization of the external clock occurs after the prescaler. When the prescaler is used, the external clock frequency may be higher then the device's frequency. The maximum frequency is 50 MHz, given the high and low time requirements of the clock.

#### 6.2 <u>Timer1 Overview</u>

Applicable Devices 72 73 73 A 74 74 A 76 77

Timer1 is a 16-bit timer/counter. The clock source can be either the internal system clock (Fosc/4), an external clock, or an external crystal. Timer1 can operate as either a timer or a counter. When operating as a counter (external clock source), the counter can either operate synchronized to the device or asynchronously to the device. Asynchronous operation allows Timer1 to operate during sleep, which is useful for applications that require a real-time clock as well as the power savings of SLEEP mode.

Timer1 also has a prescaler option which allows Timer1 to increment at the following rates: 1:1, 1:2, 1:4, and 1:8. Timer1 can be used in conjunction with the Capture/Compare/PWM module. When used with a

CCP module, Timer1 is the time-base for 16-bit Capture or the 16-bit Compare and must be synchronized to the device.

#### 6.3 Timer2 Overview

Applicable Devices 72 73 73 A 74 74 A 76 77

Timer2 is an 8-bit timer with a programmable prescaler and postscaler, as well as an 8-bit period register (PR2). Timer2 can be used with the CCP1 module (in PWM mode) as well as the Baud Rate Generator for the Synchronous Serial Port (SSP). The prescaler option allows Timer2 to increment at the following rates: 1:1, 1:4, 1:16.

The postscaler allows the TMR2 register to match the period register (PR2) a programmable number of times before generating an interrupt. The postscaler can be programmed from 1:1 to 1:16 (inclusive).

#### 6.4 CCP Overview

**Applicable Devices** 72 73 73 A 74 74 A 76 77

The CCP module(s) can operate in one of these three modes: 16-bit capture, 16-bit compare, or up to 10-bit Pulse Width Modulation (PWM).

Capture mode captures the 16-bit value of TMR1 into the CCPRxH:CCPRxL register pair. The capture event can be programmed for either the falling edge, rising edge, fourth rising edge, or the sixteenth rising edge of the CCPx pin.

Compare mode compares the TMR1H:TMR1L register pair to the CCPRxH:CCPRxL register pair. When a match occurs an interrupt can be generated, and the output pin CCPx can be forced to given state (High or Low), TMR1 can be reset (CCP1), or TMR1 reset and start A/D conversion (CCP2). This depends on the control bits CCPxM3:CCPxM0.

PWM mode compares the TMR2 register to a 10-bit duty cycle register (CCPRxH:CCPRxL<5:4>) as well as to an 8-bit period register (PR2). When the TMR2 register = Duty Cycle register, the CCPx pin will be forced low. When TMR2 = PR2, TMR2 is cleared to 00h, an interrupt can be generated, and the CCPx pin (if an output) will be forced high.

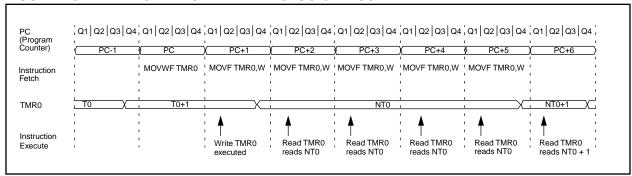

#### FIGURE 7-3: TIMERO TIMING: INTERNAL CLOCK/PRESCALE 1:2

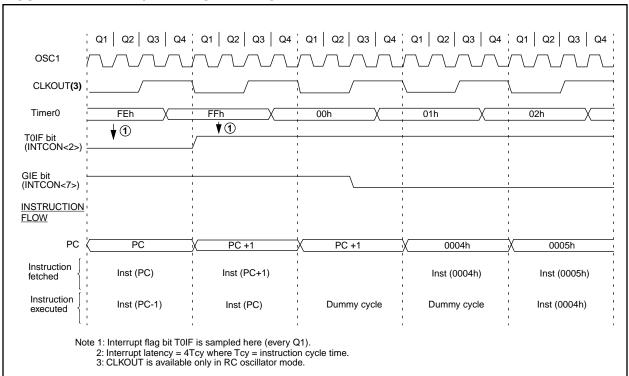

### FIGURE 7-4: TIMERO INTERRUPT TIMING

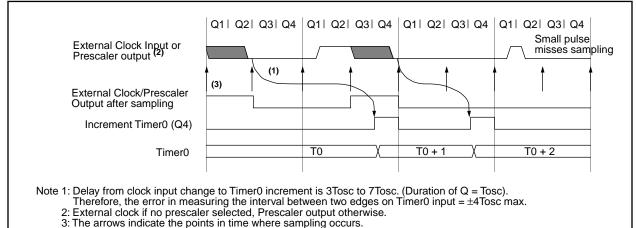

### 7.2 <u>Using Timer0 with an External Clock</u>

**Applicable Devices** 72 | 73 | 73 | 74 | 74 | 76 | 77

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 7.2.2 TMR0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

### FIGURE 11-8: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)(PIC16C76/77)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 WCOL **SSPOV SSPEN CKP** SSPM3 SSPM2 SSPM1 SSPM0 R = Readable bit W = Writable bit bit7 bit0 U = Unimplemented bit, read as '0' - n =Value at POR reset

bit 7: WCOL: Write Collision Detect bit

1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)

0 = No collision

bit 6: SSPOV: Receive Overflow Indicator bit

#### In SPI mode

1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is lost. Overflow can only occur in slave mode. The user must read the SSPBUF, even if only transmitting data, to avoid setting overflow. In master mode the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPBUF register.

0 = No overflow

#### In I<sup>2</sup>C mode

1 = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in transmit mode. SSPOV must be cleared in software in either mode.

0 = No overflow

bit 5: SSPEN: Synchronous Serial Port Enable bit

#### In SPI mode

- 1 = Enables serial port and configures SCK, SDO, and SDI as serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

#### In I<sup>2</sup>C mode

- 1 = Enables the serial port and configures the SDA and SCL pins as serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

In both modes, when enabled, these pins must be properly configured as input or output.

bit 4: CKP: Clock Polarity Select bit

#### In SPI mode

- 1 = Idle state for clock is a high level

- 0 = Idle state for clock is a low level

#### In I<sup>2</sup>C mode

#### SCK release control

- 1 = Enable clock

- 0 = Holds clock low (clock stretch) (Used to ensure data setup time)

#### bit 3-0: SSPM3:SSPM0: Synchronous Serial Port Mode Select bits

- 0000 = SPI master mode, clock = Fosc/4

- 0001 = SPI master mode, clock = Fosc/16

- 0010 = SPI master mode, clock = Fosc/64

- 0011 = SPI master mode, clock = TMR2 output/2

- 0100 = SPI slave mode, clock = SCK pin.  $\overline{SS}$  pin control enabled.

- 0101 = SPI slave mode, clock = SCK pin. SS pin control disabled. SS can be used as I/O pin

- $0110 = I^2C$  slave mode, 7-bit address

- $0111 = I^2C$  slave mode, 10-bit address

- $1011 = I^2C$  firmware controlled master mode (slave idle)

- $1110 = I^2C$  slave mode, 7-bit address with start and stop bit interrupts enabled

- $1111 = I^2C$  slave mode, 10-bit address with start and stop bit interrupts enabled

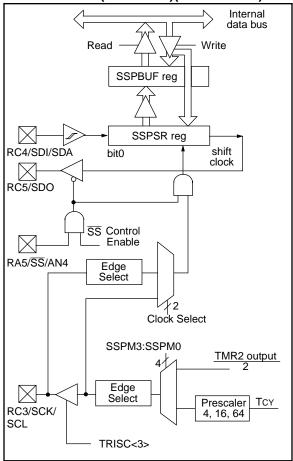

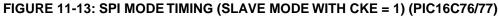

#### 11.3.1 SPI MODE FOR PIC16C76/77

The SPI mode allows 8-bits of data to be synchronously transmitted and received simultaneously. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO) RC5/SDO

- · Serial Data In (SDI) RC4/SDI/SDA

- Serial Clock (SCK) RC3/SCK/SCL

Additionally a fourth pin may be used when in a slave mode of operation:

Slave Select (SS) RA5/SS/AN4

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits in the SSPCON register (SSPCON<5:0>) and SSPSTAT<7:6>. These control bits allow the following to be specified:

- Master Mode (SCK is the clock output)

- Slave Mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Clock edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- Slave Select Mode (Slave mode only)

The SSP consists of a transmit/receive Shift Register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready. Once the 8-bits of data have been received, that byte is moved to the SSPBUF register. Then the buffer full detect bit BF (SSPSTAT<0>) and interrupt flag bit SSPIF (PIR1<3>) are set. This double buffering of the received data (SSPBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPBUF register during transmission/reception of data will be ignored, and the write collision detect bit WCOL (SSPCON<7>) will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully. When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data to transfer is written to the SSPBUF. Buffer full bit BF (SSPSTAT<0>) indicates when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, bit BF is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally the SSP Interrupt is used to determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 11-2 shows the loading of the SSPBUF (SSPSR) for data transmission. The shaded instruction is only required if the received data is meaningful.

# EXAMPLE 11-2: LOADING THE SSPBUF (SSPSR) REGISTER (PIC16C76/77)

```

BCF

STATUS, RP1

;Specify Bank 1

BSF

STATUS, RP0

LOOP BTFSS SSPSTAT, BF

:Has data been

;received

;(transmit

;complete)?

GOTO LOOP

; No

BCF

STATUS. RPO

;Specify Bank 0

MOVF

SSPBUF, W

;W reg = contents

; of SSPBUF

MOVWF RXDATA

;Save in user RAM

MOVF

TXDATA, W

;W reg = contents

; of TXDATA

MOVWF SSPBUF

; New data to xmit

```

The block diagram of the SSP module, when in SPI mode (Figure 11-9), shows that the SSPSR is not directly readable or writable, and can only be accessed from addressing the SSPBUF register. Additionally, the SSP status register (SSPSTAT) indicates the various status conditions.

# FIGURE 11-9: SSP BLOCK DIAGRAM (SPI MODE)(PIC16C76/77)

### TABLE 11-2: REGISTERS ASSOCIATED WITH SPI OPERATION (PIC16C76/77)

| Address               | Name    | Bit 7                | Bit 6       | Bit 5                         | Bit 4   | Bit 3     | Bit 2       | Bit 1  | Bit 0  |      | e on:<br>OR,<br>OR | all o | e on<br>ther<br>ets |

|-----------------------|---------|----------------------|-------------|-------------------------------|---------|-----------|-------------|--------|--------|------|--------------------|-------|---------------------|

| 0Bh,8Bh.<br>10Bh,18Bh | INTCON  | GIE                  | PEIE        | TOIE                          | INTE    | RBIE      | TOIF        | INTF   | RBIF   | 0000 | 000x               | 0000  | 000u                |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup> | ADIF        | RCIF                          | TXIF    | SSPIF     | CCP1IF      | TMR2IF | TMR1IF | 0000 | 0000               | 0000  | 0000                |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup> | ADIE        | RCIE                          | TXIE    | SSPIE     | CCP1IE      | TMR2IE | TMR1IE | 0000 | 0000               | 0000  | 0000                |

| 87h                   | TRISC   | PORTC Da             | ta Directio | n Registe                     | er      |           |             |        |        | 1111 | 1111               | 1111  | 1111                |

| 13h                   | SSPBUF  | Synchronou           | ıs Serial F | Port Recei                    | ve Buff | er/Transm | it Register | •      |        | xxxx | xxxx               | uuuu  | uuuu                |

| 14h                   | SSPCON  | WCOL                 | SSPOV       | SSPEN                         | CKP     | SSPM3     | SSPM2       | SSPM1  | SSPM0  | 0000 | 0000               | 0000  | 0000                |

| 85h                   | TRISA   | _                    | _           | PORTA Data Direction Register |         |           |             | 11     | 1111   | 11   | 1111               |       |                     |

| 94h                   | SSPSTAT | SMP                  | CKE         | D/Ā                           | Р       | S         | R/W         | UA     | BF     | 0000 | 0000               | 0000  | 0000                |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the SSP in SPI mode.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C76, always maintain these bits clear.

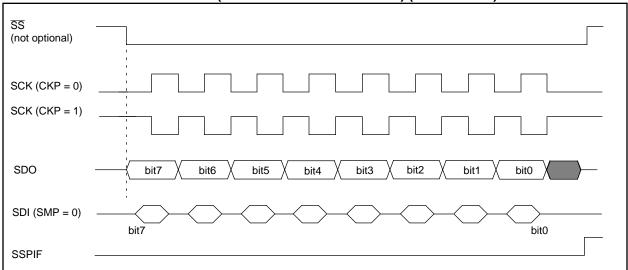

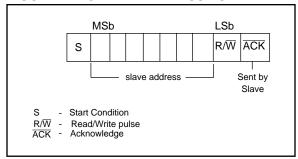

#### 11.4.2 ADDRESSING I<sup>2</sup>C DEVICES

There are two address formats. The simplest is the 7-bit address format with a  $R\overline{W}$  bit (Figure 11-15). The more complex is the 10-bit address with a  $R\overline{W}$  bit (Figure 11-16). For 10-bit address format, two bytes must be transmitted with the first five bits specifying this to be a 10-bit address.

#### FIGURE 11-15: 7-BIT ADDRESS FORMAT

### FIGURE 11-16: I<sup>2</sup>C 10-BIT ADDRESS FORMAT

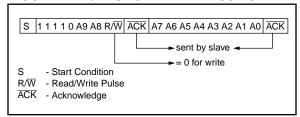

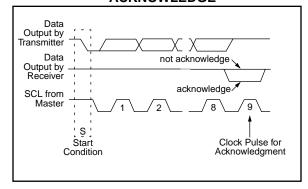

#### 11.4.3 TRANSFER ACKNOWLEDGE

All data must be transmitted per byte, with no limit to the number of bytes transmitted per data transfer. After each byte, the slave-receiver generates an acknowledge bit (ACK) (Figure 11-17). When a slave-receiver doesn't acknowledge the slave address or received data, the master must abort the transfer. The slave must leave SDA high so that the master can generate the STOP condition (Figure 11-14).

# FIGURE 11-17: SLAVE-RECEIVER ACKNOWLEDGE

If the master is receiving the data (master-receiver), it generates an acknowledge signal for each received byte of data, except for the last byte. To signal the end of data to the slave-transmitter, the master does not generate an acknowledge (not acknowledge). The slave then releases the SDA line so the master can generate the STOP condition. The master can also generate the STOP condition during the acknowledge pulse for valid termination of data transfer.

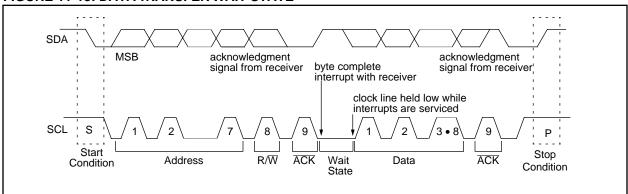

If the slave needs to delay the transmission of the next byte, holding the SCL line low will force the master into a wait state. Data transfer continues when the slave releases the SCL line. This allows the slave to move the received data or fetch the data it needs to transfer before allowing the clock to start. This wait state technique can also be implemented at the bit level, Figure 11-18. The slave will inherently stretch the clock, when it is a transmitter, but will not when it is a receiver. The slave will have to clear the SSPCON<4> bit to enable clock stretching when it is a receiver.

#### FIGURE 11-18: DATA TRANSFER WAIT STATE

**NOTES:**

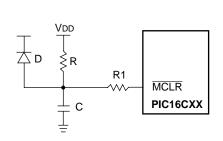

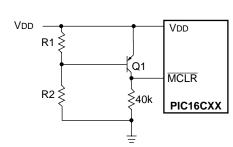

### FIGURE 14-13: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \text{ k}\Omega$  is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}$ /VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

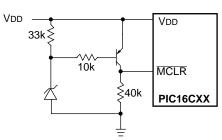

# FIGURE 14-14: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- Note 1: This circuit will activate reset when VDD goes below (Vz + 0.7V) where Vz = Zener voltage.

- 2: Internal brown-out detection on the PIC16C72/73A/74A/76/77 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

# FIGURE 14-15: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$VDD \bullet \frac{R1}{R1 + R2} = 0.7V$$

- 2: Internal brown-out detection on the PIC16C72/73A/74A/76/77 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

#### 15.0 INSTRUCTION SET SUMMARY

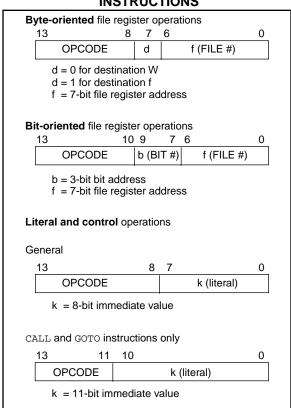

Each PIC16CXX instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXX instruction set summary in Table 15-2 lists byte-oriented, bit-oriented, and literal and control operations. Table 15-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

TABLE 15-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                        |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                               |

| W             | Working register (accumulator)                                                                                                                                     |

| b             | Bit address within an 8-bit file register                                                                                                                          |

| k             | Literal field, constant data or label                                                                                                                              |

| х             | Don't care location (= 0 or 1) The assembler will generate code with x = 0. It is the recommended form of use for compatibility with all Microchip software tools. |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                       |

| label         | Label name                                                                                                                                                         |

| TOS           | Top of Stack                                                                                                                                                       |

| PC            | Program Counter                                                                                                                                                    |

| PCLATH        | Program Counter High Latch                                                                                                                                         |

| GIE           | Global Interrupt Enable bit                                                                                                                                        |

| WDT           | Watchdog Timer/Counter                                                                                                                                             |

| TO            | Time-out bit                                                                                                                                                       |

| PD            | Power-down bit                                                                                                                                                     |

| dest          | Destination either the W register or the specified register file location                                                                                          |

| []            | Options                                                                                                                                                            |

| ( )           | Contents                                                                                                                                                           |

| $\rightarrow$ | Assigned to                                                                                                                                                        |

| <>            | Register bit field                                                                                                                                                 |

| €             | In the set of                                                                                                                                                      |

| italics       | User defined term (font is courier)                                                                                                                                |

The instruction set is highly orthogonal and is grouped into three basic categories:

- · Byte-oriented operations

- · Bit-oriented operations

- · Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu s$ . If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu s$ .

Table 15-2 lists the instructions recognized by the MPASM assembler.

Figure 15-1 shows the general formats that the instructions can have.

**Note:** To maintain upward compatibility with future PIC16CXX products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

Oxhh

where h signifies a hexadecimal digit.

FIGURE 15-1: GENERAL FORMAT FOR INSTRUCTIONS

| CLRF              | Clear f                                                        |                         |                 |                       |  |  |  |

|-------------------|----------------------------------------------------------------|-------------------------|-----------------|-----------------------|--|--|--|

| Syntax:           | [label] C                                                      | LRF f                   |                 |                       |  |  |  |

| Operands:         | $0 \le f \le 12$                                               | $0 \leq f \leq 127$     |                 |                       |  |  |  |

| Operation:        | $00h \rightarrow (f)$ $1 \rightarrow Z$                        |                         |                 |                       |  |  |  |

| Status Affected:  | Z                                                              |                         |                 |                       |  |  |  |

| Encoding:         | 00                                                             | 0001                    | 1fff            | ffff                  |  |  |  |

| Description:      | The contents of register 'f' are cleared and the Z bit is set. |                         |                 |                       |  |  |  |

| Words:            | 1                                                              |                         |                 |                       |  |  |  |

| Cycles:           | 1                                                              |                         |                 |                       |  |  |  |

| Q Cycle Activity: | Q1                                                             | Q2                      | Q3              | Q4                    |  |  |  |

|                   | Decode                                                         | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |  |  |

| Example           | CLRF                                                           | FLAG                    | G_REG           |                       |  |  |  |

|                   | Before Instruction<br>FLAG_REG = 0x5A                          |                         |                 |                       |  |  |  |

|                   | After Inst                                                     | ruction                 |                 |                       |  |  |  |

$FLAG_REG = 0x00$

| CLRW              | Clear W                                     |                  |                 |               |  |  |

|-------------------|---------------------------------------------|------------------|-----------------|---------------|--|--|

| Syntax:           | [ label ]                                   | CLRW             |                 |               |  |  |

| Operands:         | None                                        |                  |                 |               |  |  |

| Operation:        | $00h \rightarrow (W)$ $1 \rightarrow Z$     |                  |                 |               |  |  |

| Status Affected:  | Z                                           |                  |                 |               |  |  |

| Encoding:         | 00                                          | 0001             | 0xxx            | xxxx          |  |  |

| Description:      | W register is cleared. Zero bit (Z) is set. |                  |                 |               |  |  |

| Words:            | 1                                           |                  |                 |               |  |  |

| Cycles:           | 1                                           |                  |                 |               |  |  |

| Q Cycle Activity: | Q1                                          | Q2               | Q3              | Q4            |  |  |

|                   | Decode                                      | No-<br>Operation | Process<br>data | Write to<br>W |  |  |

| Example           | CLRW                                        |                  |                 |               |  |  |

|                   | Before In                                   | struction        |                 |               |  |  |

|                   |                                             | • •              | 0x5A            |               |  |  |

|                   | After Inst                                  |                  | 0x00            |               |  |  |

|                   |                                             | • •              | 1               |               |  |  |

| CLRWDT            | Clear Wa                                                                                                                         | tchdog 1              | Timer           |                         |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|-------------------------|--|--|

| Syntax:           | [ label ]                                                                                                                        | CLRWD1                | Г               |                         |  |  |

| Operands:         | None                                                                                                                             |                       |                 |                         |  |  |

| Operation:        | 00h → WDT<br>0 → WDT prescaler,<br>1 → $\overline{\text{TO}}$<br>1 → $\overline{\text{PD}}$                                      |                       |                 |                         |  |  |

| Status Affected:  | $\overline{TO}$ , $\overline{PD}$                                                                                                |                       |                 |                         |  |  |

| Encoding:         | 00                                                                                                                               | 0000                  | 0110            | 0100                    |  |  |

| Description:      | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits TO and PD are<br>set. |                       |                 |                         |  |  |

| Words:            | 1                                                                                                                                |                       |                 |                         |  |  |

| Cycles:           | 1                                                                                                                                |                       |                 |                         |  |  |

| Q Cycle Activity: | Q1                                                                                                                               | Q2                    | Q3              | Q4                      |  |  |

|                   | Decode                                                                                                                           | No-<br>Operation      | Process<br>data | Clear<br>WDT<br>Counter |  |  |

| Example           | CLRWDT                                                                                                                           |                       |                 |                         |  |  |

|                   | Before In                                                                                                                        | struction<br>WDT cour | nter =          | ?                       |  |  |

|                   | After Instruction  WDT counter = 0x00  WDT prescaler = 0  TO = 1  PD = 1                                                         |                       |                 |                         |  |  |

**Applicable Devices** 72 73 73A 74 74A 76 77

### 18.5 <u>Timing Diagrams and Specifications</u>

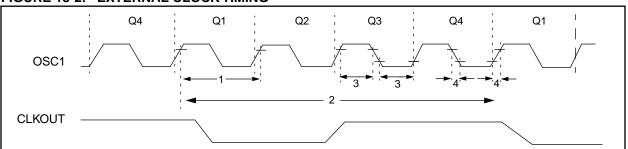

### FIGURE 18-2: EXTERNAL CLOCK TIMING

TABLE 18-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter No. | Sym   | Characteristic                        | Min | Тур† | Max    | Units | Conditions         |

|---------------|-------|---------------------------------------|-----|------|--------|-------|--------------------|

|               | Fosc  | External CLKIN Frequency              | DC  |      | 4      | MHz   | XT and RC osc mode |

|               |       | (Note 1)                              | DC  | _    | 4      | MHz   | HS osc mode (-04)  |

|               |       |                                       | DC  | _    | 10     | MHz   | HS osc mode (-10)  |

|               |       |                                       | DC  | _    | 20     | MHz   | HS osc mode (-20)  |

|               |       |                                       | DC  | _    | 200    | kHz   | LP osc mode        |

|               |       | Oscillator Frequency                  | DC  |      | 4      | MHz   | RC osc mode        |

|               |       | (Note 1)                              | 0.1 | _    | 4      | MHz   | XT osc mode        |

|               |       |                                       | 4   | _    | 20     | MHz   | HS osc mode        |

|               |       |                                       | 5   | _    | 200    | kHz   | LP osc mode        |

| 1             | Tosc  | External CLKIN Period                 | 250 |      | _      | ns    | XT and RC osc mode |

|               |       | (Note 1)                              | 250 | _    | _      | ns    | HS osc mode (-04)  |

|               |       |                                       | 100 | _    | _      | ns    | HS osc mode (-10)  |

|               |       |                                       | 50  | _    | _      | ns    | HS osc mode (-20)  |

|               |       |                                       | 5   | _    | _      | μs    | LP osc mode        |

|               |       | Oscillator Period                     | 250 |      | _      | ns    | RC osc mode        |

|               |       | (Note 1)                              | 250 | _    | 10,000 | ns    | XT osc mode        |

|               |       |                                       | 250 | _    | 250    | ns    | HS osc mode (-04)  |

|               |       |                                       | 100 | _    | 250    | ns    | HS osc mode (-10)  |

|               |       |                                       | 50  | _    | 250    | ns    | HS osc mode (-20)  |

|               |       |                                       | 5   | _    | _      | μs    | LP osc mode        |

| 2             | Tcy   | Instruction Cycle Time (Note 1)       | 200 | _    | DC     | ns    | Tcy = 4/Fosc       |

| 3             | TosL, | External Clock in (OSC1) High or      | 50  | _    | _      | ns    | XT oscillator      |

|               | TosH  | Low Time                              | 2.5 | _    | _      | μs    | LP oscillator      |

|               |       |                                       | 15  | _    | _      | ns    | HS oscillator      |

| 4             | TosR, | External Clock in (OSC1) Rise or      | _   | _    | 25     | ns    | XT oscillator      |

|               | TosF  | Fall Time                             | _   | _    | 50     | ns    | LP oscillator      |

|               |       | column is at EV 25°C upleas athorwise | _   | _    | 15     | ns    | HS oscillator      |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

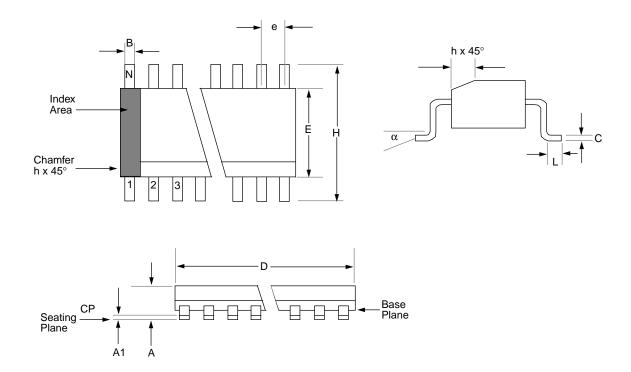

## 22.5 28-Lead Plastic Surface Mount (SOIC - Wide, 300 mil Body) (SO)

|        | Package Group: Plastic SOIC (SO) |             |         |       |        |         |  |  |

|--------|----------------------------------|-------------|---------|-------|--------|---------|--|--|

|        |                                  | Millimeters |         |       | Inches |         |  |  |

| Symbol | Min                              | Max         | Notes   | Min   | Max    | Notes   |  |  |

| α      | 0°                               | 8°          |         | 0°    | 8°     |         |  |  |

| А      | 2.362                            | 2.642       |         | 0.093 | 0.104  |         |  |  |

| A1     | 0.101                            | 0.300       |         | 0.004 | 0.012  |         |  |  |

| В      | 0.355                            | 0.483       |         | 0.014 | 0.019  |         |  |  |

| С      | 0.241                            | 0.318       |         | 0.009 | 0.013  |         |  |  |

| D      | 17.703                           | 18.085      |         | 0.697 | 0.712  |         |  |  |

| Е      | 7.416                            | 7.595       |         | 0.292 | 0.299  |         |  |  |

| е      | 1.270                            | 1.270       | Typical | 0.050 | 0.050  | Typical |  |  |

| Н      | 10.007                           | 10.643      |         | 0.394 | 0.419  |         |  |  |

| h      | 0.381                            | 0.762       |         | 0.015 | 0.030  |         |  |  |

| L      | 0.406                            | 1.143       |         | 0.016 | 0.045  |         |  |  |

| N      | 28                               | 28          |         | 28    | 28     |         |  |  |

| СР     | _                                | 0.102       |         | _     | 0.004  |         |  |  |

### PIN COMPATIBILITY

Devices that have the same package type and VDD, Vss and MCLR pin locations are said to be pin compatible. This allows these different devices to operate in the same socket. Compatible devices may only requires minor software modification to allow proper operation in the application socket (ex., PIC16C56 and PIC16C61 devices). Not all devices in the same package size are pin compatible; for example, the PIC16C62 is compatible with the PIC16C63, but not the PIC16C55.

Pin compatibility does not mean that the devices offer the same features. As an example, the PIC16C54 is pin compatible with the PIC16C71, but does not have an A/D converter, weak pull-ups on PORTB, or interrupts.

TABLE E-1: PIN COMPATIBLE DEVICES

| Pin Compatible Devices                                                                                                                                                                                                                                                                                                                                   | Package           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| PIC12C508, PIC12C509, PIC12C671, PIC12C672                                                                                                                                                                                                                                                                                                               | 8-pin             |

| PIC16C154, PIC16CR154, PIC16C156, PIC16CR156, PIC16C158, PIC16CR158, PIC16C52, PIC16C54, PIC16C54A, PIC16C84A, PIC16C56, PIC16C58A, PIC16CR58A, PIC16C61, PIC16C554, PIC16C556, PIC16C558 PIC16C620, PIC16C621, PIC16C622 PIC16C641, PIC16C642, PIC16C661, PIC16C662 PIC16C710, PIC16C71, PIC16C711, PIC16C715 PIC16F83, PIC16CR83, PIC16F84A, PIC16CR84 | 18-pin,<br>20-pin |

| PIC16C55, PIC16C57, PIC16CR57B                                                                                                                                                                                                                                                                                                                           | 28-pin            |

| PIC16CR62, PIC16C62A, PIC16C63, PIC16CR63, PIC16C66, PIC16C72, PIC16C73A, PIC16C76                                                                                                                                                                                                                                                                       | 28-pin            |

| PIC16CR64, PIC16C64A, PIC16C65A, PIC16CR65, PIC16C67, PIC16C74A, PIC16C77                                                                                                                                                                                                                                                                                | 40-pin            |

| PIC17CR42, PIC17C42A,<br>PIC17C43, PIC17CR43, PIC17C44                                                                                                                                                                                                                                                                                                   | 40-pin            |

| PIC16C923, PIC16C924                                                                                                                                                                                                                                                                                                                                     | 64/68-pin         |

| PIC17C756, PIC17C752                                                                                                                                                                                                                                                                                                                                     | 64/68-pin         |

| Registers                                   |              | SPBRG Register                                      | 26, 28             |

|---------------------------------------------|--------------|-----------------------------------------------------|--------------------|

| FSR                                         |              | Special Event Trigger                               |                    |

| Summary                                     | 29           | Special Features of the CPU                         |                    |

| INDF                                        |              | Special Function Registers                          |                    |

| Summary                                     | 20           | PIC16C72                                            | 23                 |

| Initialization Conditions                   |              | PIC16C73                                            |                    |

|                                             | 130          |                                                     | - ,                |

| INTCON                                      |              | PIC16C73A                                           | - /                |

| Summary                                     | 29           | PIC16C74                                            | •                  |

| Maps                                        |              | PIC16C74A                                           | 25, 27             |

| PIC16C72                                    | 21           | PIC16C76                                            | 27                 |

| PIC16C73                                    | 21           | PIC16C77                                            | 27                 |

| PIC16C73A                                   | 21           | Special Function Registers, Section                 | 23                 |

| PIC16C74                                    |              | SPEN bit                                            |                    |

| PIC16C74A                                   |              | SPI                                                 |                    |

|                                             |              |                                                     | 00.01              |

| PIC16C76                                    |              | Block Diagram                                       |                    |

| PIC16C77                                    | 22           | Master Mode                                         |                    |

| OPTION                                      |              | Master Mode Timing                                  |                    |

| Summary                                     | 29           | Mode                                                | 80                 |

| PCL                                         |              | Serial Clock                                        | 85                 |

| Summary                                     | 29           | Serial Data In                                      | 85                 |

| PCLATH                                      |              | Serial Data Out                                     | 85                 |

| Summary                                     | 29           | Slave Mode Timing                                   |                    |

| PORTB                                       |              | Slave Mode Timing Diagram                           |                    |

|                                             | 20           | Slave Select                                        |                    |

| Summary                                     |              |                                                     |                    |

| Reset Conditions                            | 136          | SPI clock                                           |                    |

| SSPBUF                                      |              | SPI Mode                                            |                    |

| Section                                     | 80           | SSPCON                                              | 84                 |

| SSPCON                                      |              | SSPSTAT                                             | 83                 |

| Diagram                                     | 79           | SPI Clock Edge Select bit, CKE                      | 83                 |

| SSPSR                                       |              | SPI Data Input Sample Phase Select bit, SM          |                    |

| Section                                     | 80           | SPI Mode                                            |                    |

| SSPSTAT                                     |              | SREN bit                                            |                    |

| Diagram                                     |              | SS                                                  |                    |

| <del>-</del>                                |              |                                                     | 00                 |

| Section                                     | 78           | SSP                                                 |                    |

| STATUS                                      |              | Module Overview                                     |                    |

| Summary                                     | 29           | Section                                             |                    |

| Summary                                     | 25, 27       | SSPBUF                                              | 86                 |

| TMR0                                        |              | SSPCON                                              | 84                 |

| Summary                                     | 29           | SSPSR                                               | 86                 |

| TRISB                                       |              | SSPSTAT                                             | 83                 |

| Summary                                     | 20           | SSP in I <sup>2</sup> C Mode - See I <sup>2</sup> C |                    |

| Reset                                       |              | SSPADD                                              | 01                 |

|                                             |              |                                                     |                    |

| Reset Conditions for Special Registers      |              | SSPADD Register                                     |                    |

| RP0 bit                                     | · ·          | SSPBUF                                              |                    |

| RP1 bit                                     | 30           | SSPBUF Register                                     |                    |

| RX9 bit                                     | 100          | SSPCON                                              | 79, 84             |

| RX9D bit                                    | 100          | SSPCON Register                                     | 25, 27             |

| _                                           |              | SSPEN                                               | 79. 84             |

| 5                                           |              | SSPIE bit                                           | •                  |

| 3                                           | 78 83        | SSPIF bit                                           |                    |

| SCK                                         | ,            | SSPM3:SSPM0                                         |                    |

|                                             |              |                                                     | ,                  |

| SCL                                         |              | SSPOV                                               |                    |

| SDI                                         |              | SSPSTAT                                             |                    |

| SDO                                         |              | SSPSTAT Register2                                   | 24, 26, 28, 29, 83 |

| Serial Communication Interface (SCI) Module | e, See USART | Stack                                               | 40                 |

| Services                                    |              | Overflows                                           | 40                 |

| One-Time-Programmable (OTP)                 | 7            | Underflow                                           |                    |

| Quick-Turnaround-Production (QTP)           |              | Start bit, S                                        |                    |

| Serialized Quick-Turnaround Production      |              | STATUS Register                                     |                    |

| Slave Mode                                  | . (54.1)     |                                                     |                    |

|                                             | 0.4          | Stop bit, P                                         | /8, 83             |

| SCL                                         |              | Synchronous Serial Port (SSP)                       |                    |

| SDA                                         |              | Block Diagram, SPI Mode                             | 80                 |

| SLEEP                                       | •            | SPI Master/Slave Diagram                            |                    |

| SMP                                         |              | SPI Mode                                            | 80                 |

| Software Simulator (MPSIM)                  | 165          | Synchronous Serial Port Enable bit, SSPEN           | 79, 84             |

| EDDDC .                                     | 20           | •                                                   | , -                |

| LIST OF       | TABLES                                     |     | Table 12-8:  | Registers Associated with Synchronous ter Transmission |      |

|---------------|--------------------------------------------|-----|--------------|--------------------------------------------------------|------|

| Table 1-1:    | PIC16C7XX Family of Devces                 |     | Table 12-9:  | Registers Associated with Synchronous                  |      |

| Table 3-1:    | PIC16C72 Pinout Description                |     | T 11 40 40   | ter Reception                                          | 112  |

| Table 3-2:    | PIC16C73/73A/76 Pinout Description         |     | Table 12-10: | Registers Associated with                              |      |

| Table 3-3:    | PIC16C74/74A/77 Pinout Description         | 15  | T 11 40 44   | Synchronous Slave Transmission                         | 115  |

| Table 4-1:    | PIC16C72 Special Function Register         | 00  | Table 12-11: | Registers Associated with                              | 115  |

| T 11 40       | Summary                                    | 23  | Table 40.4.  | Synchronous Slave Reception                            | 1 15 |

| Table 4-2:    | PIC16C73/73A/74/74A Special                |     | Table 13-1:  | TAD vs. Device Operating                               | 404  |

|               | Function Register Summary                  | 25  | Table 40.0   | Frequencies                                            | 121  |

| Table 4-3:    | PIC16C76/77 Special Function               |     | Table 13-2:  | Registers/Bits Associated with A/D,                    | 400  |

|               | Register Summary                           |     | Table 40.0   | PIC16C72                                               | 126  |

| Table 5-1:    | PORTA Functions                            | 44  | Table 13-3:  | Summary of A/D Registers,                              | 407  |

| Table 5-2:    | Summary of Registers Associated            |     | T-1-1-444    | PIC16C73/73A/74/74A/76/77                              |      |

|               | with PORTA                                 |     | Table 14-1:  | Ceramic Resonators                                     | 131  |

| Table 5-3:    | PORTB Functions                            | 46  | Table 14-2:  | Capacitor Selection for Crystal                        | 404  |

| Table 5-4:    | Summary of Registers Associated            |     |              | Oscillator                                             | 131  |

|               | with PORTB                                 |     | Table 14-3:  | Time-out in Various Situations,                        | 405  |

| Table 5-5:    | PORTC Functions                            | 48  |              | PIC16C73/74                                            | 135  |

| Table 5-6:    | Summary of Registers Associated            |     | Table 14-4:  | Time-out in Various Situations,                        |      |

|               | with PORTC                                 |     |              | PIC16C72/73A/74A/76/77                                 | 135  |

| Table 5-7:    | PORTD Functions                            | 50  | Table 14-5:  | Status Bits and Their Significance,                    |      |

| Table 5-8:    | Summary of Registers Associated            |     |              | PIC16C73/74                                            | 135  |

|               | with PORTD                                 |     | Table 14-6:  | Status Bits and Their Significance,                    |      |

| Table 5-9:    | PORTE Functions                            | 52  |              | PIC16C72/73A/74A/76/77                                 | 136  |

| Table 5-10:   | Summary of Registers Associated            |     | Table 14-7:  | Reset Condition for Special                            |      |

|               | with PORTE                                 | 52  |              | Registers                                              | 136  |

| Table 5-11:   | Registers Associated with                  |     | Table 14-8:  | Initialization Conditions for all                      |      |

|               | Parallel Slave Port                        | 55  |              | Registers                                              | 136  |

| Table 7-1:    | Registers Associated with Timer0           |     | Table 15-1:  | Opcode Field Descriptions                              | 147  |

| Table 8-1:    | Capacitor Selection for the                |     | Table 15-2:  | PIC16CXX Instruction Set                               | 148  |

|               | Timer1 Oscillator                          | 67  | Table 16-1:  | Development Tools from Microchip                       | 166  |

| Table 8-2:    | Registers Associated with Timer1           |     | Table 17-1:  | Cross Reference of Device Specs                        |      |

|               | as a Timer/Counter                         | 68  |              | for Oscillator Configurations and                      |      |

| Table 9-1:    | Registers Associated with                  |     |              | Frequencies of Operation                               |      |

|               | Timer2 as a Timer/Counter                  | 70  |              | (Commercial Devices)                                   | 167  |

| Table 10-1:   | CCP Mode - Timer Resource                  |     | Table 17-2:  | External Clock Timing                                  |      |

| Table 10-2:   | Interaction of Two CCP Modules             |     |              | Requirements                                           | 173  |

| Table 10-3:   | Example PWM Frequencies and                |     | Table 17-3:  | CLKOUT and I/O Timing                                  |      |

| . 42.0 . 0 0. | Resolutions at 20 MHz                      | 75  |              | Requirements                                           | 174  |

| Table 10-4:   | Registers Associated with Capture,         |     | Table 17-4:  | Reset, Watchdog Timer,                                 |      |

| 14510 10 1.   | Compare, and Timer1                        | 75  |              | Oscillator Start-up Timer, Power-up                    |      |

| Table 10-5:   | Registers Associated with PWM              |     |              | Timer, and brown-out Reset                             |      |

| Table 10 5.   | and Timer2                                 | 76  |              | Requirements                                           | 175  |

| Table 11-1:   | Registers Associated with SPI              | 10  | Table 17-5:  | Timer0 and Timer1 External                             |      |

| Table 11-1.   |                                            | 92  | Table 17 0.  | Clock Requirements                                     |      |

| Toblo 11 2:   | Operation                                  | 02  | Table 17-6:  | Capture/Compare/PWM                                    |      |

| Table 11-2:   | Registers Associated with SPI              | 00  | Table 17-0.  | Requirements (CCP1)                                    | 177  |

| Table 11 2.   | Operation (PIC16C76/77)                    |     | Table 17-7:  | SPI Mode Requirements                                  |      |

| Table 11-3:   | I <sup>2</sup> C Bus Terminology           | 69  | Table 17-7:  | I <sup>2</sup> C Bus Start/Stop Bits                   | 170  |

| Table 11-4:   | Data Transfer Received Byte                | 0.4 | Table 17-0.  |                                                        | 170  |

| T             | Actions                                    | 94  | Table 17.0   | Requirements                                           |      |

| Table 11-5:   | Registers Associated with I <sup>2</sup> C |     | Table 17-9:  | I <sup>2</sup> C Bus Data Requirements                 | 160  |

|               | Operation                                  |     | Table 17-10: | A/D Converter Characteristics:                         |      |

| Table 12-1:   | Baud Rate Formula                          | 101 |              | PIC16C72-04                                            |      |

| Table 12-2:   | Registers Associated with Baud             |     |              | (Commercial, Industrial, Extended)                     |      |

|               | Rate Generator                             |     |              | PIC16C72-10                                            |      |

| Table 12-3:   | Baud Rates for Synchronous Mode            | 102 |              | (Commercial, Industrial, Extended)                     |      |

| Table 12-4:   | Baud Rates for Asynchronous Mode           |     |              | PIC16C72-20                                            |      |

|               | (BRGH = 0)                                 | 102 |              | (Commercial, Industrial, Extended)                     |      |

| Table 12-5:   | Baud Rates for Asynchronous Mode           |     |              | PIC16LC72-04                                           |      |

|               | (BRGH = 1)                                 | 103 |              | (Commercial, Industrial)                               |      |

| Table 12-6:   | Registers Associated with                  |     | Table 17-11: | A/D Conversion Requirements                            | 182  |

|               | Asynchronous Transmission                  | 107 | Table 18-1:  | Cross Reference of Device                              |      |

| Table 12-7:   | Registers Associated with                  |     |              | Specs for Oscillator Configurations                    |      |

|               | Asynchronous Reception                     | 109 |              | and Frequencies of Operation                           |      |

|               | •                                          |     |              | (Commercial Devices)                                   | 183  |