Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

|                            |                                                                           |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 368 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                 |

| Data Converters            | A/D 8x8b                                                                  |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LCC (J-Lead)                                                           |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc77t-04-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

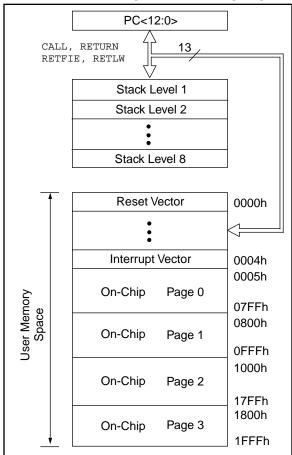

FIGURE 4-3: PIC16C76/77 PROGRAM MEMORY MAP AND STACK

### 4.2 <u>Data Memory Organization</u>

**Applicable Devices** 72 | 73 | 73 | 74 | 74 | 76 | 77 |

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

RP1:RP0 (STATUS<6:5>)

=  $00 \rightarrow Bank0$

=  $01 \rightarrow Bank1$

=  $10 \rightarrow Bank2$

=  $11 \rightarrow Bank3$

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain special function registers. Some "high use" special function registers from one bank may be mirrored in another bank for code reduction and quicker access.

### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR (Section 4.5).

TABLE 4-2: PIC16C73/73A/74/74A SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

| Address              | Name    | Bit 7                | Bit 6                        | Bit 5                   | Bit 4            | Bit 3         | Bit 2       | Bit 1         | Bit 0    | Value on:<br>POR,<br>BOR | Value on all other resets (2) |

|----------------------|---------|----------------------|------------------------------|-------------------------|------------------|---------------|-------------|---------------|----------|--------------------------|-------------------------------|

| Bank 1               |         |                      |                              |                         |                  |               |             |               |          |                          |                               |

| 80h <sup>(4)</sup>   | INDF    | Addressing           | this location                | uses conter             | nts of FSR to ac | ddress data i | memory (not | a physical re | egister) | 0000 0000                | 0000 0000                     |

| 81h                  | OPTION  | RBPU                 | INTEDG                       | TOCS                    | T0SE             | PSA           | PS2         | PS1           | PS0      | 1111 1111                | 1111 1111                     |

| 82h <sup>(4)</sup>   | PCL     | Program Co           | ounter's (PC)                | Least Signit            | ficant Byte      |               |             |               |          | 0000 0000                | 0000 0000                     |

| 83h <sup>(4)</sup>   | STATUS  | IRP <sup>(7)</sup>   | RP1 <sup>(7)</sup>           | RP0                     | TO               | PD            | Z           | DC            | С        | 0001 1xxx                | 000q quuu                     |

| 84h <sup>(4)</sup>   | FSR     | Indirect data        | a memory ad                  | dress pointe            | er               | •             |             | •             | •        | xxxx xxxx                | uuuu uuuu                     |

| 85h                  | TRISA   | _                    | _                            |                         | 11 1111          | 11 1111       |             |               |          |                          |                               |

| 86h                  | TRISB   | PORTB Dat            | ta Direction F               | Register                |                  |               |             |               |          | 1111 1111                | 1111 1111                     |

| 87h                  | TRISC   | PORTC Da             | ta Direction F               | Register                |                  |               |             |               |          | 1111 1111                | 1111 1111                     |

| 88h <sup>(5)</sup>   | TRISD   | PORTD Da             | ORTD Data Direction Register |                         |                  |               |             |               |          |                          | 1111 1111                     |

| 89h <sup>(5)</sup>   | TRISE   | IBF                  | OBF                          | IBOV                    | PSPMODE          | _             | PORTE Dat   | a Direction E | Bits     | 0000 -111                | 0000 -111                     |

| 8Ah <sup>(1,4)</sup> | PCLATH  | _                    | _                            | 0 0000                  | 0 0000           |               |             |               |          |                          |                               |

| 8Bh <sup>(4)</sup>   | INTCON  | GIE                  | PEIE                         | TOIE                    | INTE             | RBIE          | TOIF        | INTF          | RBIF     | 0000 000x                | 0000 000u                     |

| 8Ch                  | PIE1    | PSPIE <sup>(3)</sup> | ADIE                         | RCIE                    | TXIE             | SSPIE         | CCP1IE      | TMR2IE        | TMR1IE   | 0000 0000                | 0000 0000                     |

| 8Dh                  | PIE2    | _                    | _                            | _                       | _                | _             | _           | _             | CCP2IE   | 0                        | 0                             |

| 8Eh                  | PCON    | _                    | _                            | _                       | _                | _             | _           | POR           | BOR(6)   | qq                       | uu                            |

| 8Fh                  | _       | Unimpleme            | nted                         |                         | '                |               | '           |               | '        | _                        | _                             |

| 90h                  | _       | Unimpleme            | nted                         |                         |                  |               |             |               |          | _                        | _                             |

| 91h                  | _       | Unimpleme            | nted                         |                         |                  |               |             |               |          | _                        | _                             |

| 92h                  | PR2     | Timer2 Peri          | od Register                  |                         |                  |               |             |               |          | 1111 1111                | 1111 1111                     |

| 93h                  | SSPADD  | Synchronou           | us Serial Port               | (I <sup>2</sup> C mode) | Address Regis    | ter           |             |               |          | 0000 0000                | 0000 0000                     |

| 94h                  | SSPSTAT | _                    | _                            | D/Ā                     | Р                | S             | R/W         | UA            | BF       | 00 0000                  | 00 0000                       |

| 95h                  | _       | Unimpleme            | nted                         |                         |                  |               |             |               |          | _                        | _                             |

| 96h                  | _       | Unimpleme            | nted                         |                         |                  |               |             |               |          | _                        | _                             |

| 97h                  | _       | Unimpleme            | nted                         |                         |                  |               |             |               |          | _                        | _                             |

| 98h                  | TXSTA   | CSRC                 | TX9                          | TXEN                    | SYNC             | _             | BRGH        | TRMT          | TX9D     | 0000 -010                | 0000 -010                     |

| 99h                  | SPBRG   | Baud Rate            | Generator Re                 | egister                 | •                |               | -           |               | •        | 0000 0000                | 0000 0000                     |

| 9Ah                  | _       | Unimpleme            | nted                         |                         |                  |               |             |               |          | _                        | _                             |

| 9Bh                  | _       | Unimpleme            | nted                         |                         |                  |               |             |               |          | _                        | _                             |

| 9Ch                  | _       | Unimpleme            | nted                         |                         |                  |               |             |               |          | _                        | _                             |

| 9Dh                  | _       | Unimpleme            | nted                         |                         |                  |               |             |               |          | _                        | _                             |

| 9Eh                  | _       | Unimpleme            | nted                         |                         |                  |               |             |               |          | _                        | _                             |

| 9Fh                  | ADCON1  | _                    | _                            | _                       | _                | _             | PCFG2       | PCFG1         | PCFG0    | 000                      | 000                           |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

- 2: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

- 3: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A, always maintain these bits clear.

- 4: These registers can be addressed from either bank.

- 5: PORTD and PORTE are not physically implemented on the PIC16C73/73A, read as '0'.

- 6: Brown-out Reset is not implemented on the PIC16C73 or the PIC16C74, read as '0'.

- $7: \quad \text{The IRP and RP1 bits are reserved on the PIC16C73/73A/74/74A, always maintain these bits clear.}$

TABLE 4-3: PIC16C76/77 SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

| Address               | Name   | Bit 7                                                        | Bit 6                                  | Bit 5         | Bit 4           | Bit 3         | Bit 2           | Bit 1         | Bit 0    | Value on:<br>POR,<br>BOR | Value on all other resets (2) |

|-----------------------|--------|--------------------------------------------------------------|----------------------------------------|---------------|-----------------|---------------|-----------------|---------------|----------|--------------------------|-------------------------------|

| Bank 2                |        |                                                              |                                        |               |                 |               |                 |               |          |                          | •                             |

| 100h <sup>(4)</sup>   | INDF   | Addressing                                                   | this location                          | uses conten   | ts of FSR to a  | ddress data r | memory (not     | a physical re | egister) | 0000 0000                | 0000 0000                     |

| 101h                  | TMR0   | Timer0 mod                                                   | ule's registe                          | r             |                 |               |                 |               |          | xxxx xxxx                | uuuu uuuu                     |

| 102h <sup>(4)</sup>   | PCL    | Program Co                                                   | unter's (PC)                           | Least Signif  | icant Byte      |               |                 |               |          | 0000 0000                | 0000 0000                     |

| 103h <sup>(4)</sup>   | STATUS | IRP                                                          | RP1                                    | RP0           | TO              | PD            | Z               | DC            | С        | 0001 1xxx                | 000q quuu                     |

| 104h <sup>(4)</sup>   | FSR    | Indirect data                                                | memory ad                              | dress pointe  | r               | •             |                 | •             | •        | xxxx xxxx                | uuuu uuuu                     |

| 105h                  | _      | Unimplemen                                                   | nted                                   |               |                 |               |                 |               |          | _                        | _                             |

| 106h                  | PORTB  | PORTB Dat                                                    | a Latch whe                            | n written: PC | RTB pins whe    | n read        |                 |               |          | xxxx xxxx                | uuuu uuuu                     |

| 107h                  | _      | Unimpleme                                                    | nted                                   |               |                 |               |                 |               |          | _                        | _                             |

| 108h                  | _      | Unimplemer                                                   | Inimplemented —                        |               |                 |               |                 |               |          |                          |                               |

| 109h                  | _      | Unimplemen                                                   | nted                                   | _             | _               |               |                 |               |          |                          |                               |

| 10Ah <sup>(1,4)</sup> | PCLATH | — — Write Buffer for the upper 5 bits of the Program Counter |                                        |               |                 |               |                 |               |          | 0 0000                   | 0 0000                        |

| 10Bh <sup>(4)</sup>   | INTCON | GIE                                                          | GIE PEIE TOIE INTE RBIE TOIF INTF RBIF |               |                 |               |                 |               |          |                          | 0000 000u                     |

| 10Ch-<br>10Fh         | _      | Unimplemen                                                   | nted                                   |               |                 |               |                 |               |          | _                        | _                             |

| Bank 3                |        |                                                              |                                        |               |                 |               |                 |               |          |                          |                               |

| 180h <sup>(4)</sup>   | INDF   | Addressing                                                   | this location                          | uses conten   | ts of FSR to a  | ddress data r | memory (not     | a physical re | egister) | 0000 0000                | 0000 0000                     |

| 181h                  | OPTION | RBPU                                                         | INTEDG                                 | T0CS          | T0SE            | PSA           | PS2             | PS1           | PS0      | 1111 1111                | 1111 1111                     |

| 182h <sup>(4)</sup>   | PCL    | Program Co                                                   | unter's (PC)                           | Least Sign    | ificant Byte    |               |                 |               |          | 0000 0000                | 0000 0000                     |

| 183h <sup>(4)</sup>   | STATUS | IRP                                                          | RP1                                    | RP0           | то              | PD            | Z               | DC            | С        | 0001 1xxx                | 000q quuu                     |

| 184h <sup>(4)</sup>   | FSR    | Indirect data                                                | memory ad                              | dress pointe  | r               |               |                 |               |          | xxxx xxxx                | uuuu uuuu                     |

| 185h                  | _      | Unimplemen                                                   | nted                                   |               |                 |               |                 |               |          | _                        | _                             |

| 186h                  | TRISB  | PORTB Dat                                                    | a Direction F                          | Register      |                 |               |                 |               |          | 1111 1111                | 1111 1111                     |

| 187h                  | _      | Unimpleme                                                    | nted                                   |               |                 |               |                 |               |          | _                        | _                             |

| 188h                  | _      | Unimplemer                                                   | nted                                   |               |                 |               |                 |               |          | _                        | _                             |

| 189h                  | _      | Unimplemen                                                   | nted                                   |               |                 |               |                 |               |          | _                        | _                             |

| 18Ah <sup>(1,4)</sup> | PCLATH | _                                                            | _                                      | _             | Write Buffer fo | or the upper  | 5 bits of the I | Program Cou   | ınter    | 0 0000                   | 0 0000                        |

| 18Bh <sup>(4)</sup>   | INTCON | GIE                                                          | PEIE                                   | TOIE          | INTE            | RBIE          | TOIF            | INTF          | RBIF     | 0000 000x                | 0000 000u                     |

| 18Ch-<br>18Fh         | _      | Unimpleme                                                    | nted                                   |               |                 |               |                 |               |          | _                        | _                             |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

- Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

- 2: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

- 3: Bits PSPIE and PSPIF are reserved on the PIC16C76, always maintain these bits clear.

- 4: These registers can be addressed from any bank.

- 5: PORTD and PORTE are not physically implemented on the PIC16C76, read as '0'.

### 4.2.2.1 STATUS REGISTER

Applicable Devices 72 73 73 A 74 74 A 76 77

The STATUS register, shown in Figure 4-7, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

- Note 1: For those devices that do not use bits IRP and RP1 (STATUS<7:6>), maintain these bits clear to ensure upward compatibility with future products.

- Note 2: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

### FIGURE 4-7: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

| R/W-0    | R/W-0                                            | R/W-0                                                                                  | R-1                                  | R-1                                       | R/W-x                                        | R/W-x                                      | R/W-x                     |                                                                              |

|----------|--------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------|----------------------------------------------|--------------------------------------------|---------------------------|------------------------------------------------------------------------------|

| IRP      | RP1                                              | RP0                                                                                    | TO                                   | PD                                        | Z                                            | DC                                         | С                         | R = Readable bit W = Writable bit                                            |

| bit7     |                                                  |                                                                                        |                                      |                                           |                                              |                                            | bit0                      | W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset |

| bit 7:   | 1 = Bank 2                                       | ster Bank S<br>2, 3 (100h -<br>0, 1 (00h -                                             | - 1FFh)                              | (used for i                               | ndirect addr                                 | essing)                                    |                           |                                                                              |

| bit 6-5: | 11 = Bank<br>10 = Bank<br>01 = Bank<br>00 = Bank | Register E<br>3 (180h -<br>4 2 (100h -<br>5 1 (80h - F<br>6 0 (00h - 7<br>6 is 128 byt | 1FFh)<br>17Fh)<br>Fh)<br>Fh)         | ct bits (use                              | ed for direct                                | addressin                                  | g)                        |                                                                              |

| bit 4:   |                                                  |                                                                                        |                                      | struction,                                | or SLEEP ir                                  | struction                                  |                           |                                                                              |

| bit 3:   |                                                  | r-down bit<br>bower-up o<br>ecution of t                                               |                                      |                                           |                                              |                                            |                           |                                                                              |

| bit 2:   |                                                  | sult of an a                                                                           |                                      |                                           | peration is z                                |                                            |                           |                                                                              |

| bit 1:   | 1 = A carr                                       | y-out from                                                                             | the 4th lo                           | w order bi                                | w,SUBLW,S<br>t of the resu<br>pit of the res | ılt occurred                               |                           | r borrow the polarity is reversed                                            |

| bit 0:   | 1 = A carr<br>0 = No car<br>Note: For            | y-out from<br>rry-out fron<br>borrow the<br>perand. For                                | the most<br>n the mos<br>polarity is | significant<br>t significar<br>s reversed |                                              | esult occurr<br>result occu<br>ion is exec | ed<br>rred<br>uted by add | ding the two's complement of the                                             |

TABLE 5-1: PORTA FUNCTIONS

| Name         | Bit# | Buffer | Function                                                                       |

|--------------|------|--------|--------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF                                           |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0                                |

|              |      |        | Output is open drain type                                                      |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input |

Legend: TTL = TTL input, ST = Schmitt Trigger input

## TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5     | Bit 4       | Bit 3 | Bit 2   | Bit 1   | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|--------|-------|-------|-----------|-------------|-------|---------|---------|-------|--------------------------|---------------------------|

| 05h     | PORTA  | _     | _     | RA5       | RA4         | RA3   | RA2     | RA1     | RA0   | 0x 0000                  | 0u 0000                   |

| 85h     | TRISA  | _     | _     | PORTA Dat | a Direction | •     | 11 1111 | 11 1111 |       |                          |                           |

| 9Fh     | ADCON1 | _     | _     | _         | _           | _     | PCFG2   | PCFG1   | PCFG0 | 000                      | 000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

# 6.0 OVERVIEW OF TIMER MODULES

**Applicable Devices** 72 | 73 | 73 A | 74 | 74 A | 76 | 77

The PIC16C72, PIC16C73/73A, PIC16C74/74A, PIC16C76/77 each have three timer modules.

Each module can generate an interrupt to indicate that an event has occurred (i.e. timer overflow). Each of these modules is explained in full detail in the following sections. The timer modules are:

- Timer0 Module (Section 7.0)

- Timer1 Module (Section 8.0)

- Timer2 Module (Section 9.0)

### 6.1 Timer0 Overview

**Applicable Devices** 72 73 73A 74 74A 76 77

The Timer0 module is a simple 8-bit overflow counter. The clock source can be either the internal system clock (Fosc/4) or an external clock. When the clock source is an external clock, the Timer0 module can be selected to increment on either the rising or falling edge.

The Timer0 module also has a programmable prescaler option. This prescaler can be assigned to either the Timer0 module or the Watchdog Timer. Bit PSA (OPTION<3>) assigns the prescaler, and bits PS2:PS0 (OPTION<2:0>) determine the prescaler value. Timer0 can increment at the following rates: 1:1 (when prescaler assigned to Watchdog timer), 1:2, 1:4, 1:8, 1:16, 1:32, 1:64, 1:128, and 1:256 (Timer0 only).

Synchronization of the external clock occurs after the prescaler. When the prescaler is used, the external clock frequency may be higher then the device's frequency. The maximum frequency is 50 MHz, given the high and low time requirements of the clock.

### 6.2 <u>Timer1 Overview</u>

Applicable Devices 72 73 73 A 74 74 A 76 77

Timer1 is a 16-bit timer/counter. The clock source can be either the internal system clock (Fosc/4), an external clock, or an external crystal. Timer1 can operate as either a timer or a counter. When operating as a counter (external clock source), the counter can either operate synchronized to the device or asynchronously to the device. Asynchronous operation allows Timer1 to operate during sleep, which is useful for applications that require a real-time clock as well as the power savings of SLEEP mode.

Timer1 also has a prescaler option which allows Timer1 to increment at the following rates: 1:1, 1:2, 1:4, and 1:8. Timer1 can be used in conjunction with the Capture/Compare/PWM module. When used with a

CCP module, Timer1 is the time-base for 16-bit Capture or the 16-bit Compare and must be synchronized to the device.

### 6.3 Timer2 Overview

Applicable Devices 72 73 73 A 74 74 A 76 77

Timer2 is an 8-bit timer with a programmable prescaler and postscaler, as well as an 8-bit period register (PR2). Timer2 can be used with the CCP1 module (in PWM mode) as well as the Baud Rate Generator for the Synchronous Serial Port (SSP). The prescaler option allows Timer2 to increment at the following rates: 1:1, 1:4, 1:16.

The postscaler allows the TMR2 register to match the period register (PR2) a programmable number of times before generating an interrupt. The postscaler can be programmed from 1:1 to 1:16 (inclusive).

### 6.4 CCP Overview

**Applicable Devices** 72 73 73 A 74 74 A 76 77

The CCP module(s) can operate in one of these three modes: 16-bit capture, 16-bit compare, or up to 10-bit Pulse Width Modulation (PWM).

Capture mode captures the 16-bit value of TMR1 into the CCPRxH:CCPRxL register pair. The capture event can be programmed for either the falling edge, rising edge, fourth rising edge, or the sixteenth rising edge of the CCPx pin.

Compare mode compares the TMR1H:TMR1L register pair to the CCPRxH:CCPRxL register pair. When a match occurs an interrupt can be generated, and the output pin CCPx can be forced to given state (High or Low), TMR1 can be reset (CCP1), or TMR1 reset and start A/D conversion (CCP2). This depends on the control bits CCPxM3:CCPxM0.

PWM mode compares the TMR2 register to a 10-bit duty cycle register (CCPRxH:CCPRxL<5:4>) as well as to an 8-bit period register (PR2). When the TMR2 register = Duty Cycle register, the CCPx pin will be forced low. When TMR2 = PR2, TMR2 is cleared to 00h, an interrupt can be generated, and the CCPx pin (if an output) will be forced high.

# 10.0 CAPTURE/COMPARE/PWM MODULE(s)

| Аp |    |     |    |     |    |    |      |

|----|----|-----|----|-----|----|----|------|

|    |    |     |    |     |    |    | CCP1 |

| 72 | 73 | 73A | 74 | 74A | 76 | 77 | CCP2 |

Each CCP (Capture/Compare/PWM) module contains a 16-bit register which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave Duty Cycle register. Both the CCP1 and CCP2 modules are identical in operation, with the exception of the operation of the special event trigger. Table 10-1 and Table 10-2 show the resources and interactions of the CCP module(s). In the following sections, the operation of a CCP module is described with respect to CCP1. CCP2 operates the same as CCP1, except where noted.

### **CCP1** module:

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

### CCP2 module:

Capture/Compare/PWM Register2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. All are readable and writable.

For use of the CCP modules, refer to the Embedded Control Handbook, "Using the CCP Modules" (AN594).

TABLE 10-1: CCP MODE - TIMER RESOURCE

| CCP Mode | Timer Resource |  |  |  |  |

|----------|----------------|--|--|--|--|

| Capture  | Timer1         |  |  |  |  |

| Compare  | Timer1         |  |  |  |  |

| PWM      | Timer2         |  |  |  |  |

TABLE 10-2: INTERACTION OF TWO CCP MODULES

| CCPx Mode | <b>CCPy Mode</b> | Interaction                                                                           |

|-----------|------------------|---------------------------------------------------------------------------------------|

| Capture   | Capture          | Same TMR1 time-base.                                                                  |

| Capture   | Compare          | The compare should be configured for the special event trigger, which clears TMR1.    |

| Compare   | Compare          | The compare(s) should be configured for the special event trigger, which clears TMR1. |

| PWM       | PWM              | The PWMs will have the same frequency, and update rate (TMR2 interrupt).              |

| PWM       | Capture          | None                                                                                  |

| PWM       | Compare          | None                                                                                  |

#### 10.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in capture mode, the prescaler counter is cleared. This means that any reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 10-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

# EXAMPLE 10-1: CHANGING BETWEEN CAPTURE PRESCALERS

CLRF CCP1CON ;Turn CCP module off

MOVLW NEW\_CAPT\_PS ;Load the W reg with

; the new prescaler

; mode value and CCP ON

MOVWF CCP1CON ;Load CCP1CON with this

; value

### 10.2 Compare Mode

**Applicable Devices** 72 | 73 | 73 | 74 | 74 | 76 | 77

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- · Driven High

- Driven Low

- · Remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

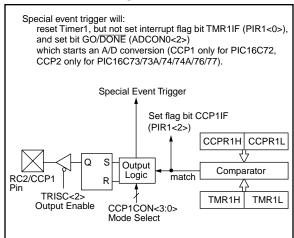

# FIGURE 10-3: COMPARE MODE OPERATION BLOCK DIAGRAM

### 10.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

**Note:** Clearing the CCP1CON register will force the RC2/CCP1 compare output latch to the default low level. This is not the data latch.

### 10.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

### 10.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

### 10.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special trigger output of CCP2 resets the TMR1 register pair, and starts an A/D conversion (if the A/D module is enabled).

For the PIC16C72 only, the special event trigger output of CCP1 resets the TMR1 register pair, and starts an A/D conversion (if the A/D module is enabled).

**Note:** The special event trigger from the CCP1 and CCP2 modules will not set interrupt flag bit TMR1IF (PIR1<0>).

**TABLE 10-5**: **REGISTERS ASSOCIATED WITH PWM AND TIMER2**

| Address               | Name    | Bit 7                  | Bit 6                               | Bit 5               | Bit 4               | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>PO<br>BO | R,   |      | e on<br>ther<br>ets |

|-----------------------|---------|------------------------|-------------------------------------|---------------------|---------------------|---------|--------|---------|---------|-------------------|------|------|---------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                    | PEIE                                | TOIE                | INTE                | RBIE    | TOIF   | INTF    | RBIF    | 0000              | 000x | 0000 | 000u                |

| 0Ch                   | PIR1    | PSPIF <sup>(1,2)</sup> | ADIF                                | RCIF <sup>(2)</sup> | TXIF <sup>(2)</sup> | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000              | 0000 | 0000 | 0000                |

| 0Dh <sup>(2)</sup>    | PIR2    | _                      | _                                   | _                   | _                   | _       | _      | _       | CCP2IF  |                   | 0    |      | 0                   |

| 8Ch                   | PIE1    | PSPIE <sup>(1,2)</sup> | ADIE                                | RCIE <sup>(2)</sup> | TXIE <sup>(2)</sup> | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000              | 0000 | 0000 | 0000                |

| 8Dh <sup>(2)</sup>    | PIE2    | _                      | _                                   | _                   | _                   | _       | _      | _       | CCP2IE  |                   | 0    |      | 0                   |

| 87h                   | TRISC   | PORTC D                | PORTC Data Direction Register       |                     |                     |         |        |         |         |                   |      | 1111 | 1111                |

| 11h                   | TMR2    | Timer2 mod             | dule's registe                      | er                  |                     |         |        |         |         | 0000              | 0000 | 0000 | 0000                |

| 92h                   | PR2     | Timer2 mod             | dule's period                       | l register          |                     |         |        |         |         | 1111              | 1111 | 1111 | 1111                |

| 12h                   | T2CON   | _                      | TOUTPS3                             | TOUTPS2             | TOUTPS1             | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000              | 0000 | -000 | 0000                |

| 15h                   | CCPR1L  | Capture/Co             | mpare/PWN                           | Л register1 (       | LSB)                |         |        |         |         | xxxx              | xxxx | uuuu | uuuu                |

| 16h                   | CCPR1H  | Capture/Co             | mpare/PWN                           | // register1 (      | (MSB)               |         |        |         |         | xxxx              | xxxx | uuuu | uuuu                |

| 17h                   | CCP1CON | _                      | _                                   | CCP1X               | CCP1Y               | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00                | 0000 | 00   | 0000                |

| 1Bh <sup>(2)</sup>    | CCPR2L  | Capture/Co             | Capture/Compare/PWM register2 (LSB) |                     |                     |         |        |         |         |                   | xxxx | uuuu | uuuu                |

| 1Ch <sup>(2)</sup>    | CCPR2H  | Capture/Co             | Capture/Compare/PWM register2 (MSB) |                     |                     |         |        |         |         |                   |      | uuuu | uuuu                |

| 1Dh <sup>(2)</sup>    | CCP2CON | _                      | _                                   | CCP2X               | CCP2Y               | CCP2M3  | CCP2M2 | CCP2M1  | CCP2M0  | 00                | 0000 | 00   | 0000                |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PWM and Timer2. Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

<sup>2:</sup> The PIC16C72 does not have a Parallel Slave Port, USART or CCP2 module, these bits are unimplemented, read as '0'.

### FIGURE 14-2: CONFIGURATION WORD FOR PIC16C72/73A/74A/76/77

CP0 PWRTE WDTE FOSC1 FOSC0 CONFIG CP1 CP0 CP1 CP0 CP1 CP0 BODEN CP1 Register: Address 2007h bit13 bit 13-8 CP1:CP0: Code Protection bits (2) 5-4: 11 = Code protection off 10 = Upper half of program memory code protected 01 = Upper 3/4th of program memory code protected 00 = All memory is code protected Unimplemented: Read as '1' bit 7: BODEN: Brown-out Reset Enable bit (1) bit 6: 1 = BOR enabled 0 = BOR disabled **PWRTE**: Power-up Timer Enable bit (1) bit 3: 1 = PWRT disabled 0 = PWRT enabled bit 2: WDTE: Watchdog Timer Enable bit 1 = WDT enabled 0 = WDT disabled bit 1-0: FOSC1:FOSC0: Oscillator Selection bits 11 = RC oscillator 10 = HS oscillator 01 = XT oscillator 00 = LP oscillator Note 1: Enabling Brown-out Reset automatically enables Power-up Timer (PWRT) regardless of the value of bit PWRTE. Ensure the Power-up Timer is enabled anytime Brown-out Reset is enabled. 2: All of the CP1:CP0 pairs have to be given the same value to enable the code protection scheme listed.

NOP No Operation Syntax: [label] NOP Operands: None Operation: No operation Status Affected: None Encoding: 0000 00 0xx00000 Description: No operation. Words: 1 1 Cycles: Q Cycle Activity: Q3 Q1 Q2 Q4 Decode No-No-No-Operation Operation Operation Example NOP

| OPTION           | Load Op                                                                                                                                                                                     | tion Reg | gister |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|--|--|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                   | OPTIO    | 1      |  |  |  |  |

| Operands:        | None                                                                                                                                                                                        |          |        |  |  |  |  |

| Operation:       | $(W) \rightarrow O$                                                                                                                                                                         | PTION    |        |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                        |          |        |  |  |  |  |

| Encoding:        | 00 0000 0110 0010                                                                                                                                                                           |          |        |  |  |  |  |

|                  | loaded in the OPTION register. This instruction is supported for code compatibility with PIC16C5X products. Since OPTION is a readable/writable register, the user can directly address it. |          |        |  |  |  |  |

| Words:           | 1                                                                                                                                                                                           |          |        |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                           |          |        |  |  |  |  |

|                  |                                                                                                                                                                                             |          |        |  |  |  |  |

| Example          | To maintain upward compatibility with future PIC16CXX products, do not use this instruction.                                                                                                |          |        |  |  |  |  |

| RETFIE            | Return fi                                                                                                                                                                                          | rom Inter        | rupt               |                    |  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|--------------------|--|--|--|--|

| Syntax:           | [ label ]                                                                                                                                                                                          | RETFIE           |                    |                    |  |  |  |  |

| Operands:         | None                                                                                                                                                                                               |                  |                    |                    |  |  |  |  |

| Operation:        | $\begin{array}{c} TOS \to F \\ 1 \to GIE \end{array}$                                                                                                                                              | PC,              |                    |                    |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                                               |                  |                    |                    |  |  |  |  |

| Encoding:         | 00                                                                                                                                                                                                 | 0000             | 0000               | 1001               |  |  |  |  |

| Description:      | Return from Interrupt. Stack is POPed and Top of Stack (TOS) is loaded in the PC. Interrupts are enabled by setting Global Interrupt Enable bit, GIE (INTCON<7>). This is a two cycle instruction. |                  |                    |                    |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                  |                  |                    |                    |  |  |  |  |

| Cycles:           | 2                                                                                                                                                                                                  |                  |                    |                    |  |  |  |  |

| Q Cycle Activity: | Q1                                                                                                                                                                                                 | Q2               | Q3                 | Q4                 |  |  |  |  |

| 1st Cycle         | Decode                                                                                                                                                                                             | No-<br>Operation | Set the<br>GIE bit | Pop from the Stack |  |  |  |  |

| 2nd Cycle         | No-<br>Operation                                                                                                                                                                                   | No-<br>Operation | No-<br>Operation   | No-<br>Operation   |  |  |  |  |

Example RETFIE

After Interrupt PC =

PC = TOS GIE = 1

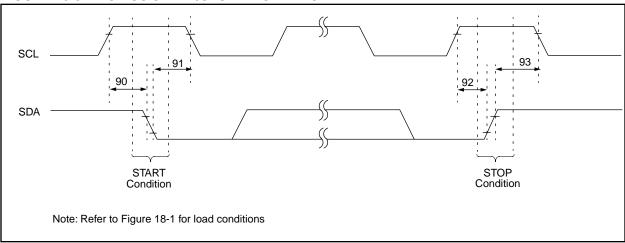

FIGURE 18-9: I<sup>2</sup>C BUS START/STOP BITS TIMING

TABLE 18-9: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Parameter No. | Sym     | Characteristic  |              | Min  | Тур | Max | Units | Conditions                        |

|---------------|---------|-----------------|--------------|------|-----|-----|-------|-----------------------------------|

| 90            | Tsu:sta | START condition | 100 kHz mode | 4700 | _   | _   | ns    | Only relevant for repeated START  |

|               |         | Setup time      | 400 kHz mode | 600  | _   | _   | 115   | condition                         |

| 91            | THD:STA | START condition | 100 kHz mode | 4000 | _   | _   | nc    | After this period the first clock |

|               |         | Hold time       | 400 kHz mode | 600  | _   | _   | ns    | pulse is generated                |

| 92            | Tsu:sto | STOP condition  | 100 kHz mode | 4700 | _   | _   | ns    |                                   |

|               |         | Setup time      | 400 kHz mode | 600  | _   | _   | 115   |                                   |

| 93            | THD:STO | STOP condition  | 100 kHz mode | 4000 | _   | _   | ns    |                                   |

|               |         | Hold time       | 400 kHz mode | 600  | _   | _   | 1115  |                                   |

## 19.2 DC Characteristics: PIC16LC73A/74A-04 (Commercial, Industrial)

| DC CHA        | RACTERISTICS                                                     |       |      | ard Ope | •      | •      | itions (unless otherwise stated)  °C ≤ TA ≤ +85°C for industrial and  C ≤ TA ≤ +70°C for commercial |

|---------------|------------------------------------------------------------------|-------|------|---------|--------|--------|-----------------------------------------------------------------------------------------------------|

| Param<br>No.  | Characteristic                                                   | Sym   | Min  | Тур†    | Max    | Units  | Conditions                                                                                          |

| D001          | Supply Voltage                                                   | VDD   | 2.5  | -       | 6.0    | V      | LP, XT, RC osc configuration (DC - 4 MHz)                                                           |

| D002*         | RAM Data Retention<br>Voltage (Note 1)                           | VDR   | -    | 1.5     | -      | V      |                                                                                                     |

| D003          | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR  | -    | Vss     | -      | >      | See section on Power-on Reset for details                                                           |

| D004*         | VDD rise rate to ensure internal Power-on Reset signal           | SVDD  | 0.05 | -       | -      | V/ms   | See section on Power-on Reset for details                                                           |

| D005          | Brown-out Reset Voltage                                          | BVDD  | 3.7  | 4.0     | 4.3    | V      | BODEN bit in configuration word enabled                                                             |

| D010          | Supply Current (Note 2,5)                                        | IDD   | -    | 2.0     | 3.8    | mA     | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                       |

| D010A         |                                                                  |       | -    | 22.5    | 48     | μΑ     | LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled                                     |

| D015*         | Brown-out Reset Current (Note 6)                                 | ΔIBOR | -    | 350     | 425    | μΑ     | BOR enabled VDD = 5.0V                                                                              |

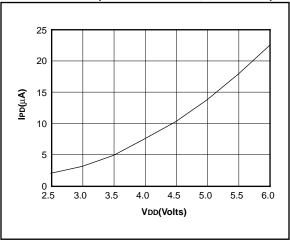

| D020          | Power-down Current                                               | IPD   | -    | 7.5     | 30     | μΑ     | VDD = 3.0V, WDT enabled, -40°C to +85°C                                                             |

| D021<br>D021A | (Note 3,5)                                                       |       | -    | 0.9     | 5<br>5 | μΑ     | VDD = 3.0V, WDT disabled, 0°C to +70°C                                                              |

| 1             | Brown-out Reset Current                                          | Albor | _    | 0.9     | •      | μA<br> | VDD = 3.0V, WDT disabled, -40°C to +85°C                                                            |

| D023*         | (Note 6)                                                         | Δlbor | -    | 350     | 425    | μΑ     | BOR enabled VDD = 5.0V                                                                              |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

- The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

- MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

**Standard Operating Conditions (unless otherwise stated)**

Operating temperature  $-40^{\circ}\text{C} \leq \text{TA} \leq +125^{\circ}\text{C}$  for extended,

-40°C ≤ TA ≤ +85°C for industrial and

$0^{\circ}C \leq TA \leq +70^{\circ}C$  for commercial

Operating voltage VDD range as described in DC spec Section 19.1 and Section 19.2.

|       | Section 13.2.                           |                   |           |     |     |       |                                                                    |  |  |  |

|-------|-----------------------------------------|-------------------|-----------|-----|-----|-------|--------------------------------------------------------------------|--|--|--|

| Param | Characteristic                          | Sym               | Min       | Тур | Max | Units | Conditions                                                         |  |  |  |

| No.   |                                         | _                 |           | †   |     |       |                                                                    |  |  |  |

|       | Output High Voltage                     |                   |           |     |     |       |                                                                    |  |  |  |

| D090  | I/O ports (Note 3)                      | Vон               | VDD - 0.7 | -   | -   | V     | IOH = $-3.0$ mA, VDD = $4.5$ V, $-40$ °C to $+85$ °C               |  |  |  |

| D090A |                                         |                   | VDD - 0.7 | -   | -   | V     | IOH = $-2.5$ mA, VDD = $4.5$ V,<br>-40°C to $+125$ °C              |  |  |  |

| D092  | OSC2/CLKOUT (RC osc config)             |                   | VDD - 0.7 | -   | -   | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40 $^{\circ}$ C to +85 $^{\circ}$ C |  |  |  |

| D092A |                                         |                   | VDD - 0.7 | -   | -   | V     | IOH = -1.0 mA, VDD = 4.5V,<br>-40°C to +125°C                      |  |  |  |

| D150* | Open-Drain High Voltage                 | Vod               | -         | -   | 14  | V     | RA4 pin                                                            |  |  |  |

|       | Capacitive Loading Specs on             |                   |           |     |     |       |                                                                    |  |  |  |

|       | Output Pins                             |                   |           |     |     |       |                                                                    |  |  |  |

| D100  | OSC2 pin                                | Cosc <sub>2</sub> | -         | -   | 15  | pF    | In XT, HS and LP modes when external clock is used to drive OSC1.  |  |  |  |

| D101  | All I/O pins and OSC2 (in RC            | Cıo               | -         | -   | 50  | pF    |                                                                    |  |  |  |

| D102  | mode) SCL, SDA in I <sup>2</sup> C mode | Св                | -         | -   | 400 | pF    |                                                                    |  |  |  |

\* These parameters are characterized but not tested.

DC CHARACTERISTICS

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C7X be driven with external clock in RC mode.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

20.1 **DC Characteristics:** PIC16C76/77-04 (Commercial, Industrial, Extended) PIC16C76/77-10 (Commercial, Industrial, Extended)

PIC16C76/77-20 (Commercial, Industrial, Extended)

Standard Operating Conditions (unless otherwise stated)

-40°C  $\leq$  TA  $\leq$  +125°C for extended, Operating temperature -40°C  $\leq$  TA  $\leq$  +85°C for industrial and

0°C ≤ TA ≤ +70°C for commercial

| Param<br>No.                   | Characteristic                                             | Sym           | Min         | Typ†                      | Max                  | Units                | Conditions                                                                                                                                                         |

|--------------------------------|------------------------------------------------------------|---------------|-------------|---------------------------|----------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D001<br>D001A                  | Supply Voltage                                             | VDD           | 4.0<br>4.5  | -                         | 6.0<br>5.5           | V<br>V               | XT, RC and LP osc configuration<br>HS osc configuration                                                                                                            |

| D002*                          | RAM Data Retention<br>Voltage (Note 1)                     | VDR           | -           | 1.5                       | -                    | V                    |                                                                                                                                                                    |

| D003                           | VDD start voltage to ensure internal Power-on Reset signal | VPOR          | -           | Vss                       | -                    | V                    | See section on Power-on Reset for details                                                                                                                          |

| D004*                          | VDD rise rate to ensure internal Power-on Reset signal     | SVDD          | 0.05        | -                         | -                    | V/ms                 | See section on Power-on Reset for details                                                                                                                          |

| D005                           | Brown-out Reset Voltage                                    | BVDD          | 3.7         | 4.0                       | 4.3                  | V                    | BODEN bit in configuration word enabled                                                                                                                            |

|                                |                                                            |               | 3.7         | 4.0                       | 4.4                  | V                    | Extended Range Only                                                                                                                                                |

| D010                           | Supply Current (Note 2,5)                                  | IDD           | -           | 2.7                       | 5                    | mA                   | XT, RC osc configuration<br>FOSC = 4 MHz, VDD = 5.5V (Note 4)                                                                                                      |

| D013                           |                                                            |               | -           | 10                        | 20                   | mA                   | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                                                  |

| D015*                          | Brown-out Reset Current (Note 6)                           | $\Delta$ lbor | -           | 350                       | 425                  | μΑ                   | BOR enabled VDD = 5.0V                                                                                                                                             |

| D020<br>D021<br>D021A<br>D021B | Power-down Current (Note 3,5)                              | IPD           | -<br>-<br>- | 10.5<br>1.5<br>1.5<br>2.5 | 42<br>16<br>19<br>19 | μΑ<br>μΑ<br>μΑ<br>μΑ | VDD = 4.0V, WDT enabled, -40°C to +85°C VDD = 4.0V, WDT disabled, -0°C to +70°C VDD = 4.0V, WDT disabled, -40°C to +85°C VDD = 4.0V, WDT disabled, -40°C to +125°C |

| D023*                          | Brown-out Reset Current (Note 6)                           | ΔIBOR         | -           | 350                       | 425                  | μΑ                   | BOR enabled VDD = 5.0V                                                                                                                                             |

- These parameters are characterized but not tested.

- Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

MCLR = VDD; WDT enabled/disabled as specified.

- 3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: Timer1 oscillator (when enabled) adds approximately 20 µA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The Δ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

**DC CHARACTERISTICS**

**Applicable Devices** 72 73 73A 74 74A 76 77

### **TABLE 20-13: A/D CONVERTER CHARACTERISTICS:**

PIC16C76/77-04 (Commercial, Industrial, Extended) PIC16C76/77-10 (Commercial, Industrial, Extended) PIC16C76/77-20 (Commercial, Industrial, Extended) PIC16LC76/77-04 (Commercial, Industrial)

| Param<br>No. | Sym                                      | Characteristic                            |                      | Min       | Тур†       | Max        | Units                                                                                              | Conditions                                     |

|--------------|------------------------------------------|-------------------------------------------|----------------------|-----------|------------|------------|----------------------------------------------------------------------------------------------------|------------------------------------------------|

| A01          | NR                                       | Resolution                                |                      | _         | _          | 8-bits     | bit                                                                                                | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF       |

| A02          | EABS                                     | Total Absolute error                      |                      | _         | _          | < ± 1      | LSb                                                                                                | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF       |

| A03          | EIL                                      | Integral linearity error                  |                      | _         | _          | < ± 1      | LSb                                                                                                | $VREF = VDD = 5.12V$ , $VSS \le VAIN \le VREF$ |

| A04          | EDL                                      | Differential linearity error              |                      | _         | _          | < ± 1      | LSb                                                                                                | $VREF = VDD = 5.12V$ , $VSS \le VAIN \le VREF$ |

| A05          | EFS                                      | Full scale error                          |                      | _         | _          | < ± 1      | LSb                                                                                                | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF       |

| A06          | Eoff                                     | Offset error                              |                      | _         | _          | < ± 1      | LSb                                                                                                | VREF = VDD = 5.12V,<br>VSS ≤ VAIN ≤ VREF       |

| A10          | _                                        | Monotonicity                              |                      | _         | guaranteed | _          | _                                                                                                  | Vss ≤ Vain ≤ Vref                              |

| A20          | VREF                                     | Reference voltage                         |                      | 3.0V      | _          | VDD + 0.3  | V                                                                                                  |                                                |

| A25          | VAIN                                     | Analog input voltage                      |                      | Vss - 0.3 | _          | VREF + 0.3 | V                                                                                                  |                                                |

| A30          | ZAIN                                     | Recommended impedar analog voltage source | ce of                | _         | _          | 10.0       | kΩ                                                                                                 |                                                |

| A40          | IAD                                      | A/D conversion current                    | PIC16 <b>C</b> 76/77 | _         | 180        | _          | μΑ                                                                                                 | Average current consump-                       |

|              |                                          | (VDD) PIC16 <b>LC</b> 76/77               |                      | _         | 90         | _          | μА                                                                                                 | tion when A/D is on.<br>(Note 1)               |

| A50          | A50   IREF   VREF input current (Note 2) |                                           | 10                   | _         | 1000       | μА         | During VAIN acquisition. Based on differential of VHOLD to VAIN to charge CHOLD, see Section 13.1. |                                                |

|              |                                          |                                           |                      | _         | _          | 10         | μА                                                                                                 | During A/D Conversion cycle                    |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: When A/D is off, it will not consume any current other than minor leakage current.

- The power-down current spec includes any such leakage from the A/D module.

- 2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

FIGURE 21-3: TYPICAL IPD vs. VDD @ 25°C (WDT ENABLED, RC MODE)

FIGURE 21-4: MAXIMUM IPD vs. VDD (WDT ENABLED, RC MODE)

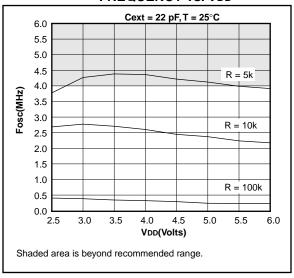

FIGURE 21-5: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

FIGURE 21-6: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

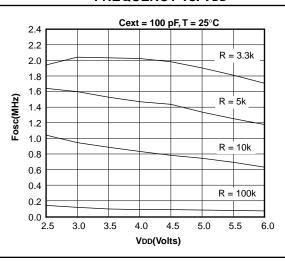

FIGURE 21-7: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

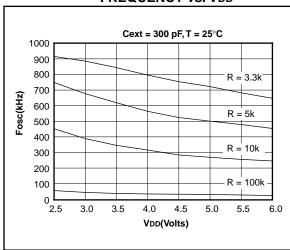

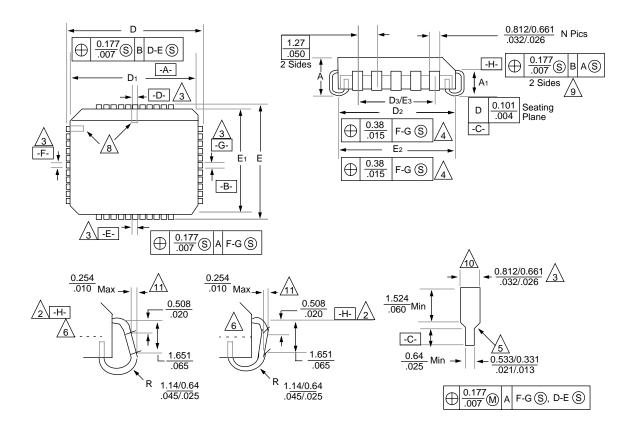

## 22.7 44-Lead Plastic Leaded Chip Carrier (Square)(PLCC)

| Package Group: Plastic Leaded Chip Carrier (PLCC) |        |             |           |       |       |           |  |  |

|---------------------------------------------------|--------|-------------|-----------|-------|-------|-----------|--|--|

|                                                   |        | Millimeters |           |       |       |           |  |  |

| Symbol                                            | Min    | Max         | Notes     | Min   | Max   | Notes     |  |  |

| Α                                                 | 4.191  | 4.572       |           | 0.165 | 0.180 |           |  |  |

| A1                                                | 2.413  | 2.921       |           | 0.095 | 0.115 |           |  |  |

| D                                                 | 17.399 | 17.653      |           | 0.685 | 0.695 |           |  |  |

| D1                                                | 16.510 | 16.663      |           | 0.650 | 0.656 |           |  |  |

| D2                                                | 15.494 | 16.002      |           | 0.610 | 0.630 |           |  |  |

| D3                                                | 12.700 | 12.700      | Reference | 0.500 | 0.500 | Reference |  |  |