Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | A/D 8x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-QFP                                                                     |

| Supplier Device Package    | 44-MQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc77t-04-pq |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

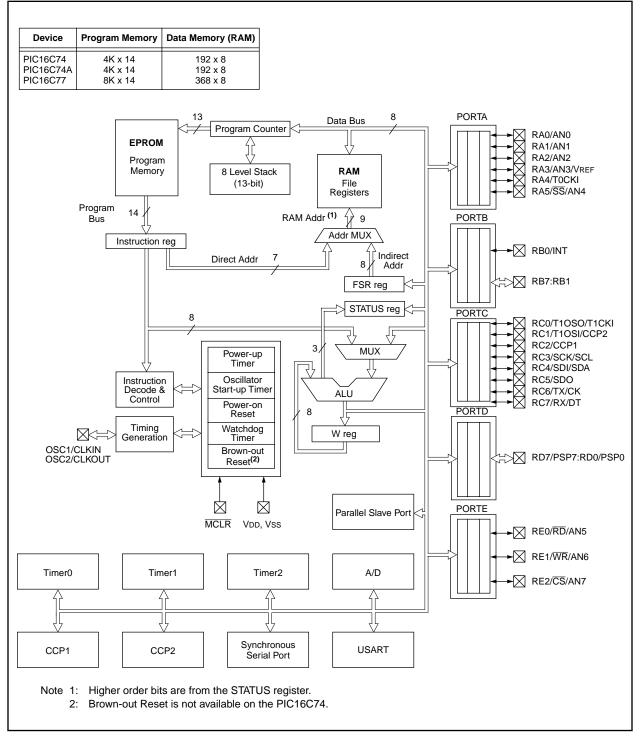

#### FIGURE 3-3: PIC16C74/74A/77 BLOCK DIAGRAM

#### TABLE 3-2:PIC16C73/73A/76 PINOUT DESCRIPTION

| Pin Name                | Name DIP SOIC I/O/P Buffer<br>Pin# Pin# Type Type |       |     | Description            |                                                                                                                                                                                                              |  |  |

|-------------------------|---------------------------------------------------|-------|-----|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| OSC1/CLKIN              | 9                                                 | 9     | I   | ST/CMOS <sup>(3)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                        |  |  |

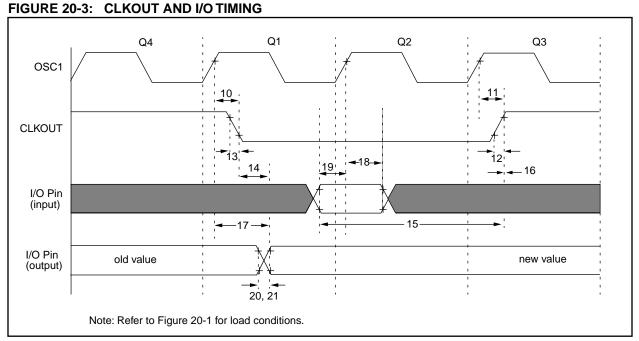

| OSC2/CLKOUT             | 10                                                | 10    | 0   | -                      | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |  |  |

| MCLR/Vpp                | 1                                                 | 1     | I/P | ST                     | Master clear (reset) input or programming voltage input. This pin is an active low reset to the device.                                                                                                      |  |  |

|                         |                                                   |       |     |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                          |  |  |

| RA0/AN0                 | 2                                                 | 2     | I/O | TTL                    | RA0 can also be analog input0                                                                                                                                                                                |  |  |

| RA1/AN1                 | 3                                                 | 3     | I/O | TTL                    | RA1 can also be analog input1                                                                                                                                                                                |  |  |

| RA2/AN2                 | 4                                                 | 4     | I/O | TTL                    | RA2 can also be analog input2                                                                                                                                                                                |  |  |

| RA3/AN3/VREF            | 5                                                 | 5     | I/O | TTL                    | RA3 can also be analog input3 or analog reference voltage                                                                                                                                                    |  |  |

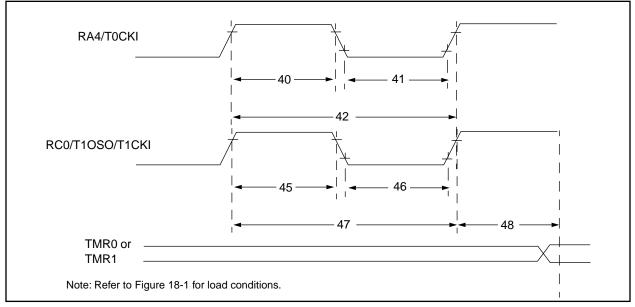

| RA4/T0CKI               | 6                                                 | 6     | I/O | ST                     | RA4 can also be the clock input to the Timer0 module.<br>Output is open drain type.                                                                                                                          |  |  |

| RA5/ <del>SS</del> /AN4 | 7                                                 | 7     | I/O | TTL                    | RA5 can also be analog input4 or the slave select for the<br>synchronous serial port.                                                                                                                        |  |  |

|                         |                                                   |       |     |                        | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                                |  |  |

| RB0/INT                 | 21                                                | 21    | I/O | TTL/ST(1)              | RB0 can also be the external interrupt pin.                                                                                                                                                                  |  |  |

| RB1                     | 22                                                | 22    | I/O | TTL                    |                                                                                                                                                                                                              |  |  |

| RB2                     | 23                                                | 23    | I/O | TTL                    |                                                                                                                                                                                                              |  |  |

| RB3                     | 24                                                | 24    | I/O | TTL                    |                                                                                                                                                                                                              |  |  |

| RB4                     | 25                                                | 25    | I/O | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |  |  |

| RB5                     | 26                                                | 26    | I/O | TTL                    | Interrupt on change pin.                                                                                                                                                                                     |  |  |

| RB6                     | 27                                                | 27    | I/O | TTL/ST(2)              | Interrupt on change pin. Serial programming clock.                                                                                                                                                           |  |  |

| RB7                     | 28                                                | 28    | I/O | TTL/ST(2)              | Interrupt on change pin. Serial programming data.                                                                                                                                                            |  |  |

|                         |                                                   |       |     |                        | PORTC is a bi-directional I/O port.                                                                                                                                                                          |  |  |

| RC0/T1OSO/T1CKI         | 11                                                | 11    | I/O | ST                     | RC0 can also be the Timer1 oscillator output or Timer1 clock input.                                                                                                                                          |  |  |

| RC1/T1OSI/CCP2          | 12                                                | 12    | I/O | ST                     | RC1 can also be the Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output.                                                                                                                   |  |  |

| RC2/CCP1                | 13                                                | 13    | I/O | ST                     | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                                                                                                                          |  |  |

| RC3/SCK/SCL             | 14                                                | 14    | I/O | ST                     | RC3 can also be the synchronous serial clock input/output for both SPI and I <sup>2</sup> C modes.                                                                                                           |  |  |

| RC4/SDI/SDA             | 15                                                | 15    | I/O | ST                     | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                                                                                              |  |  |

| RC5/SDO                 | 16                                                | 16    | I/O | ST                     | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                                 |  |  |

| RC6/TX/CK               | 17                                                | 17    | I/O | ST                     | RC6 can also be the USART Asynchronous Transmit of<br>Synchronous Clock.                                                                                                                                     |  |  |

| RC7/RX/DT               | 18                                                | 18    | I/O | ST                     | RC7 can also be the USART Asynchronous Receive of<br>Synchronous Data.                                                                                                                                       |  |  |

| Vss                     | 8, 19                                             | 8, 19 | Р   | <u> </u>               | Ground reference for logic and I/O pins.                                                                                                                                                                     |  |  |

| VDD                     | 20                                                | 20    | P   | <u> </u>               | Positive supply for logic and I/O pins.                                                                                                                                                                      |  |  |

| Legend: I = input       | O = outp                                          |       |     | input/output           | P = power                                                                                                                                                                                                    |  |  |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

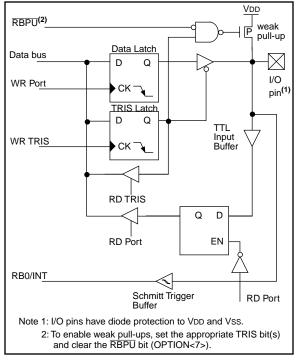

#### 5.2 PORTB and TRISB Registers

Applicable Devices

72 73 73A 74 74A 76 77

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a bit in the TRISB register puts the corresponding output driver in a hi-impedance input mode. Clearing a bit in the TRISB register puts the contents of the output latch on the selected pin(s).

#### EXAMPLE 5-2: INITIALIZING PORTB

| BCF   | STATUS, | RP0 | ; |                       |

|-------|---------|-----|---|-----------------------|

| CLRF  | PORTB   |     | ; | Initialize PORTB by   |

|       |         |     | ; | clearing output       |

|       |         |     | ; | data latches          |

| BSF   | STATUS, | RP0 | ; | Select Bank 1         |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISB   |     | ; | Set RB<3:0> as inputs |

|       |         |     | ; | RB<5:4> as outputs    |

|       |         |     | ; | RB<7:6> as inputs     |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overline{\text{RBPU}}$  (OPTION<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

#### FIGURE 5-3: BLOCK DIAGRAM OF RB3:RB0 PINS

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition, and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a keypad and make it possible for wake-up on key-depression. Refer to the Embedded Control Handbook, *"Implementing Wake-Up on Key Stroke"* (AN552).

| Note: | For the PIC16C73/74, if a change on the      |

|-------|----------------------------------------------|

|       | I/O pin should occur when the read opera-    |

|       | tion is being executed (start of the Q2      |

|       | cycle), then interrupt flag bit RBIF may not |

|       | get set.                                     |

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

#### FIGURE 10-1: CCP1CON REGISTER (ADDRESS 17h)/CCP2CON REGISTER (ADDRESS 1Dh)

| U-0      | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0    | R/W-0     | R/W-0  | R/W-0  | R/W-0  | R/W-0  |                                                                                      |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|--------|--------|--------|--------|--------------------------------------------------------------------------------------|--|--|--|--|

|          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CCPxX    | CCPxY     | CCPxM3 | CCPxM2 | CCPxM1 | CCPxM0 | R = Readable bit                                                                     |  |  |  |  |

| bit7     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |           |        |        |        | bit0   | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset |  |  |  |  |

| bit 7-6: | Unim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | plemente | d: Read a | s '0'  |        |        |        |                                                                                      |  |  |  |  |

| bit 5-4: | <b>CCPxX:CCPxY</b> : PWM Least Significant bits<br>Capture Mode: Unused<br>Compare Mode: Unused<br>PWM Mode: These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |           |        |        |        |        |                                                                                      |  |  |  |  |

| bit 3-0: | <ul> <li>CCPxM3:CCPxM0: CCPx Mode Select bits</li> <li>0000 = Capture/Compare/PWM off (resets CCPx module)</li> <li>0100 = Capture mode, every falling edge</li> <li>0110 = Capture mode, every rising edge</li> <li>0111 = Capture mode, every 4th rising edge</li> <li>0111 = Capture mode, every 16th rising edge</li> <li>1000 = Compare mode, set output on match (CCPxIF bit is set)</li> <li>1001 = Compare mode, clear output on match (CCPxIF bit is set)</li> <li>1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set, CCPx pin is unaffected)</li> <li>1011 = Compare mode, trigger special event (CCPxIF bit is set; CCP1 resets TMR1; CCP2 resets TMR1 and starts an A/D conversion (if A/D module is enabled))</li> <li>11xx = PWM mode</li> </ul> |          |           |        |        |        |        |                                                                                      |  |  |  |  |

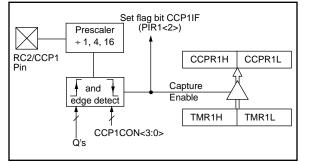

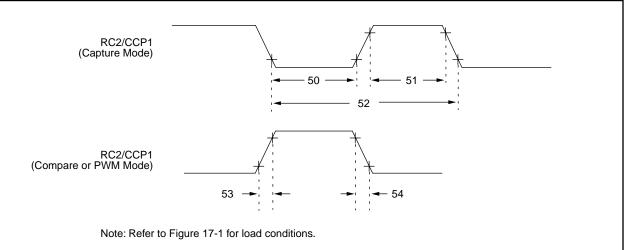

### 10.1 <u>Capture Mode</u>

Applicable Devices

72 73 73A 74 74A 76 77

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as:

- · Every falling edge

- · Every rising edge

- Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 10.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 is configured as an out-     |

|-------|----------------------------------------------|

|       | put, a write to the port can cause a capture |

|       | condition.                                   |

#### FIGURE 10-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 10.1.2 TIMER1 MODE SELECTION

Timer1 must be running in timer mode or synchronized counter mode for the CCP module to use the capture feature. In asynchronous counter mode, the capture operation may not work.

#### 10.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in operating mode.

### 12.0 UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

### Applicable Devices

72 73 73A 74 74A 76 77

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI). The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, Serial EEPROMs etc.

The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>), and bits TRISC<7:6>, have to be set in order to configure pins RC6/TX/CK and RC7/ RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

#### FIGURE 12-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

| R/W-0  | R/W-0                                                             | R/W-0                     | R/W-0        | U-0                     | R/W-0          | R-1      | R/W-0       |                                                                                            |

|--------|-------------------------------------------------------------------|---------------------------|--------------|-------------------------|----------------|----------|-------------|--------------------------------------------------------------------------------------------|

| CSRC   | TX9                                                               | TXEN                      | SYNC         | —                       | BRGH           | TRMT     | TX9D        | R = Readable bit                                                                           |

| bit7   |                                                                   |                           |              |                         |                |          | bit0        | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset       |

| bit 7: | CSRC: Clo                                                         | ck Source                 | Select bit   |                         |                |          |             |                                                                                            |

|        | Asynchrone<br>Don't care                                          | <u>ous mode</u>           |              |                         |                |          |             |                                                                                            |

|        | $\frac{\text{Synchrono}}{1 = \text{Master}}$ $0 = \text{Slave n}$ | mode (Clo                 |              |                         |                | .G)      |             |                                                                                            |

| bit 6: | <b>TX9</b> : 9-bit 7<br>1 = Selects<br>0 = Selects                | 9-bit trans               | mission      |                         |                |          |             |                                                                                            |

| bit 5: | <b>TXEN</b> : Tran<br>1 = Transm<br>0 = Transm<br>Note: SREI      | it enabled<br>it disabled |              | EN in SYN               | NC mode.       |          |             |                                                                                            |

| bit 4: | SYNC: US/<br>1 = Synchr<br>0 = Asynch                             | onous mod                 | le           |                         |                |          |             |                                                                                            |

| bit 3: | Unimplem                                                          | ented: Rea                | ad as '0'    |                         |                |          |             |                                                                                            |

| bit 2: | BRGH: Hig                                                         | h Baud Ra                 | te Select b  | it                      |                |          |             |                                                                                            |

|        | Asynchrone<br>1 = High sp                                         |                           |              |                         |                |          |             |                                                                                            |

|        | Note:                                                             | rience a h<br>baud rate   | igh rate of  | receive er<br>H = 0 can | rors. It is re | commende | ed that BRG | ode (BRGH = 1) may expe-<br>H = 0. If you desire a higher<br>a for additional information, |

|        | 0 = Low sp                                                        | eed                       |              |                         |                |          |             |                                                                                            |

|        | Synchrono<br>Unused in t                                          |                           |              |                         |                |          |             |                                                                                            |

| bit 1: | <b>TRMT</b> : Trar<br>1 = TSR en<br>0 = TSR ful                   | npty                      | Register St  | atus bit                |                |          |             |                                                                                            |

| bit 0: | <b>TX9D</b> : 9th I                                               | bit of transi             | mit data. Ca | an be pari              | ty bit.        |          |             |                                                                                            |

#### 12.4 USART Synchronous Slave Mode

## Applicable Devices 72 73 73A 74 74A 76 77

Synchronous slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 12.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the synchronous master and slave modes are identical except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

#### 12.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the synchronous master and slave modes is identical except in the case of the SLEEP mode. Also, bit SREN is a don't care in slave mode.

If receive is enabled, by setting bit CREN, prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Reception:

- 1. Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, then set enable bit RCIE.

- 3. If 9-bit reception is desired, then set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- 6. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

#### 13.4 A/D Conversions

Applicable Devices

72

73

73

74

74

76

77

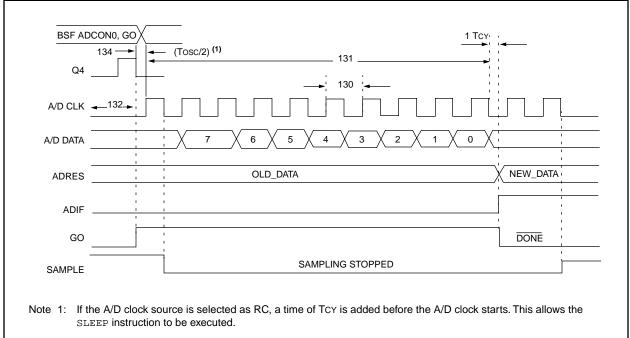

Example 13-2 shows how to perform an A/D conversion. The RA pins are configured as analog inputs. The analog reference (VREF) is the device VDD. The A/D interrupt is enabled, and the A/D conversion clock is FRC. The conversion is performed on the RA0 pin (channel 0).

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRES register will NOT be updated with the partially completed A/D conversion sample. That is, the ADRES register will continue to contain the value of the last completed conversion (or the last value written to the ADRES register). After the A/D conversion is aborted, a 2TAD wait is required before the next acquisition is started. After this 2TAD wait, an acquisition is automatically started on the selected channel.

### EXAMPLE 13-2: A/D CONVERSION

;

; ;

| BSF        | STATUS,  | RP0           | ;   | Select Bank 1                                       |

|------------|----------|---------------|-----|-----------------------------------------------------|

| BCF        | STATUS,  | RP1           | ;   | PIC16C76/77 only                                    |

| CLRF       | ADCON1   |               | ;   | Configure A/D inputs                                |

| BSF        | PIE1,    | ADIE          | ;   | Enable A/D interrupts                               |

| BCF        | STATUS,  | RP0           | ;   | Select Bank 0                                       |

| MOVLW      | 0xC1     |               | ;   | RC Clock, A/D is on, Channel 0 is selected          |

| MOVWF      | ADCON0   |               | ;   |                                                     |

| BCF        | PIR1,    | ADIF          | ;   | Clear A/D interrupt flag bit                        |

| BSF        | INTCON,  | PEIE          | ;   | Enable peripheral interrupts                        |

| BSF        | INTCON,  | GIE           | ;   | Enable all interrupts                               |

| Enquiro th | at the m | oquirod gamp  | 14. | ng time for the selected input channel has elapsed. |

|            |          | on may be sta |     |                                                     |

| BSF | ADCON0, | GO | ; | ; Start A/D Conversion                              |  |

|-----|---------|----|---|-----------------------------------------------------|--|

| :   |         |    | ; | ; The ADIF bit will be set and the GO/DONE bit      |  |

| :   |         |    | ; | ; is cleared upon completion of the A/D Conversion. |  |

| TABLE 14-6: | STATUS BITS AND THEIR SIGNIFICANCE, PIC16C72/73A/74A/76/77 |

|-------------|------------------------------------------------------------|

|-------------|------------------------------------------------------------|

| POR | BOR | TO | PD |                                                         |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset                                          |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | x  | x  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP |

#### TABLE 14-7: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register<br>PIC16C73/74 | PCON<br>Register<br>PIC16C72/73A/74A/76/77 |

|------------------------------------|-----------------------|--------------------|---------------------------------|--------------------------------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0-                              | 0x                                         |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | u-                              | uu                                         |

| MCLR Reset during SLEEP            | 000h                  | 0001 Ouuu          | u-                              | uu                                         |

| WDT Reset                          | 000h                  | 0000 luuu          | u-                              | uu                                         |

| WDT Wake-up                        | PC + 1                | uuu0 Ouuu          | u-                              | uu                                         |

| Brown-out Reset                    | 000h                  | 0001 luuu          | N/A                             | u0                                         |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | u-                              | uu                                         |

Legend: u = unchanged, x = unknown, - = unimplemented bit read as '0'.

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

| TABLE 14-8: | INITIALIZATION CONDITIONS FOR ALL REGISTERS |

|-------------|---------------------------------------------|

|-------------|---------------------------------------------|

| Register |    | Α  | pplica | ble | Devices |    |    | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT<br>or<br>Interrupt |  |

|----------|----|----|--------|-----|---------|----|----|------------------------------------|--------------------------|------------------------------------|--|

| W        | 72 | 73 | 73A    | 74  | 74A     | 76 | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                          |  |

| INDF     | 72 | 73 | 73A    | 74  | 74A     | 76 | 77 | N/A                                | N/A                      | N/A                                |  |

| TMR0     | 72 | 73 | 73A    | 74  | 74A     | 76 | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                          |  |

| PCL      | 72 | 73 | 73A    | 74  | 74A     | 76 | 77 | 0000h                              | 0000h                    | PC + 1 <sup>(2)</sup>              |  |

| STATUS   | 72 | 73 | 73A    | 74  | 74A     | 76 | 77 | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <b>(3)</b>               |  |

| FSR      | 72 | 73 | 73A    | 74  | 74A     | 76 | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                          |  |

| PORTA    | 72 | 73 | 73A    | 74  | 74A     | 76 | 77 | 0x 0000                            | 0u 0000                  | uu uuuu                            |  |

| PORTB    | 72 | 73 | 73A    | 74  | 74A     | 76 | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                          |  |

| PORTC    | 72 | 73 | 73A    | 74  | 74A     | 76 | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                          |  |

| PORTD    | 72 | 73 | 73A    | 74  | 74A     | 76 | 77 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                          |  |

| PORTE    | 72 | 73 | 73A    | 74  | 74A     | 76 | 77 | xxx                                | uuu                      | uuu                                |  |

| PCLATH   | 72 | 73 | 73A    | 74  | 74A     | 76 | 77 | 0 0000                             | 0 0000                   | u uuuu                             |  |

Legend: u = unchanged, x = unknown, -= unimplemented bit, read as '0', <math>q = value depends on condition

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 14-7 for reset value for specific condition.

| Register |    | Applicable Devices |     |    |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT<br>or<br>Interrupt |           |           |

|----------|----|--------------------|-----|----|-----|------------------------------------|--------------------------|------------------------------------|-----------|-----------|

| SSPADD   | 72 | 73                 | 73A | 74 | 74A | 76                                 | 77                       | 0000 0000                          | 0000 0000 | uuuu uuuu |

| SSPSTAT  | 72 | 73                 | 73A | 74 | 74A | 76                                 | 77                       | 00 0000                            | 00 0000   | uu uuuu   |

| TXSTA    | 72 | 73                 | 73A | 74 | 74A | 76                                 | 77                       | 0000 -010                          | 0000 -010 | uuuu -uuu |

| SPBRG    | 72 | 73                 | 73A | 74 | 74A | 76                                 | 77                       | 0000 0000                          | 0000 0000 | uuuu uuuu |

| ADCON1   | 72 | 73                 | 73A | 74 | 74A | 76                                 | 77                       | 000                                | 000       | uuu       |

#### TABLE 14-8: INITIALIZATION CONDITIONS FOR ALL REGISTERS (Cont.'d)

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 14-7 for reset value for specific condition.

# 14.8 Power-down Mode (SLEEP) Applicable Devices 727373A7474A7677

Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit (STATUS<3>) is cleared, the  $\overline{TO}$  (STATUS<4>) bit is set, and the oscillator driver is turned off. The I/O ports maintain the status they had, before the SLEEP instruction was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, place all I/O pins at either VDD, or Vss, ensure no external circuitry is drawing current from the I/O pin, power-down the A/D, disable external clocks. Pull all I/O pins, that are hi-impedance inputs, high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

#### 14.8.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin.

- 2. Watchdog Timer Wake-up (if WDT was enabled).

- 3. Interrupt from INT pin, RB port change, or some Peripheral Interrupts.

External  $\overline{\text{MCLR}}$  Reset will cause a device reset. All other events are considered a continuation of program execution and cause a "wake-up". The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the STATUS register can be used to determine the cause of device reset. The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up).

The following peripheral interrupts can wake the device from SLEEP:

- 1. TMR1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. SSP (Start/Stop) bit detect interrupt.

- 3. SSP transmit or receive in slave mode (SPI/ $l^2$ C).

- 4. CCP capture mode interrupt.

- 5. Parallel Slave Port read or write.

- 6. A/D conversion (when A/D clock source is RC).

- 7. Special event trigger (Timer1 in asynchronous mode using an external clock).

- 8. USART TX or RX (synchronous slave mode).

Other peripherals cannot generate interrupts since during SLEEP, no on-chip Q clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

#### 14.8.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT postscaler will not be cleared, the TO bit will not be set and PD bits will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will immediately wake up from sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT postscaler will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

| CLRF              | Clear f                                                               |                         |                 |                       |  |  |  |

|-------------------|-----------------------------------------------------------------------|-------------------------|-----------------|-----------------------|--|--|--|

| Syntax:           | [ <i>label</i> ] C                                                    | LRF f                   |                 |                       |  |  |  |

| Operands:         | $0 \le f \le 127$                                                     |                         |                 |                       |  |  |  |

| Operation:        | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |                         |                 |                       |  |  |  |

| Status Affected:  | Z                                                                     |                         |                 |                       |  |  |  |

| Encoding:         | 00                                                                    | 0001                    | lfff            | ffff                  |  |  |  |

| Description:      | The contents of register 'f' are cleared and the Z bit is set.        |                         |                 |                       |  |  |  |

| Words:            | 1                                                                     |                         |                 |                       |  |  |  |

| Cycles:           | 1                                                                     |                         |                 |                       |  |  |  |

| Q Cycle Activity: | Q1                                                                    | Q2                      | Q3              | Q4                    |  |  |  |

|                   | Decode                                                                | Read<br>register<br>'f' | Process<br>data | Write<br>register 'f' |  |  |  |

| Example           | CLRF                                                                  | FLAG                    | G_REG           |                       |  |  |  |

|                   | Before Instruction                                                    |                         |                 |                       |  |  |  |

|                   | After Inst                                                            | FLAG_RE                 | EG =            | 0x5A                  |  |  |  |

|                   |                                                                       | FLAG RE                 | EG =            | 0x00                  |  |  |  |

|                   |                                                                       | Ζ                       | =               | 1                     |  |  |  |

| CLRW                                                                                                               | Clear W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                            | [label] CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Operands:                                                                                                          | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Operation:                                                                                                         | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Status Affected:                                                                                                   | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Encoding:                                                                                                          | 00 0001 0xxx xxxx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Description:                                                                                                       | W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Words:                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Cycles:                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Q Cycle Activity:                                                                                                  | Q1 Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                    | Decode No-<br>Operation Process Write to<br>W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Example                                                                                                            | CLRW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                    | Before Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                    | W = 0x5A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                    | After Instruction<br>W = 0x00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                    | Z = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CLRWDT                                                                                                             | Clear Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Syntax:                                                                                                            | [label] CLRWDT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Operands:                                                                                                          | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| -                                                                                                                  | None $00h \rightarrow WDT$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Operands:                                                                                                          | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT$ prescaler,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Operands:                                                                                                          | None $00h \rightarrow WDT$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Operands:                                                                                                          | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT$ prescaler,<br>$1 \rightarrow \overline{TO}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Operands:<br>Operation:                                                                                            | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT$ prescaler,<br>$1 \rightarrow \overline{TO}$<br>$1 \rightarrow \overline{PD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Operands:<br>Operation:<br>Status Affected:                                                                        | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT$ prescaler,<br>$1 \rightarrow \overline{TO}$<br>$1 \rightarrow \overline{PD}$<br>$\overline{TO}, \overline{PD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:                                                           | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT$ prescaler,<br>$1 \rightarrow \overline{TO}$<br>$1 \rightarrow \overline{PD}$<br>$\overline{TO}, \overline{PD}$<br>OU 0000 0110 0100<br>CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits TO and PD are                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Operands:<br>Operation:<br>Status Affected:<br>Encoding:<br>Description:                                           | None<br>$00h \rightarrow WDT$<br>$0 \rightarrow WDT prescaler,$<br>$1 \rightarrow \overline{TO}$<br>$1 \rightarrow \overline{PD}$<br>$\overline{TO}, \overline{PD}$<br>CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits TO and PD are<br>set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |