Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

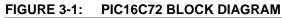

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | A/D 8x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc77t-04-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# FIGURE 4-4: PIC16C72 REGISTER FILE MAP

| File<br>Address   | 3                     |                     | File<br>Address |

|-------------------|-----------------------|---------------------|-----------------|

| 00h               | INDF <sup>(1)</sup>   | INDF <sup>(1)</sup> | 80h             |

| 01h               | TMR0                  | OPTION              | 81h             |

| 02h               | PCL                   | PCL                 |                 |

| 03h               | STATUS                | STATUS              |                 |

| 04h               | FSR                   | FSR                 |                 |

| 05h               | PORTA                 | TRISA               | 85h             |

| 06h               | PORTB                 | TRISB               | 86h             |

| 07h               | PORTC                 | TRISC               |                 |

| 08h               |                       |                     |                 |

| 09h               |                       |                     | 89h             |

| 0Ah               | PCLATH                | PCLATH              | 8Ah             |

| 0Bh               | INTCON                | INTCON              | 8Bh             |

| 0Ch               | PIR1                  | PIE1                | 8Ch             |

| 0Dh               |                       |                     | 8Dh             |

| 0Eh               | TMR1L                 | PCON                | 8Eh             |

| 0Fh               | TMR1H                 |                     | 8Fh             |

| 10h               | T1CON                 |                     | 90h             |

| 11h               | TMR2                  |                     | 91h             |

| 12h               | T2CON                 | PR2                 | 92h             |

| 13h               | SSPBUF                | SSPADD              | 93h             |

| 14h               | SSPCON                | SSPSTAT             |                 |

| 15h               | CCPR1L                |                     | 95h             |

| 16h               | CCPR1H                |                     | 96h             |

| 17h               | CCP1CON               |                     | 97h             |

| 18h               |                       |                     | 98h             |

| 19h               |                       |                     | 99h             |

| 1Ah               |                       |                     | 9Ah             |

| 1Bh               |                       |                     | 9Bh             |

| 1Ch               |                       |                     | 9Ch             |

| 1Dh               |                       |                     | 9Dh             |

| 1Eh               | ADRES                 |                     | 9Eh             |

| 1Fh               | ADCON0                | ADCON1              | 9Fh             |

| 20h               |                       |                     | A0h             |

|                   | General<br>Purpose    | General<br>Purpose  |                 |

|                   | Register              | Register            |                 |

|                   | U U                   |                     | BFh             |

|                   |                       |                     | C0h             |

|                   |                       |                     |                 |

|                   |                       |                     |                 |

|                   |                       |                     |                 |

| 7Fh               |                       |                     | FFh             |

|                   | Bank 0                | Bank 1              |                 |

|                   |                       |                     |                 |

|                   | nimplemented data     | a memory locations  | s, read as      |

| '0'.<br>Note 1: 1 | Not a physical regis  | stor                |                 |

|                   | tot a priysical regit | лот.                |                 |

|                   |                       |                     |                 |

#### FIGURE 4-5: PIC16C73/73A/74/74A REGISTER FILE MAP

| File<br>Addres                                    | SS                                                            |                                | File<br>Address |  |  |  |

|---------------------------------------------------|---------------------------------------------------------------|--------------------------------|-----------------|--|--|--|

| 00h                                               | INDF <sup>(1)</sup>                                           | INDF <sup>(1)</sup>            | 80h             |  |  |  |

| 01h                                               | TMR0                                                          | OPTION                         |                 |  |  |  |

| 02h                                               | PCL                                                           | PCL                            | 82h             |  |  |  |

| 03h                                               | STATUS                                                        | STATUS                         | 83h             |  |  |  |

| 04h                                               | FSR                                                           | FSR                            |                 |  |  |  |

| 05h                                               | PORTA                                                         | TRISA                          | 85h             |  |  |  |

| 06h                                               | PORTB                                                         | TRISB                          | 86h             |  |  |  |

| 07h                                               | PORTC                                                         | TRISC                          |                 |  |  |  |

| 08h                                               | PORTD <sup>(2)</sup>                                          | TRISD <sup>(2)</sup>           |                 |  |  |  |

| 09h                                               | PORTE <sup>(2)</sup>                                          | TRISE <sup>(2)</sup>           | 89h             |  |  |  |

| 0Ah                                               | PCLATH                                                        | PCLATH                         | 8Ah             |  |  |  |

| 0Bh                                               | INTCON                                                        | INTCON                         | 8Bh             |  |  |  |

| 0Ch                                               | PIR1                                                          | PIE1                           | 8Ch             |  |  |  |

| 0Dh                                               | PIR2                                                          | PIE2                           | 8Dh             |  |  |  |

| 0Eh                                               | TMR1L                                                         | PCON                           | 8Eh             |  |  |  |

| 0Fh                                               | TMR1H                                                         |                                | 8Fh             |  |  |  |

| 10h                                               | T1CON                                                         |                                | 90h             |  |  |  |

| 11h                                               | TMR2                                                          |                                | 91h             |  |  |  |

| 12h                                               | T2CON                                                         | PR2                            |                 |  |  |  |

| 13h                                               | SSPBUF                                                        | SSPADD                         | 93h             |  |  |  |

| 14h                                               | SSPCON                                                        | SSPSTAT                        | 94h             |  |  |  |

| 15h                                               | CCPR1L                                                        |                                | 95h             |  |  |  |

| 16h                                               | CCPR1H                                                        |                                | 96h             |  |  |  |

| 17h                                               | CCP1CON                                                       |                                | 97h             |  |  |  |

| 18h                                               | RCSTA                                                         | TXSTA                          |                 |  |  |  |

| 19h                                               | TXREG                                                         | SPBRG                          | 99h             |  |  |  |

| 1Ah                                               | RCREG                                                         |                                | 9Ah             |  |  |  |

| 1Bh                                               | CCPR2L                                                        |                                | 9Bh             |  |  |  |

| 1Ch                                               | CCPR2H                                                        |                                | 9Ch             |  |  |  |

| 1Dh                                               | CCP2CON                                                       |                                | 9Dh             |  |  |  |

| 1Eh                                               | ADRES                                                         |                                | 9Eh             |  |  |  |

| 1Fh                                               | ADCON0                                                        | ADCON1                         | 9Fh             |  |  |  |

| 20h                                               |                                                               |                                | A0h             |  |  |  |

|                                                   | General<br>Purpose<br>Register                                | General<br>Purpose<br>Register |                 |  |  |  |

| 7Fh                                               |                                                               |                                | FFh             |  |  |  |

|                                                   | Bank 0                                                        | Bank 1                         |                 |  |  |  |

| Unimplemented data memory locations, read as '0'. |                                                               |                                |                 |  |  |  |

| Note 1:<br>2:                                     | Not a physical reg<br>These registers ar<br>mented on the PIC | e not physically               |                 |  |  |  |

|                                                   |                                                               |                                |                 |  |  |  |

### TABLE 5-1: PORTA FUNCTIONS

| Name         | Bit# | Buffer | Function                                                                       |

|--------------|------|--------|--------------------------------------------------------------------------------|

| RA0/AN0      | bit0 | TTL    | Input/output or analog input                                                   |

| RA1/AN1      | bit1 | TTL    | Input/output or analog input                                                   |

| RA2/AN2      | bit2 | TTL    | Input/output or analog input                                                   |

| RA3/AN3/VREF | bit3 | TTL    | Input/output or analog input or VREF                                           |

| RA4/T0CKI    | bit4 | ST     | Input/output or external clock input for Timer0                                |

|              |      |        | Output is open drain type                                                      |

| RA5/SS/AN4   | bit5 | TTL    | Input/output or slave select input for synchronous serial port or analog input |

Legend: TTL = TTL input, ST = Schmitt Trigger input

### TABLE 5-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name   | Bit 7 | Bit 6 | Bit 5     | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0   | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|--------|-------|-------|-----------|-------------------------------|-------|-------|-------|---------|--------------------------|---------------------------|

| 05h     | PORTA  | —     | _     | RA5       | RA4                           | RA3   | RA2   | RA1   | RA0     | 0x 0000                  | 0u 0000                   |

| 85h     | TRISA  | —     | —     | PORTA Dat | PORTA Data Direction Register |       |       |       | 11 1111 | 11 1111                  |                           |

| 9Fh     | ADCON1 | —     |       | —         | _                             | _     | PCFG2 | PCFG1 | PCFG0   | 000                      | 000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

#### 10.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in capture mode, the prescaler counter is cleared. This means that any reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 10-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 10-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ; the new prescaler     |

|       |             | ; mode value and CCP ON |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ; value                 |

# 10.2 <u>Compare Mode</u>

Applicable Devices

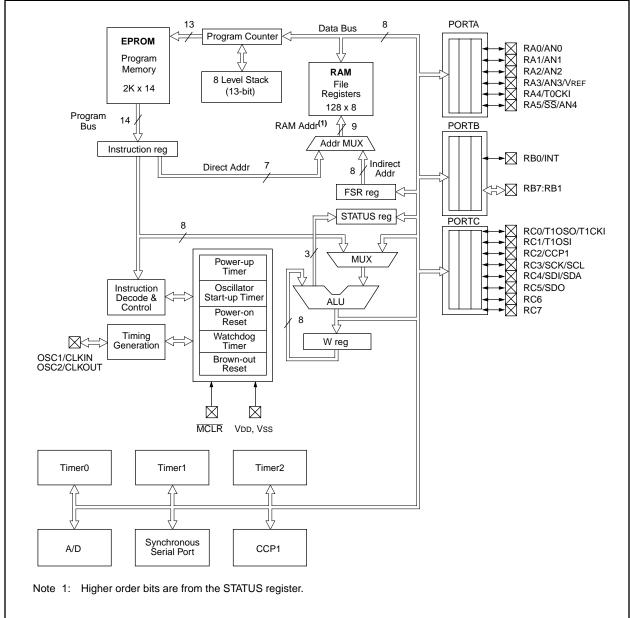

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- Driven High

- Driven Low

- · Remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### FIGURE 10-3: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 10.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force       |

|-------|------------------------------------------------|

|       | the RC2/CCP1 compare output latch to the       |

|       | default low level. This is not the data latch. |

#### 10.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 10.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 10.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special trigger output of CCP2 resets the TMR1 register pair, and starts an A/D conversion (if the A/D module is enabled).

For the PIC16C72 only, the special event trigger output of CCP1 resets the TMR1 register pair, and starts an A/D conversion (if the A/D module is enabled).

Note: The special event trigger from the CCP1and CCP2 modules will not set interrupt flag bit TMR1IF (PIR1<0>).

٦

#### 11.5.1.2 RECEPTION

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no acknowledge ( $\overline{ACK}$ ) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set. An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

# FIGURE 11-25: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

| Receiving Address         R/W           SDA         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - | =0Receiving Data<br>' <sup>ACK</sup> /D7XD6XD5XD4XD3XD2XD1XE<br> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| SSPIF (PIR1<3>)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Cleared in software                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Bus Master<br>terminates<br>transfer |

| SSPOV (SSPCON<6>)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Bit SSPOV is set b                                               | ecause the SSPBUF register is still free and the second structure of the second second structure of the second sec |                                      |

#### 12.4 USART Synchronous Slave Mode

# Applicable Devices 72 73 73A 74 74A 76 77

Synchronous slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 12.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the synchronous master and slave modes are identical except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

#### 12.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the synchronous master and slave modes is identical except in the case of the SLEEP mode. Also, bit SREN is a don't care in slave mode.

If receive is enabled, by setting bit CREN, prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Reception:

- 1. Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, then set enable bit RCIE.

- 3. If 9-bit reception is desired, then set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- 6. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

| NOP               | No Operation |                  |                  |                  |  |  |

|-------------------|--------------|------------------|------------------|------------------|--|--|

| Syntax:           | [ label ]    | NOP              |                  |                  |  |  |

| Operands:         | None         |                  |                  |                  |  |  |

| Operation:        | No operation |                  |                  |                  |  |  |

| Status Affected:  | None         |                  |                  |                  |  |  |

| Encoding:         | 00           | 0000             | 0xx0             | 0000             |  |  |

| Description:      | No operat    | ion.             |                  |                  |  |  |

| Words:            | 1            |                  |                  |                  |  |  |

| Cycles:           | 1            |                  |                  |                  |  |  |

| Q Cycle Activity: | Q1           | Q2               | Q3               | Q4               |  |  |

|                   | Decode       | No-<br>Operation | No-<br>Operation | No-<br>Operation |  |  |

| Example           | NOP          |                  |                  |                  |  |  |

| RETFIE                       | Return f                                                              | rom Inter                                                  | rupt                                                      |                            |  |

|------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------|----------------------------|--|

| Syntax:                      | [ label ]                                                             | RETFIE                                                     |                                                           |                            |  |

| Operands:                    | None                                                                  |                                                            |                                                           |                            |  |

| Operation:                   | $TOS \rightarrow PC$ ,<br>1 $\rightarrow GIE$                         |                                                            |                                                           |                            |  |

| Status Affected:             | None                                                                  |                                                            |                                                           |                            |  |

| Encoding:                    | 00                                                                    | 0000                                                       | 0000                                                      | 1001                       |  |

|                              | •                                                                     | · ·                                                        | ) is load                                                 |                            |  |

|                              | PC. Interru<br>Global Inte                                            | upts are er<br>errupt Ena<br><7>). This i                  | ble bit, GIE                                              | setting                    |  |

| Words:                       | PC. Interru<br>Global Inte<br>(INTCON<                                | upts are er<br>errupt Ena<br><7>). This i                  | habled by s<br>ble bit, GIE                               | setting                    |  |

| Words:<br>Cycles:            | PC. Interru<br>Global Inte<br>(INTCON-<br>instruction                 | upts are er<br>errupt Ena<br><7>). This i                  | habled by s<br>ble bit, GIE                               | setting                    |  |

|                              | PC. Interru<br>Global Inte<br>(INTCON-<br>instruction                 | upts are er<br>errupt Ena<br><7>). This i                  | habled by s<br>ble bit, GIE                               | setting                    |  |

| Cycles:                      | PC. Interru<br>Global Inte<br>(INTCON-<br>instruction<br>1<br>2       | upts are er<br>errupt Ena<br><7>). This i                  | nabled by s<br>ble bit, GIE<br>is a two cy                | setting<br>cle<br>Q4       |  |

| Cycles:<br>Q Cycle Activity: | PC. Interru<br>Global Inte<br>(INTCON-<br>instruction<br>1<br>2<br>Q1 | upts are er<br>errupt Ena<br><7>). This i<br><br>Q2<br>No- | abled by s<br>ble bit, GIE<br>s a two cy<br>Q3<br>Set the | setting<br><u>=</u><br>cle |  |

After Interrupt PC = TOS GIE = 1

| OPTION                 | Load Option Register                                                                        |                                                |                                                        |                                         |  |

|------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------|-----------------------------------------|--|

| Syntax:                | [ label ]                                                                                   | OPTION                                         | ٧                                                      |                                         |  |

| Operands:              | None                                                                                        |                                                |                                                        |                                         |  |

| Operation:             | $(W) \rightarrow OPTION$                                                                    |                                                |                                                        |                                         |  |

| Status Affected:       | None                                                                                        |                                                |                                                        |                                         |  |

| Encoding:              | 00                                                                                          | 0000                                           | 0110                                                   | 0010                                    |  |

| Description:<br>Words: | The conte<br>loaded in t<br>instruction<br>patibility w<br>Since OPT<br>register, th<br>it. | he OPTIC<br>is suppo<br>ith PIC16<br>TION is a | DN register<br>rted for coo<br>C5X produ<br>readable/v | r. This<br>de com-<br>ucts.<br>vritable |  |

|                        | •                                                                                           |                                                |                                                        |                                         |  |

| Cycles:                | 1                                                                                           |                                                |                                                        |                                         |  |

| Example                | <b>T</b>                                                                                    |                                                |                                                        | (1), 11(c - c                           |  |

|                        |                                                                                             | re PIC16                                       | rd compa<br>CXX produ<br>uction.                       |                                         |  |

|                        |                                                                                             |                                                |                                                        |                                         |  |

### SLEEP

| [ label ]                                                                                                                                                                                                      | SLEEP                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| None                                                                                                                                                                                                           |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                           |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| TO, PD                                                                                                                                                                                                         |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 00                                                                                                                                                                                                             | 0000                                                                                                                                                                                                                        | 0110                                                                                                                                                                                                                                                                                                | 0011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| The power-down status bit, PD is<br>cleared. Time-out status bit, TO is<br>set. Watchdog Timer and its pres-<br>caler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped. See |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 1                                                                                                                                                                                                              |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 1                                                                                                                                                                                                              |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Q1                                                                                                                                                                                                             | Q2                                                                                                                                                                                                                          | Q3                                                                                                                                                                                                                                                                                                  | Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Decode                                                                                                                                                                                                         | No-<br>Operation                                                                                                                                                                                                            | No-<br>Operation                                                                                                                                                                                                                                                                                    | Go to<br>Sleep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| SLEEP                                                                                                                                                                                                          |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                                                                                                                                                                                                                | None<br>$00h \rightarrow V$<br>$0 \rightarrow WD$<br>$1 \rightarrow TO, D$<br>TO, PD<br>TO, PD<br>00<br>The power<br>cleared. T<br>set. Watcl<br>caler are<br>The proce<br>mode with<br>Section 1<br>1<br>1<br>Q1<br>Decode | None<br>00h → WDT,<br>0 → WDT presca<br>1 → TO,<br>0 → PD<br>TO, PD<br>00 0000<br>The power-down sta<br>cleared. Time-out sta<br>set. Watchdog Time-<br>caler are cleared.<br>The processor is pur-<br>mode with the oscill<br>Section 14.8 for model<br>1<br>1<br>Q1 Q2<br>Decode No-<br>Operation | None         00h → WDT,         0 → WDT prescaler,         1 → TO,         0 → PD         TO, PD         00       0000         0100       0110         The power-down status bit, PI         cleared. Time-out status bit, T         set. Watchdog Timer and its p         caler are cleared.         The processor is put into SLE         mode with the oscillator stopp         Section 14.8 for more details.         1         Q1       Q2       Q3         Decode       No-       No-         Operation       Operation |  |  |

| SUBLW             | Subtract         | W from I            | iteral                                       |              |

|-------------------|------------------|---------------------|----------------------------------------------|--------------|

| Syntax:           | [ label ]        | SUBLW               | ′ k                                          |              |

| Operands:         | $0 \le k \le 25$ | 55                  |                                              |              |

| Operation:        | k - (W) →        | → (W)               |                                              |              |

| Status Affected:  | C, DC, Z         |                     |                                              |              |

| Encoding:         | 11               | 110x                | kkkk                                         | kkkk         |

| Description:      | ment meth        | nod) from th        | ntracted (2's<br>ne eight bit<br>n the W reg | literal 'k'. |

| Words:            | 1                |                     |                                              |              |

| Cycles:           | 1                |                     |                                              |              |

| Q Cycle Activity: | Q1               | Q2                  | Q3                                           | Q4           |

|                   | Decode           | Read<br>literal 'k' | Process<br>data                              | Write to W   |

| Example 1:        | SUBLW            | 0x02                |                                              |              |

|                   | Before In        | struction           |                                              |              |

|                   |                  | W =<br>C =<br>Z =   | 1<br>?<br>?                                  |              |

|                   | After Inst       | ruction             |                                              |              |

|                   |                  | W =<br>C =<br>Z =   | 1<br>1; result is<br>0                       | positive     |

| Example 2:        | Before In        | struction           |                                              |              |

|                   |                  | W =<br>C =<br>Z =   | 2<br>?<br>?                                  |              |

|                   | After Inst       | ruction             |                                              |              |

|                   |                  | W =<br>C =<br>Z =   | 0<br>1; result i<br>1                        | s zero       |

| Example 3:        | Before In        | struction           |                                              |              |

|                   |                  | W =<br>C =<br>Z =   | 3<br>?<br>?                                  |              |

|                   | After Inst       | ruction             |                                              |              |

|                   |                  | W =<br>C =<br>Z =   | 0xFF<br>0; result is<br>0                    | negative     |

| XORLW             | Exclusiv        | ve OR Li                                  | iteral wit      | th W          |

|-------------------|-----------------|-------------------------------------------|-----------------|---------------|

| Syntax:           | [label]         | XORL                                      | V k             |               |

| Operands:         | $0 \le k \le 2$ | 55                                        |                 |               |

| Operation:        | (W) .XO         | $R.k \rightarrow (N)$                     | N)              |               |

| Status Affected:  | Z               |                                           |                 |               |

| Encoding:         | 11              | 1010                                      | kkkk            | kkkk          |

| Description:      | XOR'ed v        | ents of the<br>vith the ei<br>t is placed | ght bit lite    | ral 'k'.      |

| Words:            | 1               |                                           |                 |               |

| Cycles:           | 1               |                                           |                 |               |

| Q Cycle Activity: | Q1              | Q2                                        | Q3              | Q4            |

|                   | Decode          | Read<br>literal 'k'                       | Process<br>data | Write to<br>W |

| Example:          | XORLW           | 0xAF                                      |                 |               |

|                   | Before I        | nstructio                                 | n               |               |

|                   |                 | W =                                       | 0xB5            |               |

|                   | After Ins       | truction                                  |                 |               |

|                   |                 | W =                                       | 0x1A            |               |

|                   |                 |                                           |                 |               |

| XORWF             | Exclusiv                                               | e OR W                    | with f                          |                        |

|-------------------|--------------------------------------------------------|---------------------------|---------------------------------|------------------------|

| Syntax:           | [label]                                                | XORWF                     | f,d                             |                        |

| Operands:         | $0 \le f \le 12$ $d \in [0,1]$                         | 7                         |                                 |                        |

| Operation:        | (W) .XOF                                               | $R.\left(f\right)\to(o$   | destinatio                      | on)                    |

| Status Affected:  | Z                                                      |                           |                                 |                        |

| Encoding:         | 00                                                     | 0110                      | dfff                            | ffff                   |

| Description:      | Exclusive<br>register wi<br>result is st<br>1 the resu | th registe<br>ored in the | r 'f'. If 'd' is<br>e W registe | 0 the<br>er. If 'd' is |

| Words:            | 1                                                      |                           |                                 |                        |

| Cycles:           | 1                                                      |                           |                                 |                        |

| Q Cycle Activity: | Q1                                                     | Q2                        | Q3                              | Q4                     |

|                   | Decode                                                 | Read<br>register<br>'f'   | Process<br>data                 | Write to destination   |

| Example           | XORWF                                                  |                           | 1                               |                        |

|                   | Before In                                              | struction                 |                                 |                        |

|                   |                                                        | REG<br>W                  | = 0x<br>= 0x                    | AF<br>B5               |

|                   | After Inst                                             | ruction                   |                                 |                        |

|                   |                                                        | REG<br>W                  | = 0x<br>= 0x                    | 1A<br>B5               |

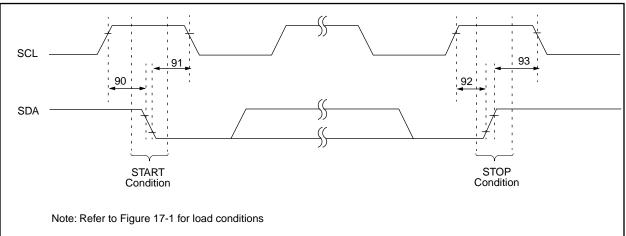

# Applicable Devices 72 73 73A 74 74A 76 77

# TABLE 17-8: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Parameter<br>No. | Sym     | Characteristic  |              | Min  | Тур | Max | Units | Conditions                        |

|------------------|---------|-----------------|--------------|------|-----|-----|-------|-----------------------------------|

| 90               | TSU:STA | START condition | 100 kHz mode | 4700 | —   | —   | ns    | Only relevant for repeated START  |

|                  |         | Setup time      | 400 kHz mode | 600  | -   | —   |       | condition                         |

| 91               | THD:STA | START condition | 100 kHz mode | 4000 | —   | —   | ns    | After this period the first clock |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | 115   | pulse is generated                |

| 92               | Tsu:sto | STOP condition  | 100 kHz mode | 4700 | —   | —   | ns    |                                   |

|                  |         | Setup time      | 400 kHz mode | 600  | —   | —   |       |                                   |

| 93               | THD:STO | STOP condition  | 100 kHz mode | 4000 | —   | —   | ns    |                                   |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | 113   |                                   |

Applicable Devices 72 73 73A 74 74A 76 77

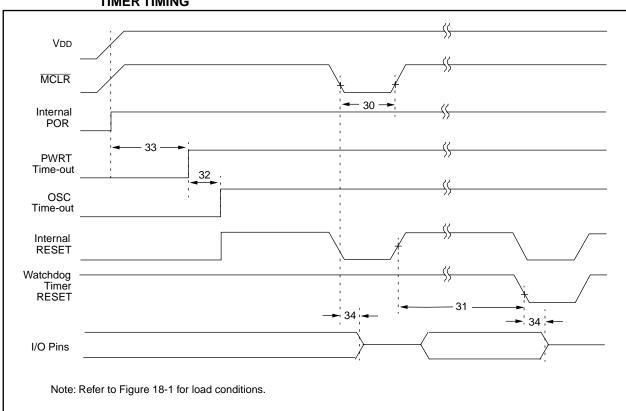

# FIGURE 18-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

# TABLE 18-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP<br/>TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†     | Max | Units | Conditions               |

|------------------|-------|--------------------------------------------------------|-----|----------|-----|-------|--------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                 | 100 | —        | —   | ns    | VDD = 5V, -40°C to +85°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +85°C |

| 32               | Tost  | Oscillation Start-up Timer Period                      | _   | 1024Tosc | —   | _     | Tosc = OSC1 period       |

| 33*              | Tpwrt | Power up Timer Period                                  | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +85°C |

| 34               | Tıoz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | —   | _        | 100 | ns    |                          |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# Applicable Devices 72 73 73A 74 74A 76 77

# 19.2 DC Characteristics: PIC16LC73A/74A-04 (Commercial, Industrial)

| DC CHARACTERISTICSStandard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C$ $\leq TA \leq +85^{\circ}C$ for industrial and<br>$0^{\circ}C$ $\leq TA \leq +70^{\circ}C$ for commercial |                                                                  |               |             |                   |              |                |                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------|-------------|-------------------|--------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                                                                                                                                                                                                                | Characteristic                                                   | Sym           | Min         | Тур†              | Max          | Units          | Conditions                                                                                                                                                                                   |

| D001                                                                                                                                                                                                                        | Supply Voltage                                                   | Vdd           | 2.5         | -                 | 6.0          | V              | LP, XT, RC osc configuration (DC - 4 MHz)                                                                                                                                                    |

| D002*                                                                                                                                                                                                                       | RAM Data Retention<br>Voltage (Note 1)                           | Vdr           | -           | 1.5               | -            | V              |                                                                                                                                                                                              |

| D003                                                                                                                                                                                                                        | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR          | -           | Vss               | -            | V              | See section on Power-on Reset for details                                                                                                                                                    |

| D004*                                                                                                                                                                                                                       | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | Svdd          | 0.05        | -                 | -            | V/ms           | See section on Power-on Reset for details                                                                                                                                                    |

| D005                                                                                                                                                                                                                        | Brown-out Reset Voltage                                          | Bvdd          | 3.7         | 4.0               | 4.3          | V              | BODEN bit in configuration word enabled                                                                                                                                                      |