Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | I²C, SPI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 368 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | A/D 8x8b                                                                   |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

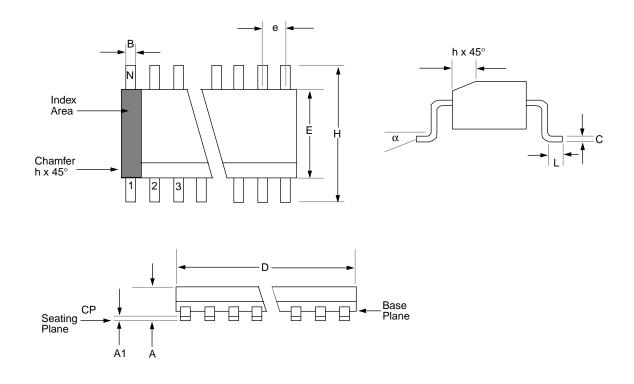

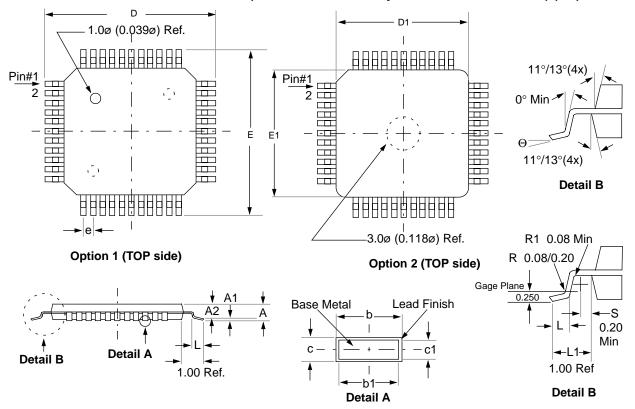

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc77t-04i-l |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

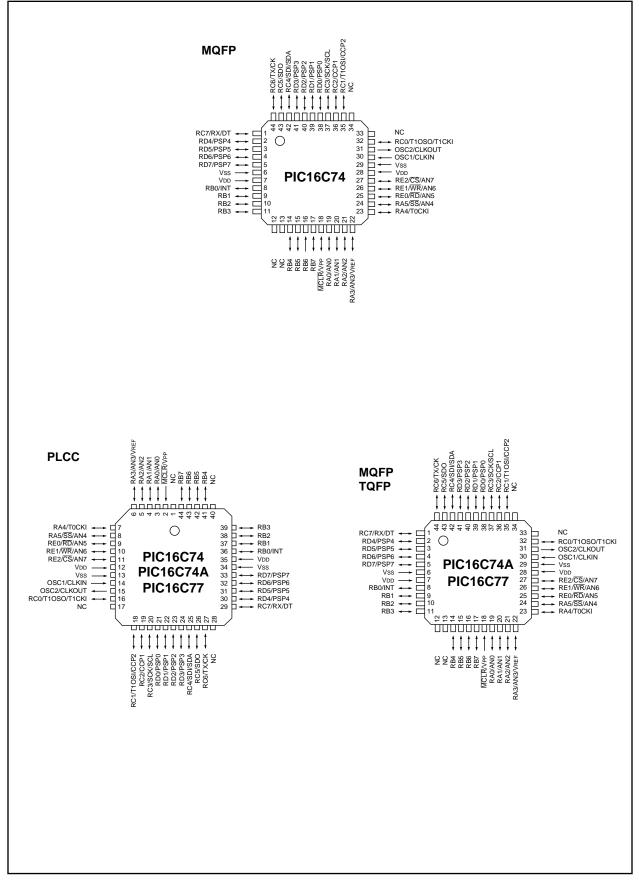

#### Pin Diagrams (Cont.'d)

# TABLE 3-3: PIC16C74/74A/77 PINOUT DESCRIPTION (Cont.'d)

| Pin Name          | DIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin# | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                            |

|-------------------|-------------|--------------|-------------|---------------|-----------------------|--------------------------------------------------------------------------------------------------------|

|                   |             |              |             |               |                       | PORTC is a bi-directional I/O port.                                                                    |

| RC0/T1OSO/T1CKI   | 15          | 16           | 32          | I/O           | ST                    | RC0 can also be the Timer1 oscillator output or a<br>Timer1 clock input.                               |

| RC1/T1OSI/CCP2    | 16          | 18           | 35          | I/O           | ST                    | RC1 can also be the Timer1 oscillator input or<br>Capture2 input/Compare2 output/PWM2 output.          |

| RC2/CCP1          | 17          | 19           | 36          | I/O           | ST                    | RC2 can also be the Capture1 input/Compare1 output/<br>PWM1 output.                                    |

| RC3/SCK/SCL       | 18          | 20           | 37          | I/O           | ST                    | RC3 can also be the synchronous serial clock input/<br>output for both SPI and I <sup>2</sup> C modes. |

| RC4/SDI/SDA       | 23          | 25           | 42          | I/O           | ST                    | RC4 can also be the SPI Data In (SPI mode) or data I/O ( $I^2$ C mode).                                |

| RC5/SDO           | 24          | 26           | 43          | I/O           | ST                    | RC5 can also be the SPI Data Out (SPI mode).                                                           |

| RC6/TX/CK         | 25          | 27           | 44          | I/O           | ST                    | RC6 can also be the USART Asynchronous Transmit or<br>Synchronous Clock.                               |

| RC7/RX/DT         | 26          | 29           | 1           | I/O           | ST                    | RC7 can also be the USART Asynchronous Receive or<br>Synchronous Data.                                 |

|                   |             |              |             |               |                       | PORTD is a bi-directional I/O port or parallel slave port when interfacing to a microprocessor bus.    |

| RD0/PSP0          | 19          | 21           | 38          | I/O           | ST/TTL <sup>(3)</sup> | when interfacing to a microprocessor bus.                                                              |

| RD1/PSP1          | 20          | 21           | 39          | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD2/PSP2          | 20          | 22           | 40          | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD3/PSP3          | 22          | 23           | 41          | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD4/PSP4          | 27          | 30           | 2           | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD5/PSP5          | 28          | 31           | 3           | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD6/PSP6          | 29          | 32           | 4           | 1/O           | ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD7/PSP7          | 30          | 33           | 5           | 1/0           | ST/TTL <sup>(3)</sup> |                                                                                                        |

|                   |             |              |             | 1/0           | OI/ITE                | PORTE is a bi-directional I/O port.                                                                    |

| RE0/RD/AN5        | 8           | 9            | 25          | I/O           | ST/TTL <sup>(3)</sup> | RE0 can also be read control for the parallel slave port,<br>or analog input5.                         |

| RE1/WR/AN6        | 9           | 10           | 26          | I/O           | ST/TTL <sup>(3)</sup> | RE1 can also be write control for the parallel slave port, or analog input6.                           |

| RE2/CS/AN7        | 10          | 11           | 27          | I/O           | ST/TTL <sup>(3)</sup> | RE2 can also be select control for the parallel slave port, or analog input7.                          |

| Vss               | 12,31       | 13,34        | 6,29        | Р             |                       | Ground reference for logic and I/O pins.                                                               |

| Vdd               | 11,32       | 12,35        | 7,28        | Р             | _                     | Positive supply for logic and I/O pins.                                                                |

| NC                | —           | 1,17,28,     | 12,13,      |               |                       | These pins are not internally connected. These pins should                                             |

|                   |             | 40           | 33,34       |               |                       | be left unconnected.                                                                                   |

| Legend: I = input | 0 = oi      | •            |             |               | put/output            | P = power                                                                                              |

|                   |             | lot used     |             |               | TL input              | ST = Schmitt Trigger input<br>external interrupt.                                                      |

Note 1: This buffer is a Schmitt Trigger input when configured as an external interrupt.

This buffer is a Schmitt Trigger input when used in serial programming mode.

This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel

Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

| Address              | Name    | Bit 7                                               | Bit 6                                               | Bit 5          | Bit 4           | Bit 3         | Bit 2           | Bit 1         | Bit 0    | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(2) |

|----------------------|---------|-----------------------------------------------------|-----------------------------------------------------|----------------|-----------------|---------------|-----------------|---------------|----------|--------------------------|-------------------------------------|

| Bank 0               | ·       | ·                                                   |                                                     |                |                 |               |                 |               |          |                          |                                     |

| 00h <sup>(4)</sup>   | INDF    | Addressing                                          | this location                                       | uses conter    | ts of FSR to a  | ddress data r | memory (not     | a physical re | egister) | 0000 0000                | 0000 0000                           |

| 01h                  | TMR0    | Timer0 mod                                          | lule's registe                                      | r              |                 |               |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 02h <sup>(4)</sup>   | PCL     | Program Co                                          | ounter's (PC)                                       |                | 0000 0000       | 0000 0000     |                 |               |          |                          |                                     |

| 03h <sup>(4)</sup>   | STATUS  | IRP                                                 | RP1                                                 | RP0            | TO              | PD            | Z               | DC            | С        | 0001 1xxx                | 000q quuu                           |

| 04h <b>(4)</b>       | FSR     | Indirect data                                       | Indirect data memory address pointer                |                |                 |               |                 |               |          |                          |                                     |

| 05h                  | PORTA   | _                                                   | PORTA Data Latch when written: PORTA pins when read |                |                 |               |                 |               |          |                          |                                     |

| 06h                  | PORTB   | PORTB Data Latch when written: PORTB pins when read |                                                     |                |                 |               |                 |               |          |                          | uuuu uuuu                           |

| 07h                  | PORTC   | PORTC Dat                                           | RTC Data Latch when written: PORTC pins when read   |                |                 |               |                 |               |          |                          | uuuu uuuu                           |

| 08h <sup>(5)</sup>   | PORTD   | PORTD Dat                                           | ta Latch whe                                        | n written: PC  | ORTD pins whe   | en read       |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 09h <sup>(5)</sup>   | PORTE   | —                                                   | _                                                   | _              | _               | _             | RE2             | RE1           | RE0      | xxx                      | uuu                                 |

| 0Ah <sup>(1,4)</sup> | PCLATH  | —                                                   | _                                                   | _              | Write Buffer fo | or the upper  | 5 bits of the I | Program Cou   | unter    | 0 0000                   | 0 0000                              |

| 0Bh <b>(4)</b>       | INTCON  | GIE                                                 | PEIE                                                | TOIE           | INTE            | RBIE          | TOIF            | INTF          | RBIF     | 0000 000x                | 0000 000u                           |

| 0Ch                  | PIR1    | PSPIF <sup>(3)</sup>                                | ADIF                                                | RCIF           | TXIF            | SSPIF         | CCP1IF          | TMR2IF        | TMR1IF   | 0000 0000                | 0000 0000                           |

| 0Dh                  | PIR2    | —                                                   | _                                                   | _              | -               | _             | —               | _             | CCP2IF   | 0                        | 0                                   |

| 0Eh                  | TMR1L   | Holding reg                                         | ister for the l                                     | _east Signific | ant Byte of the | e 16-bit TMR  | 1 register      |               | •        | xxxx xxxx                | uuuu uuuu                           |

| 0Fh                  | TMR1H   | Holding reg                                         | ister for the I                                     | Most Signific  | ant Byte of the | 16-bit TMR1   | register        |               |          | xxxx xxxx                | uuuu uuuu                           |

| 10h                  | T1CON   | _                                                   | _                                                   | T1CKPS1        | T1CKPS0         | T1OSCEN       | T1SYNC          | TMR1CS        | TMR10N   | 00 0000                  | uu uuuu                             |

| 11h                  | TMR2    | Timer2 mod                                          | lule's registe                                      | r              |                 | •             |                 |               |          | 0000 0000                | 0000 0000                           |

| 12h                  | T2CON   | —                                                   | TOUTPS3                                             | TOUTPS2        | TOUTPS1         | TOUTPS0       | TMR2ON          | T2CKPS1       | T2CKPS0  | -000 0000                | -000 0000                           |

| 13h                  | SSPBUF  | Synchronou                                          | s Serial Por                                        | t Receive Bu   | ffer/Transmit R | egister       |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 14h                  | SSPCON  | WCOL                                                | SSPOV                                               | SSPEN          | СКР             | SSPM3         | SSPM2           | SSPM1         | SSPM0    | 0000 0000                | 0000 0000                           |

| 15h                  | CCPR1L  | Capture/Co                                          | mpare/PWM                                           | Register1 (I   | _SB)            |               |                 |               |          | XXXX XXXX                | uuuu uuuu                           |

| 16h                  | CCPR1H  | Capture/Co                                          | mpare/PWM                                           | Register1 (I   | MSB)            |               |                 |               |          | XXXX XXXX                | uuuu uuuu                           |

| 17h                  | CCP1CON | —                                                   | _                                                   | CCP1X          | CCP1Y           | CCP1M3        | CCP1M2          | CCP1M1        | CCP1M0   | 00 0000                  | 00 0000                             |

| 18h                  | RCSTA   | SPEN                                                | RX9                                                 | SREN           | CREN            | _             | FERR            | OERR          | RX9D     | 0000 -00x                | 0000 -00x                           |

| 19h                  | TXREG   | USART Trai                                          | nsmit Data R                                        | egister        |                 |               |                 |               |          | 0000 0000                | 0000 0000                           |

| 1Ah                  | RCREG   | USART Red                                           | ceive Data R                                        | egister        |                 |               |                 |               |          | 0000 0000                | 0000 0000                           |

| 1Bh                  | CCPR2L  | Capture/Compare/PWM Register2 (LSB)                 |                                                     |                |                 |               |                 |               |          |                          | uuuu uuuu                           |

| 1Ch                  | CCPR2H  | Capture/Compare/PWM Register2 (MSB)                 |                                                     |                |                 |               |                 |               |          | XXXX XXXX                | uuuu uuuu                           |

| 1Dh                  | CCP2CON | —                                                   | _                                                   | CCP2X          | CCP2Y           | CCP2M3        | CCP2M2          | CCP2M1        | CCP2M0   | 00 0000                  | 00 0000                             |

| 1Eh                  | ADRES   | A/D Result                                          | Register                                            |                |                 |               |                 |               |          | xxxx xxxx                | uuuu uuuu                           |

| 1Fh                  | ADCON0  | ADCS1                                               | ADCS0                                               | CHS2           | CHS1            | CHS0          | GO/DONE         | —             | ADON     | 0000 00-0                | 0000 00-0                           |

TABLE 4-3: PIC16C76/77 SPECIAL FUNCTION REGISTER SUMMARY

$\label{eq:legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.$  Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the PIC16C76, always maintain these bits clear.

4: These registers can be addressed from any bank.

5: PORTD and PORTE are not physically implemented on the PIC16C76, read as '0'.

NOTES:

#### 5.4 PORTD and TRISD Registers

# Applicable Devices 72 73 73A 74 74A 76 77

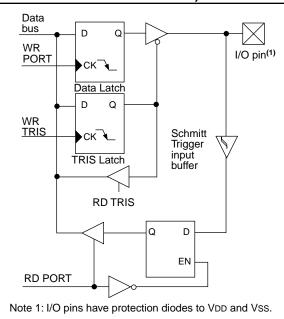

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

PORTD can be configured as an 8-bit wide microprocessor port (parallel slave port) by setting control bit PSPMODE (TRISE<4>). In this mode, the input buffers are TTL.

# FIGURE 5-7: PORTD BLOCK DIAGRAM (IN I/O PORT MODE)

| Name     | Bit# | Buffer Type           | Function                                          |

|----------|------|-----------------------|---------------------------------------------------|

| RD0/PSP0 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit0 |

| RD1/PSP1 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit1 |

| RD2/PSP2 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit2 |

| RD3/PSP3 | bit3 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit3 |

| RD4/PSP4 | bit4 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit4 |

| RD5/PSP5 | bit5 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit5 |

| RD6/PSP6 | bit6 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit6 |

| RD7/PSP7 | bit7 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit7 |

#### TABLE 5-7:PORTD FUNCTIONS

Legend: ST = Schmitt Trigger input TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffer when in Parallel Slave Port Mode.

#### TABLE 5-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Address | Name  | Bit 7 | Bit 6  | Bit 5    | Bit 4       | Bit 3 | Bit 2     | Bit 1         | Bit 0     | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|-------|--------|----------|-------------|-------|-----------|---------------|-----------|--------------------------|---------------------------|

| 08h     | PORTD | RD7   | RD6    | RD5      | RD4         | RD3   | RD2       | RD1           | RD0       | xxxx xxxx                | uuuu uuuu                 |

| 88h     | TRISD | PORT  | D Data | Directio | on Register |       |           |               |           | 1111 1111                | 1111 1111                 |

| 89h     | TRISE | IBF   | OBF    | IBOV     | PSPMODE     | —     | PORTE Dat | a Direction B | 0000 -111 | 0000 -111                |                           |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTD.

# 8.3 <u>Timer1 Operation in Asynchronous</u> <u>Counter Mode</u> Applicable Devices 72 73 73A 74 74A 76 77

If control bit T1SYNC (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during SLEEP and can generate an interrupt on overflow which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 8.3.2).

In asynchronous counter mode, Timer1 can not be used as a time-base for capture or compare operations.

# 8.3.1 EXTERNAL CLOCK INPUT TIMING WITH UNSYNCHRONIZED CLOCK

If control bit T1SYNC is set, the timer will increment completely asynchronously. The input clock must meet certain minimum high time and low time requirements. Refer to the appropriate Electrical Specifications Section, timing parameters 45, 46, and 47.

# 8.3.2 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running, from an external asynchronous clock, will guarantee a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself poses certain problems since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Example 8-1 is an example routine to read the 16-bit timer value. This is useful if the timer cannot be stopped.

#### EXAMPLE 8-1: READING A 16-BIT FREE-RUNNING TIMER

```

; All interrupts are disabled

MOVE

TMR1H, W ;Read high byte

MOVWF TMPH

;

TMR1L, W ;Read low byte

MOVF

MOVWE TMPL

;

MOVF

TMR1H, W ;Read high byte

TMPH, W ;Sub 1st read

SUBWF

; with 2nd read

BTFSC STATUS,Z ;Is result = 0

CONTINUE ;Good 16-bit read

GOTO

;

; TMR1L may have rolled over between the read

of the high and low bytes. Reading the high

;

and low bytes now will read a good value.

MOVF

TMR1H, W ;Read high byte

MOVWF

TMPH

TMR1L, W ;Read low byte

MOVE

MOVWE TMPL

;

; Re-enable the Interrupt (if required)

;Continue with your code

CONTINUE

```

## 8.4 <u>Timer1 Oscillator</u> Applicable Devices 72 73 73 74 74 76 77

A crystal oscillator circuit is built in between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 200 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal. Table 8-1 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator. The user must provide a software time delay to ensure proper oscillator start-up.

#### TABLE 8-1: CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR

| Osc Type                                                                                                                                                                                                                                                                                                   | Freq                                     | C1    | C2    |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------|-------|--|--|--|--|--|--|--|--|

| LP                                                                                                                                                                                                                                                                                                         | 32 kHz                                   | 33 pF | 33 pF |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                            | 100 kHz 15 pF 15 p                       |       |       |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                            | 200 kHz                                  | 15 pF |       |  |  |  |  |  |  |  |  |

| These v                                                                                                                                                                                                                                                                                                    | ese values are for design guidance only. |       |       |  |  |  |  |  |  |  |  |

| Crystals Tested:                                                                                                                                                                                                                                                                                           |                                          |       |       |  |  |  |  |  |  |  |  |

| 32.768 kHz                                                                                                                                                                                                                                                                                                 | 2.768 kHz Epson C-001R32.768K-A ± 20 PPM |       |       |  |  |  |  |  |  |  |  |

| 100 kHz                                                                                                                                                                                                                                                                                                    | Epson C-2 100.00 KC-P ± 20 PP            |       |       |  |  |  |  |  |  |  |  |

| 200 kHz                                                                                                                                                                                                                                                                                                    | STD XTL 200.000 kHz ± 20 P               |       |       |  |  |  |  |  |  |  |  |

| <ul> <li>Note 1: Higher capacitance increases the stability of oscillator but also increases the start-up time.</li> <li>2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.</li> </ul> |                                          |       |       |  |  |  |  |  |  |  |  |

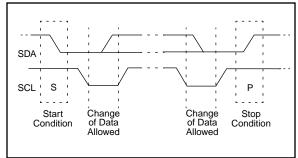

## 11.4 <u>I<sup>2</sup>C<sup>™</sup> Overview</u>

This section provides an overview of the Inter-Integrated Circuit ( $I^2C$ ) bus, with Section 11.5 discussing the operation of the SSP module in  $I^2C$  mode.

The  $l^2C$  bus is a two-wire serial interface developed by the Philips Corporation. The original specification, or standard mode, was for data transfers of up to 100 Kbps. The enhanced specification (fast mode) is also supported. This device will communicate with both standard and fast mode devices if attached to the same bus. The clock will determine the data rate.

The  $l^2C$  interface employs a comprehensive protocol to ensure reliable transmission and reception of data. When transmitting data, one device is the "master" which initiates transfer on the bus and generates the clock signals to permit that transfer, while the other device(s) acts as the "slave." All portions of the slave protocol are implemented in the SSP module's hardware, except general call support, while portions of the master protocol need to be addressed in the PIC16CXX software. Table 11-3 defines some of the  $l^2C$  bus terminology. For additional information on the  $l^2C$  interface specification, refer to the Philips document "*The*  $l^2C$  bus and how to use it."#939839340011, which can be obtained from the Philips Corporation.

In the I<sup>2</sup>C interface protocol each device has an address. When a master wishes to initiate a data transfer, it first transmits the address of the device that it wishes to "talk" to. All devices "listen" to see if this is their address. Within this address, a bit specifies if the master wishes to read-from/write-to the slave device. The master and slave are always in opposite modes (transmitter/receiver) of operation during a data transfer. That is they can be thought of as operating in either of these two relations:

- Master-transmitter and Slave-receiver

- · Slave-transmitter and Master-receiver

In both cases the master generates the clock signal.

The output stages of the clock (SCL) and data (SDA) lines must have an open-drain or open-collector in order to perform the wired-AND function of the bus. External pull-up resistors are used to ensure a high level when no device is pulling the line down. The number of devices that may be attached to the I<sup>2</sup>C bus is limited only by the maximum bus loading specification of 400 pF.

# 11.4.1 INITIATING AND TERMINATING DATA TRANSFER

During times of no data transfer (idle time), both the clock line (SCL) and the data line (SDA) are pulled high through the external pull-up resistors. The START and STOP conditions determine the start and stop of data transmission. The START condition is defined as a high to low transition of the SDA when the SCL is high. The STOP condition is defined as a low to high transition of the SDA when the SCL is high. The START and STOP conditions for starting and terminating data transfer. Due to the definition of the START and STOP conditions, when data is being transmitted, the SDA line can only change state when the SCL line is low.

#### FIGURE 11-14: START AND STOP CONDITIONS

| Term            | Description                                                                                                                                 |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Transmitter     | The device that sends the data to the bus.                                                                                                  |

| Receiver        | The device that receives the data from the bus.                                                                                             |

| Master          | The device which initiates the transfer, generates the clock and terminates the transfer.                                                   |

| Slave           | The device addressed by a master.                                                                                                           |

| Multi-master    | More than one master device in a system. These masters can attempt to control the bus at the same time without corrupting the message.      |

| Arbitration     | Procedure that ensures that only one of the master devices will control the bus. This ensure that the transfer data does not get corrupted. |

| Synchronization | Procedure where the clock signals of two or more devices are synchronized.                                                                  |

# TABLE 11-3: I<sup>2</sup>C BUS TERMINOLOGY

#### TABLE 12-3: BAUD RATES FOR SYNCHRONOUS MODE

| BAUD        | Fosc = 2 | 20 MHz     | SPBRG              | 16 MHz |            | SPBRG              | 10 MHz |            | SPBRG              | 7.15909 I | MHz        | SPBRG              |

|-------------|----------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|-----------|------------|--------------------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD     | %<br>ERROR | value<br>(decimal) |

| 0.3         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 1.2         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 2.4         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 9.6         | NA       | -          | -                  | NA     | -          | -                  | 9.766  | +1.73      | 255                | 9.622     | +0.23      | 185                |

| 19.2        | 19.53    | +1.73      | 255                | 19.23  | +0.16      | 207                | 19.23  | +0.16      | 129                | 19.24     | +0.23      | 92                 |

| 76.8        | 76.92    | +0.16      | 64                 | 76.92  | +0.16      | 51                 | 75.76  | -1.36      | 32                 | 77.82     | +1.32      | 22                 |

| 96          | 96.15    | +0.16      | 51                 | 95.24  | -0.79      | 41                 | 96.15  | +0.16      | 25                 | 94.20     | -1.88      | 18                 |

| 300         | 294.1    | -1.96      | 16                 | 307.69 | +2.56      | 12                 | 312.5  | +4.17      | 7                  | 298.3     | -0.57      | 5                  |

| 500         | 500      | 0          | 9                  | 500    | 0          | 7                  | 500    | 0          | 4                  | NA        | -          | -                  |

| HIGH        | 5000     | -          | 0                  | 4000   | -          | 0                  | 2500   | -          | 0                  | 1789.8    | -          | 0                  |

| LOW         | 19.53    | -          | 255                | 15.625 | -          | 255                | 9.766  | -          | 255                | 6.991     | -          | 255                |

|                     | Fosc = | 5.0688 M   | Hz                          | 4 MHz  |            |                             | 3.579545 | 5 MHz      |                             | 1 MHz  |            |                             | 32.768 kHz |            |                             |

|---------------------|--------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|--------|------------|-----------------------------|------------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD      | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | NA     | -          | -                           | 0.303      | +1.14      | 26                          |

| 1.2                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | 1.202  | +0.16      | 207                         | 1.170      | -2.48      | 6                           |

| 2.4                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | 2.404  | +0.16      | 103                         | NA         | -          | -                           |

| 9.6                 | 9.6    | 0          | 131                         | 9.615  | +0.16      | 103                         | 9.622    | +0.23      | 92                          | 9.615  | +0.16      | 25                          | NA         | -          | -                           |

| 19.2                | 19.2   | 0          | 65                          | 19.231 | +0.16      | 51                          | 19.04    | -0.83      | 46                          | 19.24  | +0.16      | 12                          | NA         | -          | -                           |

| 76.8                | 79.2   | +3.13      | 15                          | 76.923 | +0.16      | 12                          | 74.57    | -2.90      | 11                          | 83.34  | +8.51      | 2                           | NA         | -          | -                           |

| 96                  | 97.48  | +1.54      | 12                          | 1000   | +4.17      | 9                           | 99.43    | +3.57      | 8                           | NA     | -          | -                           | NA         | -          | -                           |

| 300                 | 316.8  | +5.60      | 3                           | NA     | -          | -                           | 298.3    | -0.57      | 2                           | NA     | -          | -                           | NA         | -          | -                           |

| 500                 | NA     | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | NA     | -          | -                           | NA         | -          | -                           |

| HIGH                | 1267   | -          | 0                           | 100    | -          | 0                           | 894.9    | -          | 0                           | 250    | -          | 0                           | 8.192      | -          | 0                           |

| LOW                 | 4.950  | -          | 255                         | 3.906  | -          | 255                         | 3.496    | -          | 255                         | 0.9766 | -          | 255                         | 0.032      | -          | 255                         |

# TABLE 12-4: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD |       |            | SPBRG     | 16 MHz |       | SPBRG     | 10 MHz |       | SPBRG     | 7.15909 | MHz        | SPBRG     |

|------|-------|------------|-----------|--------|-------|-----------|--------|-------|-----------|---------|------------|-----------|

| RATE |       | %<br>ERROR | value     |        | %     | value     |        | %     | value     |         | %<br>ERROR | value     |

| (K)  | KBAUD | ERROR      | (decimal) | RBAUD  | ERROR | (decimal) | REAUD  | ERROR | (decimal) | REAUD   | ERROR      | (decimal) |

| 0.3  | NA    | -          | -         | NA     | -     | -         | NA     | -     | -         | NA      | -          | -         |

| 1.2  | 1.221 | +1.73      | 255       | 1.202  | +0.16 | 207       | 1.202  | +0.16 | 129       | 1.203   | +0.23      | 92        |

| 2.4  | 2.404 | +0.16      | 129       | 2.404  | +0.16 | 103       | 2.404  | +0.16 | 64        | 2.380   | -0.83      | 46        |

| 9.6  | 9.469 | -1.36      | 32        | 9.615  | +0.16 | 25        | 9.766  | +1.73 | 15        | 9.322   | -2.90      | 11        |

| 19.2 | 19.53 | +1.73      | 15        | 19.23  | +0.16 | 12        | 19.53  | +1.73 | 7         | 18.64   | -2.90      | 5         |

| 76.8 | 78.13 | +1.73      | 3         | 83.33  | +8.51 | 2         | 78.13  | +1.73 | 1         | NA      | -          | -         |

| 96   | 104.2 | +8.51      | 2         | NA     | -     | -         | NA     | -     | -         | NA      | -          | -         |

| 300  | 312.5 | +4.17      | 0         | NA     | -     | -         | NA     | -     | -         | NA      | -          | -         |

| 500  | NA    | -          | -         | NA     | -     | -         | NA     | -     | -         | NA      | -          | -         |

| HIGH | 312.5 | -          | 0         | 250    | -     | 0         | 156.3  | -     | 0         | 111.9   | -          | 0         |

| LOW  | 1.221 | -          | 255       | 0.977  | -     | 255       | 0.6104 | -     | 255       | 0.437   | -          | 255       |

|                     | Fosc = | 5.0688 MI  | Hz                          | 4 MHz  |            |                             | 3.57954 | 5 MHz      |                             | 1 MHz  |            |                             | 32.768 kHz |            |                             |

|---------------------|--------|------------|-----------------------------|--------|------------|-----------------------------|---------|------------|-----------------------------|--------|------------|-----------------------------|------------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD      | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3                 | 0.31   | +3.13      | 255                         | 0.3005 | -0.17      | 207                         | 0.301   | +0.23      | 185                         | 0.300  | +0.16      | 51                          | 0.256      | -14.67     | 1                           |

| 1.2                 | 1.2    | 0          | 65                          | 1.202  | +1.67      | 51                          | 1.190   | -0.83      | 46                          | 1.202  | +0.16      | 12                          | NA         | -          | -                           |

| 2.4                 | 2.4    | 0          | 32                          | 2.404  | +1.67      | 25                          | 2.432   | +1.32      | 22                          | 2.232  | -6.99      | 6                           | NA         | -          | -                           |

| 9.6                 | 9.9    | +3.13      | 7                           | NA     | -          | -                           | 9.322   | -2.90      | 5                           | NA     | -          | -                           | NA         | -          | -                           |

| 19.2                | 19.8   | +3.13      | 3                           | NA     | -          | -                           | 18.64   | -2.90      | 2                           | NA     | -          | -                           | NA         | -          | -                           |

| 76.8                | 79.2   | +3.13      | 0                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA         | -          | -                           |

| 96                  | NA     | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA         | -          | -                           |

| 300                 | NA     | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA         | -          | -                           |

| 500                 | NA     | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA         | -          | -                           |

| HIGH                | 79.2   | -          | 0                           | 62.500 | -          | 0                           | 55.93   | -          | 0                           | 15.63  | -          | 0                           | 0.512      | -          | 0                           |

| LOW                 | 0.3094 | -          | 255                         | 3.906  | -          | 255                         | 0.2185  | -          | 255                         | 0.0610 | -          | 255                         | 0.0020     | -          | 255                         |

| BAUD<br>RATE<br>(K) | Fosc = 2<br>KBAUD | 20 MHz<br>%<br>ERROR | SPBRG<br>value<br>(decimal) | 16 MHz<br>KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) | 10 MHz<br>KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) | 7.16 MH | z<br>%<br>ERROR | SPBRG<br>value<br>(decimal) |

|---------------------|-------------------|----------------------|-----------------------------|-----------------|------------|-----------------------------|-----------------|------------|-----------------------------|---------|-----------------|-----------------------------|

| 9.6                 | 9.615             | +0.16                | 129                         | 9.615           | +0.16      | 103                         | 9.615           | +0.16      | 64                          | 9.520   | -0.83           | 46                          |

| 19.2                | 19.230            | +0.16                | 64                          | 19.230          | +0.16      | 51                          | 18.939          | -1.36      | 32                          | 19.454  | +1.32           | 22                          |

| 38.4                | 37.878            | -1.36                | 32                          | 38.461          | +0.16      | 25                          | 39.062          | +1.7       | 15                          | 37.286  | -2.90           | 11                          |

| 57.6                | 56.818            | -1.36                | 21                          | 58.823          | +2.12      | 16                          | 56.818          | -1.36      | 10                          | 55.930  | -2.90           | 7                           |

| 115.2               | 113.636           | -1.36                | 10                          | 111.111         | -3.55      | 8                           | 125             | +8.51      | 4                           | 111.860 | -2.90           | 3                           |

| 250                 | 250               | 0                    | 4                           | 250             | 0          | 3                           | NA              | -          | -                           | NA      | -               | -                           |

| 625                 | 625               | 0                    | 1                           | NA              | -          | -                           | 625             | 0          | 0                           | NA      | -               | -                           |

| 1250                | 1250              | 0                    | 0                           | NA              | -          | -                           | NA              | -          | -                           | NA      | -               | -                           |

# TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD        | Fosc = 5 | .068 MHz   | SPBRG              | 4 MHz  |            | SPBRG              | 3.579 Mł | Ηz         | SPBRG              | 1 MHz  |            | SPBRG              | 32.768 | κHz        | SPBRG              |

|-------------|----------|------------|--------------------|--------|------------|--------------------|----------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) |

| 9.6         | 9.6      | 0          | 32                 | NA     | -          | -                  | 9.727    | +1.32      | 22                 | 8.928  | -6.99      | 6                  | NA     | -          | -                  |

| 19.2        | 18.645   | -2.94      | 16                 | 1.202  | +0.17      | 207                | 18.643   | -2.90      | 11                 | 20.833 | +8.51      | 2                  | NA     | -          | -                  |

| 38.4        | 39.6     | +3.12      | 7                  | 2.403  | +0.13      | 103                | 37.286   | -2.90      | 5                  | 31.25  | -18.61     | 1                  | NA     | -          | -                  |

| 57.6        | 52.8     | -8.33      | 5                  | 9.615  | +0.16      | 25                 | 55.930   | -2.90      | 3                  | 62.5   | +8.51      | 0                  | NA     | -          | -                  |

| 115.2       | 105.6    | -8.33      | 2                  | 19.231 | +0.16      | 12                 | 111.860  | -2.90      | 1                  | NA     | -          | -                  | NA     | -          | -                  |

| 250         | NA       | -          | -                  | NA     | -          | -                  | 223.721  | -10.51     | 0                  | NA     | -          | -                  | NA     | -          | -                  |

| 625         | NA       | -          | -                  | NA     | -          | -                  | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| 1250        | NA       | -          | -                  | NA     | -          | -                  | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

**Note:** For the PIC16C73/73A/74/74A, the asynchronous high speed mode (BRGH = 1) may experience a high rate of receive errors. It is recommended that BRGH = 0. If you desire a higher baud rate than BRGH = 0 can support, refer to the device errata for additional information, or use the PIC16C76/77.

#### 12.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>) or enable bit CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set then CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to the RCREG register (if it is empty). When the transfer is complete, interrupt flag bit RCIF (PIR1<5>) is set. The actual interrupt can be enabled/disabled by setting/clearing enable bit RCIE (PIE1<5>). Flag bit RCIF is a read only bit which is reset by the hardware. In this case it is reset when the RCREG register has been read and is empty. The RCREG is a double buffered register, i.e. it is a two deep FIFO. It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR register. On the clocking of the last bit of the third byte, if the RCREG register is still full then overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. The RCREG register can be read twice to retrieve the two bytes in the FIFO. Bit OERR has to be cleared in software (by clearing bit CREN). If bit OERR is set, transfers from the RSR to the RCREG are inhibited, so it is essential to clear bit OERR if it is set. The 9th receive bit is buffered the same way as the receive data. Reading the RCREG register, will load bit RX9D with a new value, therefore it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old RX9D information.

Steps to follow when setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. (Section 12.1)

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

| Address | Name  | Bit 7                | Bit 6     | Bit 5    | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|-------|----------------------|-----------|----------|-------|-------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF      | RCIF     | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA | SPEN                 | RX9       | SREN     | CREN  | _     | FERR   | OERR   | RX9D   | 0000 -00x                | 0000 -00x                 |

| 1Ah     | RCREG | USART Re             | eceive Re | egister  |       |       |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE      | RCIE     | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA | CSRC                 | TX9       | TXEN     | SYNC  |       | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | SPBRG | Baud Rate            | Generat   | or Regis | ter   |       |        |        |        | 0000 0000                | 0000 0000                 |

#### TABLE 12-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Reception.

Note 1: Bits PSPIE and PSPIF are reserved on the PIC16C73/73A/76, always maintain these bits clear.

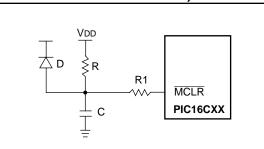

#### FIGURE 14-13: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- R < 40 kΩ is recommended to make sure that voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

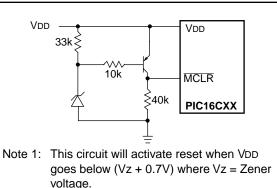

#### FIGURE 14-14: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- 2: Internal brown-out detection on the PIC16C72/73A/74A/76/77 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

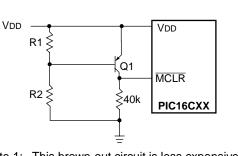

## FIGURE 14-15: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

- 2: Internal brown-out detection on the PIC16C72/73A/74A/76/77 should be disabled when using this circuit.

- 3: Resistors should be adjusted for the characteristics of the transistor.

#### FIGURE 14-20: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| ; a1   a2   a3   a4 ; a1   a2   a<br>osc1/^_/_/_/_//                               | 23 Q4 Q1              | Q1  Q2  Q3  Q4 | ; q1   q2   q3   q4 ;<br>//////////////////////////////////// | Q1   Q2   Q3   Q4 ; | Q1   Q2   Q3   Q4;<br>∕──∕──∕─ |

|------------------------------------------------------------------------------------|-----------------------|----------------|---------------------------------------------------------------|---------------------|--------------------------------|

| CLKOUT(4) ,//                                                                      | Tost(2)               |                |                                                               | \'                  | '                              |

| INT pin                                                                            |                       |                |                                                               | 1<br>1<br>1         |                                |

| INTF flag<br>(INTCON<1>)                                                           | <b>`</b>              | 1              | Interrupt Latency<br>(Note 2)                                 |                     |                                |

| GIE bit<br>(INTCON<7>)                                                             | Processor in<br>SLEEP |                |                                                               | ו<br>ו<br>ו<br>ו    | 1<br>1<br>1                    |

| INSTRUCTION FLOW                                                                   |                       |                |                                                               | 1                   | 1                              |

| PC X PC X PC+1                                                                     | X PC+2                | PC+2           | PC + 2                                                        | X 0004h             | 0005h                          |

| Instruction $\begin{cases} \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $ | + 1)                  | Inst(PC + 2)   |                                                               | Inst(0004h)         | Inst(0005h)                    |

| Instruction<br>executed I Inst(PC - 1) SLEEP                                       |                       | Inst(PC + 1)   | Dummy cycle                                                   | Dummy cycle         | Inst(0004h)                    |

| Note 1. XT US or Descillator mode on                                               |                       |                |                                                               |                     |                                |

Note 1: XT, HS or LP oscillator mode assumed.

2: TOST = 1024TOSC (drawing not to scale) This delay will not be there for RC osc mode.

3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

# 14.9 <u>Program Verification/Code Protection</u>

Applicable Devices

72 73 73A 74 74A 76 77

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip does not recommend code pro- |

|-------|----------------------------------------|

|       | tecting windowed devices.              |

#### 14.10 ID Locations

Applicable Devices

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

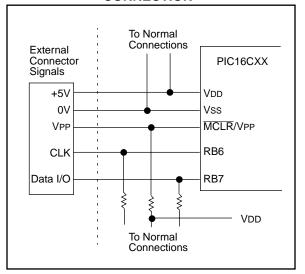

# 14.11 In-Circuit Serial Programming Applicable Devices 72/73/73A/74/74A/76/77

PIC16CXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed. The device is placed into a program/verify mode by holding the RB6 and RB7 pins low while raising the  $\overline{\text{MCLR}}$  (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After reset, to place the device into programming/verify mode, the program counter (PC) is at location 00h. A 6bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X Programming Specifications (Literature #DS30228).

#### FIGURE 14-21: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| RETLW             | Return v                         | vith Liter                                                                                                                                                         | al in W                             |                                      | RETURN            | Return f         | rom Sub                                                                | routine          |                       |

|-------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------------|-------------------|------------------|------------------------------------------------------------------------|------------------|-----------------------|

| Syntax:           | [ label ]                        | RETLW                                                                                                                                                              | k                                   |                                      | Syntax:           | [ label ]        | RETUR                                                                  | N                |                       |

| Operands:         | $0 \le k \le 2$                  | 55                                                                                                                                                                 |                                     |                                      | Operands:         | None             |                                                                        |                  |                       |

| Operation:        | $k \rightarrow (W);$             |                                                                                                                                                                    |                                     |                                      | Operation:        | $TOS\toF$        | ъС                                                                     |                  |                       |

|                   | $TOS \to F$                      | С                                                                                                                                                                  |                                     |                                      | Status Affected:  | None             |                                                                        |                  |                       |

| Status Affected:  | None                             |                                                                                                                                                                    |                                     |                                      | Encoding:         | 00               | 0000                                                                   | 0000             | 1000                  |

| Encoding:         | 11                               |                                                                                                                                                                    |                                     | Description:                         | Return fro        | m subrout        | ine. The st                                                            | ack is           |                       |

| Description:      | bit literal 'l<br>loaded fro     | The W register is loaded with the eight<br>bit literal 'k'. The program counter is<br>oaded from the top of the stack (the<br>return address). This is a two cycle |                                     |                                      |                   | nto the pro      | he top of the stack (TOS)<br>the program counter. This<br>instruction. |                  |                       |

|                   |                                  | eturn address). This is a two cycle<br>nstruction.                                                                                                                 |                                     |                                      | Words:            | 1                |                                                                        |                  |                       |

| Words:            | 1                                |                                                                                                                                                                    |                                     |                                      | Cycles:           | 2                |                                                                        |                  |                       |

| Cycles:           | 2                                |                                                                                                                                                                    |                                     |                                      | Q Cycle Activity: | Q1               | Q2                                                                     | Q3               | Q4                    |

| Q Cycle Activity: | 2<br>Q1                          | Q2                                                                                                                                                                 | Q3                                  | Q4                                   | 1st Cycle         | Decode           | No-<br>Operation                                                       | No-<br>Operation | Pop from<br>the Stack |

| 1st Cycle         | Decode                           | Read<br>literal 'k'                                                                                                                                                | No-<br>Operation                    | Write to W,<br>Pop from<br>the Stack | 2nd Cycle         | No-<br>Operation | No-<br>Operation                                                       | No-<br>Operation | No-<br>Operation      |

| 2nd Cycle         | No-<br>Operation                 | No-<br>Operation                                                                                                                                                   | No-<br>Operation                    | No-<br>Operation                     | Example           | RETURN           |                                                                        |                  |                       |

|                   | Operation                        | Operation                                                                                                                                                          | Operation                           | Operation                            |                   | After Inte       | errupt                                                                 |                  |                       |

| Example           | CALL TABL                        | ;offset                                                                                                                                                            | tains tabl<br>t value<br>7 has tabl |                                      |                   |                  | PC =                                                                   | TOS              |                       |

| TABLE             | ADDWF PC<br>RETLW k1<br>RETLW k2 | ;W = off<br>;Begin t<br>;                                                                                                                                          |                                     |                                      |                   |                  |                                                                        |                  |                       |

|                   | RETLW kn                         | ; End of                                                                                                                                                           | f table                             |                                      |                   |                  |                                                                        |                  |                       |

|                   |                                  | Before Instruction                                                                                                                                                 |                                     |                                      |                   |                  |                                                                        |                  |                       |

|                   | After Inst                       |                                                                                                                                                                    | 0x07                                |                                      |                   |                  |                                                                        |                  |                       |

|                   |                                  |                                                                                                                                                                    | value of k                          | 8                                    |                   |                  |                                                                        |                  |                       |

Applicable Devices 72 73 73A 74 74A 76 77

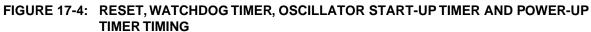

#### FIGURE 17-5: BROWN-OUT RESET TIMING

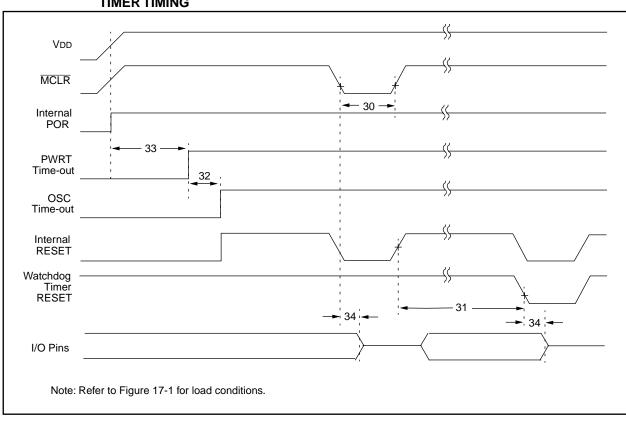

# TABLE 17-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†     | Max | Units | Conditions                |

|------------------|-------|--------------------------------------------------------|-----|----------|-----|-------|---------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                                 | 2   | —        | —   | μs    | VDD = 5V, -40°C to +125°C |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +125°C |

| 32               | Tost  | Oscillation Start-up Timer Period                      | _   | 1024Tosc | —   | —     | Tosc = OSC1 period        |

| 33*              | Tpwrt | Power-up Timer Period                                  | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +125°C |

| 34               | Tıoz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | _   | —        | 2.1 | μs    |                           |

| 35               | TBOR  | Brown-out Reset pulse width                            | 100 | _        | —   | μs    | $VDD \le BVDD (D005)$     |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# Applicable Devices 72 73 73A 74 74A 76 77

19.1 DC Characteristics: PIC16C73A/74A-04 (Commercial, Industrial, Extended) PIC16C73A/74A-10 (Commercial, Industrial, Extended) PIC16C73A/74A-20 (Commercial, Industrial, Extended)

| DC CHA                         | ARACTERISTICS                                                    |               | <b>Standa</b><br>Operati |                           |                      | ure -4<br>-4         | litions (unless otherwise stated) $10^{\circ}C \leq TA \leq +125^{\circ}C$ for extended, $10^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial and $C \leq TA \leq +70^{\circ}C$ for commercial                                                                                                                                      |